一种增益增强型套筒式运算放大器的设计

0.18um数字cmos工艺下的高增益运算放大器设计

0.18um数字cmos工艺下的高增益运算放大器设计

在0.18um数字CMOS工艺下,设计高塔益运算放大器需要考虑到各种因素。

以下是一些设计考虑和技术要素:

1.确定设计目标:首先需要确定设计高增益运算放大器的目标,例如放大器的增益、带宽、功耗等。

这些目标将直接影响设计的选择和决策。

2.选择台适的放大器架构:根据设计目标,选择合适的放大器架构。

例如,可以采用两级或三级放大器架构,以实现较高的增益和带宽。

3.优化输入和输出阻抗:输入和输出阻抗是影响放大器性能的重要因素。

通过优化输入和输出阻抗,可以提高放大器的增益、带宽和线性度。

4.考虑电源电压和功耗:在数字CMOS工艺下,电源电压和功耗是必须要考虑的因素。

通过优化电路设计和选择台适的器件。

可以降低功耗并提高电源效率。

5.考虑工艺偏差和失配:在数字CMOS工艺中,由于制造工艺的偏差和失配,会影响放大器的性能。

因此,在设计时需要考虑到这些因素,并采取相应的措施进行补偿和调整。

6.进行仿真和测试:在设计完成后,需要进行仿真和测试以验证设计的正确性和性能。

通过仿真和测试,可以发现并解决设计中存在的问题,并进行优化和改进。

总之。

在0.18um数字CMOS工艺下设计高增益运算放大器需要综合考虑各种因素。

并进行优化和调整。

通过不断改进和迭代,可以获得高性能、可靠性的放大器设计。

制表:审核:批准:。

程控增益放大器的几种通用设计方法

程控增益放大器的几种通用设计方法1. 引言1.1 引言程控增益放大器是一种常用的电子元器件,能够对输入信号进行放大,从而实现信号处理和传输。

在现代电子技术领域,程控增益放大器应用广泛,可以用于音频放大、信号采集、通信系统等多个领域。

在设计程控增益放大器时,需要考虑到电路的稳定性、放大倍数、输出功率等因素。

根据不同的需求和应用场景,可以采用不同的设计方法来实现。

本文将介绍几种通用的设计方法,包括反馈电路设计、桥式电路设计和共源共漏极电路设计。

通过深入研究这些设计方法,可以帮助工程师们更好地理解程控增益放大器的原理和工作方式,从而在实际应用中更加灵活地进行设计和调试。

希望本文能为读者提供有益的参考和指导,帮助他们在工程实践中取得更好的成果。

2. 正文2.1 设计方法一:反馈电路设计反馈电路是程控增益放大器设计中常用的一种方法。

通过在放大器的输入端和输出端之间引入反馈回路,可以有效地控制放大器的增益、带宽和稳定性。

反馈电路分为正反馈和负反馈两种类型,其中负反馈是应用最为广泛的一种。

在设计反馈电路时,首先需要选择合适的放大器结构和反馈类型。

常用的放大器结构包括电压放大器、电流放大器和功率放大器。

而在选择反馈类型时,需要考虑到设计的目的和性能要求,比如希望增加放大器的带宽就需要采用带宽增强型反馈电路。

在设计反馈电路时,还需要注意反馈回路的稳定性和相位裕度。

通过合理设计反馈网络中的元件参数,可以提高放大器的稳定性和抑制干扰。

还需要考虑反馈电路的线性度和降噪能力,以确保放大器输出的信号质量。

反馈电路是一种有效的设计方法,可以帮助提高放大器的性能和稳定性。

在实际应用中,设计者需要根据具体需求选择合适的反馈类型和参数,以实现最佳的设计效果。

2.2 设计方法二:桥式电路设计桥式电路设计是一种常用的程控增益放大器设计方法,具有较好的性能和稳定性。

在桥式电路设计中,通过合理选择电阻和电容的数值,可以实现放大器的特定增益和频率响应。

模拟集成电路设计——两级全差分高增益放大器设计_2

全差分高增益放大器的设计一、设计产品名称全差分高增益放大器二、设计目的1.掌握模拟集成电路的基本设计流程;2.掌握Cadence基本使用方法;3.学习模拟集成电路版图的设计要点;4.培养分析、解决问题的综合能力;5.掌握模拟集成电路的仿真方法;6.熟悉设计验证流程方法。

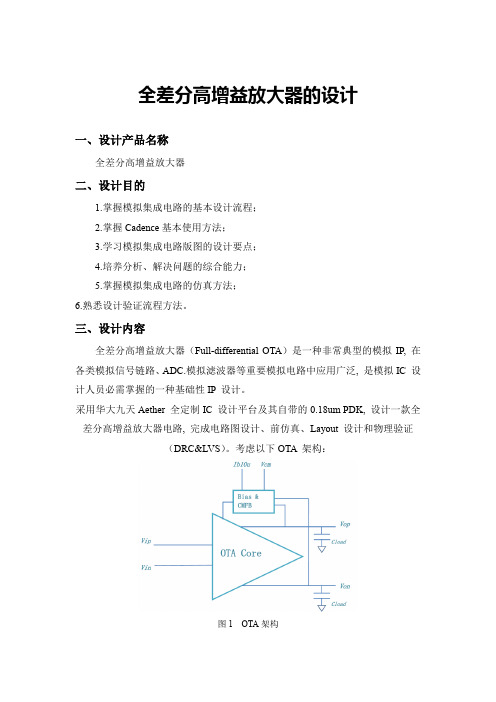

三、设计内容全差分高增益放大器(Full-differential OTA)是一种非常典型的模拟IP, 在各类模拟信号链路、ADC.模拟滤波器等重要模拟电路中应用广泛, 是模拟IC 设计人员必需掌握的一种基础性IP 设计。

采用华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK, 设计一款全差分高增益放大器电路, 完成电路图设计、前仿真、Layout 设计和物理验证(DRC&LVS)。

考虑以下OTA 架构:图1 OTA架构四、电路设计思路模拟集成电路的设计分为前端与后端, 设计流程可以分为明确性能要求、选择电路结构、计算器件参数、原理图绘制、前仿真、版图绘制、DRC设计规则检查、LVS版图与电路图一致性检查、寄生参数提取及后仿真、流片测试。

本次实验使用基于华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK, 实现模拟集成电路全差分高增益放大器的全流程设计与仿真。

(1)性能指标:需要验证三种PVT Corner:a) 电源电压1.8V, 温度27℃, corner 为TT;b) 电源电压1.6V, 温度80℃, corner 为SS;c) 电源电压2.0V, 温度-40℃, corner 为FF;要求各Corner 下开环技术指标(含Cload=10fF):①放大器开环DC 增益Av0≥90dB;②0dB 带宽BW0≥500MHz;③相位裕度Phase Margin≥50°。

④DC 抑制比PSRR-0≥60dB, (3*2=6 分)⑤10MHz 时抑制比PSRR-10M≥45dB。

2016套筒式运放器指导书

《模拟集成电路分析与设计课程设计》指导书题目:套筒式运算放大器仿真与优化指导老师:朱玮联系方式:wzhu@ 一、课程设计目的复习、巩固模拟集成电路课程所学知识,运用软件candence,在一定的工艺模型基础上,完成一个套筒式运放器的电路结构设计、参数手工估算和电路仿真验证,并根据仿真结果与指标间的折衷关系,对重点指标进行优化,掌握电路分析、电路设计的基本方法,加深对运放相关知识点的理解,培养分析问题、解决问题的能力。

二、实验目标和要求1)学习cadence工具的基本设计流程;2)了解运放器的工作原理,对运放器进行设计和优化;3)结合理论知识与实际操作,加深对理论知识的理解;4)完成课程设计报告。

三、设计参数和要求1 设计参数(供参考):表1:设计参数表2 设计要求:1)给出满足题目要求的电路图;2)根据设计目标,计算各MOS管的尺寸,各个结点的偏置电压和电流;3)利用cadence对电路进行仿真,仿真内容包括:DC、AC及瞬态仿真、幅频及相频特性曲线、直流开环增益、单位增益带宽、共模抑制比、电源抑制比、输出电压摆幅、功耗等;4)对结果进行分析,并设计优化电路(共模反馈和二级放大电路)提高套筒式共源共栅运放器的输出摆幅;5)若对参数进行改动,应说明改动原因。

3 设计报告要求1)设计指标的确定及原因;2)电路结构的确定及原因;3)电路原理论述,具体到每个MOS管的作用;4)每个晶体管沟道长度与宽度的确定依据,所用电阻电容的选取依据;5)设计过程;6)完成设计要求中的各种波形和性能指标:幅相和频相特性、带宽增益;7)仿真结果的总结与改进(思考与感想)。

四、设计基础1套筒式运放器提高输入跨导和输入阻抗可以优化单级运算放大器的增益性能。

提高输入阻抗比提高输入跨导更具有研究价值。

在电路结构中添置一个共源共栅放大器会显著提高阻抗值,套筒式共源共栅结构应运而生。

伴随着共源共栅结构的加入,P 管和N管的输出阻抗增大,以共源共栅差动的形式,使电路获得理想的增益,较高的速度、低功率损耗、低噪声效应。

基于增益增强技术轨至轨运算放大器的设计的开题报告

基于增益增强技术轨至轨运算放大器的设计的开题报告一、选题背景轨至轨运算放大器 (Rail-to-Rail Operational Amplifiers,RR-Op Amps) 是一种常见的运算放大器类型,具有能够输出接近电源电压(通常为正负电源电压)的输出电压范围的特性。

在许多应用中,轨至轨运算放大器非常重要,例如电源电压小或噪声敏感应用,以确保全范围内准确的放大器输入输出。

因此,设计一种高性能的轨至轨运算放大器是有意义和必要的。

二、选题意义在诸如自然科学、仪器测量、通信等广泛领域,运算放大器(Operational Amplifiers,Op Amps)已成为最为重要的电子元器件之一,起到放大输入电信号、提高电压、控制开关等多种作用。

轨至轨运算放大器以其特有的电压范围优势,适用于多种应用场合,因此研究和设计符合实际应用需要的轨至轨运算放大器具有非常广泛的应用前景。

三、论文研究内容本文将着重从设计角度出发,利用增益增强技术,设计一种高性能的轨至轨运算放大器。

具体研究内容包括以下方面:1. 初步探究轨至轨电路的基本原理和常见电路结构。

2. 详细介绍增益增强技术的基本原理和特点。

3. 分析增益增强技术在轨至轨运算放大器设计中的应用价值和意义。

4. 着重研究增益增强技术在轨至轨运算放大器设计中的具体实现方案和步骤。

5. 通过LTspice等模拟工具,进行仿真验证,并对结果进行分析和评价。

6. 结合以上分析和评价,进一步探究优化轨至轨运算放大器电路设计的可能途径。

7. 对本文研究成果进行总结,并展望轨至轨运算放大器发展前景。

四、研究方法和技术路线1. 文献综述,查阅相关文献,了解轨至轨运算放大器以及增益增强技术的研究现状和发展历程。

2. 理论分析,通过文献综述和相关理论知识,深入研究轨至轨运算放大器和增益增强技术的基本原理和特点。

3. 设计实现,根据前期的理论分析,通过CAD软件进行轨至轨运算放大器电路设计,实现增益增强技术在电路设计中的应用。

CMOS低噪声高增益放大器的设计及仿真分析

CMOS低噪声高增益放大器的设计及仿真分析本科学生毕业论文论文题目: CMOS低噪声高增益放大器的设计及仿真分析学院: 电子工程学院年级:专业: 集成电路设计与集成系统姓名:学号:指导教师:摘要运算放大器已经成为模拟电路设计中用途最广、最重要的部分。

运算放大器简称运放被广泛应用于无线电接收机的高频或中频前置放大级和一些高灵敏度电子设备中。

运放在电路中会产生噪声,在一些需要放大微弱信号的情况下,运放自身的噪声对有用信号的干扰可能会很严重,所以设计了一款低噪声系数、高功率增益、工作稳定性强、有足够带宽和较大动态范围的运算放大器电路。

MOS场效应晶体管会在电路中产生噪声,而且随着MOSFET尺寸的减小与信号幅度的降低,电路中低频噪声特性变得越来越重要。

论文首先分析运放电路中主要产生噪声的原因,然后结合基本噪声理论对电路中相应的元器件参数进行分析设计,然后针对电路的各项指标要求再对电路的元器件的参数进行调整。

运放输入级采用PMOS差分输入的结构,可以提高增益,也起到了抑制噪声的目的,输出级也采用共源共栅形式,可进一步抑制噪声。

通过对电路整体的噪声性能分析,优化了电路的噪声特性。

最后电路达到了设计的目标:增益带宽积大于60MHz、输入噪声功率谱密度在10MHz时小于35nV/rtHz、DC增益大于60dB、相位裕度大于45º。

关键词CMOS;运算放大器;低噪声;高增益;带宽IAbstractOperational amplifier (Op amp) is the most important and comprehensive element in CMOS analog integrated circuits. Operational amplifier is widely used in various types of high-frequency or intermediate frequency as a radio receiver pre-amplifier stage or the high sensitivity of electronic devices. MOS field effect transistor (MOSFET) circuit would bring noise under weak signal amplification. Noise interference may be very serious for useful signal in an op amp. Thus, it is very necessary that designing an op amp circuit with low noise, high gain, good stability, sufficient bandwidth and large dynamic range.MOS field effect transistor circuit would bring noise. With the MOSFET sizes decreasing and the signal amplitude decreasing, the low-frequency noise characteristics of the circuit are becoming increasingly important. This paper analyzes mainly noise sources of thee op ampcircuit firstly, then designs the corresponding component parameters of the circuit considering of the basic noise theory, and adjusts the parameters of certain components. The input stage of Op amp used PMOS differential input gain enhances direct telescopic structure to improve gain and suppress noise. The output stage is horizontal+output+stage to further suppress noise. Seen from the whole circuit noise performance,the noise characteristics are optimized. At last the simulated result also indicated that it reached the requirement of design: gain bandwidth product should be larger than 60dB, input noise power spectral density should be lower than 35nV/rtHz, DC gain shoud be higher than 60dB, phase margin should be larger than 45º.Key wordsCMOS; Operational amplifier; Low noise; High gain; BandwidthII目录摘要 ..................................................................... .. (I)Abstract ........................................................... .. (II)第一章绪论 ..................................................................... ................................................... 1 1.1 论文课题的价值及其意义 ..................................................................... ............... 1 1.2 运算放大器的发展过程及现状 ..................................................................... ........ 1 1.3 论文的章节安排 ..................................................................... . (2)第二章运算放大器的性能分析 ..................................................................... .................... 3 2.1 噪声 ..................................................................... .. (3)2.1.1 噪声类型 ..................................................................... .. (3)2.1.1.1 热噪声 ..................................................................... .. (3)2.1.1.2 散弹噪声 ..................................................................... . (4)2.1.1.3 闪烁噪声 ..................................................................... . (5)2.1.1.4 爆裂噪声 ..................................................................... . (5)2.1.2 MOS管中影响较大的噪声源 ....................................................................52.1.2.1 散弹噪声 ..................................................................... . (6)2.1.2.2 闪烁噪声 ..................................................................... . (6)2.1.2.3 沟道热噪声 ..................................................................... (6)2.1.3 噪声系数与计算噪声的基本方法 (7)2.1.3.1噪声系数 ..................................................................... .. (7)2.1.3.2噪声计算方法 ..................................................................... ..................... 7 2.2 开环增益 ..................................................................... .......................................... 8 2.3 开环带宽和增益带宽积 ..................................................................... ................... 8 2.4 输出摆幅 ..................................................................... .......................................... 9 2.5 相位裕度 ............................................................................................................... 9 2.6 DC功耗 ..................................................................... ............................................ 9 2.7 共模输入范围...................................................................... . (9)2.8 运放中各性能指标之间的关系 ..................................................................... ........ 9 2.9 两种常用结构CMOS放大器 ..................................................................... ........ 10 2.9.1 差分结构放大器 ..................................................................... ......................... 10 2.9.2 共源共栅结构放大器 ..................................................................... .. (13)第三章低噪声高增益运算放大器的设计 ..................................................................... ... 15 3.1 电路设计的指标 ..................................................................... ............................. 15 3.2 电路结构的设计 ..................................................................... .. (15)3.2.1 电路结构的确定 ..................................................................... (15)3.2.2 电路的噪声分析 ..................................................................... (17)3.2.3 电路的增益分析 ..................................................................... .................. 18 3.3 电路参数的确定 ..................................................................... ............................. 19 3.4 电路参数的验证 ..................................................................... .. (21)3.4.1 增益指标的验证 ..................................................................... (21)3.4.2 噪声指标的验证 ..................................................................... (22)第四章电路的仿真分析 ..................................................................... .............................. 23 4.1 理论值仿真分析 ..................................................................... .. (23)4.1.1 直流参数仿真 ..................................................................... . (23)4.1.2 交流小信号仿真 ..................................................................... .................. 24 4.2 电路的改进及仿真分析 ..................................................................... .. (25)4.2.1 M1管与M2管宽长比为20/1的仿真结果 (25)4.2.2 M1管与M2管宽长比为30/1的仿真结果 (26)4.2.3 增益提高的总结 ..................................................................... .................. 26 4.3 考虑噪声的仿真分析 ..................................................................... (27)4.3.1 噪声仿真 ..................................................................... (27)4.3.2 直流仿真 ..................................................................... (28)4.3.3 交流分析 ..................................................................... (28)4.3.4 与设计目标的比较 ..................................................................... .. (29)第五章版图的设计 ..................................................................... . (30)结论 ..................................................................... .. (33)参考文献 ..................................................................... . (34)致谢 ..................................................................... .. (36)CMOS低噪声高增益放大器的设计及仿真分析第一章绪论本章内容主要介绍运算放大器的发展过程,现阶段运算放大器的发展状况论文研究的意义与背景及论文的章节安排。

高增益CMOS全差分运放的研究和设计

possession of the market and their performance are in high challenge.To solve this problem,we had to take care in such aspect as circuit structure、material、teclmology.

operational amplifier will enhance the properties of the system.Now,the research

focus on the high speed signal processing and low power dissipation,which are appropriate domains we can make breakout.

1.3本文的工作以及文章组织

本文就是对工作在3V的运放放大电路进行研究,并分析各类 运放的性能指标。按照所提出的性能指标选择电路结构,这里我们 采用的是运算放大电路中的套筒式(telescopic)结构。通过对其性 能的分析,并进行器件参数上的优化,设计出一个增益在78dB, 功耗只有l 5roW的运算放大器单元,基本能够满足了设计的要求, 最后在CADENCE上画出版图。

这里我们具体的介绍一下目前运放的性能中一些重要的指标参 数,主要有开环增益、单位增益带宽、输出摆幅、建立时间、噪声等。 在后面的设计中,我们将进一步说明对每个参数的取舍以及折中的处 理办法。

套筒共源共栅运算放大器的mos管参数计算

套筒共源共栅运算放大器的mos管参数计算套筒共源共栅(Source Follower)运算放大器是一种常见的放大电路,由MOS管组成。

在这篇文章中,我将详细介绍套筒共源共栅运算放大器的MOS管参数计算方法。

我们需要明确套筒共源共栅运算放大器的结构。

它由一个MOS管的栅极和漏极之间串联一个电阻组成,形成了共源共栅结构。

这个结构中,MOS管的栅极和漏极分别是输入端和输出端。

在计算MOS管参数之前,我们需要先了解一些基本概念。

MOS管的工作点是指MOS管工作时的电流和电压值。

为了使套筒共源共栅运算放大器工作在最佳状态,我们需要确定MOS管的工作点。

MOS管的工作点可以通过偏置电压来确定。

在套筒共源共栅运算放大器中,我们通常选择漏极电流为恒定值,以确保放大器的稳定性和线性度。

因此,我们需要计算出电阻的值,并通过它来确定偏置电压。

接下来,我们需要计算MOS管的增益。

MOS管的增益可以通过计算输出电流和输入电流的比值来得到。

在套筒共源共栅运算放大器中,输出电流等于输入电流减去MOS管的漏极电流。

通过计算这两个电流的比值,我们可以得到MOS管的增益。

我们还需要计算输入电阻和输出电阻。

输入电阻是指输入端电压变化引起的输入电流变化的比率,输出电阻是指输出端电压变化引起的输出电流变化的比率。

通过计算输入电阻和输出电阻,我们可以评估套筒共源共栅运算放大器的输入输出特性。

我们还需要计算频率响应。

频率响应是指套筒共源共栅运算放大器对不同频率信号的放大程度。

通过计算频率响应,我们可以了解套筒共源共栅运算放大器在不同频率下的放大性能。

套筒共源共栅运算放大器的MOS管参数计算涉及到偏置电压、增益、输入输出电阻和频率响应等方面。

通过计算这些参数,我们可以全面评估套筒共源共栅运算放大器的性能,并进行合理的设计和优化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中 图 分 类 号 :T 0 N4 1 文 献 标 识 码 :A

De in o a n-b o t d t l s o c o r to l a l ir sg f a g i o s e ee c pi pe a i na mp i e f

OT a c iv 0 % s t n c u a y wi i s A c n a h e e 0. l et g a c r c t n 4 n ,whc es t e e i n g as q i e 1 i h ih me t h d sg o l u t w l . e

Ap ia in o It r t d Ci ui pl t f neg a e r t c o c s

一

种增益增强型套筒式运算放大器 的设计

蔡 坤 明 , 杞 鑫 。陶 吉 利 , 扣 宝 何 , 丁 (. 江 大 学 宁 波 理 工 学 院 , 江 宁 波 35 1 ; 1浙 浙 12 1 2 浙 江 大 学 微 电 子 与 光 电 子 研 究 所 , 江 杭 州 30 2 ) . 浙 10 7

2Ist eo colc oisad O t l t nc,Z ei g U i rt, n zo 10 7 C ia . tu fMir et nc n po e r i n it e r e c o s hj n nv s y Hagh u 30 2 , hn ) a ei

Ab t c :A u l i e e t l tl s o i O A s d n ih s e d ADC wa d sg e sr t a f l d f r ni ee c p c T u e i a h g p e y f a s e in d.F o rm t e ADC ’ d sg p c i ain, h s e in s e i c t f o

C IK n Mig , E Q i , A iL D N o a A u n H iX n T O j i, I G K u B o

( .igo Istt o eh o g ,Z e ag U i r t,Z ei g 3 5 1 , hn ; 1Nnb ntue fT cn l y hj n nv sy hj n 12 1 C ia i o i ei a

t a h T h s t e g i f 1 5. B n h U i— i h t t e O A a h an o 0 8 d a d t e n t Gan—B n w d h o 8 6 MHz a d i t f 9 3. .w t n y 2 . i o l 6 2 mW p w r c n u t n h h o e o s mp i .T e o

u e i a 2 b t 1 0 s d n 1 i 、 0 MHz h g s e d i h p e A ih p e hg s e d DC.B s d n MI 1 m ,3. P a e o S C 0. 3 3 V DK,S e t s lt n e u t s o s p cr i ai r s l h w e mu o

摘 要 :设 计 了一 种 用 于 高速 A C 中 的全 差 分 套 筒 式 运 算 放 大 器 。从 A C的 应 用 指 标 出发 , D D 确

定 了 设 计 目标 , 用 开 关 电 容 共 模 反 馈 、 益 增 强 等 技 术 实 现 了 一 个 可 用 于 l i 度 、0 利 增 2 bt精 10 MHz采 样 频 率 的 高 速 流 水 线 (ieie) D 中 的 运 算 放 大 器 。 基 于 S C 0 1 m, . 工 艺 ,pc e仿 真 结 Ppl dA C n MI .3t 33V x S et r 果 表 明 , 运 放 可 以 达 到 158d 的 增 益 , 位 增 益 带 宽 达 到 9 36MH , 功 耗 仅 为 2 . 。 运 放 该 0 . B 单 8 . z 而 62mW

t ei b cv f t T a cn r d s te cm o d ed ak ad gi bot ehiu ,te O A cn b h ds n oj t e o h O A w s o fme .U e h o m n moe feb c n a e g ei e i n— os d t nqe h T a e e c

Ke r s: tl s o i A ; an- o s d; o y wo d e e c p c OT gi bot e c mmo d e d a k; ih s e d ADC n mo e f e b c h g p e

随 着 数 字 信 号 处 理 技 术 的 不 断 发 展 , 号 处 理 系 统 信 对 模 数 转 换 器 ( DC 提 出 了 更 高 的 要 求 : 要 能 够 处 理 A ) 需 更 高 频 率 、 到更 高 精 度 的 AD 达 C。 运 算 放 大 器 作 为 高 速 高 精 度 A C 中 的 重 要 部 分 ,其 性 能 好 坏 直 接 决 定 整 个 D 系 统 性 能 的 高 低 。 而 在 电 源 电压 和 沟 道 长 度 不 断 减 少 然