串行数字存储测试系统设计

基于Labview实时系统设计与实现的测试系统

( h nIsi t o r eEeti P o us n C I Wu a 3 0 4 C ia Wu a tue f n t Mai lcr rp l o , SC, h n4 0 6 , hn ) n c i

Ab ta t hsat l it d cstetsigsse b s do a ve e l i esse t t esp ot f sr c:T i ri e nr u e t t c o h e n y m a e nL b iw ra— m tm.4 ht u p r o t y  ̄ h

o r i n s mpl. pe ato i y Ke y wor :v rua nsr me ;l or o y v r u n tume n n e i g r e c " e -i y t m ds it li t u nt ab at r i t alI s r nte gi e r n wo kb n h,r alimes s e

1 引 言

随着 计 算 机 和 软件 技 术 的 发 展 , 虚 拟 仪 器 软 件开发平 台L b e aViw加 上 多 功 能 数 据采 集 卡 的 实 现 方 案 ,具 有 简 便 灵 活 的 特 点 , 因 此 正在 逐渐 成 为 测 试 领 域 的发 展 方 向 。 aVI W 是 业 界 领 先 的 Lb E 高 效 图 形 化 开 发 环 境 , 是 美 国 NI ( t nl Nai a o Is u n) 司 研 制 的具 有 革 命 性 的虚 拟 仪 器 开 nt me t公 r 发 环 境 , a V E 功 能 非 常 强 大 ,它 是 带 有 可 扩 L b IW 展 函数 库 和 子 程 序 的通 用 程 序 设 计 系 统 , 不 仅 可 以用 于 一 般 的 Widws 面 应 用 程 序 设 计 , 且 no 桌 而

基于ARMLinux的GPS信号存储转发系统的设计

基于ARM-Linux 的GPS 信号存储转发系统的设计郭建京1,3,张云2,袁国良1,颜廷管3(1.上海海事大学信息工程学院,上海201306;2.上海海洋大学信息学院,上海201306;3.上海地测瑟福信息科技有限公司上海201306)摘要:为了克服徕卡GMX902系列接收机只有串口短距离数据传输的缺陷,实现徕卡GMX902远距离传输GPS 信号的目的,使其可以在野外恶劣无人坏境中实时存储GPS 信号数据,并且控制中心可以远距离调控GMX902,文中提出了一种基于ARM-Linux 的GPS 信号存储转发系统的设计方案,并完成了系统的软件设计和整套硬件测试。

长时间的综合测试数据表明,该系统能准确实时地将GPS 信号存储到ARM 板并转发给控制中心的上位机,实现了远距离调控和数据传输,系统性能稳定且容易操作,达到了系统设计要求。

关键词:ARM-Linux ;GPS ;TCP/IP ;存储转发;交互处理中图分类号:TP302文献标识码:A文章编号:1674-6236(2013)03-0123-03Design of GPS signal storage and retransmission system based on ARM-LinuxGUO Jian -jing 1,3,ZHANG Yun 2,YUAN Guo -liang 1,YAN Ting -guan 3(1.College of Information Engineering ,Shanghai Maritime University ,Shanghai 201306,China ;2.College of Information ,Shanghai Ocean University ,Shanghai 201306,China ;3.Shanghai Geosurf Corporation ,Shanghai 201306,China )Abstract:In order to overcome the defect that Leica GMX902series software receiver can only transmit data in short distance ,achieve the purpose of Leica GMX902remote transmitting GPS signal ,make it can real -time storage GPS signal data in the field and unmanned environment under bad weather ,and the control center can remote control GMX902,put forward a design scheme of GPS signal storage and retransmission system based on ARM -Linux ,and complete the system software design and a complete set of hardware test.Long time integration test data shows that the system can accurately real -time store GPS signal to ARM board and transmit to GPS signal analysis software of the computer in the control center ,realizes remote control and data transmission ,the system performance is stable and easy to operate ,meet the system design requirements.Key words:ARM -Linux ;GPS ;TCP/IP ;signal retransmission ;interactive processing收稿日期:2012-10-11稿件编号:201210074基金项目:上海市科学技术委员会资助项目(11510501300)作者简介:郭建京(1988—),男,河南开封人,硕士研究生。

基于TMS320F2812的DSP最小系统设计毕业设计论文

题目:基于TMS320F2812的DSP最小系统设计要求:TMS320F2812的DSP最小系统设计包括两个模块,即硬件设计模块和软件检测模块。

硬件设计模块包括电源设计、复位电路设计、时钟电路设计、存储器设计、JTAC接口设计等。

软件检测模块需要编写测试程序。

用Protel软件绘制原理图和PCB图。

从理论上分析,设计的系统要满足基本的信号处理要求。

DSP主要应用在数字信号处理中,目的是为了能够满足实时信号处理的要求,因此需要将数字信号处理中的常用运算执行的尽可能快。

这就决定了DSP的特点和关键技术。

适合数字信号处理的技术:DSP包涵乘法器,累加器,特殊地址发生器,领开销循环等;提高处理速度的技术:流水线技术,并行处理技术,超常指令等。

DSP对元件值的容限不敏感,受温度、环境等外部参与影响小;容易实现集成;VLSI 可以时分复用,共享处理器;方便调整处理器的系数实现自适应滤波;可实现模拟处理不能实现的功能:线性相位、多抽样率处理、级联、易于存储等;可用于频率非常低的信号。

关键词: TMS320F2812,CCS3.3,Protel99SE软件目录第1章绪论第2章系统设计2.1系统方案介绍2.2 系统结构设计第3章硬件电路设计3.1 TMS320F2812芯片介绍3.2电源及复位电路设计3.3 时钟电路设计3.4 DSP与JTAG接口设计3.5 DSP的串行接口设计3.6 通用扩展口设计3.7 总体电路原理图设计第4章软件设计4.1 程序设计4.2 仿真调试总结参考文献附录1:总体电路图附录2:程序代码第1章绪论数字化已成为电子、通信和信息技术的发展趋势与潮流。

在这种趋势与潮流的推动下,数字信号处理的理论与实现手段获得了快速的发展,已成为当代发展最快的学科之一。

而DSP芯片作为数字信号处理,尤其是实时数字信号处理的主要方法和手段,自20世纪70年代末、80年代初诞生以来,无论在性能上还是在价格上,都取得了突破性的迅猛发展。

基于单片机的PCBA测试系统研究

基于单片机的PCBA测试系统研究摘要:在本文中,基于PCBA的特点,提出了设备的PCB装配(PCBA,PCB assembly)测试系统。

该方案以功能测试方法为主,测试与测试框架相结合,无论是设计成本和是测试能力都达到了最佳,并给出了测试系统的硬件和软件设计方案。

关键词:PCBA 测试系统FPGA随着计算机技术和网络技术以及微电子技术的飞速发展,在电子测量技术领域,测量仪器不断更新发展,数字化仪器,智能仪器和虚拟仪器对电子设备的电子测量系统提出越来越高的要求。

在电子行业集成程度越来越高,从而使母板和PCB在材料和生产过程控制和发展越来越严格,而性能和可靠性的PCB测试要求会更高。

PCBA是Printed Circuit Board Assembly的简称,是在空的PCB板经过SMT上件,再通过DIP插件的全过程后得到的电路板。

任何电子产品的核心是PCBA,因此,为PCBA测试,尤其是现代电子产品的自动测试是一个重要的组成部分。

1 PCBA测试系统总体概述对不同性质的PCBA,该系统将重点讨论如何建立一个比较通用的PCBA的自动化测试平台。

基于功能测试的方面,PCBA测试平台是模拟系统的反馈信号和控制信号,并从相应的输出探针捕获输出通道互连的信号,判断输出通道信号从PC端软件来实现。

测试设备通常基于嵌入式处理器核心的控制面板,既包括内部的数字电路和模拟电路,还包含嵌入式处理器,无论是模拟信号,数字信号都存在,所以需要测试更多类型的内容。

为了全面完成设计任务,测试系统结构分为六个主要部分,即信号输入单元,信号采集与处理单元,数据存储单元,外部接口单元,控制单元,输出单元。

信号输入单元来完成从主电路板PCBA的被测试的信号预处理,如信号放大,滤波,整形,以满足后续的采集处理要求;采集与处理单元,分别是输入设备输出的信号采集和信号处理,以获得准确的测试数据,以确定系统是否准确;存储单元主要用于存储采集和处理的数据,和测试系统需要预先设定参数;输出单元有LED的输出,LCD液晶显示输出,并在主机上显示输出;接口单元是RS-232串行接口,USB接口,键盘接口和微控制器和FPGA的JTAG接口。

SOC中MBIST结构的设计与实现

SOC中MBIST结构的设计与实现作者:黄玮来源:《科技传播》2015年第12期摘要现代SOC电路中,嵌入式存储器所占规模与数量趋于变大,使得测试也越之复杂,目前常用的测试方法是通过eda软件自动生成MBIST电路进行自测试。

该设计基于一个实际的项目,对电路中存储器进行了完整的MBIST结构设计,同时加入了一个标志位移位电路,从而能够准确诊断出故障存储器,最后通过NC_verilog软件完成MBIST结构电路的仿真。

关键词存储器;MBIST;测试;SOC中图分类号TP39 文献标识码 A 文章编号 1674-6708(2015)141-0130-020 引言随着集成电路的规模越来越大,嵌入的存储器也随着变多,传统的测试方法受测试难度和测试成本所制约,已不为芯片设计厂商所接受。

目前存储器最常用的测试方法是通过内建自测试存储器电路[1](MBIST:存储器内建自测试)来实现,其通过eda软件,自动生成存储器的测试电路,根据相应的算法对存储器地址进行读写,完成存储器的测试。

该种测试方法虽然会在电路中加入一些控制逻辑,从而增加芯片的面积,但是对于大规模测试电路,其能够实现测试自动化,减小测试时间,提高测试覆盖率,很大程度上节约测试成本。

本文采用MBIST测试方法,完成对电路中存储器的测试,同时加入了标志位移位电路,能够准确判断错误存储器的位置,从而减少测试诊断时间。

1 MBIST结构介绍MBIST是以存储器为目标,通过采用特定的算法,来检测存储器中存在的某些缺陷的一种测试方法,其主要由bist控制电路,测试向量生成电路,测试响应比较电路三部分组成[2-3],其常用的结构图如图1所示。

图1 MBIST电路结构图1中bist控制电路其内部为一个状态机电路,控制bist电路对存储器进行读写操作;测试向量生成电路根据所选的算法生成不同的测试向量,不同的算法可以得到不同的存储器测试覆盖率;测试响应比较电路是通过对实际存储器输出值与控制电路生成的理想值做对比,来判断存储器是否有问题。

Tekronix TDS1000 2000数字存储示波器 说明书

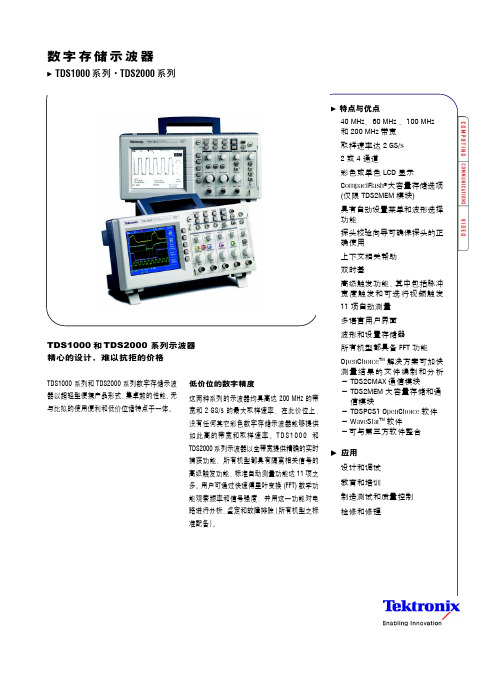

数字存储示波器系列·系列和TDS2000 系列示波器精心的设计,难以抗拒的价格TDS2000 系列数字存储示波低价位的数字精度数字存储示波器TDS1002系列·TDS2000系列2 TDS1000/TDS2000 系列示波器 /tds1000_2000脉冲宽度以及场选和行选视频触发功能使该 系列示波器适用于各种应用。

无与比拟的测量精度及高达 200 MHz 的带宽 和 2 GS/s 的最大取样速率。

自动检测正弦波、方波和视频信号,提供相 关测量读出值,用户可选择其它信号视图。

设置和使用易如反掌这些仪器具有古典的模拟式控制,用户界面非常简单,易于使用,不仅可减少学用时间,而且也提高了使用效率。

自动设置菜单、探头校验向导和上下文相关帮助以及彩色 LCD 显示(TDS2000 系列)等创新性功能,使仪器的设置和操作得以进一步的优化。

简单快捷的文件编制和分析功能OpenChoice TM 解决方案为示波器和个人计算机提供了既简单又全面的整合途径,使您可通过多种选择,轻而易举地编制测量报告和分析测量结果。

供选用的部件包括通信模块、CompactFlash ®大容量存储能力、OpenChoice 软件和第三方软件整合。

数字存储示波器TDS1002系列·TDS2000系列可迅速将波形和测量数据传送至外部 PC 机或在示波器之间快速传送。

只需按一下自动设置菜单上的按钮即可对电 路进行精确的分析、鉴定和故障排除。

通过 OpenChoice TM 软件轻而易举地编制测量结果文件并进行分析。

外部触发输入所有型号提供记录长度所有型号上2.5 K 样点垂直分辨率8位垂直灵敏度 在校准微调后,所有型号上2mV -5V/div DC 垂直精度所有型号上±3%垂直缩放 垂直扩展或压缩活动波形或已停止的波形最大输入电压 300 VRMS CAT II; 在超过100 kHz 时额定值以20 dB/10 Hz 下降,在3MHz 及以上时为13 Vp-pAC 位置范围 2mV -200 mV/div 2V; >200 mV -5V/div 50 V 带宽限制所有型号上20 MHz 输入耦合所有型号上AC, DC, GND输入阻抗1M Ω, 并联, 20 pF时基精度50 ppm水平缩放水平扩展或压缩活动波形或已停止的波形*1在2mV/div 时带宽为20 MHz, 适用于所有型号。

Agilent DSO8104A

Infiniium 8000 系列示波器是业内第一款同时具有快响应深存储技术、三维信息观察能力和高级分析能力的示波器。

包括数字存储示波器 (DSO) 和混合信号示波器 (MSO)的共4个型号的产品都支持最新一代MegaZoom 专利技术,该项技术把业内最深和响应最敏捷的存储器与最新高清晰显示技术结合,为长时间捕获和观察复杂波形中的关键技术资料全新Agilent Infiniium 8000 系列示波器新一代 MegaZoom 快响应深存储技术实现卓越混合信号分析1GHz 和 600MHz 带宽混合信号示波器(MSO )集成了4个示波器通道和 16 个数字通道4GSa/s 采样率高达128Mpts 的业内最高的深存储器最新一代 MegaZoom 技术:快速、响应敏捷的深存储器1024×768分辨率的XGA 的高清晰显示256 级彩色亮度等级提供丰富的第三维信息丰富的应用分析软件无人能及的 InfiniiMax 有源探头及连接附件获奖的用户界面标配触摸屏显示器开放 Windows ® XP Pro 操作系统更高性能的系统CPU信号细节提供了最佳手段。

最新一代 MegaZoom 技术能让设计人员长时间捕获模拟和数字信号,不但能够直观迅速地发现异常信号、对信号细节展开进行分析,而且还可通过分析软件得到详细分析数据。

所有这些能力均已集成在单台仪器之中。

为了满足您在性能和预算方面的双重要求,深存储器可以有多种选件。

2Infiniium 带给您的好处Agilent Infiniium 8000 系列示波器型号带宽通道数采样率标准存储器最大存储器DSO8064A 600 MHz 4 4 GSa/s 1 Mpts 128 Mpts MSO8064A 600 MHz 4 + 16 4 GSa/s 1 Mpts 128 Mpts DSO8104A 1 GHz 4 4 GSa/s 1 Mpts 128 Mpts MSO8104A1 GHz4 + 164 GSa/s1 Mpts128 Mpts嵌入式系统设计由于集成了诸如 SDRAM 和 PCI 这类更高速度的数字总线,并且采用 了16位或 32位处理器而变得成更为复杂,因此工程师非常需要满足测试需求、便于操作和配置灵活的测试仪器。

无人机测试数据采集系统设计

无人机测试数据采集系统设计冯博【摘要】For the rotary motion and short distance movement tests of UAV,a design scheme for the hardware platform of data acquisition system is provided. The hardware system was designed,in which the chipSTM32F103VE and C8051F340 are taken as the master controller module and signal acquisition module of the control core respectively,and based on it,the pro-gram design of the hardware equipment,communication protocol design of data acquisition system,and the development of Lab-VIEW test software were completed further. The functions of data acquisition,wireless data transmission,and host computer data display and storage were verified and realized by debugging and testing the data acquisition system.%针对无人机的旋转运动和短距离移动等环节的测试,给出一种数据采集系统硬件平台的设计方案,设计了以STM32F103VE,C8051F340为控制核心的主控制器模块、信号采集模块等硬件系统.在此基础上,进一步完成了硬件设备的程序设计,数据采集系统通信协议设计以及LabVIEW测试软件的开发.最后,对数据采集系统进行调试试验,最终验证和实现了系统的数据采集,无线数据传输,上位机数据显示存储等功能.【期刊名称】《现代电子技术》【年(卷),期】2016(039)001【总页数】5页(P49-53)【关键词】数据采集;无人机测试;无线数据通信;LabVIEW【作者】冯博【作者单位】沈阳工程学院,辽宁沈阳 110136【正文语种】中文【中图分类】TN911-34;TQ028.1随着无人机相关技术的发展,无人机的使用范围已拓展至军事、民用和科研三大领域[1]。

MCS-52单片机

智能,高效率,以及高可靠性!

由于单片机对成本是敏感的,所以目前占统治地位的软件还是最低级汇编语言,它是除了二进制机器码以上最低级的语言了,既然这么低级为什么还要用呢?很多高级的语言已经达到了可视化编程的水平为什么不用呢?原因很简单,就是单片机没有家用计算机那样的CPU,也没有像硬盘那样的海量存储设备。一个可视化高级语言编写的小程序里面即使只有一个按钮,也会达到几十K的尺寸!对于家用PC的硬盘来讲没什么,可是对于单片机来讲是不能接受的。单片机在硬件资源方面的利用率必须很高才行,所以汇编虽然原始却还是在大量使用。一样的道理,如果把巨型计算机上的操作系统和应用软件拿到家用PC上来运行,家用PC的也是承受不了的。

单片机扩展系统是在以MCS-52单片机为基础上扩展,使其能更方便地运用于测试系统中,不仅具有控制方便、组态简单和灵活性大等优点,而且可以大幅度提高被测试的技术指标,从而能够大大提高产品的质量和数量。单片机以其功能强、体积小、可靠性高、造价低和开发周期短等优点,称为在实时检测和自动控制领域中广泛应用的器件,在工业生产中称为必不可少的器件,尤其是在日常生活中发挥的作用也越来越大。本课题设计主要在MCS-52单片机上进行系统扩展,它包括程序存储器(ROM)扩展、数据存储器(RAM)扩展、I/O口扩展、定时/计数器扩展、中断系统扩展以及其它特殊功能扩展等。本文详述了在基本型单片机8052芯片的基础上,根据实际应用需要扩展必要的接口芯片资源,设计一个单片机通用系统的过程,并说明设计原理。

1.3 单片机应用

目前单片机渗透到我们生活的各个领域,几乎很难找到哪个领域没有单片机的踪迹。导弹的导航装置,飞机上各种仪表的控制,计算机的网络通讯与数据传输,工业自动化过程的实时控制和数据处理,广泛使用的各种智能IC卡,民用豪华轿车的安全保障系统,录像机、摄像机、全自动洗衣机的控制,以及程控玩具、电子宠物等等,这些都离不开单片机。更不用说自动控制领域的机器人、智能仪表、医疗器械了。因此,单片机的学习、开发与应用将造就一批计算机应用与智能化控制的科学家、工程师。

ATE

ATE的技术演进规律及多点测试的成本分析摘要:经由专用发展而成通用的ATE的新趋势之一是并行测试。

并行系统的设计原理揭示自阿姆达尔定律。

依据ITRS-2009对比2005年的ATE基础数据,计算分析了多点ATE测试的成本优势。

关键词:ATE;演进规律;阿姆达尔定律;并行测试;成本分析1引言测试技术的历史一直是一种有趣的对话,其发生在可能的测试技术与系统复杂性不断增长的指标需求之间,旨在达到较高水准的测试指标――比较每成本。

测试技术启用新方法(例如,并行测试)必将带来新挑战,新方法不仅决定于电子学的趋势,更依赖于我们每天都在与其握手的微电子学革命。

ATE(automatic test equipment,ATE)系统之于半导体制造业的作用,恰似神奇的自动“示波器”。

复杂的ATE系统的设计领域,包括了机械、电源、冷却、工业安全、模拟和数字电子学以及软件。

半导体自动测试机(ATE)的工作,主要使用两套测试系统:一是针对电流和电压等参数,二是针对逻辑功能。

当被测芯片内的门数量大于500 K,时钟频率大于200 MHz,ATE的测试成本已经等于硅工艺成本(Stephen Sunter,1998年)。

因此,测试经济学(economics of test)将继续成为新的测试方法学和测试师的关键驱动力之一。

本文首先概论ATE技术的演进规律,兼及ATE发展的并行测试新趋势,指出并行计算的理论――阿姆达尔定律的意义所在。

根据实用模型,例析ATE多点并行测试的成本优势,最后,总结全篇。

2ATE技术的演进规律ATE是一种通过计算机控制,进行器件、电路板和子系统等测试的设备。

通过计算机编程取代人工劳动,自动化地完成测试序列。

以下分论ATE的结构及其演进规律。

2.1 ATE的结构图1是典型的ATE结构组成:主机、测试台和工作站[[1, 2]。

主机内置了测试图形发生器、数据格式化与定时发生器、管脚参数测量单元(PMU)、中心PWU,以及器件电压源。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

串行数字存储测试系统设计摘要本文介绍了存储测试系统的发展与应用。

对串行SPI总线的原理、功能、信号和特点进行了详细的分析,并利用了串行SPI总线的优点,实现了存储测试过程中数据的转换和存储,大大的提高了系统的资源利用率。

此处详细的分析系统中CPLD控制数据的转换和存储的过程。

介绍了Verilog HDL语言的发展和优点,并用它进行编程和仿真,通过软件来控制硬件的运行。

关键词:存储测试,SPI,CPLD,Verilog HDL。

The design of Serial digital memorized testing andmeasuring systemAbstractThis paper introduces the development and applications of memorized testing and measuring system .The principle, function, signal and features of the serial SPI bus have been analyzed detailed, and the advantage of the serial SPI bus has been used that realize to the transform and the memory of the data, greatly improved the rate of systematic resource. Here, it analysis the process that how the CPLD controls the transform and the memory of the data. The advantage and development of the Verilog HDL that has been introduced, programming and simulating it , using the software to control the operation of hardware..Keyword: memorized test and measurement, SPI, CPLD, Verilog HDL.目录1 绪论 (1)1.1 存储测试技术的发展与应用 (1)1.2 CPLD的发展与特点 (3)1.2.1 CPLD的发展 (3)1.2.2 CPLD的特点 (4)1.3 Verilog HDL语言的介绍 (5)1.3.1 硬件描述语言(HDL) (5)1.3.2 Verilog HDL语言简介 (5)1.3.3 Verilog HDL语言的特点 (6)1.4.4 Verilog HDL与VHDL的比较 (7)1.4 Modelsim的简介 (7)2 串行SPI的介绍 (9)2.1各种串行总线的比较 (9)2.1.1 UART (9)2.1.2 I2C总线 (10)2.1.3 CAN (11)2.1.4 LIN (12)2.1.5 其它通用串行总线 (13)2.2 SPI 简介: (13)2.3 SPI总线的组成 (14)2.4在系统设计中使用SPI总线应注意的问题 (14)2.5 SPI总线的原理 (15)2.5.1信号线定义 (15)2.5.2通信机制 (16)3 硬件的设计 (18)3.1 主要芯片的介绍 (18)3.1.1 AT25640A芯片的介绍 (18)3.1.2 MAX147的介绍 (19)3.1.3 XCR3064XL的介绍 (21)3.2 硬件电路原理图 (22)4 软件的设计 (23)4.1存储器擦除程序 (23)4.2存储器写入程序 (28)5结论 (34)参考文献 (34)致谢 (37)1 绪论1.1 存储测试技术的发展与应用存储测试技术是将传感器、适配电路、数字化存储记录电路、通讯接口、控制指示单元及电源合成为一体,构成一个微小型化的、可安装在被测体内(相对)独立工作的测试系统的一种技术。

由于存储测试系统具有无需外引线、体积小、抗干扰性好、能适应特殊测试环境的特点,所以对于工程测试,特别是实况测试中经常遇到的测试引线困难或不便、安装空间狭窄、信号干扰严重的问题,存储测试提供了一个很好的解决方案。

存储测试典型的应用背景实例如:火炮膛压的测试、弹箭运动过程中各种参数的测试、机械运动零部件工况参数的测试。

八十年代初期随着微电子技术的发展,国外报道了利用存储器芯片作为信息载体的数字存储测试仪[1,2]。

九十年代传感器与微型电子记录仪组为一体的存储测试产品也在国际上出现,如奥地利AVL公司于1992年推出了存储式电子测压器[3]。

在国内,有关科技人员及时意识到了以数字存储为特征的新型测试方法的发展前景[4]。

中北大学(原华北工学院)祖静教授领导的小组率先开展了存储测试技术的研究。

1989年他们采用自行设计的存储测试专用厚膜集成电路,研制成功了用于火炮膛压测试的‘放入式电子测压器’。

该电子测压器体积小于38cm3,测压器内部的单通道瞬态波形记录仪体积仅为3cm3,该项技术处于国际领先水平。

这项成果标志着国内存储测试技术在军工测试领域首先取得了突破[5]。

此后,该小组研制的‘弹载全弹道参数记录仪’于1995年获国家发明三等奖[6]。

发展到目前为止,用于火炮膛压测试的放入式电子测压器已在多种火炮和弹药试验中进行了膛压测试,并于1997年正式颁布《放入式电子测压器规范》国军标[7];弹载全弹道参数记录仪已在多种弹箭试验中得到了应用,测量的参数有:发射飞行着靶加速度、弹底压力、子弹飞行姿态及其它弹箭参数[8.9];各种导弹(战术、战略导弹)及载人宇宙飞船的多种黑匣子己成为该领域试验研究的基本手段[10]。

车辆机械运动部件工况参数存测系统己在齿轮啮合应力测试、发动机活塞应力实况测试、坦克传动轴扭矩测试中获得了应用[10、11、12];石油井下电子测压器,已先后为玉门油田、江苏油田、河南油田等进行了井下压力测试[14];存储式冲击波超压测试系统已进行了炸药实爆测试试验,并取得了成功[15];人体运动及生理参数存储测试系统也得到了实际应用[16]。

综上所述可以看出,存储测试技术的发展解决了许多的测试难题,打破了一些传统的测试禁区,开辟了测试技术的一个新领域。

在无引线测试中,存储测试技术己经与传统的遥测技术互为补充,成为解决许多特殊测试问题(特别是军工测试问题)的一个重要技术手段。

从最初存储测试系统的开发到现在基于微米纳米技术的集成测试系统的研究,存储测试的内涵及相关技术不断发展前进。

在祖静教授的带领下,华北工学院在存储测试技术领域做了大量工作,现简要总结为以下几个方面:第一,在存储测试的理论方面。

1995年张文栋博士在他的博士论文中,对存测系统的设计理论、数字采样策略、信息编码压缩及存储方式进行了系统的研究总结。

此外他还提出了存测测试的几项关键技术,并做了初步的讨论。

他的工作为存储测试建立了一定的理论基础[17]。

第二,在电路的具体设计和实现上。

存测系统电路一直在改进提高。

这一方面是得益于高性能的电子元器件(如新型A/D转换器、仪表放大器、电源管理芯片等)的不断涌现,另一方面是由于自行设计的存储测试专用集成电路(ASIC)的集成度、设计水平也在不断提高。

这两方面的因素使得存测系统电路可靠性、通用性,测试精度、记录容量等性能都有了很大的提高[18]。

第三,在存测系统的制作工艺上。

通过反复实践,在不断总结经验的基础上,高强度、密集化、芯片与电池的合理布置的封装技术使系统体积得到了尽可能的减小、抗恶劣环境能力特别是抗冲击性能大大提高[19]。

第四,在测试系统的环境特性—环境因子的研究方面。

第五,存测系统的触发控制及电源管理技术。

存测系统安置在被测体内后,要能够通过适当的触发技术有效地控制系统的工作状态。

这一点对于存测系统与被测系统的协调工作是必不可少的,对于存测系统的功耗控制也起着非常重要的作用。

第六,微电子机械技术(MEMS)在存储测试中的应用。

MEMS 技术意味着可将传感器与电路系统集成在一个晶片上,构成单片的集成测试系统。

这将会极大地扩展存测系统的应用领域。

目前国内己经研制出将微机械加速度计与存测电路微封装为一体的集成加速度测试系统.。

MEMS技术作为一项革命性的技术,会给存测技术的发展提供新的、巨大的技术推动力[20]。

1.2 CPLD的发展与特点1.2.1 CPLD的发展当今社会是数字化的社会,是数字集成电路广泛应用的社会。

数字集成电路本身在不断的更新换代。

它由早期的电子管、晶体管、小中规模集成电路,发展到超大规模集成电路以及许多具有特定功能的专用集成电路[21]。

按制造的过程的不同专用集成电路ASIC(Application Specific IC)可以分为两大类:全定制和半定制。

全定制电路是有制造厂根据用户的要求,专门设计和制造的芯片。

这一类芯片专业性强,适合在大批量定型生产的产品中使用。

常见的存储器、CPU等芯片就是全定制产品[21]。

从20世纪70年代末开始,发展了一种称为可编程逻辑器件(PLD)的半定制芯片,这解决了门阵列和标准逻辑单元这两类产品的设计和编程只能在制造厂家进行的缺点。

这一阶段的产品主要有PAL(可编程阵列逻辑)和GAL(通用阵列逻辑)。

PAL,由一个可编程的“与”平面和一个固定的“或”平面构成,或门的输出可以通过触发器有选择地被置为寄存状态。

PAL器件是现场可编程的,实现工艺有反熔丝技术、EPROM 技术和EEPROM技术[22]。

还有一类结构更为灵活的可逻辑逻辑器件是可编程逻辑阵列(PLA),它也由一个“与”平面和一个“或”平面构成,但是这两个平面的连接关系是可编程的。

PLA器件既有现场可编程的,也有掩膜可编程的。

在PAL的基础上,又发展了一种通用阵列逻辑GAL,如GA1.16V8,GA L22VIO等。

它采用了EEPROM工艺,实现了电可按除、电可改写,其输出结构是可编程的逻辑宏单元,因而它的设计具有很强的灵活性,至今仍有许多人使川。

这些早期的PLD器件的一个共同特点是可以实现速度特性较好的逻辑功能,但其过于简单的结构也使它们只能实现规模较小的电路。

PLD 芯片内的硬件资源和连线资源是由制造厂生产好的,但用户可以借助功能强大的是设计自动化软件和编程器,自行在实验室内、研究室内,甚至车间等生产现场,进行设计和编程,实现所希望的数字系统。

设计师的主要任务是主要工作是: (1)功根据设计对象的逻辑功能进行算法设计和电路划分,进而给出相应的行为描述或结构描述。

(2)利用制造厂提供的编辑工具以文本方式或图形文件(例如逻辑图)把上述描述输入计算机。