增益可调宽带CMOS低噪声放大器设计

CMOS低噪声放大器的设计与优化的开题报告

CMOS低噪声放大器的设计与优化的开题报告一、选题背景CMOS低噪声放大器作为一种重要的电路结构,在各种电子系统中广泛应用。

在无线通信、雷达测量、成像等领域,CMOS低噪声放大器的性能对整个系统的性能影响至关重要。

因此,设计和优化高性能的CMOS低噪声放大器对于提高电子系统性能具有重要的意义。

二、选题意义本课题的研究涉及到多个学科领域,包括电路设计、模拟仿真、集成电路工艺等。

另外,开展该课题有以下几个方面的意义:1. CMOS低噪声放大器是现代电子技术中不可缺少的一个部分。

在很多应用领域中,CMOS低噪声放大器的性能影响到整个系统的性能。

因此,设计和优化CMOS低噪声放大器对于提高电子系统的性能至关重要。

2. 现有的CMOS低噪声放大器设计方法存在一定的缺陷,比如性能复杂或者难以实现等。

因此,本课题的研究可为该领域提供新的设计方法,从而提高CMOS低噪声放大器的性能。

3. CMOS低噪声放大器的研究还直接关系到一些领域的发展,比如通信领域、医学成像领域等。

因此,本课题的研究可以推动这些领域的发展。

三、研究内容本课题的研究内容包括以下几个方面:1. CMOS低噪声放大器的设计和优化。

包括设计各个环节的电路部分(如共源放大器,差动放大器,电流源等),在完成设计后进行仿真和优化。

并通过实际测量对设计的放大器进行验证。

2. CMOS低噪声放大器的模拟仿真。

通过仿真软件(如Cadence等)对放大器的性能进行模拟,包括增益、带宽、噪声等指标。

3. CMOS低噪声放大器的工艺实现。

在进行电路设计后,需要实际在实验室中通过CMOS工艺进行实现以进行实际测试。

四、研究方法本课题研究采用的方法主要包括仿真模拟和实验测试两个部分。

具体来讲,仿真模拟主要采用SPICE仿真软件,进行各个部分电路的仿真以及系统仿真。

实验测试主要通过实际电路设计,并在实验室中进行工艺实现和测试。

五、预期结果本课题的研究旨在设计并优化高性能的CMOS低噪声放大器,主要预期结果如下:1. 在各个环节的电路设计上,实现高性能的CMOS低噪声放大器。

CMOS 3~5GHz超宽带低噪声放大器的设计

C MOS3~5GHz 宽带低 噪声放 大器 的设 计 超

刘玉静 ,温幸Biblioteka ,赵红东 (1 .河北 T 业 人学 信 息 Ⅲ 学 院 ,天 津 3 0 3 ;2 河 北 省』 电 视局 ,石 家庄 0 0 1 ) _ l 程 0 10 播 50 1

摘要

设计 了一个应用于超 宽带 ( WB)系统的 3 G 超 宽带低噪声放 大器.电路 由二阶切 比雪夫滤波器, U ~5 Hz

Ke r s UW B:c e y h v fl r e it es u t e d a k O n iea l e ;c s o e y wo d h b s e t ;r ssi h n — e b c ;i W o s mp i r a c d i e v f i f

0 引言

LUY -n ’ I uj g,W E n - o,Z AO Ho gd n i N Xigr H n .o g a

( . co l fn r a o n i e n ,H b i n e i f eh o g, i j 0 3 , h a . ee Po i e r d a i 1 S h o o I om t nE g er g ee U i r t o T cn l y Ta i 3 10 C i ;2 H b i rv c Bo cs n f i n i v sy o nn0 n n a tg

T ecr u t o s t f wo o d r e y h v f t rt e e it es u tfe b c i u tt et —tg a c d r ht c t r, h i ic n i s t — r e b s e l , h s i h n — d a kcr i h c s o Ch i e r sv e c , wo sa ec s o e c i h u e a e

小型cmos低噪放设计.wps

一个使用并联电阻反馈和系列感性调峰技术的小型宽带CMOS低噪声放大器摘要宽带低噪声放大器(LNA)利用分流电阻反馈和系列电感调峰技术达到宽频带内的输入匹配,功率增益和平滑的噪声系数(NF)响应。

此宽带低噪声放大器(LNA)是使用0.18米CMOS技术来实现的。

测量结果表明功率增益大于10 dB,从2到11.5 GHz的输入回波损耗低于10 dB。

三阶输入截点IIP3为+3 dBm,和带外NF范围从3.1至4.1分贝。

结果发现模拟与实测数据非常吻合,归因于与以往的设计相比此电路所需的被动元件数量更少。

此外,电路片的品质因数为190(MW每平方毫米),这在所有先前报道的以CMOS为基础的宽带低噪声放大器(LNA)中是最好的。

关键词CMOS,反馈,低成本,低噪声放大器(LNA),系列调峰,小芯片尺寸,宽带。

一·概述宽带系统最近获得关注是由于其高速的数据传输能力,所谓的超宽带(UWB)技术提供了频率在3.1到10.6 GHz有吸引力的高速无线信号的方案。

为了与天线和预选择滤波器接口匹配,低噪声放大器(LNA)在3.1到10.6 GHz的整个波段的输入阻抗应该接近50Ώ。

到现在为止,已经提出了许多为UWB LNA设计的宽带技术。

分布式放大器(DA)是广泛应用于宽带的技术,由于其固有的宽带频率响应伴随着良好的输入和输出阻抗匹配线性下降到DC。

然而,到目前为止,它的高功耗和芯片面积大,阻碍了其广泛应用[1][2]。

最近一个具有输入带通响应的宽带阻抗匹配的级联CMOS低噪声放大器已被报道[3]。

带通滤波器(BPF)基于拓扑结构采用了级联的输入阻抗放大器作为滤波器的一部分。

然而,在采用的滤波器输入端需要许多电抗性元件,这就不可避免地导致更大的芯片面积和噪声系数(NF)从而造成芯片实现的退化。

一个有效的方式来实现小功耗的宽带匹配和芯片面积为共栅输入拓扑结构。

然而,据报道共栅LNA具有较低的增益和比共源放大器更高的噪声系数[4]。

增益可调超宽带低噪声放大器的开题报告

增益可调超宽带低噪声放大器的开题报告一、选题背景随着科技的不断发展,射频电路对于通信、雷达、导航等应用中的信号处理器件的需求越来越高。

在射频电路中,低噪声放大器(LNA)是一个重要的组成部分,它需要保持着高增益、低噪声和宽频带等特性。

而可调增益的LNA能够实现在不同的场合下,通过调整增益达到最佳性能的要求。

因此,开发一种增益可调、超宽带、低噪声的LNA具有重要的实际意义和应用前景。

二、研究内容本研究旨在设计一种增益可调超宽带低噪声放大器,主要研究内容包括以下几个方面:1. 设计一种高增益、低噪声的放大电路,采用合适的电路拓扑结构来实现。

2. 对于这种放大电路进行参数优化,以获得更高的性能指标。

3. 设计一种增益可调电路,实现对放大电路增益的调整。

4. 将增益可调电路和放大电路组合在一起,并设计出合适的功率分配网络,以实现超宽带的频率响应。

5. 通过电路仿真和实验验证,检验该低噪声放大器的表现。

三、预期成果通过本研究,预期达到以下几个成果:1. 设计出一种增益可调、超宽带低噪声放大器,实现高增益、低噪声、超宽带的特性。

2. 对于设计的放大器进行仿真和实验验证,检验其性能指标,并与同类产品进行比较。

3. 探究增益可调、超宽带低噪声放大器应用于通信、雷达、导航等领域的实际效果。

四、研究意义增益可调、超宽带低噪声放大器在通信、雷达、导航等领域具有重要的应用价值,本研究的开展将有助于:1. 为射频电路技术提供新型的解决方案,推动相关领域的发展。

2. 具有重要的应用前景,进一步发挥现有系统的性能,实现系统整合和功能升级。

3. 推进中国电子产业的发展,增强我国在该领域的竞争力,提高我国在国际射频电路市场上的话语权。

五、研究计划本研究计划分为以下几个阶段:1. 阶段一:研究论文调研和介绍,确定研究方向,制定具体研究计划,制定相关技术规范和标准。

预计研究时间为2周。

2. 阶段二:设计低噪声放大器电路,优化电路参数,初步进行电路仿真。

2.4GHz CMOS全集成低噪声放大器的设计

关键模块 ,它的主要作用是将天线从空 中接收到的 微弱信号进行放大 ,从而有效 的抑制后续电路的噪 声 ,自 身只引入较低 的噪声 ,提高接收信号 的灵敏 度, 以提供系统解调所需要的信息数据。 低噪声放大

器广 泛应用 于宇宙通 讯 、 雷达 、 电子 对抗 、 遥测 遥 控 、

微波通信以及各种高精度 的微波测量系统 , 其噪声 、 线性度和输入输出匹配等性能好坏直接影响到整个 接 收系统 的性能 。

() 2

2 5 H 的中心频率下 , .G z 4 噪声系数为 2 0 d ; 1 . 5 B ¥ 表 6 2

jot t  ̄

j(g ÷ tL L + o +)

= 0

示低 噪声 放 大器 的增 益 , 由图可 以看 出 , 本设 计 的增 益为 2.2d ;1 010 B S 1和 ¥2分别 表 示输 入 、 出端 口 2 输 的匹 配程度 ,输 入反 射 系数 S 达到 一 118B, 1 1 3 . d 输 7

中心 频率 2 5 H 上 。 .G z 4

3 共 源 共栅 低 噪声 放 大 器 的仿 真

在 本 次设计 过 程 中 , 过设 计优 化后 , 经 电路 的 主 约 为 1n 。 2 i 采用 台积 电( S 01 m C S工 l T MC).8 MO 艺 模 型 , 过 A S电路 仿 真 软 件 进 行 仿 真 , 到 仿 通 D 得 真 结果 , 1 V 的电源 电压 下 , 作 电流 约为 6 A, 在 . 8 工 m 噪声 系数 和 J参数 结果如 图 2所示 。 s 在 图 2中 , F为低 噪声 放 大 器 的 噪声 系 数 , N 在

图 1 共源共栅结构低噪声放大器

6 8

CH| V L NA NE v TE EcoM MUNt CAT ONS De e b r o 8 l c m e o 2

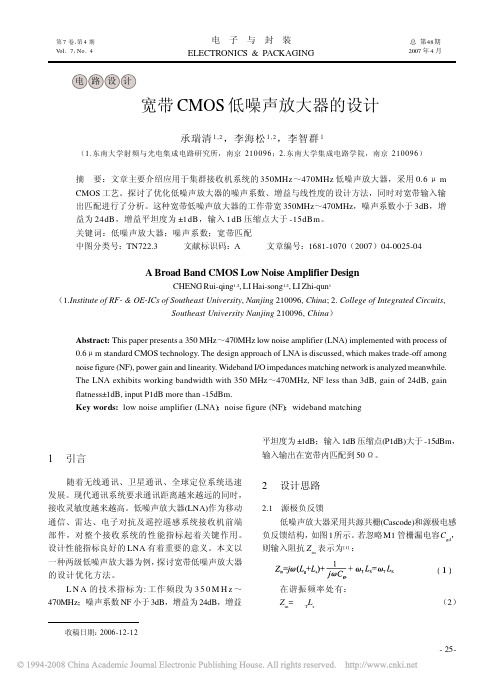

宽带CMOS低噪声放大器的设计

第 7 卷第 4 期

承瑞清,李海松,李智群:宽带 CMOS 低噪声放大器的设计

表1 电路元器件参数

图 4 LNA 电路结构

其中输出 1dB 压缩点为 8.1dBm,输入 1dB 压缩点 为 -14.9dBm。

4 电路仿真结果及分析

本设计采用无锡华润上华 0.6 μ m 工艺模型和 Cadence 仿真工具。 4.1 S 参数分析

第第77卷卷,第第44期期 Vol. 7,No. 4

电子与封装 ELECTRONICS & PACKAGING

电 路 设 计

宽带 CMOS 低噪声放大器的设计

总 第48 期 2007 年 4 月

承瑞清 1,2,李海松 1,2,李智群 1

(1. 东南大学射频与光电集成电路研究所,南京 210 096;2. 东南大学集成电路学院,南京 210 096)

( 1)

在谐振频率处有:

Z =ω L

in

Ts

(2)

收稿日期:2006-12-12

- 25 -

第 7 卷第 4 期

电子与封装

增益和最小输入输出驻波比。在输入匹配过程中采 用无源匹配网络LC La dder宽带滤波器,电感采用 高频电感模型。由于最大增益和最小噪声的要求不 能同时满足,因此实际中需要利用 Smi th圆图对输 人输出、级间匹配网络进行优化。最后在增益、 噪声系数、输入输出驻波比等几项指标中取折衷以 达到最终要求。

[2]C.J.M.Verhoeven . Structured Electronic Design-Negative Feedback Amplifiers[M]. Kluwer Academic Publishers, 2003.

[3]K. van Hartingsveldt. HF Low Noise Amplifiers with Integrated Transformer Feedback[J]. ISCAS,2002,5(2): 815-818.

1.5-6GHz增益和噪声系数稳定的两级超宽带CMOS低噪声放大器设计与性能模拟

1.5-6GHz增益和噪声系数稳定的两级超宽带CMOS低噪声放大器设计与性能模拟何小威;李晋文;张民选【期刊名称】《电子学报》【年(卷),期】2010(038)007【摘要】针对UWB应用设计实现了一个1.5-6GHz的两级CMOS低噪声放大器(LNA).通过引入共栅(CG)和共源(CS)结构以获得宽范围内的输入匹配,采用电流镜和峰化电感进行电流复用,所提出的LNA实现了非常平坦化的功率增益和噪声系数(NF).经标准0.18μm CMOS工艺实现后,版图后模拟结果表明在1.5-5GHz频率范围内功率增益(S21)为11.45±0.05dB,在2-6GHz频率范围内噪声系数(NF)为5.15±0.05dB,输入损耗(S11)小于-18dB.在5GHz时,模拟得到的三阶交调点(IIP3)为-7dBm,1dB压缩点为-5dBm.在1.8V电源电压下,LNA消耗6mA的电流,版图实现面积仅为0.62mm2.【总页数】5页(P1668-1672)【作者】何小威;李晋文;张民选【作者单位】国防科技大学计算机学院并行与分布式处理重点实验室,湖南长沙,410073;国防科技大学计算机学院并行与分布式处理重点实验室,湖南长沙,410073;国防科技大学计算机学院并行与分布式处理重点实验室,湖南长沙,410073【正文语种】中文【中图分类】TN402【相关文献】1.CMOS超宽带低噪声放大器设计难点和要点分析 [J], 石磊;华梦琪;张惠国2.基于3.1~10.6 GHz CMOS超宽带低噪声放大器设计 [J], 赵小荣;范洪辉;朱明放;傅中君;黄海军;陈鉴富3.基于变压器反馈的平坦噪声系数超宽带CMOS低噪声放大器 [J], 吴小平;刘继业;郑士源;吴亮4.3~5 GHz超宽带无电感CMOS低噪声放大器设计 [J], 王巍;宫召英;杨铿;马晓英;唐政维;王岳生5.0.13微米CMOS双通道超宽带低噪声放大器设计 [J], 张弘;梁元因版权原因,仅展示原文概要,查看原文内容请购买。

0.18μm CMOS无线传感器网络低噪声放大器设计及优化的开题报告

0.18μm CMOS无线传感器网络低噪声放大器设计及优化的开题报告【摘要】无线传感网络具有广泛的应用前景,其中低功耗,低噪声放大器是非常重要的组件。

本文提出了一种0.18μm CMOS无线传感器网络低噪声放大器设计及优化的方案。

首先,引入井垒侧壁电容的布局技术,减小了井垒面积,提高了单位面积的输入电容。

接着,通过优化源极偏压与集电极电阻的比例,实现了最佳的功率噪声平衡。

然后,设计了一个基于电压控制电阻的增益控制电路,实现了动态增益控制。

最后,利用TSMC 0.18μm工艺实现了该低噪声放大器,并测试了其性能。

实验结果表明,该低噪声放大器具有68dB的增益,1.2nV/√Hz的输入等效噪声,2.2μA 的静态功耗,以及20nA/mV的动态功耗。

该低噪声放大器的优化方案可以为无线传感器网络中的低功耗前置放大器设计提供参考。

【关键词】无线传感器网络;低噪声放大器;0.18μm CMOS工艺;动态增益控制。

【Abstract】Wireless sensor networks have broad application prospects, and low-power, low-noise amplifiers are critical components. This paper proposes a design and optimization scheme for a low-noise amplifier for 0.18μm CMOS wireless sensor networks. First, the layout technology of the sidewall capacitance of the well is introduced, which reduces the well area and increases the unit area input capacitance. Next, the optimal power noise balance is achieved by optimizing the ratio of the source-drain bias voltage and the collector resistor. Then, a gain control circuit based on voltage-controlled resistors is designed to achieve dynamic gain control. Finally, the low-noise amplifier was implemented using TSMC 0.18μm technology, and its performance was tested. The experimental results show that the low-noise amplifier has a gain of 68dB, an input equivalent noise of 1.2nV/√Hz, a static power consumption of 2.2μA, and a dynamic power consumption of 20nA/mV. The optimization scheme for the low-noise amplifier can provide a reference for the design of low-power preamplifiers in wireless sensor networks.【Keywords】Wireless sensor networks; Low-noise amplifier; 0.18μm CMOS technology; Dynamic gain control.。

一种0.8GHz~6GHz CMOS超宽带低噪声放大器设计

一种0.8GHz~6GHz CMOS超宽带低噪声放大器设计肖奔;邓爱萍

【期刊名称】《电子技术应用》

【年(卷),期】2008(34)12

【摘要】给出了一个针对0.8GHz~6GHz的超宽带低噪声放大器UWB

LNA(ultra-wideband low noise amplifier)设计.设计采用0.18μm RF CMOS工艺完成.在0.8GHz~6GHz的频段内,放大器增益S21达到了17.6dB~13.6dB.输入、输出均实现良好的阻抗匹配,S11、S22均低于-10dB.噪声系数(NF)为

2.7dB~4.6dB.在1.8V工作电压下放大器的直流功耗约为12mW.

【总页数】4页(P57-60)

【作者】肖奔;邓爱萍

【作者单位】湖南人文科技学院,湖南,娄底,417000;湖南人文科技学院,湖南,娄底,417000

【正文语种】中文

【中图分类】TP3

【相关文献】

1.CMOS超宽带低噪声放大器设计难点和要点分析 [J], 石磊;华梦琪;张惠国

2.一种新型超宽带CMOS低噪声放大器设计 [J], 戴彬;陈迪平;刘文用

3.基于3.1~10.6 GHz CMOS超宽带低噪声放大器设计 [J], 赵小荣;范洪辉;朱明放;傅中君;黄海军;陈鉴富

4.3~5 GHz超宽带无电感CMOS低噪声放大器设计 [J], 王巍;宫召英;杨铿;马晓

英;唐政维;王岳生

5.0.13微米CMOS双通道超宽带低噪声放大器设计 [J], 张弘;梁元

因版权原因,仅展示原文概要,查看原文内容请购买。

基于CMOS工艺的超宽带低噪声放大器设计的开题报告

基于CMOS工艺的超宽带低噪声放大器设计的开题报告一、研究背景和意义超宽带(Ultra-WideBand, UWB)是近年来新兴的无线通信技术,其传输带宽一般大于20 MHz,一般以极短脉冲时间间隔传输数据。

UWB技术具有以下优越性:(1)高速传输:UWB技术的传输速度可达到数Gbps,比传统的通信技术(如WLAN、Bluetooth)快上几个数量级。

(2)高保真度:UWB技术具有极好的时域特性,可提供准确可靠的位置和距离信息,适用于高精度定位和跟踪应用。

(3)抗干扰:UWB信号是低功率、短脉冲的宽带信号,干扰产生的能量很小,因此UWB信号不容易被其他无线设备干扰。

低噪声放大器(Low-Noise Amplifier,LNA)作为UWB系统中一项重要且难以实现的关键电路,承担着接收器前端的信号放大和噪声降低的任务。

在UWB系统中,LNA的主要目标是最大限度地提高接收器的灵敏度,并提高传输速率和特征值的信噪比。

此外,LNA还需要尽可能降低功耗、占用面积和成本,以提高整个系统的性能。

基于CMOS工艺的LNA已经成为了UWB通信领域的核心研究方向。

CMOS工艺具有功耗低、占用面积小、成本低等优点,可以满足UWB通信系统对电路设计的要求。

因此,设计一种基于CMOS工艺的超宽带LNA,具有促进新一代UWB无线通信技术发展的重要意义。

二、研究内容和方法本文旨在设计一种基于CMOS工艺的超宽带LNA,并分析其性能表现。

具体研究内容和方法如下:(1)分析UWB系统的要求和LNA的设计指标,建立设计模型。

(2)根据设计模型,利用Cadence软件设计出LNA电路,并进行仿真验证。

该电路包括放大器的结构、调制方式、传输媒介和双平衡混频器(Double Balanced Mixer,DBM)的设计。

(3)根据仿真结果优化LNA电路,进一步提高其性能表现,并进行特性分析。

(4)在TSMC 65nm工艺下进行电路实现,对电路进行测试评估,比较仿真结果和实验结果,验证设计结果的准确性和性能表现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Ke o d : N ( o o eA l e) vr begi ; iea d C S m l-a dt nio yw rs L A L w N i mpi r ; a al a wdbn ; MO ; utgt a s t s i f i n i e r sr s

EEACC :1 2 20

i ot i d b s gmutgt rnios( T .T e d s n o L A c ci i bsd o M C 0 1 m s p m z y ui l - e t s t i e n i a d a s r MG R) h ei f N i ut s ae n S I . 8 g r

o d r B t r o t l r sa o td t c iv x eln n u th a d o t u th i e cr u t o t u l u a r e u t w r f t d p e a h e ee c l t p t e hi e i o e i mac n u p t ma c t i i n h c .A c n i a t n — n b e a l e i w t g s c s o ei r p s d b o t l n h u r n ft e s c n tg .T e l e r y o N l mp i rw t t o s e a c d p o o e y c n r l g t e c r t e o d sa e h i ai f A i f h a s oi e o h n t L

匹配 电 路 ; 采用 了两 级 共 源共 栅 结 构实 现 电路 的放 大 , 通 过控 制 第 二 级 的 电流 , 现 了在 宽 频 带 范 围 内 增 益 连 续 可 调 ; 用 了 并 实 采

多栅管( G R)提高了电路 的线性度 ; M T , 设计基于 S C0 1 m C O MI .8 M S工艺 。仿真结果显示 , 在频带 3— H 5G z的范围内最高增 益 1 B, 益波动小于 18d , 7d 增 . B 输入和输 出端 口反射 系数分别小于 一1 B和 一1 B 噪声系数 n 小于 3 5d 当控制电压 V Od 4d , f . B,

p o e s h e s ltd rs l h w t a h jh s g i s 1 B,t e g i u t ain i l s a . B,S l n r c s .T i a e e u t s o t e h g e t an i 7 d mu s h t h an f cu t s e s t n 1 8 d l o h Ia d

第3 3卷 第 2期

21 00年 4月

电 子 器 件

C iee Ju n l fE e t n D vc s h n s o r a lc o e ie o r

V0 _ 3 No 2 l3 .

Ap .2 0 r 01

De i n o ra l i i e a d CM OS LNA sg f Va i b e Ga n W d b n

=14V时 , P 为 2d m, . I 3约 I B 电路 功耗 为 1 W 。 6m

关键词 : 低噪声放大器(N )增益可调 ; ;MБайду номын сангаасS多栅管 LA ; 宽带 C O ;

中图分类号 : N T 4

文献标 识码 : A

文章编 号 :05— 40 2 1 )2— 18— 4 10 9 9 (0 0 0 0 7 0 宽带 范 围内实现 连续 增 益 可调 低 噪 声放 大 器 , 过 通

C E hq n H NGZ iu ,

K iog L i, HO 咖 ah n , 1 n Z U J

( e a F Crut n yt , nsyo dct n H nzo a z U i rt, aghu30 1 , hn KyLbo fR i iadSs r Miir c e n t fE uai , aghuDi i nv sy H nzo 10 8 C i o n ei a)

S2 a e l s h n 一1 B n 一1 B epe tv l 2 r e s t a 0d ad 4 d r s cie y,n ie fg r sl s h n 3. B,IP3 i b u Bm tc n os u e i e st a 5 d i I sa o t2 d a o - to ld v l g t o . a h r q e c r m r l — ot e V l f1 4 V tt e fe u n y fo 3 GHz t e a o5 GHz h e p we o s mp in i 6 mW . .T o rc n u t s 1 o

Abtat A vr begi wd bn N V s c: a a l an i adL A( G— N r i e L A)i d s ndf laWiea dS s m a pi t n T eto s ei e r t db n yt p l a o . h — g oU r e ci w

增 益可调 宽带 C O M S低 噪 声 放 大 器 设 计 木

程知群 , 傅开红, 进 , 李 周云芳

( 杭州电子科技大学 , 射频电路与系统教育部重点实验室 , 杭州 30 1 ) 10 8

摘 要 : 了一种应用于超宽带系统 中的可变增益宽带低噪声放大器。电路 中采用 了二阶巴特沃斯滤波器作为输人和输 出 设计