串口电平转换芯片数据手册SP3222_3232E

DESCRIPTION

s Meets true EIA/TIA-232-F Standards from a +3.0V to +5.5V power supply

s 235KBps Transmission Rate Under Load s 1μA Low-Power Shutdown with Receivers Active (SP3222E )

s Interoperable with RS-232 down to +2.7V power source

s Enhanced ESD Specifications: ±15kV Human Body Model

±15kV IEC1000-4-2 Air Discharge ±8kV IEC1000-4-2 Contact Discharge

The SP3222E/3232E series is an RS-232 transceiver solution intended for portable or hand-held applications such as notebook or palmtop computers. The SP3222E/3232E series has a high-efficiency, charge-pump power supply that requires only 0.1μF capacitors in 3.3V operation. This charge pump allows the SP3222E/3232E series to deliver true RS-232performance from a single power supply ranging from +3.3V to +5.0V. The SP3222E/3232E are 2-driver/2-receiver devices. This series is ideal for portable or hand-held applications such as notebook or palmtop computers. The ESD tolerance of the SP3222E/3232E devices are over ±15kV for both Human Body Model and IEC1000-4-2 Air discharge test methods. The SP3222E device has a low-power shutdown mode where the devices' driver outputs and charge pumps are disabled. During shutdown, the supply current falls to less than 1μA.

SELECTION TABLE

L E D O M s e i l p p u S r e w o P 232-S R s r D e v i r 232-S R s

r e v i e c e R l a n r e t x E s

t n e n o p m o C n

w o d t u h S L T T a S -3e t t f o .o N s n i P 2223P S V 5.5+o t V 0.3+224s e Y s e Y 02,812

323P S V

5.5+o t V 0.3+2

2

4

o

N o

N 6

1

R

E T E M A R A P .

N I M .

P Y T .

X A M S

T I N U S

N O I T I D N O C S C I T S I R E T C A R A H C C D t

n e r r u C y l p p u S 3.00.1A m T ,d a o l o n B M A 52+=o V ,C C C V 3.3=t

n e r r u C y l p p u S n w o d t u h S 0

.10

1μA

,D N G =N D H S T B M A 52+=o V ,C C C V

3.3+=S T U P T U O R E V I E C E R D N A S T U P N I C I G O L W O L d l o h s e r h T c i g o L t u p n I 8

.0V 2e t o N ,N D H S ,N E ,N I x T H G I H d l o h s e r h T c i g o L t u p n I 0.24

.2V V C C 2e t o N ,V 3.3=V C C 2

e t o N ,V 0.5=t n e r r u C e g a k a e L t u p n I 10.0±0.1±μA ,N D H S ,N E ,N I x T T B M A 52+=o C t n e r r u C e g a k a e L t u p t u O 5

0.0±01±μA d e l b a s i d s r e v i e c e r W O L e g a t l o V t u p t u O 4.0V I T U O A m 6.1=H G I H e g a t l o V t u p t u O V C C 6

.0-V C C 1

.0-V

I T U O A

m 0.1-=S T U P T U O R E V I R D g

n i w S e g a t l o V t u p t u O 0

.5±4

.5±V

k 3?,s t u p t u o r e v i r d l l a t a d n u o r g o t d a o l T B M A 52+=o C

e

c n a t s i s e R t u p t u O 0

03?V C C T ,V 0=-V =+V =T U O =+V 2t n e r r u C t i u c r i C -t r o h S t u p t u O 53±0

7±06±001±A m A m V T U O V 0=V T U O =+V

51t

n e r r u C e g a k a e L t u p t u O 5

2±μA

V T U O =+V ,V 21C C d

e l b a s i d s r e v i r d ,V 5.5o t V 0=NOTE 1: V+ and V- can have maximum magnitudes o

f 7V, but their absolute difference cannot exceed 13V.

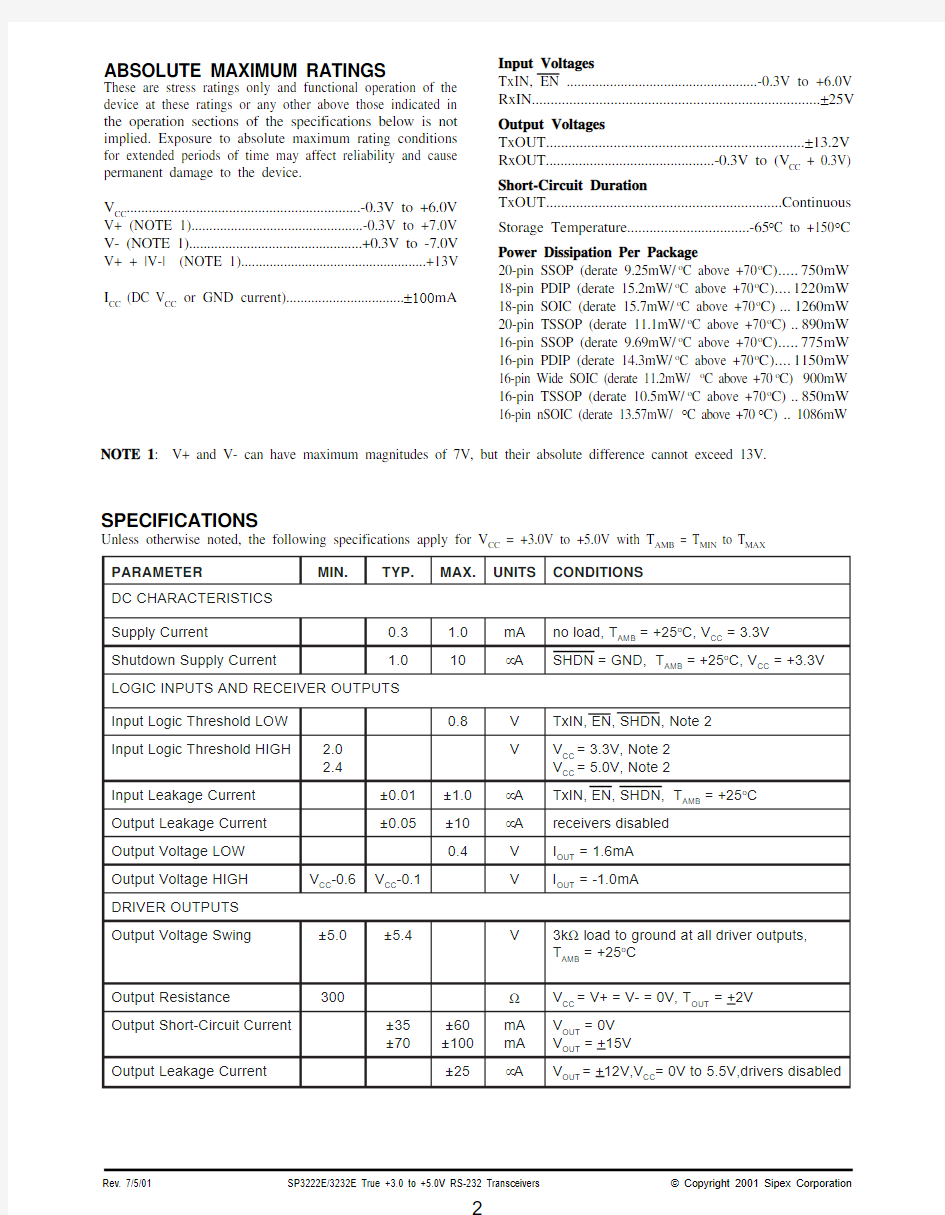

ABSOLUTE MAXIMUM RATINGS

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the device.

V CC ................................................................-0.3V to +6.0V V+ (NOTE 1)................................................-0.3V to +7.0V V- (NOTE 1)................................................+0.3V to -7.0V V+ + |V-| (NOTE 1)....................................................+13V I CC (DC V CC or GND current).................................±100mA

Input Voltages

TxIN, EN .....................................................-0.3V to +6.0V RxIN.............................................................................±25V Output Voltages

TxOUT.....................................................................±13.2V RxOUT..............................................-0.3V to (V CC + 0.3V)Short-Circuit Duration

TxOUT...............................................................Continuous Storage Temperature.................................-65°C to +150°C Power Dissipation Per Package

20-pin SSOP (derate 9.25mW/o C above +70o C).....750mW 18-pin PDIP (derate 15.2mW/o C above +70o C)....1220mW 18-pin SOIC (derate 15.7mW/o C above +70o C)...1260mW 20-pin TSSOP (derate 11.1mW/o C above +70o C)..890mW 16-pin SSOP (derate 9.69mW/o C above +70o C).....775mW 16-pin PDIP (derate 14.3mW/o C above +70o C)....1150mW 16-pin Wide SOIC (derate 11.2mW/o C above +70o C)900mW 16-pin TSSOP (derate 10.5mW/o C above +70o C)..850mW 16-pin nSOIC (derate 13.57mW/°C above +70°C)..1086mW

SPECIFICATIONS

Unless otherwise noted, the following specifications apply for V CC = +3.0V to +5.0V with T AMB = T MIN to T MAX

R E T E M A R A P .

N I M .

P Y T .

X A M S

T I N U S

N O I T I D N O C S T U P N I R E V I E C E R e g n a R e g a t l o V t u p n I 51-5

1+V W O L d l o h s e r h T t u p n I 6.08

.02.15.1V V C C V 3.3=V C C V 0.5=H G I H d l o h s e r h T t u p n I 5.18.14.24.2V V C C V 3.3=V C C V

0.5=s i s e r e t s y H t u p n I 3.0V e

c n a t s i s e R t u p n I 35

7k ?

S C I T S I R E T C A R A H C G N I M I T e t a R a t a D m u m i x a M 0

21532s p b k R L k 3=?C ,L g n i h c t i w s r e v i r d e n o ,F p 0001=y a l e D n o i t a g a p o r P r e v i r D 0.10.1μs μs t L H P R ,L K 3=?C ,L F p 0001=t H L P R ,L K 3=?C ,L F p 0001=y a l e D n o i t a g a p o r P r e v i e c e R 3.03.0μs t L H P C ,T U O x R o t N I x R ,L F p 051=t H L P C ,T U O x R o t N I x R ,L F

p 051=e m i T e l b a n E t u p t u O r e v i e c e R 002s n e m i T e l b a s i D t u p t u O r e v i e c e R 002s n w e k S r e v i r D 001005s n t |L H P t -H L P T ,|B M A 52=o C w

e k S r e v i e c e R 0

020001s n t |L H P t -H L P |

e

t a R w e l S n o i g e R -n o i t i s n a r T 0

3/V μs

V C C R ,V 3.3=L K 3=?T ,B M A 52=o ,

C V 0.3+o t V 0.3-m o r f n e k a t s t n e m e r u s a e m V

0.3-o t V 0.3+r o SPECIFICATIONS (continued)

Unless otherwise noted, the following specifications apply for V CC = +3.0V to +5.0V with T AMB = T MIN to T MAX .Typical Values apply at V CC = +3.3V or +5.0V and T AMB = 25o C.

NOTE 2: Driver input hysteresis is typically 250mV.

Capacitance for the SP3222 and the SP3232SP3222 and the SP3232

Transmitting Data for the SP3222 and the SP3232

TYPICAL PERFORMANCE CHARACTERISTICS

Unless otherwise noted, the following performance characteristics apply for V CC = +3.3V, 235kbps data rates, all drivers loaded with 3k ?, 0.1μF charge pump capacitors, and T AMB = +25°C.

DESCRIPTION

The SP3222E/3232E transceivers meet the EIA/TIA-232 and V.28/V.24 communication proto-cols and can be implemented in battery-pow-ered, portable, or hand-held applications such as notebook or palmtop computers. The SP3222E/3232E devices all feature Sipex's proprietary on-board charge pump circuitry that generates 2x V CC for RS-232 voltage levels from a single +3.0V to +5.5V power supply. This series is ideal for +3.3V-only systems, mixed +3.3V to +5.5V systems, or +5.0V-only systems that re-quire true RS-232 performance. The SP3222E/3232E series have drivers that operate at a typi-cal data rate of 235Kbps fully loaded.The SP3222E and SP3232E are 2-driver/2-re-ceiver devices ideal for portable or hand-held applications. The SP3222E features a 1μA shutdown mode that reduces power consump-tion and extends battery life in portable systems.Its receivers remain active in shutdown mode,allowing external devices such as modems to be monitored using only 1μA supply current.THEORY OF OPERATION

The SP3222E/3232E series are made up of three basic circuit blocks: 1. Drivers, 2. Receivers,and 3. the Sipex proprietary charge pump.Drivers

The drivers are inverting level transmitters that convert TTL or CMOS logic levels to ±5.0V EIA/TIA-232 levels inverted relative to the in-put logic levels. Typically, the RS-232 output voltage swing is ±5.5V with no load and at least ±5V minimum fully loaded. The driver outputs are protected against infinite short-circuits to ground without degradation in reliability. Driver outputs will meet EIA/TIA-562 levels of ±3.7V with supply voltages as low as 2.7V.

The drivers typically can operate at a data rate of 235Kbps. The drivers can guarantee a data rate of 120Kbps fully loaded with 3K ? in parallel with 1000pF, ensuring compatibility with PC-to-PC communication software.

The slew rate of the driver output is internally limited to a maximum of 30V/μs in order to meet the EIA standards (EIA RS-232D 2.1.7, Para-graph 5). The transition of the loaded output from HIGH to LOW also meets the monotonic-ity requirements of the standard.

The SP3222E/3232E drivers can maintain high data rates up to 240Kbps fully loaded. Figure 8shows a loopback test circuit used to test the RS-232 drivers. Figure 9 shows the test results of the loopback circuit with all drivers active at 120Kbps with RS-232 loads in parallel with 1000pF capacitors. Figure 10 shows the test results where one driver was active at 235Kbps and all drivers loaded with an RS-232 receiver in parallel with a 1000pF capacitor. A solid RS-232 data transmission rate of 120Kbps provides compatibility with many designs in personal computer peripherals and LAN applications.

The SP3222E driver's output stages are turned off (tri-state) when the device is in shutdown mode. When the power is off, the SP3222E device permits the outputs to be driven up to ±12V. The driver's inputs do not have pull-up resistors. Designers should connect unused inputs to V CC or GND.

In the shutdown mode, the supply current falls to less than 1μA, where SHDN = LOW. When the SP3222E device is shut down, the device's driver outputs are disabled (tri-stated) and the charge pumps are turned off with V+ pulled down to V CC and V- pulled to GND. The time required to exit shutdown is typically 100μs.Connect SHDN to V CC if the shutdown mode is RxOUTB. As they become active, the two driver outputs go to opposite RS-232 levels where one driver input is HIGH and the other LOW. Note that the drivers are enabled only when the magnitude of V- exceeds approximately 3V.

Receivers

The receivers convert EIA/TIA-232 levels to TTL or CMOS logic output levels. All receivers have an inverting tri-state output. These receiver outputs (RxOUT) are tri-stated when the enable control EN = HIGH. In the shutdown mode, the receivers can be active or inactive. EN has no effect on TxOUT. The truth table logic of the SP3222E/3232E driver and receiver outputs can be found in Table 2.

Since receiver input is usually from a transmis-sion line where long cable lengths and system interference can degrade the signal, the inputs have a typical hysteresis margin of 300mV. This ensures that the receiver is virtually immune to noisy transmission lines. Should an input be left unconnected, a 5k ? pulldown resistor to ground will commit the output of the receiver to a HIGH state.

Charge Pump

The charge pump is a Sipex –patented design (5,306,954) and uses a unique approach com-pared to older less–efficient designs. The charge pump still requires four external capacitors, but uses a four–phase voltage shifting technique to attain symmetrical 5.5V power supplies. The internal power supply consists of a regulated dual charge pump that provides output voltages 5.5V regardless of the input voltage (V CC ) over the +3.0V to +5.5V range.

In most circumstances, decoupling the power supply can be achieved adequately using a 0.1μF bypass capacitor at C5 (refer to Figures 6 and 7).In applications that are sensitive to power-sup-ply noise, decouple V CC to ground with a capaci-tor of the same value as charge-pump capacitor C1. Physically connect bypass capacitors as close to the IC as possible.

The charge pumps operate in a discontinuous mode using an internal oscillator. If the output voltages are less than a magnitude of 5.5V, the charge pumps are enabled. If the output voltage exceed a magnitude of 5.5V, the charge pumps are disabled. This oscillator controls the four phases of the voltage shifting. A description of each phase follows.

Phase 1

— V SS charge storage — During this phase of the clock cycle, the positive side of capacitors C 1and C 2 are initially charged to V CC . C l + is then switched to GND and the charge in C 1– is trans-ferred to C 2–. Since C 2+ is connected to V CC , the voltage potential across capacitor C 2 is now 2times V CC .

Phase 2

— V SS transfer — Phase two of the clock con-nects the negative terminal of C 2 to the V SS storage capacitor and the positive terminal of C 2to GND. This transfers a negative generated voltage to C 3. This generated voltage is regu-lated to a minimum voltage of -5.5V. Simulta-neous with the transfer of the voltage to C 3, the positive side of capacitor C 1 is switched to V CC and the negative side is connected to GND.Phase 3

— V DD charge storage — The third phase of the clock is identical to the first phase — the charge transferred in C 1 produces –V CC in the negative terminal of C 1, which is applied to the negative side of capacitor C 2. Since C 2+ is at V CC , the voltage potential across C 2 is 2 times V CC .

Table 2. Truth Table Logic for Shutdown and Enable Control

N D H S N E T U O x T T U O x R 00e t a t s -i r T e v i t c A 01e t a t s -i r T e t a t s -i r T 10e v i t c A e v i t c A 1

1

e

v i t c A e

t a t s -i r T

Phase 4

— V DD transfer — The fourth phase of the clock connects the negative terminal of C 2 to GND,and transfers this positive generated voltage across C 2 to C 4, the V DD storage capacitor. This voltage is regulated to +5.5V. At this voltage,the internal oscillator is disabled. Simultaneous with the transfer of the voltage to C 4, the positive side of capacitor C 1 is switched to V CC and the negative side is connected to GND, allowing the charge pump cycle to begin again. The charge pump cycle will continue as long as the opera-tional conditions for the internal oscillator are present.

Since both V + and V – are separately generated from V CC ; in a no–load condition V + and V – will be symmetrical. Older charge pump approaches that generate V – from V + will show a decrease in the magnitude of V – compared to V + due to the inherent inefficiencies in the design.

The clock rate for the charge pump typically operates at 250kHz. The external capacitors can be as low as 0.1μF with a 16V breakdown voltage rating.ESD Tolerance

The SP3222E/3232E series incorporates ruggedized ESD cells on all driver output and receiver input pins. The ESD structure is improved over our previous family for more rugged applications and environments sensitive to electro-static discharges and associated transients. The improved ESD tolerance is at least ±15kV without damage nor latch-up.There are different methods of ESD testing applied:

a) MIL-STD-883, Method 3015.7b) IEC1000-4-2 Air-Discharge c) IEC1000-4-2 Direct Contact The Human Body Model has been the generally accepted ESD testing method for semiconduc-tors. This method is also specified in MIL-STD-883, Method 3015.7 for ESD testing. The premise of this ESD test is to simulate the human body’s

potential to store electro-static energy and discharge it to an integrated circuit. The simulation is performed by using a test model as shown in Figure 17. This method will test the IC’s capability to withstand an ESD transient during normal handling such as in manufacturing areas where the ICs tend to be handled frequently.

The IEC-1000-4-2, formerly IEC801-2, is generally used for testing ESD on equipment and systems. For system manufacturers, they must guarantee a certain amount of ESD protection since the system itself is exposed to the outside environment and human presence.The premise with IEC1000-4-2 is that the system is required to withstand an amount of static electricity when ESD is applied to points and surfaces of the equipment that are accessible to personnel during normal usage.The transceiver IC receives most of the ESD current when the ESD source is applied to the connector pins. The test circuit for IEC1000-4-2is shown on Figure 18. There are two methods within IEC1000-4-2, the Air Discharge method and the Contact Discharge method.

With the Air Discharge Method, an ESD voltage is applied to the equipment under test (EUT) through air. This simulates an electrically charged person ready to connect a cable onto the rear of the system only to find an unpleasant zap just before the person touches the back panel. The high energy potential on the person discharges through an arcing path to the rear panel of the system before he or she even touches the system. This energy, whether discharged directly or through air, is predominantly a function of the discharge current rather than the discharge voltage.Variables with an air discharge such as approach speed of the object carrying the ESD potential to the system and humidity will tend to change the discharge current. For example, the rise time of the discharge current varies with the approach speed.

Figure 14. Charge Pump Waveforms

The Contact Discharge Method applies the ESD current directly to the EUT. This method was devised to reduce the unpredictability of the ESD arc. The discharge current rise time is constant since the energy is directly transferred without the air-gap arc. In situations such as hand held systems, the ESD charge can be directly discharged to the equipment from a person already holding the equipment. The current is transferred on to the keypad or the serial port of the equipment directly and then travels through the PCB and finally to the IC.The circuit models in Figures 17 and 18 represent the typical ESD testing circuits used for all three methods. The C S is initially charged with the DC power supply when the first switch (SW1) is on. Now that the capacitor is charged, the second switch (SW2) is on while SW1 switches off. The voltage stored in the capacitor is then applied through R S, the current limiting resistor, onto the device under test (DUT). In ESD tests, the SW2 switch is pulsed so that the device under test receives a duration of voltage.

Figure 17. ESD Test Circuit for Human Body Model

Figure 18. ESD Test Circuit for IEC1000-4-2

Figure 19. ESD Test Waveform for IEC1000-4-2

30A

I ¥

0A

15A

t=30ns

t ¥

t=0ns

For the Human Body Model, the current limiting resistor (R S ) and the source capacitor (C S ) are 1.5k ? an 100pF, respectively. For IEC-1000-4-2, the current limiting resistor (R S )and the source capacitor (C S ) are 330? an 150pF,respectively.

The higher C S value and lower R S value in the IEC1000-4-2 model are more stringent than the Human Body Model. The larger storage capacitor injects a higher voltage to the test point when SW2 is switched on. The lower current limiting resistor increases the current charge onto the test point.

Device Pin Human Body IEC1000-4-2

Tested Model Air Discharge Direct Contact Level

Driver Outputs ±15kV ±15kV ±8kV 4Receiver Inputs ±15kV

±15kV

±8kV

4

Table 3. Transceiver ESD Tolerance Levels

PACKAGE:PLASTIC SHRINK

PACKAGE:PLASTIC

DUAL–IN–LINE (NARROW)

PACKAGE:PLASTIC

PACKAGE:PLASTIC

SMALL OUTLINE (SOIC)(NARROW)

DIMENSIONS

in inches (mm) Minimum/Maximum Symbol16 Lead20 Lead D0.193/0.2010.252/0.260

(4.90/5.10)(6.40/6.60)

e0.026 BSC0.026 BSC

(0.65 BSC)(0.65 BSC)PACKAGE:PLASTIC THIN

SMALL OUTLINE

(TSSOP)

ORDERING INFORMATION

Model Temperature Range Package Type SP3222ECA.............................................0?C to +70?C..........................................20-Pin SSOP SP3222ECP.............................................0?C to +70?C............................................18-Pin PDIP SP3222ECT.............................................0?C to +70?C...........................................18-Pin SOIC SP3222ECY.............................................0?C to +70?C........................................20-Pin TSSOP SP3222EEA............................................-40?C to +85?C........................................20-Pin SSOP SP3222EEP............................................-40?C to +85?C..........................................18-Pin PDIP SP3222EET............................................-40?C to +85?C.........................................18-Pin SOIC SP3222EEY............................................-40?C to +85?C......................................20-Pin TSSOP SP3232ECA.............................................0?C to +70?C..........................................16-Pin SSOP SP3232ECP.............................................0?C to +70?C............................................16-Pin PDIP SP3232ECT.............................................0?C to +70?C..................................16-Pin Wide SOIC SP3232ECN.............................................0?C to +70?C.........................................16-Pin nSOIC SP3232ECY.............................................0?C to +70?C........................................16-Pin TSSOP SP3232EEA............................................-40?C to +85?C........................................16-Pin SSOP SP3232EEP............................................-40?C to +85?C..........................................16-Pin PDIP SP3232EET............................................-40?C to +85?C................................16-Pin Wide SOIC SP3232EEN............................................-40?C to +85?C.......................................16-Pin nSOIC SP3232EEY............................................-40?C to +85?C......................................16-Pin TSSOP

MAX232芯片可以完成TTL与EIA双向电平转换

TTL/CMOS INPUTS 端.这个端口是的作用是输入TLL或CMOS信号的...一般为0-5V... 低电平为零,高电平为VCC. TTL/CMOS OUTPUTS端,这个端口的作用是输出TLL或CMOS信号...输出电压一般为0-5V...低电平为零..高电平为VCC. RS232 OUTPUTS 这端口是把TTL或CMOS的信号转为RS232的信号输出...输出为正负12V...到电脑.... RS232 INPUTS 这个端口是接收到电脑发出的正负12伏...由232输出转为TTL或CMOS信号...这个信号也为正负12V... MAX232内部有二组232转换电路... 使用的时候...一般是11------ 14 13----12为一组. 10-----7 8----9为一组... 51单片机要与PC机进行串口通信,通常使用MAX232芯片来作电平转换。下面把MAX232与51单片机的接口电路贴出来供大家参考。(此电路图已经过实际验证) MAX232芯片可以完成TTL与EIA双向电平转换,MAX232提供两路串口电平转换,现在只用一路串口,所以另一路悬空不使用,MAX232与51单片机接口电路如下图所示。(单击图片可放大)

图中DB9为串口的插头(母接头),插座共有9个引线. MAX232的12脚接单片机的P3.0(RXD) MAX232的12脚接单片机的P3.1(TXD) MAX232还带有4个电容,都是容量都是104,为了减少电路板体积,可以用无极电容代替极性电容。 VCC 是5V DC 提示:串口插座有公母两种类型其中 公的串口插座是带有插针的(有针) 母的串口插座是不带有插针的(有洞) 如下图所示 由以上分析可知,DB9为母接头,而电脑PC的串口接头一般是分接头。 所以此电路与PC相连时,所用的串口线应该是一公一母的串口线。TTL电平信号被利用的最多是因为通常数据表示采用二进制规定,+5V等价于逻辑"1",0V等价于逻辑"0",这被称做TTL(晶体管-晶体管逻辑电平)信号系统,这是计算机处理器控制的设备内部各部分之间通信的标准技术。 TTL电平信号对于计算机处理器控制的设备内部的数据传输是很理想的,首先计算机处理器控制的设备内部的数据传输对于电源的要求不高以及热损耗也较低,另外TTL 电平信号直接与集成电路连接而不需要价格昂贵的线路驱动器以及接收器电路;再者,计算机处理器控制的设备内部的数据传输是在高速下进行的,而TTL接口的操作恰能满足这个要求。TTL型通信大多数情况下,是采用并行数据传输方式,而并行数据传输对于超过10英尺的距离就不适合了。这是由于可靠性和成本两面的原因。因为在并行接口中存在着偏相和不对称的问题,这些问题对可靠性均有影响;另外对于并行数据传输,电缆以及连接器的费用比起串行通信方式来也要高一些。

详解电平种类与电平转换

详解电平种类与电平转换 1. 常用的电平转换方案 (1) 晶体管+上拉电阻法 就是一个双极型三极管或 MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。 (2) OC/OD 器件+上拉电阻法 跟 1) 类似。适用于器件输出刚好为 OC/OD 的场合。 (3) 74xHCT系列芯片升压(3.3V→5V) 凡是输入与 5V TTL 电平兼容的 5V CMOS 器件都可以用作3.3V→5V电平转换。 ——这是由于 3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而 CMOS 的输出电平总是接近电源电平的。 廉价的选择如 74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列 (那个字母 T 就表 示 TTL 兼容)。 (4) 超限输入降压法(5V→3.3V,3.3V→1.8V, ...) 凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。 这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制 (改变了输入级保护电路)。 例如,74AHC/VHC 系列芯片,其 datasheets 明确注明"输入电压范围为0~5.5V",如果采 用 3.3V 供电,就可以实现5V→3.3V电平转换。 (5) 专用电平转换芯片 最著名的就是 164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的 (俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。 (6) 电阻分压法 最简单的降低电平的方法。5V电平,经1.6k+3.3k电阻分压,就是3.3V。 (7) 限流电阻法 如果嫌上面的两个电阻太多,有时还可以只串联一个限流电阻。某些芯片虽然原则上不允许输入电平超过电源,但只要串联一个限流电阻,保证输入保护电流不超过极限(如 74HC 系列为 20mA),仍然是安全的。 (8) 无为而无不为法 只要掌握了电平兼容的规律。某些场合,根本就不需要特别的转换。例如,电路中用到了某种 5V 逻辑器件,其输入是 3.3V 电平,只要在选择器件时选择输入为 TTL 兼容的,就不需要任何转换,这相当于隐含适用了方法3)。

串口电平转换芯片数据手册SP3222_3232E

DESCRIPTION s Meets true EIA/TIA-232-F Standards from a +3.0V to +5.5V power supply s 235KBps Transmission Rate Under Load s 1μA Low-Power Shutdown with Receivers Active (SP3222E ) s Interoperable with RS-232 down to +2.7V power source s Enhanced ESD Specifications: ±15kV Human Body Model ±15kV IEC1000-4-2 Air Discharge ±8kV IEC1000-4-2 Contact Discharge The SP3222E/3232E series is an RS-232 transceiver solution intended for portable or hand-held applications such as notebook or palmtop computers. The SP3222E/3232E series has a high-efficiency, charge-pump power supply that requires only 0.1μF capacitors in 3.3V operation. This charge pump allows the SP3222E/3232E series to deliver true RS-232performance from a single power supply ranging from +3.3V to +5.0V. The SP3222E/3232E are 2-driver/2-receiver devices. This series is ideal for portable or hand-held applications such as notebook or palmtop computers. The ESD tolerance of the SP3222E/3232E devices are over ±15kV for both Human Body Model and IEC1000-4-2 Air discharge test methods. The SP3222E device has a low-power shutdown mode where the devices' driver outputs and charge pumps are disabled. During shutdown, the supply current falls to less than 1μA. SELECTION TABLE L E D O M s e i l p p u S r e w o P 232-S R s r D e v i r 232-S R s r e v i e c e R l a n r e t x E s t n e n o p m o C n w o d t u h S L T T a S -3e t t f o .o N s n i P 2223P S V 5.5+o t V 0.3+224s e Y s e Y 02,812 323P S V 5.5+o t V 0.3+2 2 4 o N o N 6 1

电平转换方法

5V-3.3V电平转换方法 在实际电路设计中,一个电路中会有不同的电平信号。 方案一:使用光耦进行电平转换 首先要根据要处理的信号的频率来选择合适的光耦。高频(20K~1MHz)可以用高速带放大整形的光藕,如6N137/TLP113/TLP2630/4N25等。如果是20KHz以下可用TLP521。然后搭建转换电路。如将3.3V信号转换为5V信号。电路如下图: CP是3.3V的高速信号,通过高速光耦6N137转换成5V信号。如果CP接入的是5V 的信号VCC=3.3V,则该电路是将5V信号转换成3.3V信号。优点:电路搭建简单,可以调制出良好的波形,另外光耦还有隔离作用。缺点:对输入信号的频率有一定的限制。 方案二:使用三极管搭建转换电路 三极管的开关频率很高,一般都是几百兆赫兹,但是与方案一相比,电路搭建相对麻烦,而且输出的波形也没有方案一的好。 电路如下图: 其中C1为加速电容,R1为基极限流电阻,R2为集电极上拉电阻,R3将输入端下拉到地,保证在没有输入的情况下,输出端能稳定输出高电平。同时在三极管截止时给基区过量的电荷提供泄放回路缩短三极管的退饱和时间。 优点:开关频率高,在不要求隔离,考虑性价比的情况下,此电路是很好的选择。 缺点:输出波形不是很良好。 方案三:电阻分压 这里分析TTL电平和COMS电平的转换。首先看一下TTL电平和CMOS电平的区别。 TTL电平:输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2。最小输入高电平>=2.0V,输入低电平<=0.8,噪声容限是0.4V。 CMOS电平:1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。而且有很宽的噪声容限。 下面的电路是将5V的TTL电平转换成3V的TTL电平

常见TTL电平转换电路

常见TTL电平转换电路 ------设计参考 1.二、三级管组成的TTL/CMOS电平转换电路,优点是价格非常低,缺点是要求使用在 信号频率较低的条件下。 建议上拉电阻为10K时,可使用在信号频率为几百Khz以下的环境中,曾经在960Khz 的串口通信中做过测试。上拉电阻越小,速率越高,但是电路的功耗也越高,在低功耗要求高的电路中需要慎重考虑。在选择二、三极管时,尽量选用结电容小,开关速率高的。 A ) 图1所示电路,仅能使用在输入信号电平大于输出信号电平的转换上,例如3.3V转2.8V。二极管选用高速肖特基二极管,并且V F尽量小,例如RB521S。 图1 B ) 图2电路,仅能使用在输入信号电平大于输出信号电平的转换上,例如3.3V转2.8V,否则PNP管可能关不断。如果对输出低电平电压幅度有较严格的要求,PNP管则选用饱和压降小些的管子。PNP管也不如NPN的通用。VCC_OUT是输出信号的电源电压。 图2

C ) 图3是NPN管组成的转换电路,对输入和输出电平的谁高谁低没有要求,适用性很好。其中VCC_IN是输入信号的电源电压,VCC_OUT是输出信号的电源电压。转换后输出的低电平VOL=Vin_Lmax+Vsat,Vin_Lmax为输入信号低电平的最高幅值,Vsat为NPN管的饱和压降,如果对输出低电平电压幅度有较严格的要求,NPN管则选用饱和压降小些的管子,以满足一般电路中VOL<0.8V的要求。 图3 2.OC/OD输出的反相器组成的电平转换电路。 图4,由2级反相器组成,反相器必须是OC/OD输出的。反相器的电源与输入信号的电平相同或者相匹配,最后的输出电平由上拉电阻上拉到输出信号的目标电平上。上拉电阻的取值直接影响功耗和可适用的信号频率。 图4

选择正确的电平转换方案英文

Application Report SCEA044–June2010 A Guide to Voltage Translation With TXS-Type Translators Dave Moon,Aeysha Sultana High Volume Linear ABSTRACT Modern trends are driving the need for lower supply voltages across many system-level designs.As most processor voltage levels continue to decrease in the interest of achieving the lowest possible power consumption,peripheral devices maintain a need for higher voltage levels,creating potential for voltage discontinuities within a system.To remedy this mixed voltage system incompatibility,a voltage translator can be used. Texas Instruments High Volume Linear group offers a wide-range of voltage level translators.A variety of architectures provide solutions for different application environments including dual-supply direction-controlled,auto-direction sensing,and application-specific memory card interface translators. The information in this application report is intended to help system designers understand the architecture and operation of the TXS-type auto-direction sensing translator family Contents 1The Need For Voltage-Level Translation (2) 2Auto-Direction Sensing Voltage Translator Architecture (2) 3Input Driver Requirements With TXS-Type Translators (6) 4Driving External Loads With TXS-Type Translators (7) 5Output Enable Control (7) 6Conclusion (7) List of Figures 1Digital Switching Levels (2) 2Basic TXS0101,TXS0102,and TXS0104Architecture (3) 3Transfer Characterisitics of an N-Channel Transistor (3) 4Basic TXS0108E Architecture (4) 5TXS0108E During Low-to-High Signal Transition (5) 6TXS0108E During High-to-Low Signal Transition (6) 1 SCEA044–June2010A Guide to Voltage Translation With TXS-Type Translators Copyright?2010,Texas Instruments Incorporated

RS232接口芯片双电荷泵电平转换器原理

RS232接口芯片双电荷泵电平转换器 原理 电子工业协会Electronic Industries Association Electronic Industries Association(EIA)电子工业协会(EIA) 1924年成立的EIA是美国的一个电子制造商组织。 EIA-232,就是众所周知的RS-232,它定义了数据终端设备(DTE)和数据通信设备(DCE)之间的串行连结。这个标准被广泛采用。 EIA-RS-232C电气特性: 在TxD和RxD上:逻辑1=-3V~-15V 逻辑0=+3~+15V 在RTS、CTS、DSR、DTR和DCD等控制线上: 信号有效(接通,ON状态,正电压)=+3V~+15V 信号无效(断开,OFF状态,负电压)=-3V~-15V RS-232-C电平采用负逻辑,即逻辑1:-3~-15V,逻辑0:+3~+15V。 注意,单片机使用的CMOS电平中,高电平(3.5~5V)为逻辑1,低电平(0~0.8V)为逻辑0。 单片机的SCI口要外接电平转换电路芯片把与TTL兼容的CMOS高电平表示的1转换成RS-232的负电压信号,把低电平转换成RS-232的正电压信号。典型的转换电路给出-9V和+9V。

典型的电平转换电路MAXx2xx系列芯片因单电源+5V供电,均有电荷泵电平转换器产生±10V电源,以供RS232电平所需。 一般是接4个泵电容,采用双电荷泵进行电平转换。标准接法如下图。 图1 芯片内带振荡器驱动双电荷泵,分双相四步工作,如下图。 图2电荷泵框图

第一步:S1、S3闭合,电源+5V向C1充电(图3)。C1电压最高可至5V。 图3 第二步:S2、S4闭合,C1所储电荷经S2、S4转移至C3,C3电压最高也可至5V。 C1电荷转移充电途径如红色虚线所示。 C3电压和电源+5V迭加起来提供10V的V+电源。 这时C1负端电位应等于电源+5V,所以C1负端电压波形应是0-+5V 的方波。 第三步:S5、S7闭合,C3所储电荷和电源+5V迭加经S5、S7向C2充电。 C2电压最高可至10V。充电途径如棕色虚线所示。 第二、三步实际同时进行(图4)。

TI-选择正确的电平转换方案

1. 简介 在今天的电子电路系统中电压电平的转换基本成为了必须。例如:一 个ASIC的供电为VccA,而I/O器件的供电为VccB。为了使它们之间正常通信,就需要一个如图1的电平转换(level-translation)方案。 输入电平限值和器件的输出电平主要根据器件采用的工艺技术和供电 。图2显示了不同的供电和元件技术的限值范围。为了成功的实现两个 器件的接口,一定要保证以下的条件: ■驱动器件的Voh必须大于接收器件的Vih ■驱动器件的Vol必须小于接收器件的Vil ■驱动器件的输出电压范围不能超过接收器件的可容忍的I/O电 压范围

2. 双电源电平转换器件(Dual-Supply Level Translators) 2.1 特性 双电源的器件是为了满足两类总线或不同供电器件之间的异步通讯的 。这类器件采用双电源:VccA为A端(A side)供电,VccB为B端供电。对于数据从A到B或B到A都能传输的双向的电平转换器件,方向取决于输入pin DIR的逻辑电平。如果器件有OE控制,在OE有无效时 A端和B端的总线隔离。 TI的双电源器件有各种位宽的应用并几乎覆盖了当前出现的全部的供 电应用。这些器件灵活,易用并能实现双向转换,对于许多电平转换 的应用都是理想的选择(译者注:强!)。它们的电流驱动能力可以 使其适合长线及重载的应用。 SN74AVCB324245是一种32位双电源电平转换器件(由四组8位端口组成)。图3显示了SN74AVCB324245的1.8V转3.3V的一个端口,同

时另一个端口实现3.3V到1.8V的转换。 双电源器件的优点: ●可以在不同电压结点间灵活的转换 ●具有电流驱动的能力 ●具有不同的位宽 2.2 产品列表

常用的电平转换方案

常用的电平转换方案 TTL、CMOS、ECL等电路的高低电平阀值不同,他们之间逻辑连接需要电平转换;还有,就是接口与接口之间的,如RS232与485之间,USB与串口之间等等,由于这些接口协议里面定义的电平不同,所以也需要电平转换。 1. 常用的电平转换方案 (1) 晶体管+上拉电阻法 就是一个双极型三极管或MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。 图1. 电阻-二极管拓扑,是在同一根信号线上实现双向转换的可选技术之一

图2. 分立/数字晶体管是实现双向转换的另外一种选择 (数据入和数据出也被称为主入从出(MISO)和主出从入(MOSI)。SPI能够使用超过20Mbp的时钟信号,使用CMOS推挽逻辑。由于SPI是单向的,没有必要在同一根信号线上实现双向转换。这使电平转换变得简单一些,因为 可以采用电阻与二极管(图1)或分立/数字晶体管(图2)等简单方案。I2C、SMBusTM和1-Wire 接口为双向、漏极开路拓?扑。I2C有3个速度范围:≤ 100kbps的标准模式,≤ 400kbps的快速模式,≤ 3.4Mbps的高速模式。双向总线的电平转换更加困难,因为必须在同一根数据线上进行双向转换。基于电阻-二极管或集电极/漏极开路的单级晶体管转换器的简单拓扑由于固有的单向性,无法满足要求。 ) (2) OC/OD 器件+上拉电阻法 跟1) 类似。适用于器件输出刚好为OC/OD 的场合。 (3) 74xHCT系列芯片升压(3.3V→5V) 凡是输入与5V TTL 电平兼容的5V CMOS 器件都可以用作 3.3V→5V 电平转换。 ——这是由于3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而CMOS 的输出电平总是接近电源电平的。 廉价的选择如74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列(那个字母T 就表示TTL 兼容)。 (4) 超限输入降压法(5V→3.3V, 3.3V→1.8V, ...) 凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。 这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制(改变了输入级保护电路)。 例如,74AHC/VHC 系列芯片,其datasheets 明确注明"输入电压范围为0~5.5V",如果采用 3.3V 供电,就可以实现5V→3.3V 电平转换。 (5) 专用电平转换芯片 最著名的就是164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的(俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。

各种电平总结

TTL和CMOS电平总结 TTL和CMOS电平总结 TTL——Transistor-Transistor Logic HTTL——High-speed TTL LTTL——Low-power TTL STTL——Schottky TTL LSTTL——Low-power Schottky TTL ASTTL——Advanced Schottky TTL ALSTTL——Advanced Low-power Schottky TTL FAST(F)——Fairchild Advanced schottky TTL CMOS——Complementary metal-oxide-semiconductor HC/HCT——High-speed CMOS Logic(HCT与TTL电平兼容) AC/ACT——Advanced CMOS Logic(ACT与TTL电平兼容)(亦称ACL) AHC/AHCT——Advanced High-speed CMOS Logic(AHCT与TTL电平兼容) FCT——FACT扩展系列,与TTL电平兼容 FACT——Fairchild Advanced CMOS Technology 1,TTL电平: 输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平 是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。 2,CMOS电平: 1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。而且具有很宽的噪声容限。 3,电平转换电路: 因为TTL和COMS的高低电平的值不一样(ttl 5v<==>cmos 3.3v),所以互相连接时需 要电平的转换:就是用两个电阻对电平分压,没有什么高深的东西。哈哈 4,OC门,即集电极开路门电路,OD门,即漏极开路门电路,必须外界上拉电阻和电源才能将开关电平作为高低电平用。否则它一般只作为开关大电压和大电流负载,所以又叫做驱 动门电路。 5,TTL和COMS电路比较: 1)TTL电路是电流控制器件,而coms电路是电压控制器件。 2)TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。 COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。 COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常

电平转换资料

74AVC1T145 1、概述 74AVC1T145是一款具有双向电压转换和3态输出的单位双电源收发器。它的功能端口有1位输入输出端口(A和B),一个方向控制输入(DIR)和双电源引脚(V CC(A)和V CC(B))。同时V CC(A)和V CC(B)可以输入介于0.8 V 到3.6 V的电压实现器件在任意低电压节点之间的转换(0.8 V, 1.2 V, 1.5 V, 1.8 V, 2.5 V 和3.3 V)。引脚A和DIR由V CC(A)供电,引脚B由V CC(B)供电。在DIR上的高电平允许从A传输到B,也允许在DIR上的低电平从B传输到A。 该器件明确规定在局部省电模式时使用I OFF。I OFF将使输出失能,防止在电源关闭时破坏性的回路电流通过器件。当VCC(A)或VCC(B)处于地电平电压时处于挂起模式,同时A和B 将处于高阻态。 2、功能与优点 ?电源电压范围宽: ◆ ◆ ?噪声抑制能力强 ?符合JEDEC标准: ◆-12 (0.8 V to 1.3 V) ◆-11 (0.9 V to 1.65 V) ◆-7 (1.2 V to 1.95 V) ◆-5 (1.8 V to 2.7 V) ◆-B (2.7 V to 3.6 V) ?静电保护: ◆HBM JESD22-A114E类3 b超过8000 V ◆MM JESD22-A115-A超过200 V ◆CDM JESD22-C101C超过1000 V ?最大数据速率: ◆500 Mbit / s(1.8 V至3.3 V的转换) ◆320 Mbit / s(< 1.8 V至3.3 V转换) ◆320 Mbit / s(转换为2.5 V和2.5 V) ◆280 Mbit / s(转换到1.5 V) ◆240 Mbit / s(转换到1.2 V) 挂起模式或睡眠模式; ?锁存性能超过100 mA / JESD 100 II级 ?输入接受电压最高达3.6 V ?低噪声时过冲和欠冲小于VCC的10% ?I OFF电流提供部分省电模式操作 ?多种封装选择 ?指定使用温度范围从-40°C到+ 85°C和?40°C到+ 125°C 3、订购信息(略) 4、标记(略) 5、逻辑图

5V-3.3V电平转换方案

2013年1月8日 15:17 源文档

3.3V转5V的双向电平转换电路

3.3V转5V的双向电平转换电路 说说所有的电平转换方法,你自己参考~ (1) 晶体管+上拉电阻法 就是一个双极型三极管或MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。 (2) OC/OD 器件+上拉电阻法 跟1) 类似。适用于器件输出刚好为OC/OD 的场合。 (3) 74xHCT系列芯片升压(3.3V→5V) 凡是输入与5V TTL 电平兼容的5V CMOS 器件都可以用作3.3V→5V 电平转换。 ——这是由于3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而CMOS 的输出电平总是接近电源电平的。 廉价的选择如74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列(那个字母 T 就表示TTL 兼容)。 (4) 超限输入降压法(5V→3.3V, 3.3V→1.8V, ...) 凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。 这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制(改变了输入级保护电路)。 例如,74AHC/VHC 系列芯片,其datasheets 明确注明"输入电压范围为0~5.5V",如果采用3.3V 供电,就可以实现5V→3.3V 电平转换。 (5) 专用电平转换芯片 最著名的就是164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的(俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。 (6) 电阻分压法 最简单的降低电平的方法。5V电平,经1.6k+3.3k电阻分压,就是3.3V。 (7) 限流电阻法 如果嫌上面的两个电阻太多,有时还可以只串联一个限流电阻。某些芯片虽然原则上不允许输入电平超过电源,但只要串联一个限流电阻,保证输入保护电流不超过极限(如74HC 系列为20mA),仍然是安全的。 (8) 无为而无不为法 只要掌握了电平兼容的规律。某些场合,根本就不需要特别的转换。例如,电路中用到了某种5V 逻辑器件,其输入是3.3V 电平,只要在选择器件时选择输入为TTL 兼容的,就不需要任何转换,这相当于隐含适用了方法3)。 (9) 比较器法 算是凑数,有人提出用这个而已,还有什么运放法就太恶搞了。 那位说的可以~但我分析你也不是非要芯片不可吧?尽量节约成本啊~ 3.3V转5V 电平转换方法参考 电平转换

5V到3V3的电平转换-串口通信

5V到3V3的电平转换-串口通信 一、电平转换电路 下面来分析一下电路的设计思路: https://www.360docs.net/doc/105913843.html,/BLOG_ARTICLE_244240.HTM 首先声明一下:这个电路是从3V3的角度考虑的! 1、接收通道 我们首先来明确一下数据流向(其实就是电平驱动方向),接收通道是由5V方驱动的(Source),3V3方只是取电平(Sink),因此TXD5V作为此通道的输入方,RXD3V3作为通道的输出方。 我们知道,三极管(开关型)集电极输出驱动能力不错,我们就设计为集电极输出;但是,只有一个三极管是不行的,因为集电极输出的时候,基极电平和集电极逻辑是相反的;那么,加一个反相器?没必要,那是另外一种电平转换的方法了,我们只需要再使用一个三极管,基极接前级输出就可以了。这样,逻辑转换就完成了,当输入低电平时,Q1截止,集电极输出高电平,Q2导通,集电极输出低电平。同理,高电平分析是一样的。 逻辑转换完成了,那么就是电平的问题了。这很好解决,输入方为5V逻辑,那么就给它一个VCC5,3V3逻辑高电平需要一个3V3,那么就给一个VCC3V3;OK! 2、发送通道 分析完接收通道,发送通道的原理其实也是一样的,就不详细介绍了。 3、结论 其实如果稍微熟悉电子电路知识的人看来,这个电路实在太简单,正因为如此,我才要强调,基础很重要!否则,一个系统的设计会在这些小地方卡住。 二、电平问题: 单片机手册————电气特性 常用逻辑电平:12V,5V,3.3V; 1.TTL电平: 输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

常用数字芯片大全

产品 型号规格性能说明型号规格性能说明 名称 74LS SN74LSOO四2输入与非门SN74LSO1四2输入与非门 SN74LSO2四2输入与非门SN74LS03四2输入与非门 SN74LS04六反相器SN74LS05六反相器 SN74LS06六反相缓冲器/驱动器SN74LS07六缓冲器/驱动器 SN74LS08四2输入与非门SN74LS09四2输入与非门 SN74LS10三3输入与非门SN74LS11三3输入与非门 SN74LS12三3输入与非门SN74LS13三3输入与非门 SN74LS14六反相器.斯密特触发SN74LS15三3输入与非门 SN74LS16六反相缓冲器/驱动器SN74LS17六反相缓冲器/驱动器 SN74LS20双4输入与门SN74LS21双4输入与门 SN74LS22双4输入与门SN74LS25双4输入与门 SN74LS26四2输入与非门SN74LS27三3输入与非门 SN74LS28四输入端或非缓冲器SN74LS30八输入端与非门 SN74LS32四2输入或门SN74LS33四2输入或门 SN74LS37四输入端与非缓冲器SN74LS38双2输入与非缓冲器 SN74LS40四输入端与非缓冲器SN74LS42BCD-十进制译码器 SN74LS47BCD-七段译码驱动器SN74LS48BCD-七段译码驱动器SN74LS49BCD-七段译码驱动器SN74LS51三3输入双与或非门 SN74LS54四输入与或非门SN74LS55四4输入与或非门 SN74LS63六电流读出接口门SN74LS73双J-K触发器 SN74LS74双D触发器SN74LS754位双稳锁存器 SN74LS76双J-K触发器SN74LS78双J-K触发器 SN74LS83双J-K触发器SN74LS854位幅度比较器 SN74LS86四2输入异或门SN74LS884位全加器 SN74LS904位十进制波动计数器SN74LS918位移位寄存器 SN74LS9212分频计数器SN74LS93二进制计数器 SN74LS965位移位寄存器SN74LS954位并入并出寄存器 SN74LS109正沿触发双J-K触发器SN74LS107双J-K触发器 SN74LS113双J-K负沿触发器SN74LS112双J-K负沿触发器 SN74LS121单稳态多谐振荡器SN74LS114双J-K负沿触发器 SN74LS123双稳态多谐振荡器SN74LS122单稳态多谐振荡器 SN74LS125三态缓冲器SN74LS124双压控振荡器 SN74LS1313-8线译码器SN74LS126四3态总线缓冲器 SN74LS13313输入与非门SN74LS132二输入与非触发器 SN74LS137地址锁存3-8线译码器SN74LS136四异或门 SN74LS139双2-4线译码-转换器SN74LS1383-8线译码/转换器 SN74LS14710-4线优先编码器SN74LS145BCD十进制译码/驱动器SN74LS153双4选1数据选择器SN74LS1488-3线优先编码器 SN74LS155双2-4线多路分配器SN74LS1518选1数据选择器 SN74LS157四2选1数据选择器SN74LS1544-16线多路分配器 SN74LS160同步BDC十进制计数器SN74LS156双2-4线多路分配器

电平转换方法

常用的电平转换方案 (1) 晶体管+上拉电阻法 就是一个双极型三极管或 MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。 (2) OC/OD 器件+上拉电阻法 跟 1) 类似。适用于器件输出刚好为 OC/OD 的场合。 (3) 74xHCT系列芯片升压 (3.3V→5V) 凡是输入与 5V TTL 电平兼容的 5V CMOS 器件都可以用作 3.3V→5V 电平转换。 ——这是由于 3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而 CMOS 的输出电平总是接近电源电平的。 廉价的选择如 74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列 (那个字母 T 就表 示 TTL 兼容)。 (4) 超限输入降压法 (5V→3.3V, 3.3V→1.8V, ...) 凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。 这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制 (改变了输入级保护电路)。 例如,74AHC/VHC 系列芯片,其 datasheets 明确注明"输入电压范围为0~5.5V",如果采 用 3.3V 供电,就可以实现 5V→3.3V 电平转换。 (5) 专用电平转换芯片 最著名的就是 164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的 (俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。 (6) 电阻分压法 最简单的降低电平的方法。5V电平,经1.6k+3.3k电阻分压,就是3.3V。 (7) 限流电阻法 如果嫌上面的两个电阻太多,有时还可以只串联一个限流电阻。某些芯片虽然原则上不允许输入电平超过电源,但只要串联一个限流电阻,保证输入保护电流不超过极限(如 74HC 系列为 20mA),仍然是安全的。 (8) 无为而无不为法 只要掌握了电平兼容的规律。某些场合,根本就不需要特别的转换。例如,电路中用到了某种 5V 逻辑器件,其输入是 3.3V 电平,只要在选择器件时选择输入为 TTL 兼容的,就不需要任何转换,这相当于隐含适用了方法3)。 (9) 比较器法

3.3v和5v双向电平转换芯片

3.3v和5v双向电平转换芯片 74LVC4245,8位电平转换 74LVC4245A,8位双向 NLSX4373,2位电平转换 NLSX4014,4位电平转换 NLSX4378,4位电平转换 NLSX3018,8位电平转换 max3002,8路双向 TXB0104?(她好像有一个系列?0102?0104?0106?0108), ADG3308 74HCT245:三态输出的八路总线收发器 SN74AVCH2T45 SN74AVC16T245:具有可配置电压转换和3 态输出的16 位双电源总线收发器 SN74LVC2T45DCT:双位双电源总线收发器可配置电压转换和三态输出 SN74LVC4245A:8位 德州仪器宣布推出SN74LVC1T45、SN74LVC2T45、SN74AVC8T245及SN74AVC20T245四款新型双电源电平转换收发器。该新品能够在 1.5V、1.8V、2.5V、3.3V 与5V 电压节点之间进行灵活的双向电平转换,而且可提供全面的可配置性。如果采用AVC 技术,则每条轨可从 1.4V 配置为 3.6V;而采用LVC 技术时则可从1.65V 配置为5.5V。适用于便携式消费类电子产品、网络、数据通信以及计算应用领域。 日前,德州仪器(TI)宣布推出四款新型的双电源电平转换器--AVC1T45、AVC2T45、AVC16T245及AVC32T245,从而进一步扩展其电平转换产品系列。这些转换器能够在互不兼容的I/O之间进行通信。这四款器件均支持1.2V、1.5V、1.8V、2.5V与3.3V节点之间的双向电平转换。在混合信号环境中,可以使用这些电压电平的任意组合,从而提高这些器件的灵活性。 1位AVC1T45与2位AVC2T45可根据需要在电路板上集成单或双转换器功能,而不是通过较高位宽的器件进行路由,这有助于简化电路板布线作业(board routing),可适用于便携式手持应用的转换要求。AVC16T245与AVC32T245是TI当前16位与32位双电源转换功能的改进版本。这些器件能够提供较低的功耗(AVC16T245的功耗为25μA,而AVCA164245的功耗则为40μA)。该类器件的总线控制选件无需外部上拉/下拉电阻器。TI还提供全面的IBIS模型支持。 SN74AVC1T45与SN74AVC2T45以及总线控制版本SN74AVCH1T45与SN74AVCH2T45均采用NanoStar 与NanoFree芯片级封装。这些器件现已推出,并可提供样片。批量为千套时,预计1T45器件的最低零售单价为0.24美元,而2T45器件的最低零售单价为0.35美元。 SN74AVC16T245和总线控制版本SN74AVCH16T245采用56球栅VFBGA封装。该器件现已推出,并可提