计组实验报告Add8

附页:

1.代码

module Add8(A,B,asc,Cin,en,d,Cout,Af);

input en,asc,Cin;

Input [7:0] A,B;

output Cout,Af;

Output [7:0] d;

reg Cout,Af;

reg [7:0] d;

integer i,n,k;

always@(A or B or en or Cin or asc )

if(!en)

begin end

else begin

if(!asc)

begin n=Cin;

k=0;

for(i=0;i<8;i=i+1)

begin

n=A[i]+B[i]+n;

k=k+1;

if(k==4)

begin

if(n> 1)

begin Af=1;

if(n>1)begin d[i]=n-2;n=1;end

else begin d[i]=n;n=0;end

end

else if (n<2)

begin Af=0;

if(n>1)begin d[i]=n-2;n=1;end

else begin d[i]=n;n=0;end end

end

else begin

if(n>1)begin d[i]=n-2;n=1;end

else begin d[i]=n;n=0;end

end

end

Cout=n;

end

else begin

n=Cin;k=0;

for(i=0;i<8;i=i+1)

begin

if(n>=0)begin d[i]=n;n=0;end

else if(n==-1)begin d[i]=1;n=1;end

else if(n==-2)begin d[i]=0;n=1;end

end

Cout=n;

end

endmodule

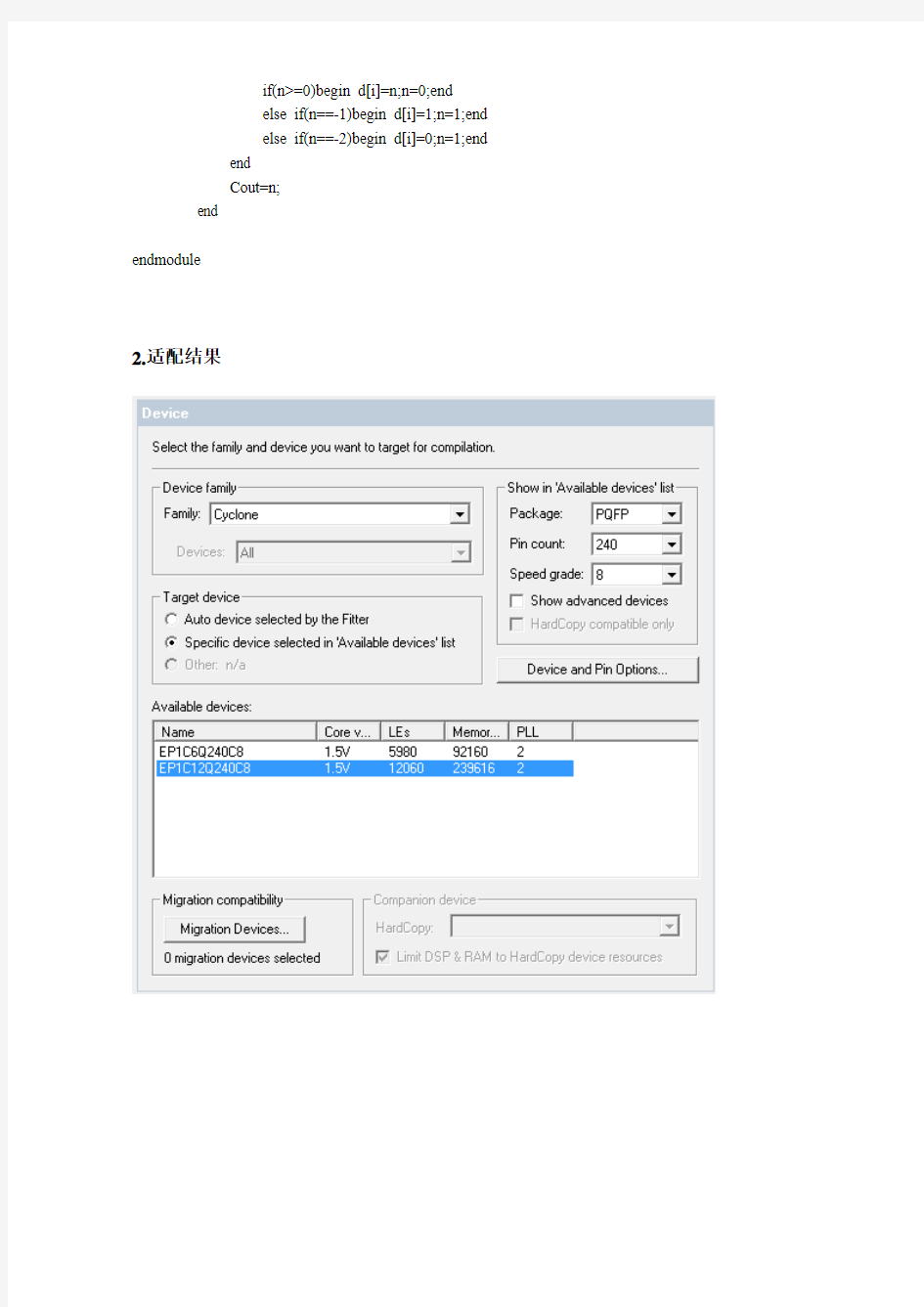

2.适配结果

3.波形图

①非工作状态:en=0

②加法:en=1,Cin=0,asc=0

③带进位加法:en=1,Cin=1,asc=0

④减法:en=1,Cin=0,asc=1

⑤带借位减法:en=1,Cin=1,asc=1

计组实验报告

计算机组成原理实验报告 实验1:VERILOG 设计基础 专业班级:14级计算机二班 学号:14048001 姓名:杨娜 学号:14048003 姓名:周蓉 实验地点:理工楼901 实验时间:2016年5月14日

实验十VGA显示控制器的设计 一、实验目的 1、学习VERILOG的基本语法和编程规则 2、掌握通用寄存器等常用基本数字模块的VERILOG描述和基本设计方法 3、理解带使能控制和异步清零的8位寄存器的设计原理 4、掌握使用VERILOG设计和验证带使能控制和异步清零的8位寄存器的方法 5、掌握移位寄存器的设计方法 二、实验任务 1、设计一个带使能控制和异步清零的8位寄存器REG8X,实现8位输入的锁存,在时钟的上升沿处得到一个8位的输出和一个8位的反向输出,将结果显示在发光二极管。 模块的端口描述如下: 模块的参考物理结构如下: R7 R6 R i R 0 7 6 i 0 带使能控制和异步清零的8位寄存器 模块的使用注意事项

1.数据源D(7..0)一直加在寄存器的数据输入端; 2.周期性的时钟信号Clock一直加在寄存器的时钟输入端 3.使能信号Enable控制寄存器是否接受数据。当Enable = '0'时,寄存器不 接受数据,保持原来的状态不变;当Enable = '1'时,在时钟信号Clock正 跳变时,寄存器接受并保存当时D(7..0)的数据; 4.本寄存器其它方面的功能与上述的寄存器相同。 完成的参考电路图如下:dout=q 2、设计一个有左、右移位功能的8位寄存器REGSHIFT8,并仿真验证。

三、实验内容 1、通过输入数据先进行计算,并通过实验进行验证REG8X。 (1)、将清零信号Resetn(sw17)设为0,将输入信号D(sw7~sw0)设为10101010,观察输出信号Q(ledr7~ledr0)和Qb(ledg7~ledg0),观察并记录输出。 (2)、将清零信号Resetn(sw17)设为1,在时钟信号处输入一个上升沿(按下key0),观察并记录输出。 (3)、将输入信号D(sw7~sw0)设为01010101,观察并记录输出。 (4)、在时钟信号处输入一个上升沿(按下key0),观察并记录输出。 (5)、自行完善设计表格,观察并记录测试输出。 实验数据表 2、通过输入数据先进行计算,并通过实验进行验证REGSHIFT8。 (1)、测试清零信号Resetn (2)、测试移位功能 (3)、测试寄存功能 (4)、自行设计表格观察并记录测试输出。 实验数据表

杭电计组实验报告10

计组实验十 老师:包健 一、源代码测试模块代码: module Top( inputinclk, inputmem_clk, inputrst, outputreg[7:0] LED, input [3:0] SW ); wireclk; MyButtonmb( .clk_100MHz(mem_clk), .BTN(inclk), .BTN_Out(clk) ); wire [31:0] ALU_F; wire [31:0] M_R_Data; wire ZF; wire OF; wire [31:0]PC; My_I_CPUmy_i_cpu( .clk(clk), .mem_clk(mem_clk), .rst(rst), .ALU_F(ALU_F), .M_R_Data(M_R_Data), .ZFF(ZF), .OF(OF), .PC_out(PC) ); always@(*) begin case(SW) 4'd0:LED=ALU_F[7:0]; 4'd1:LED=ALU_F[15:8]; 4'd2:LED=ALU_F[23:16]; 4'd3:LED=ALU_F[31:24]; 4'd4:LED=M_R_Data[7:0];

4'd5:LED=M_R_Data[15:8]; 4'd6:LED=M_R_Data[23:16]; 4'd7:LED=M_R_Data[31:24]; 4'd8:LED={ZF,6'd0,OF}; 4'd12:LED=PC[7:0]; 4'd13:LED=PC[15:8]; 4'd14:LED=PC[23:16]; 4'd15:LED=PC[31:24]; default:LED=8'b0000_0000; endcase end endmodule 顶层模块代码: moduleMy_I_CPU( inputclk, inputmem_clk, inputrst, output [31:0] ALU_F, output [31:0] M_R_Data, output ZFF, output OF, output [31:0]PC_out ); //wire clk_n = ~clk; wire[31:0] codes; wire [31:0]PC_new; reg [31:0]PC; Inst_Fetch1 inst_fetch( .PC(PC), .rst(rst), .clk(clk), .Inst_codes(codes), .PC_new(PC_new) ); wire[5:0] OP; wire[5:0] func;

数电实验报告

北京邮电大学 数字电路与逻辑设计实验简易电子琴演奏器 班级: 学号: 姓名:

一.设计课题的任务要求 题目五简易电子琴演奏器 原理概述: 根据声乐知识,产生音乐的两个因素是音乐频率的持续时间,音乐的十二平均率规定,每两个八音度之间的频率相差一倍,在两个八音度之间,又可分为12个半音。每两个半音的频率比为4。另外,音名A(乐谱中的低音6)的频率为440HZ,音名B到C之间,E到F之间为半音,其余为全音。由此可以计算出乐谱中从低音1到高音1之间每个音名的频率如下表所示。 基本要求: 1、用8×8点阵显示“1 2 3 4 5 6 7”七个音符构成的电子琴键盘。其中点阵 的第一列用一个LED点亮表示音符“1”,第二列用二个LED点亮表示音符“2”,依此类推,如下图所示。 图1 点阵显示的电子琴键盘 2、用BTN1~BTN7七个按键模拟电子琴手动演奏时的“1 2 3 4 5 6 7”七个 音符。当某个按键按下时,数码管显示相应的音符,点阵上与之对应的音符显示列全灭,同时蜂鸣器演奏相应的声音;当按键弹开时数码管显示的音符灭掉,点阵显示恢复,蜂鸣器停止声音的输出。下图所示为按下BTN3按键时点阵的显示情况。

图2 按键按下后的点阵显示 3、由拨码开关切换选择高、中、低音,并用数码管进行相应的显示。 4、通过按键BTN0进行复位,控制点阵显示图1的初始状态。 提高要求: 1、可通过一个拨码开关进行手动/自动演奏的切换,并与点阵显示配合增加 自动演奏乐曲的功能。 2、增加手动演奏的音符存储、播放功能。 二、系统设计(包括设计思路、总体框图、分块设计) 设计思路 电子琴的设计主要包括了显示与发声部分,发声部分主要分为三个不同的音阶,每个音阶包括了七个音,发生部分可以通过对50M晶振的分频,通过改变分频系数,得到响应频率的时钟脉冲,以这个脉冲控制蜂鸣器发出声音;显示部分则包括了数码管的音阶显示与点阵的琴键显示。数码管可以动态显示出音阶与当前音符,点阵则模拟显示琴键,动态显示实现了一个三角阵,并对应到音符琴键,这两个显示模块可以通过动态显示来实现显示显示不同的内容,配合按键可以实现基本功能。不同的音阶可以通过相应拨码开关的选择来调节,至于显示的复位,则不需要专门设置键位来完成,因为每个转台结束后就会自动转入等待状态。对于音调,乐曲的12平均率规定:每2个八度音之间的频率相差1倍。在2个八度音之间,又可分为12个半音,每2个半音的频率比为12√2。另外,音符A 的频率为440Hz,音符B到C之间、E到F之间为半音,其余为全音。由此可以计算出简谱中从低音1到高音1之间每个音符的频率。而对于节拍,如果将一拍的长度定为1秒,则1/4拍的时间为1/4秒,为其提供一个4Hz的时钟频率即可产生出1/4拍的效果了。若需要半拍,只需将该音符记录两次就可以了。 总体框图

计组-加法器实验报告

半加器、全加器、串行进位加法器以及超前进位加法器 一、实验原理 1.一位半加器 A和B异或产生和Sum,与产生进位C 2.一位全加器 将一位半加器集成封装为halfadder元件,使用两个半加器构成一位的全加器 3.4位串行进位加法器 将一位全加器集成封装为Fulladder元件,使用四个构成串行进位加法器

4.超前进位加法器(4位) ⑴AddBlock 产生并行进位链中的ti(即Cthis)和di(即Cpass),以及本位结果Sum ⑵进位链(Cmaker) 四位一组并行进位链,假设与或非门的级延迟时间为1.5ty,与非门的延迟时间为1ty,在di和ti产生之后,只需2.5ty就可产生所有全部进位

⑶超前进位加法器 将以上二者结合起来即可完成,A和B各位作为各个AddBlock的输入,低一位的进位Ci-1作为本位AddBlock的C-1的输入。各个AddBlock输出的C_this和C_pass作为对应的Cmaker的thisi和passi的输入。

二、实验器材 QuartusII仿真软件,实验箱 三、实验结果 1.串行进位加法器结果 2.超前进位加法器结果

四、实验结果分析 1.实验仿真结果显示串行加法器比超前进位加法器快,部分原因应该是电路结构优化 不到位。另外由于计算的位数比较少,超前进位加法链结构较复杂,所以优势没体现出来,反倒运作的更慢一点。当位数增加的时候,超前进位加法器会比串行的更快。 2.波形稳定之前出现上下波动,应该与“竞争冒险”出现的情况类似,门的延迟和路径 的不同导致了信号变化时到达的时间有先有后,因此在最终结果形成前出现了脉冲尖峰和低谷;另外也可能部分原因由于电路结构优化的不到位所致

广州大学实习报告

广州大学实习报告 项目名称:电工电子实习H 学院:机械与电气工程学院 专业年级:机械144 学号:1407200138 姓名:张誉霖 指导老师:陈新兵张倩 实习单位:广州大学电工电子实习中心 实习时间:2016/5/30-2016/6/3 广州大学教务处制

-、实习目的 1、目的和意义 通过一周的电工电子实习,是自己对元器件有一定感性和理性的认识,打好以后学习专业知识的基础。培养了理论与实践相联系的能力,提高自己分析和解决问题的能力,增强了独立工作的能力。实习是培养学生操作技能的重要环节,而技能的形式是通过观察、实践和反复练习实现的。以实习实践激发同学们的兴趣。在实习过程中,熟悉手工焊锡的常用工具的使用及其维护,基本掌握手工电烙铁的焊接技 术,能够独立的完成简单电子产品的安装与焊接。熟悉电子产品的安装工艺的生产流程。熟悉印制电路板设计的步骤和方法,熟悉手工制作印制电路板的工艺流程,能够根据电路原理图,元器件实物设计并制作印制电路板。熟悉常用电子器件的类别、型号、规格、性能及其适用范围。能够正确识别和选用常用的电子器件,并且能够熟练地使用普通万用表和熟悉万用表。了解电子产品的焊接、调试与维修方 法。通过这样的学习,使学生产生好奇心,凝聚学生的注意力,以保持兴趣。通过对画图软件的学习。提高了学生电路分析能力,增强独立工作,独立思考的能力。 同时在讨论中,培养了学生的团结协作能力 2、发展情况及实习要求 发展情况:“广州大学电工电子实验中心”是“广州大学实验中心”以省级实验教学示范中心的建设要求为标准,根据广州大学“培养知识面宽、基础 厚实、创新意识和创新能力强的高素质应用型人才”的人才培养目标要 求,并基于实验中心的“电子信息实验室”来建设的。本中心的定位是 全校共享的电工电子类专业基础实验室,以及电类专 业学生实践和创新活动基地。电子信息实验室位于广州大学电子信息实 验楼,用房面积11300平方米,现有实验教学分室24间、教师开放室 2间以及学生全天候开放室7间。电子信息实验室承担全校 12 个学院27个专业约50门电工电子以及摄影类的实验教学任务, 实验室还常年全天候开放,承接了大量的毕业设计、电子设计竞赛、自 主学习等开放实验任务。2005年以来,学校正式启动了实验教学团队 的建设。使我校实验教学改革工作得以蓬勃开展。我们注重科研活动 的开展,老师和实验技术人员均积极参与科学研究和实验教学研究,并 取得不少的成绩。学生科研也得到重视。通过开放实验室为学生科研和 电子制作提供条件。学生参加全国大学生电子设计竞赛、实验大赛、挑 战杯等竞赛活动,获得各种各样的奖项,同时还培养了学生的创新、创 业精神和实践能力。 实习要求:在实习过程中,以及今后的专业知识学习过程中以工程人员应具备的基本素养为要求来锻炼自己。在每天的实习结束后,认真检查自己,看自 己达到多少要求,还有什么不足,了解以后应该如何加强。 二、实习内容 实习项目一:安全用电 了解安全用电知识,学会安全操作要领,培养严谨的科学作风和良好的安全作风,电子

计组-4位乘法器实验报告

实验4位乘法器实验报告 姓名:X XX 学号:X XX 专业:计算机科学与技术课程名称:计算机组成同组学生姓名:无 实验时间:实验地点:指导老师:XXX 一、实验目的和要求 1.熟练掌握乘法器的工作原理和逻辑功能 二、实验内容和原理 实验内容: 根据课本上例3-7的原理,来实现4位移位乘法器的设计。 具体要求:1. 乘数和被乘数都是4位 2. 生成的乘积是8位的 3. 计算中涉及的所有数都是无符号数 4.需要设计重置功能 5.需要分步计算出结果(4位乘数的运算,需要四步算出结果) 实验原理: 1.乘法器原理图

2.本实验的要求: 1.需要设计按钮和相应开关,来增加乘数和被乘数 2.每按一下M13,给一个时钟,数码管的左边两位显示每一步的乘 积 3.4步计算出最终结果后,LED灯亮,按RESET重新开始计算 三、主要仪器设备 1.Spartan-III开发板1套 2.装有ISE的PC机1台 四、操作方法与实验步骤 实验步骤: 1.创建新的工程和新的源文件 2.编写verilog代码(top模块、display模块、乘法运算模块、去抖动模块以及 UCF引脚) 3.进行编译 4.进行Debug 工作,通过编译。

5.. 生成FPGA代码,下载到实验板上并调试,看是否与实现了预期功能 操作方法: TOP: module alu_top(clk, switch, o_seg, o_sel); input wire clk; input wire[4:0] switch; output wire [7:0] o_seg; // 只需七段显示数字,不用小数点 output wire [3:0] o_sel; // 4个数码管的位选 wire[15:0] disp_num; reg [15:0] i_r, i_s; wire [15:0] disp_code; wire o_zf; //zero detector initial begin i_r <= 16'h1122; //0x1122 i_s <= 16'h3344; //0x3344 end alu M1(i_r, i_s, switch[4:2], o_zf, disp_code); display M3(clk, disp_num, o_seg, o_sel); assign disp_num = switch[0]?disp_code:(switch[1] ? i_s : i_r); endmodule

数电实验实验报告

数字电路实验报告

实验一 组合逻辑电路分析 一.试验用集成电路引脚图 74LS00集成电路 74LS20集成电路 四2输入与非门 双4输入与非门 二.实验内容 1.实验一 自拟表格并记录: 2.实验二 密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开。否则,报警信号为“1”,则接通警铃。试分析密码锁的密码ABCD 是什么? X1 2.5 V A B C D 示灯:灯亮表示“1”,灯灭表示“0” ABCD 按逻辑开关,“1”表示高电平,“0”表示低电平

ABCD 接逻辑电平开关。 最简表达式为:X1=AB ’C ’D 密码为: 1001 A B C D X1 X2 A B C D X1 X2 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 1 1 0 0 1 1 0 0 0 1 0 0 1 1 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 0 1 0 1 0 0 0 1 1 1 0 0 0 1 0 1 0 1 0 1 1 1 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 1 0 1 1 1 1 1 1 1 1 1 三.实验体会: 1.分析组合逻辑电路时,可以通过逻辑表达式,电路图和真值表之间的相互转换来到达实验所要求的目的。 2.这次试验比较简单,熟悉了一些简单的组合逻辑电路和芯片 ,和使用仿真软件来设计和构造逻辑电路来求解。 实验二 组合逻辑实验(一) 半加器和全加器 一.实验目的 1. 熟悉用门电路设计组合电路的原理和方法步骤 二.预习内容 1. 复习用门电路设计组合逻辑电路的原理和方法步骤。 2. 复习二进制数的运算。 3. 用“与非门”设计半加器的逻辑图。 4. 完成用“异或门”、“与或非”门、“与 非”门设计全加器的逻辑图。 5. 完成用“异或”门设计的3变量判奇 电路的原理图。 三.元 件参考 U1A 74LS00D U1B 74LS00D U1C 74LS00D U1D 74LS00D U2A 74LS00D U2B 74LS00D U2C 74LS00D U3A 74LS20D X1 2.5 V X2 2.5 V VCC 5V A B C D

计组实验二实验报告-80868088指令系统

HUNAN UNIVERSITY 课程实习报告 题目: 8086/8088指令系统 学生姓名 学生学号 专业班级计算机科学与技术2班 指导老师 完成日期2013年4月21日

一、实验目的 利用debug工具的e和u功能找出8086/8088指令系统的指令格式中各种操作吗编码对应的指令功能,得到8086/8088操作吗从00~FF所对应的的汇编指令的名字。并加以分析总结,形成你的关于8086/8088指令系统操作码编码方法的实验报告。 二、实验过程 1、编写C++程序,生成debug的输入文件(shuru.txt) 2、将shuru.txt复制到debug的根目录下,在debug界面输入如下指令“debug

打开out2.txt,对256条记录进行分析。 三、256条记录 指令码汇编指令 ------------------------------------------------------------- 0B76:0100 0000 ADD [BX+SI],AL 0B76:0100 0100 ADD [BX+SI],AX 0B76:0100 0200 ADD AL,[BX+SI] 0B76:0100 0300 ADD AX,[BX+SI] 0B76:0100 0400 ADD AL,00 0B76:0100 050000 ADD AX,0000 0B76:0100 06 PUSH ES 0B76:0100 07 POP ES 0B76:0100 0800 OR [BX+SI],AL 0B76:0100 0900 OR [BX+SI],AX 0B76:0100 0A00 OR AL,[BX+SI] 0B76:0100 0B00 OR AX,[BX+SI] 0B76:0100 0C00 OR AL,00 0B76:0100 0D0000 OR AX,0000 0B76:0100 0E PUSH CS 0B76:0100 0F DB 0F 0B76:0100 1000 ADC [BX+SI],AL 0B76:0100 1100 ADC [BX+SI],AX 0B76:0100 1200 ADC AL,[BX+SI] 0B76:0100 1300 ADC AX,[BX+SI] 0B76:0100 1400 ADC AL,00 0B76:0100 150000 ADC AX,0000 0B76:0100 16 PUSH SS 0B76:0100 17 POP SS 0B76:0100 1800 SBB [BX+SI],AL 0B76:0100 1900 SBB [BX+SI],AX 0B76:0100 1A00 SBB AL,[BX+SI] 0B76:0100 1B00 SBB AX,[BX+SI] 0B76:0100 1C00 SBB AL,00 0B76:0100 1D0000 SBB AX,0000 0B76:0100 1E PUSH DS 0B76:0100 1F POP DS 0B76:0100 2000 AND [BX+SI],AL 0B76:0100 2100 AND [BX+SI],AX 0B76:0100 2200 AND AL,[BX+SI] 0B76:0100 2300 AND AX,[BX+SI] 0B76:0100 2400 AND AL,00 0B76:0100 250000 AND AX,0000

数电实验报告

数字电子技术实验报告 学院:工程学院 专业:※※※ 姓名: ※※※ 学号: ※※※ 指导教师:※※ 时间: 2013.12.10

目录 实验一 2位二进制乘法器 (1) 一、实验要求: (1) 二、实验原理: (1) 三、实验分析 (1) 四、实验电路(如图1-7): (4) 五、仿真结果: (4) 六、注意事项: (6) 实验二可控加/减法 (7) 一、实验要求: (7) 二、实验原理: (7) 三、实验分析: (7) 四、实验电路: (11) 五、仿真结果: (13) 六、注意事项: (14) 实验三可控乘/除法 (15) 一、实验要求: (15) 二、实验原理: (15) 三、实验分析: (15) 四、实验电路: (19) 五、仿真结果: (20) 六、注意事项: (21) 实验四模拟信号可控乘除法 (22) 一、实验要求: (22) 二、实验原理: (22) 三、实验分析: (24)

四、实验电路 (26) 五、仿真结果: (27) 六、注意事项: (32) 实验五自动控制增益电路 (33) 一、实验要求: (33) 二、实验原理: (33) 三、实验分析: (34) 四、实验电路: (35) 五、仿真结果: (36) 六、注意事项: (39) 参考文献 (40) 总结 (41)

实验一2位二进制乘法器 一、实验要求: 用加法器实现两位二进制数的乘法。 二、实验原理: 设两位二进制数分别为A1A0和B1B0,就跟我们平常进行手工乘法一样,我们需要列乘式,则它们之间的乘法可用如下计算表示(如图1-1): 图1-1 二进制数间乘法图 所以我们如果实现了两个一位二进制的相乘,再利用加法器就可以得出结果,而两个位二进制的乘法即与运算。 三、实验分析 乘法的相乘利用与门实现,比如74LS08,然后将乘出的结果进行相加可以利用加法实现,比如四位加法器74LS283。 74LS08只是含有4个独立的与门,没有什么需要深入分析的。74LS283是快速进位集成4位加法器,所谓快速进位,是指加法运算过程中,各级进位信号同时送到各位全加器的进位输出端。超前进位加法器使每位的进位直接由加数和被加数产生,而无需等待低位的进位信号。这种加法器比串行进位加法器速度快了不少。74LS283是由4个全加器构成的,全加器的结构图如下图1-2: 1位二进制数和 1位二进制数相加 低位来的进位高位进位 图1-2 全加器的结构图

计组实验报告.

武汉大学计算机学院计算机科学与技术专业 CPU设计实验报告 实验名称:开放式实验CPU设计课题名称: 计算机组成原理 班级: 指导教师:徐爱萍 组长: 组员: 二零一五年三月

目录 目录 (1) 1 实验环境 (2) 1.1 Quartus Ⅱ介绍 (2) 1.2 硬件描述语言(VHDL) (3) 1.3实验的主要成果 (3) 2 实验要求 (5) 2. 1 指令格式要求 (5) 2. 2 指令流程及微信号序列分析 (6) 2.2.1 ADD指令分析 (6) 2.2.2 ADC指令分析 (7) 2.2.3 SUB指令分析 (7) 2.2.4 SBC指令分析 (7) 2.2.5 INC指令分析 (7) 2.2.6 DEC指令分析 (8) 2.2.7 SHL指令分析 (8) 2.2.8 SHR指令分析 (8) 2.2.9 MOVR指令分析 (8) 2.2.10 MOVD指令分析 (9) 2.2.11 LDRR指令分析 (9) 2.2.12 STRR指令分析 (10) 2.2.13 JMP指令分析 (10) 2.2.14 JRC指令分析 (11) 2.2.15 JRZ指令分析 (11) 2.2.16 JRS指令分析 (11) 2.2.17 CLC指令分析 (11) 2.2.18 STC指令分析 (11) 3.部件仿真实验 (11) 3.1 八个通用寄存器设计与仿真 (11) 3.1.1 设计代码 (11) 3.1.2 RTL连接图 (17) 3.1.3 仿真过程 (17) 3.2算术逻辑单元设计与仿真 (18) 3.2.1 设计代码 (18) 3.2.2 RTL连接图 (21) 3.2.3 仿真过程 (22) 4. CPU设计 (23) 4.1取指设计 (23) 4.2指令译码的设计 (25) 4.3执行部分设计 (28) 4.4存储器部分设计 (31) 4.5通用寄存器组设计 (32)

常用电子仪器的使用实验报告

广州大学学生实验报告 院(系)名称班 别姓名 专业名称学号 实验课程名称模拟电路实验 实验项目名称常用电子仪器的使用 实验时间实验地点 实验成绩指导老师签名 【实验目的】 1、学习电子电路实验中常用的电子仪器——示波器、函数信号发生器、直流稳压电源、交流毫伏表、频率计等的主要技术指标、性能及正确使用方法。 2、初步掌握用双踪示波器观察正弦信号波形,锯齿波信号波形,方波波形与读取波形参数的方法。【实验仪器与材料】 DS1062E数字示波器一台 AS101E函数信号发生器一台 DA-16D交流毫伏表一台 【实验原理】 在模拟电子电路实验中,经常使用的电子仪器有示波器、函数信号发生器、直流稳压电源、交流毫伏表及频率计等。它们与万用电表一起,可以完成对模拟电子电路的静态与动态工作情况的测试。 实验中要对各种电子仪器进行综合使用,可按照信号流向,以连线简捷,调节顺手,观察与读 数方便等原则进行合理布局,各仪器与被测实验装置之间的布局与连接如图1-1所示。接线时应注意,为防止外界干扰,各仪器的共公接地端应连接在一起,称共地。信号源与交流毫伏表的引线通常用屏蔽线或专用电缆线,示波器接线使用专用电缆线,直流电源的接线用普通导线。 【实验步骤】 1、用机内校正信号对示波器进行自检。 (1) 扫描基线调节 将示波器的显示方式开关置于“单踪”显示(Y1或Y2),输入耦合方式开关置“GND”,触发方式开关置于“自动”。开启电源开关后,调节“辉度”、“聚焦”、“辅助聚焦”等旋钮,使荧光屏上显 示一条细而且亮度适中的扫描基线。然后调节“X轴位移”()与“Y轴位移”( )旋钮,使扫 描线位于屏幕中央,并且能上下左右移动自如。 (2)测试“校正信号”波形的幅度、频率 将示波器的“校正信号”通过专用电缆线引入选定的Y通道(Y1或Y2),将Y轴输入耦合方式开关置于“AC”或“DC”,触发源选择开关置“内”,内触发源选择开关置“Y1”或“Y2”。调节X轴“扫描速率”开关(t/div)与Y轴“输入灵敏度”开关(V/div),使示波器显示屏上显示出一个或数个周期稳定的方波波形。

计算机组成原理实验报告二

实验二存储器实验 一、实验目的 熟悉和了解存储器组织与总线组成的数据通路。 二、实验原理 存储器是计算机的存储部件,用于存放程序和数据。存储器是计算机信息存储的核心,是计算机必不可少的部件之一,计算机就是按存放在存储器中的程序自动有序不间断地进行工作。本系统从提高存储器存储信息效率的角度设计数据通路,按现代计算机中最为典型的分段存储理念把存储器组织划分为程序段、数据段等,由此派生了数据总线(DBUS)、指令总线(IBUS)、微总线( BUS)等与现代计算机设计规范相吻合的实验环境。该存储器组织由二片6116构成具有奇偶概念的十六位信息存储体系,该存储体系AddBus由PC指针和AR 指针分时提供,E/M控位为“0”时选通PC,反之选通AR。该存储体系可随机定义总线宽度,动态变更总线结构,把我们的教学实验提高到能与现代计算机设计规范相匹配与接轨的层面。 连线信号孔接入孔作用有效电平 1 DRCK CLOCK 单元手动实验状态的时钟来源下降沿打入 2 W K6(M6) 总线字长:1=16位字操作,0=8位字节操作 3 XP K7(M7) 源部件奇偶标志:1=偶寻址,0=奇寻址 4 X2 K10(M10) 源部件定义译码端X2 三八译码 八中选一5 X1 K9(M9) 源部件定义译码端X1

四、实验过程 1. 存储器数据段读写操作 (1) 数据段写操作(字) 在进行数据存储器字操作时,地址线A0必须为0(偶地址)。向数据段的0000~0005h 存储单元写入11 22 33 44 55 66一串数据,以0000h 地址单元写入数据1122h 为例表述操作流程。 置地址I/O=0000h AR 地址写入(0000h)置数据I/O=1122h 存储器写入(1122h)关存储器写X2 X1 X0=011XP W=11 LDAR(K17)=0 MWR(K21)=1按[单拍] E/M(K23)=1LDAR(K17)=1按[单拍] MWR(K21)=0 (2) 数据段读操作(字) 依次读出数据段0~0005h 单元的内容,这里以0000h 地址单元读出为例阐述操作流程。 置地址I/O=0000h AR 地址写入(0000h)关AR 写使能存储器读出(1122h)数据总线显示存储器值 X2 X1 X0=011XP W=11 LDAR(K17)=0 E/M(K23)=1LDAR(K17)=1按 [单拍] X2 X1 X0=100W=1 2. 存储器程序段读写操作 (1) 程序段字节写操作 计算机规范的取指操作均以字节为单位。所以本实验以字节操作方式展开。程序段写入必须从定义地址入手,然后再进入程序存储器的写入。 PC 指针是带预置加法计数器,因此在输入起始地址后一旦后续地址为PC+1的话就不需重装PC ,用PC+1指令完成下续地址的读写操作。 PC 地址装载写入与PC+1写入流程 置地址I/O=0000h PC 地址写入(0000h)I/O=1234h 12h →[PC]地址增量PC+1关存储器写X2 X1 X0=011XP W=11 E/M(K23)=0LDPC(K22)=0MWR(K21)=1W=0,按[单拍] LDPC(K22)=1MWR(K21)=0 E/M(K23)=1LDPC(K22)=1按[单拍] LDPC(K22)=0MWR(K21)=1XP=0,按[单拍] (2) 程序段字节读操作 PC 地址装载读出及PC+1读出流程 X2 X1 X0=011XP W=11 E/M(K23)=0LDPC(K22)=0X2 X1 X0=100XP=1, W=0 LDPC(K22)=1按[单拍] E/M(K23)=1LDPC(K22)=1按[单拍] 按[单拍] 五、结果分析

数电实验报告

班级:姓名: 学号: 实验报告(一)TTL集成逻辑门的逻辑功能与参数测试1.测试TTL集成与非门74LS20的逻辑功能,测试结果记录如下表: 输入输出 An Bn Cn Dn Yn 1 1 1 1 0 1 1 1 1 0 1 1 1 1 0 1 1 1 1 0 2. 74LS20主要参数的测试 I CCL (mA) I CCH (mA) I il (mA) I OL (mA) N O= iL OL I I 3. 电压传输特性测试 V i(V) 0 0.4 0.7 0.9 1.0 1.1 1.2 1.3 1.4 2.0 3.0 4.0 … V O(V) 4.画出实测的电压传输特性曲线,并从中读出各有关参数值。

实验报告(二)CMOS 电路 1.用所给的集成电路(CD4007)实现F=ABC ,将实验结果填入真值表中,并测出高、低电平(真值表自拟,测试步骤自拟)。 2. 用所给的集成电路实现F=C B A ++(真值表自拟,测试步骤自拟)。 3. 用所给的集成电路,构成图2-2反相器。 (a )测最大灌电流I OL (V OL =0.1V ,接通图2-2中的虚线框①)。 (b )测最大拉电流I OH (V OH =4.9V,断开虚线框①,接通虚线框②。 4. 构成如图2-3所示的反相器,测最大灌电流I OL 。

实验报告(三)组合逻辑电路实验分析与设计(1) 写出由与非门组成的半加器电路的逻辑表达式 (2) 根据表达式列出真值表,并画出卡诺图判断能否简化 A B Z1 Z2 Z3 S C 0 0 0 1 1 0 1 1 实验: 1.测试由与非门组成的半加器电路的逻辑功能 A B S C 0 0 0 1 1 0 1 1 2.测试用异或门74LS86和与非门74LS00组成的半加器的逻辑功能 A B S C 0 0 0 1 1 0 1 1

计组实验报告--部分

2、设计报告 2、1实验方法 本实验要完成的工作主要包括: 1、指令系统的设计 2、利用VHDL语言完成实验CPU的设计,包括通用寄存器的设计、取值部分设计、指令译 码设计、执行设计、存储器设计、程序包设计和顶层设计设计 3、在Quatus II 平台上进行仿真,并下载到TEC-CA教学实验箱上进行调试。 这三大部分为并行关系,只有在完成上一部分的基础上才能继续进行下一步,而第二大部分可以同时并行进行。 实验的主要流程图为图2.1所示。 图2.1

在指令系统和CPU逻辑设计时,主要的方法是先根据老师给的指令要求,确定CPU所要实现的功能,根据寄存器等的情况划分指令格式,然后根据功能写出指令,根据不同指令的特点将它们分组并确定操作码;接下来设想每条指令的执行过程,需要哪些硬件支持,最后确定整个CPU的逻辑结构图。 2、2总体说明 2.2.1 CPU组成部件 实验CPU由5部分组成:取指部分instru_fetch、指令译码部分decoder_unit、执行部分exe_unit、存储器部分memory_unit和通用寄存器组fegile.另外,还有一个程序包exe_cpu_components,将各底层设计实体作为元件存储,供各设计实体使用。顶层设计实体exe_cpu完成5个组成部分的链接。 GR(8位,4个寄存器),ALU(8位),时序节拍发生器timer,AR(8位),IR(8位),PC(8位)、PC(8位),RAM(8位),组合期间T1,T2,T3。逻辑控制器件controller,地址总线(8位),数据总线(8位)。 2、2、2整机原理实验图

图2.2.1 图2.2.2

数电实验报告

实验一门电路逻辑功能及测试 一、实验目的 1、熟悉门电路逻辑功能。 2、熟悉数字电路学习机及示波器使用方法。 二、实验仪器及材料 1、双踪示波器 2、器件 74LS00 二输入端四与非门 2片 74LS20 四输入端双与非门 1片 74LS86 二输入端四异或门 1片 74LS04 六反相器 1片 三、预习要求 1、复习门电路工作原理相应逻辑表达示。 2、熟悉所有集成电路的引线位置及各引线用途。 3、了解双踪示波器使用方法。 四、实验内容 实验前按学习机使用说明先检查学习机是否正常,然后选择实验用的集成电路,按自己设计的实验接线图接好连线,特别注意Vcc及地线不能接错。线接好后经实验指导教师检查无误方可通电。试验中改动接线须先断开电源,接好线后在通电实验。 1、测试门电路逻辑功能。 (1)选用双输入与非门74LS20一只,插入面包板,按图 连接电路,输入端接S1~S4(电平开关输入插口),输 出端接电平显示发光二极管(D1~D8任意一个)。 (2)将电平开关按表1.1置位,分别测出电压及逻辑状态。(表1.1)

2、异或门逻辑功能测试 (1)选二输入四异或门电路74LS86,按图接线,输入端1﹑2﹑4﹑5接电平开关,输出端A﹑B﹑Y接电平显示发光二极管。 (2)将电平开关按表1.2置位,将结果填入表中。 表 1.2 3、逻辑电路的逻辑关系 (1)选用四二输入与非门74LS00一只,插入面包板,实验电路自拟。将输入输出逻辑关系分别填入表1.3﹑表1.4。

(2)写出上面两个电路的逻辑表达式。 表1.3 Y=A ⊕B 表1.4 Y=A ⊕B Z=AB 4、逻辑门传输延迟时间的测量 用六反相器(非门)按图1.5接线,输80KHz 连续脉冲,用双踪示波器测输入,输出相位差,计算每个门的平均传输延迟时间的tpd 值 : tp d=0.2μs/6=1/30μs 5、利用与非门控制输出。 选用四二输入与非门74LS00一只,插入面包板,输入接任一电平开关,用示波器观察S 对输出脉冲的控制作用: 一端接高有效的脉冲信号,另一端接控制信号。只有控制信号端为高电平时,脉冲信号才能通过。这就是与非门对脉冲的控制作用。 6.用与非门组成其他门电路并测试验证 (1)组成或非门。 用一片二输入端与非门组成或非门 Y = A + B = A ? B 画出电路图,测试并填表1.5 中。 表1.5 图如下: (2)组成异或门 ① 将异或门表达式转化为与非门表达式。 A ⊕B={[(AA)'B]'[A(BB)']}' ② 画出逻辑电路图。 ③ 测试并填表1.6。 表1.6 输入 输出 A B Y 0 1 0 1 0 1 0 0 1 1 A B Y 0 0 0 0 1 1 1 0 1 1 1

数电实验报告(一)

数字电路实验设计报告

实验名称:组合逻辑研究(一)——QuartusⅡ软件的使用 实验目的: 1.学会使用QuartusⅡ软件,运用该软件设计电路原理图。 2.学会用语言设计电路原理图,并会对设计图进行功能和时序 仿真。 3.学会从QuartusⅡ软件中下载原理图到FPGA,测试电路功能。实验仪器: 1.计算机1台 2.数字电路实验板1块 实验内容: 1.利用软件,用原理图输入的方法实现三变量多数表决器电 路,进行功能和时序仿真,记录仿真波形。 2.利用QuartusⅡ软件,用VHDL文本输入的方法实现一位全加 器电路,进行功能和时序仿真,并下载入FPGA,在试验箱上 测试其电路功能。 设计过程及仿真结果: 1.三变量多数表决器原理图

功能仿真波形 时序仿真波形 2.一位全加器的VHDL语言描述 entity add1 is port( A,B,C: in bit; D,S: out bit ); end add1; architecture one of add1 is begin S<=A XOR B XOR C; D<=((A XOR B) AND C) OR (A AND B); end one;

一位全加器功能真值表 验证其功能 功能仿真波形 时序仿真波形

实验结果分析: (1)由仿真结果可以看出,三变量多数表决器电路原理图及一位全加器的VHDL语言描述正确。 (2)由仿真结果可知,功能仿真时对信号的输入没有延迟,而时序仿真时,当多个输入信号在同一时刻处同时发生变化时,此时电路存在竞争,会有冒险,故从仿真图上可以看到毛刺。

数电实验实验报告

[键入文档标题] 实验一组合逻辑电路分析 一.试验用集成电路引脚图 74LS00集成电路74LS20集成电路 四2输入与非门双4输入与非门 二.实验内容 1.实验一 2.实验二 密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开。否则,报警信号为“1”,则接通警铃。试分析密码锁的密码ABCD是什么? ABCD接逻辑电平开关。 最简表达式为:X1=AB’C’D 密码为:1001

A B C D X1 X2 A B C D X1 X2 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 1 1 0 0 1 1 0 0 0 1 0 0 1 1 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 0 1 0 1 0 0 0 1 1 1 0 0 0 1 0 1 0 1 0 1 1 1 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 1 0 1 1 1 0 1 1 1 1 1 0 1 三.实验体会: 1.分析组合逻辑电路时,可以通过逻辑表达式,电路图和真值表之间的相互转换来到达实验所要求的目的。 2.这次试验比较简单,熟悉了一些简单的组合逻辑电路和芯片,和使用仿真软件来设计和构造逻辑电路来求解。 实验二组合逻辑实验(一)半加器和全加器 一.实验目的 1.熟悉用门电路设计组合电路的原理和方法步骤 二.预习内容 1.复习用门电路设计组合逻辑电路的原理和方法步骤。 2.复习二进制数的运算。 3.用“与非门”设计半加器的逻辑图。 4.完成用“异或门”、“与或非”门、“与非”门设计全加器的逻辑图。 5.完成用“异或”门设计的3变量判奇电路的原理图。 三.元件参考 依次为74LS283、 74LS00、74LS51、 74LS136 其中74LS51:Y= (AB+CD)’, 74LS136: Y=A⊕B(OC门)四.实验内容 1.用与非门组成半加器,用或非门、与或非门、与非门组成全加器(电路自拟) 半加器 被加数A i0 1 0 1 0 1 0 1 加数B i0 0 1 1 0 0 1 1 前级进位C i-10 0 0 0 1 1 1 1 和S i0 1 1 0 1 0 0 1

数电实验报告

学生实验实习报告册 学年学期:2019 -2020 学年?春?秋学期 课程名称:数字电路与逻辑设计实验A 实验项目:基于FPGA的数字电子钟的设计与实现 姓名:康勇 学号:2018211580 学院和专业:计算机科学学院计算机科学与技术专业 班级:04911801 指导教师:罗一静 重庆邮电大学教务处制

1.系统顶层模块设计 本项目分为四个模块,分别为分频模块、计时模块、数码管动态显示模块、按键消抖模块。功能包括:基本时钟功能,整点报时功能,手动校时功能,秒表功能,小数点分割时分秒功能等。 设计思路如下: 图表 1数字时钟系统顶层模块设计思路 设计结果: 图表2数字时钟系统顶层模块设计电路图 2.分频模块电路设计及仿真 (1)模块功能

将输入的频率为50MHz的时钟信号利用74390通过2、5、100分频,对输入信号进行逐级分频。 (2)设计思路 图表3分频模块电路设计思路 (3)设计结果(电路) 图表4分频模块电路设计图 图表5模100电路图 (4)测试结果 图表6模100仿真图 图表7模5仿真图

图表8模2仿真图 3.计时模块设计及仿真 本模块主要功能是实现电子时钟计数功能。 图表9计时模块顶层设计电路图 3.1分、秒计时模块(模60计数) (1)模块功能(计数、进位) 电子时钟的分钟位和秒钟位均采用模60计数; 计数功能:从0到59; 进位功能:当计数记到59的时候,输出一个进位信号。 (2)设计思路 模60计数器可以通过一个模6计数器和一个模10计数器组成,由分钟位和秒位的特性可知,可以用模10计数器为个位,模6计数器为十位。当个位到9后,向十位进一。本模块使用器件74160。 计数功能:74160是十进制同步计数器(异步清零),为实现计数功能,首先将74160的LDN 反,CLRN反,ENT,ENP接高位,再接入时钟脉冲信号CLK,即可完成下图左侧(个位)模