ALU的实验verilog例子

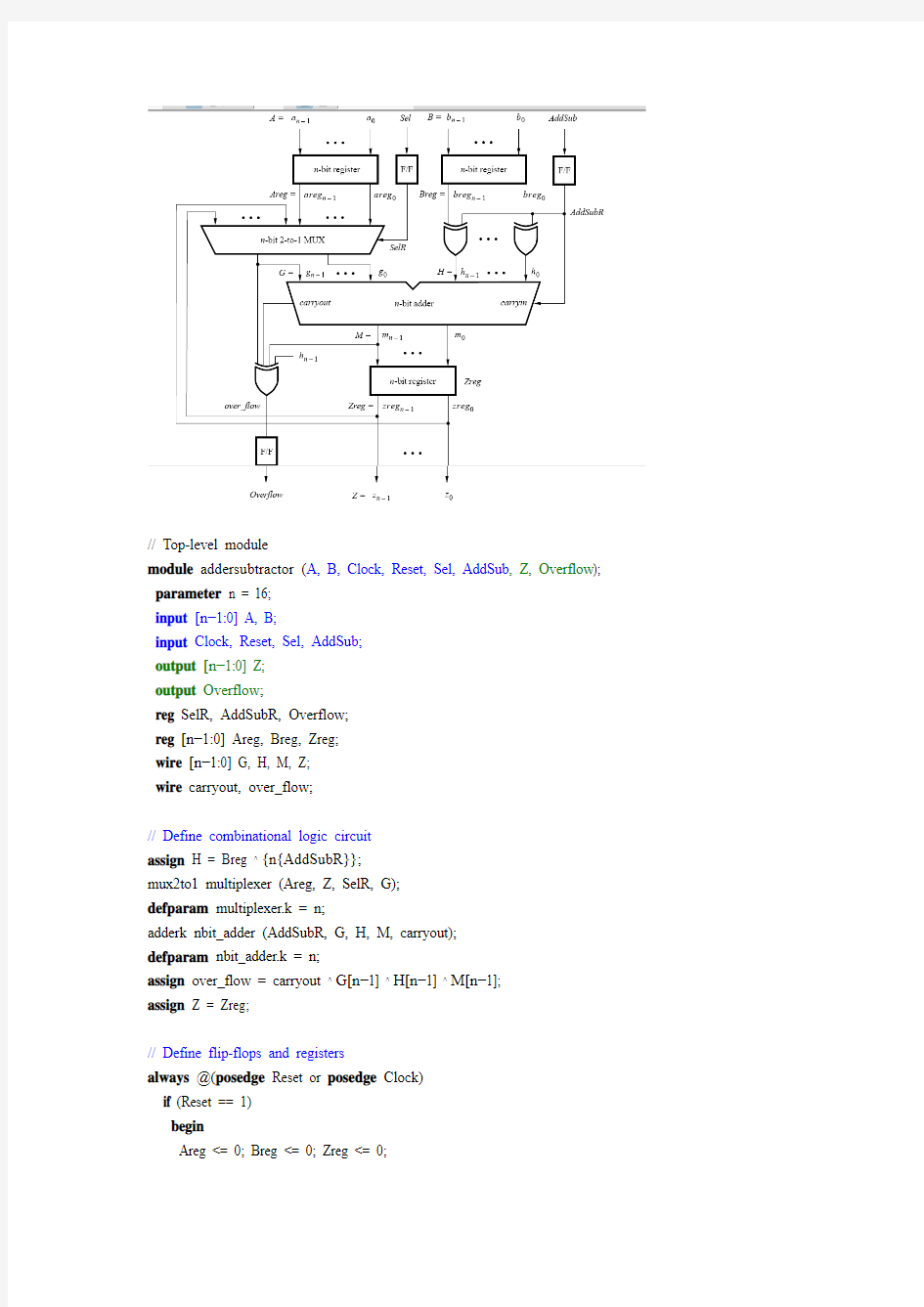

// Top-level module

module addersubtractor (A, B, Clock, Reset, Sel, AddSub, Z, Overflow); parameter n = 16;

input [n?1:0] A, B;

input Clock, Reset, Sel, AddSub;

output [n?1:0] Z;

output Overflow;

reg SelR, AddSubR, Overflow;

reg [n?1:0] Areg, Breg, Zreg;

wire [n?1:0] G, H, M, Z;

wire carryout, over_flow;

// Define combinational logic circuit

assign H = Breg ^ {n{AddSubR}};

mux2to1 multiplexer (Areg, Z, SelR, G);

defparam multiplexer.k = n;

adderk nbit_adder (AddSubR, G, H, M, carryout);

defparam nbit_adder.k = n;

assign over_flow = carryout ^ G[n?1] ^ H[n?1] ^ M[n?1];

assign Z = Zreg;

// Define flip-flops and registers

always @(posedge Reset or posedge Clock)

if (Reset == 1)

begin

Areg <= 0; Breg <= 0; Zreg <= 0;

SelR <= 0; AddSubR <= 0; Overflow <= 0;

end

else

begin

Areg <= A; Breg <= B; Zreg <= M;

SelR <= Sel; AddSubR <= AddSub; Overflow <= over_flow; end

endmodule

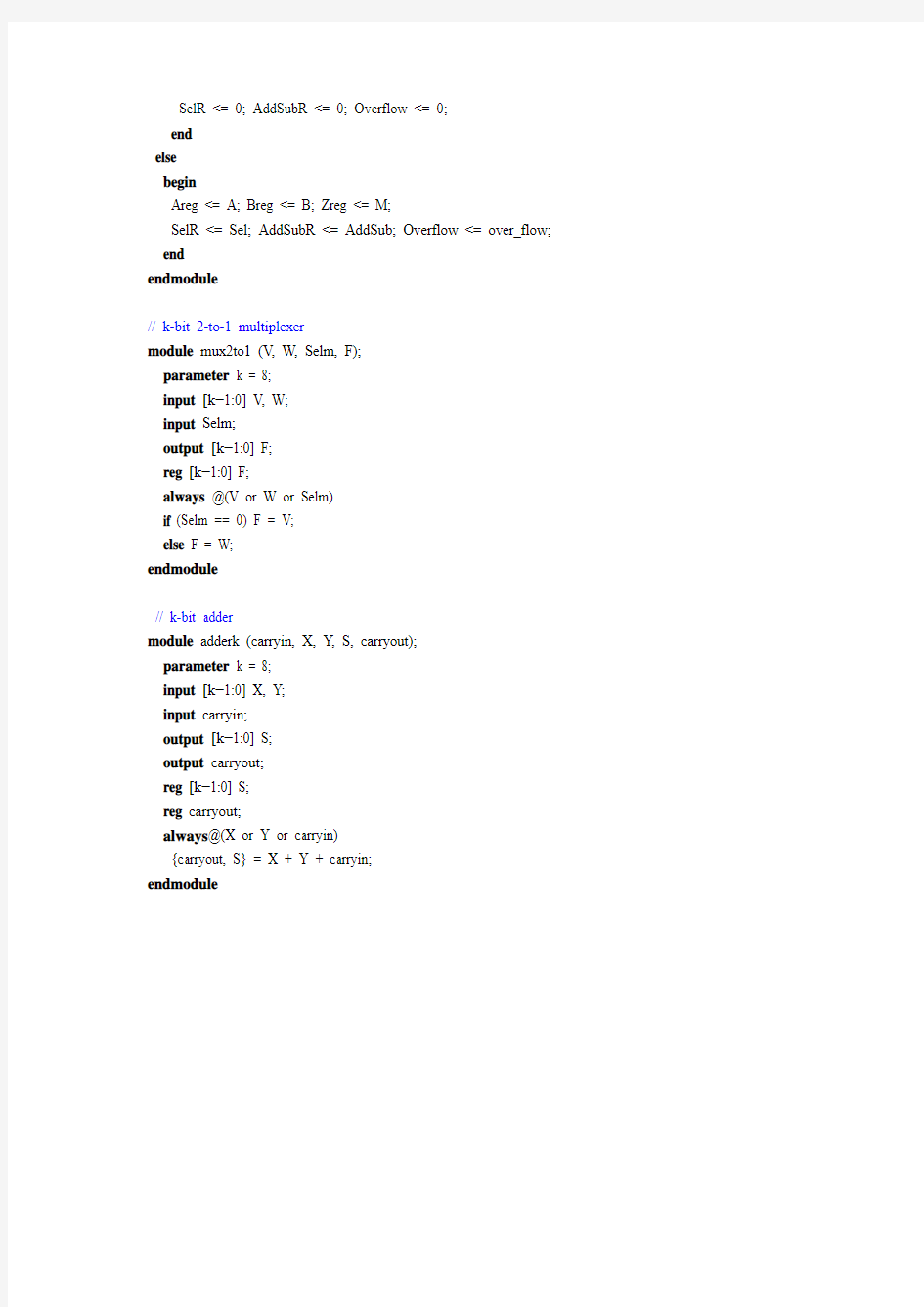

// k-bit 2-to-1 multiplexer

module mux2to1 (V, W, Selm, F);

parameter k = 8;

input [k?1:0] V, W;

input Selm;

output [k?1:0] F;

reg [k?1:0] F;

always @(V or W or Selm)

if (Selm == 0) F = V;

else F = W;

endmodule

// k-bit adder

module adderk (carryin, X, Y, S, carryout);

parameter k = 8;

input [k?1:0] X, Y;

input carryin;

output [k?1:0] S;

output carryout;

reg [k?1:0] S;

reg carryout;

always@(X or Y or carryin)

{carryout, S} = X + Y + carryin;

endmodule

AD转换verilog程序

// 16-bit Analogue-Digital Converter // // +-----------------------------+ // | Copyright 1996 DOULOS | // | designer : Tim Pagden | // | opened: 7 Jun 1996 | // +-----------------------------+ `timescale 1 ns / 1 ps module ADC_16bit (analog_in,digital_out); parameter conversion_time = 25.0, // conversion_time in ns // (see `timescale above) charge_limit = 1000000; // = 1 million input[63:0] analog_in; // double-precision representation of a real-valued input port; a fix that enables // analog wires between modules to be coped with in Verilog. // Think of input[63:0]

verilog综合心得

综合:不可综合的运算符:= = = ,!= =,/(除法),%(取余数)。 1、不使用初始化语句。 2、不使用带有延时的描述。 3、不使用循环次数不确定的循环语句,如:forever、while等。 4、尽量采用同步方式设计电路。 5、除非是关键路径的设计,一般不调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 6、用always过程块描述组合逻辑,应在信号敏感列表中列出所有的输入信号。 7、所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 8、在verilog模块中,任务(task)通常被综合成组合逻辑的形式,每个函数(function)在调用时通常也被综合为一个独立的组合电路模块。 9、用户自定义原语(UDP)是不可综合的,它只能用来建立门级元件的仿真模型。 一般综合工具支持的V erilog HDL结构

移位运算符:V erilog HDL提供向右(>>)及向左(<<)两种运算符,运算符高位或地位一旦移出即予丢弃,其空缺的位则予以补零。 连续赋值语句(assign)、case语句、if…else语句都是可以综合的 initial 语句内若包含有多个语句时,必须以begin end 作聚合;单一的初值赋值,因此并不需以begin end做聚合。 循环(Loops)并不能单独地在程序中存在,而必须在initial和always块中才能使用。initial过程块中的语句仅执行一次,而always块中的语句是不断重复执行的。 编写顶层模块的注意事项 每个端口除了要声明是输入、输出还是双向外,还要声明其数据类型,是连线型(wire)还是寄存器型(reg),如果没有声明则综合器默认为wire型。 1、输入和双向端口不能声明为寄存器型。 2、在测试模块中不需要定义端口。 编写testbentch所归纳的心得

VerilogHDL经典程序非常适合新手

一、2线-4线译码器 module counter4(q1,q0,ncr,cp); input cp,ncr; output q1,q0; reg q1,q0; always@(posedge cp or negedge ncr) begin if(~ncr){q1,q0}<=2'b00; else{q1,q0}<={q1,q0}+1'b1; end endmodule 二、4选1数据选择器 module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0; output y; reg y; always@(a1or a0) begin case({a1,a0}) 2'b00:y=i0; 2'b01:y=i1; 2'b10:y=i2; 2'b11:y=i3; default:y=0; 一、2线-4线译码器 module counter4(q1,q0,ncr,cp); input cp,ncr; output q1,q0; reg q1,q0; always@(posedge cp or negedge ncr) begin if(~ncr){q1,q0}<=2'b00; else{q1,q0}<={q1,q0}+1'b1; end endmodule 二、4选1数据选择器 module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0; output y; reg y; always@(a1or a0) begin case({a1,a0}) 2'b00:y=i0;

原创:VHDL verilog 互相调用的例子

给两个例子, 一个是VHDL做顶层调用verilog 一个是verilog 做顶层调用VHDL VHDL调用verilog: module sync_block #( parameter INITIALISE = 2'b00 ) ( input clk, // clock to be sync'ed to input data_in, // Data to be 'synced' output data_out // synced data ); //VHD entity dcm_reset is port( ref_reset : in std_logic; -- Synchronous reset in ref_clk domain ref_clk : in std_logic; -- Reliable reference clock of known frequency (125MHz) dcm_locked : in std_logic; -- The DCM locked signal dcm_reset : out std_logic -- The reset signal which should be connected to the DCM ); end dcm_reset; component sync_block port ( clk : in std_logic; -- clock to be sync'ed to data_in : in std_logic; -- Data to be 'synced' data_out : out std_logic -- synced data ); end component; dcm_locked_sync_tx : sync_block port map( clk => ref_clk, data_in => dcm_locked, data_out => dcm_locked_sync ); verilog调用VHDL:(目标还是上述VHDL模块) module gmii_if ( …… ); dcm_reset rx_dcm_reset ( .ref_reset (tx_reset), .ref_clk (tx_clk),

Verilog HDL编程举例

设计示范和上机习题 练习一.简单的组合逻辑设计 //(方法一): //---------------文件名compare.v ----------------- module compare(equal,a,b); input a,b; output equal; assign equal = (a==b)? 1 : 0; //a等于b时,equal输出为1;a不等于b时,equal输出为0。endmodule //(方法二): module compare(equal,a,b); input a,b; output equal; reg equal; always @(a or b) if(a==b) //a等于b时,equal输出为1; equal =1; else //a不等于b时,equal输出为0。 equal = 0; //思考:如果不写else 部分会产生什么逻辑?

endmodule //------------------------------------------------------------- //----------测试模块源代码(方法之一): `timescale 1ns/1ns // 定义时间单位。 `include "./compare.v" // 包含模块文件。在有的仿真调试环境中并不需要此语句。 //而需要从调试环境的菜单中键入有关模块文件的路径和名称 module t; reg a,b; wire equal; initial // initial常用于仿真时信号的给出。 begin a=0; b=0; #100 a=0; b=1; #100 a=1; b=1; #100 a=1; b=0; #100 a=0; b=0; #100 $stop; //系统任务,暂停仿真以便观察仿真波

非常好的Verilog设计经验谈

时序是设计出来的 我的boss有在华为及峻龙工作的背景,自然就给我们讲了一些华为及altera 做逻辑的一些东西,而我们的项目规范,也基本上是按华为的那一套去做。在工作这几个月中,给我感触最深的是华为的那句话:时序是设计出来的,不是仿出来的,更不是湊出来的。 在我们公司,每一个项目都有很严格的评审,只有评审通过了,才能做下一步的工作。以做逻辑为例,并不是一上来就开始写代码,而是要先写总体设计方案和逻辑详细设计方案,要等这些方案评审通过,认为可行了,才能进行编码,一般来说这部分工作所占的时间要远大于编码的时间。 总体方案主要是涉及模块划分,一级模块和二级模块的接口信号和时序(我们要求把接口信号的时序波形描述出来)以及将来如何测试设计。在这一级方案中,要保证在今后的设计中时序要收敛到一级模块(最后是在二级模块中)。什么意思呢?我们在做详细设计的时候,对于一些信号的时序肯定会做一些调整的,但是这种时序的调整最多只能波及到本一级模块,而不能影响到整个设计。记得以前在学校做设计的时候,由于不懂得设计时序,经常因为有一处信号的时序不满足,结果不得不将其它模块信号的时序也改一下,搞得人很郁闷。 在逻辑详细设计方案这一级的时候,我们已经将各级模块的接口时序都设计出来了,各级模块内部是怎么实现的也基本上确定下来了。 由于做到这一点,在编码的时候自然就很快了,最重要的是这样做后可以让设计会一直处于可控的状态,不会因为某一处的错误引起整个设计从头进行。 ==================================================================== 如何提高电路工作频率 对于设计者来说,我们当然希望我们设计的电路的工作频率(在这里如无特别说明,工作频率指FPGA片内的工作频率)尽量高。我们也经常听说用资源换速度,用流水的方式可以提高工作频率,这确实是一个很重要的方法,今天我想进一步去分析该如何提高电路的工作频率。 我们先来分析下是什么影响了电路的工作频率。 我们电路的工作频率主要与寄存器到寄存器之间的信号传播时延及 clock skew有关。在FPGA内部如果时钟走长线的话,clock skew很小,基本上可以忽略, 在这里为了简单起见,我们只考虑信号的传播时延的因素。 信号的传播时延包括寄存器的开关时延、走线时延、经过组合逻辑的时延(这样划分或许不是很准确,不过对分析问题来说应该是没有可以的),要提高电路的工作频率,我们就要在这三个时延中做文章,使其尽可能的小。 我们先来看开关时延,这个时延是由器件物理特性决定的,我们没有办法去改变,所以我们只能通过改变走线方式和减少组合逻辑的方法来提高工作频率。

verilog程序-60进制计数器

module count60_dongtai_LED ( input clk, input rest_n, output reg [2:0] sel, //位选 output reg [6:0] display ); reg [15:0] count_clk; // 分频计数器,最大2^16=64K分频 reg [5:0] sum_num; //计数缓存器,2^6=64 reg [3:0] g_bit; //个位 reg [3:0] s_bit; //十位 reg [3:0] disp_temp; //分频 always @ (posedge clk or negedge rest_n) begin if(rest_n ==0) begin count_clk=16'b0; end else begin if(count_clk==16'hffff) begin count_clk=16'b0; end else begin count_clk=count_clk+1'b1; end end end // 60进制计数 always @ (negedge count_clk[3] or negedge rest_n) begin // clk_clk[3] 对"clk" 16分频if(rest_n ==0) begin g_bit=4'b0; s_bit=4'b0; sum_num=6'b0; end else begin if (sum_num==6'd59) begin sum_num=6'b0; end else begin sum_num=sum_num+1'b1; end end s_bit=(sum_num/10)%10;

VerilogHDL实例

本文档含有很多Verilog HDL例子://与门 module zxhand2(c,a,b); input a,b; output c; assign c= a & b; endmodule //或门 module zxhor2(c,a,b); input a,b; output c; assign c= a | b; endmodule //非门 module zxhnot2(c,b); input b; output c; assign c=~ b; endmodule ////异或门 module zxhxro2(c,a,b); input b; output c; assign c=a ^ b; endmodule 两选一电路 module data_scan(d0,d1,sel,q); output q; input d0,d1,sel; wire t1,t2,t3; n1 zxhand2(t1,d0,sel); n2 zxhnot2 (t4,sel); n3 zxhand2(t2,d1,t4); n4 zxhor2(t3,t1,t2);

assign q=t1; endmodule verilog HDL实例(一) 练习一.简单的组合逻辑设计 目的: 掌握基本组合逻辑电路的实现方法。 这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。在Verilog HDL中,描述组合逻辑时常使用assign结构。注意 equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。 模块源代码: //--------------- compare.v ----------------- module compare(equal,a,b); input a,b; output equal; assign equal=(a==b)?1:0; //a等于b时,equal输出为1;a不等于b时, //equal输出为0。 endmodule 测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号和输出信号,如果发现结果与预期的有所偏差,则要对设计模块进行修改。 测试模块源代码: `timescale 1ns/1ns //定义时间单位。 module comparetest; reg a,b; wire equal; initial //initial常用于仿真时信号的给出。 begin a=0; b=0; #100 a=0; b=1; #100 a=1; b=1; #100 a=1; b=0; #100 $stop; //系统任务,暂停仿真以便观察仿真波形。 end compare compare1(.equal(equal),.a(a),.b(b)); //调用模块。 Endmodule

Verilog程序(汉字点阵显示

中国石油大学 数电课程设计报告题目: 学院: 班级: 姓名: 学号: 日期: 2012 年 12月

摘要 设计要求: 利用EDA/SOPC 实验开发平台提供的16*16点阵LED以及EPC235核心板,实现循环显示“中国石油大学”这6个汉字(左移或者右移均可)。 (1)手动生成“中国石油大学”这6个汉字在16*16点阵LED 上的6个字模(即控制某些LED亮,某些LED灭)。 (2)实现循环显示“中国石油大学”这6个汉字(左移或者右移均可)。 (3)拓展要求:自主设计(如控制循环速度,方向)。 关键词: 扫描分频,控制速度,点阵,点阵汉字显示,

设计原理及方案: 1、16*16点阵LED内部结构如下图所示。 2、总体设计框图: 3、各子模块的设计: (1)、分频,扫描: module fenpin (clk_50Mhz,clk_4hz,k2,k3); input clk_50Mhz,k2,k3; // 输入端口声明

output clk_4hz; // 输出端口声明reg[24:0] count,ccount; reg clk_4hz; always @(posedge clk_50Mhz) begin if ((k2==0) && (k3==0)) ccount<=500000000; if ((k2==0) && (k3==1)) ccount<=100000000; if ((k2==1) && (k3==0)) ccount<=50000000; if ((k2==1) && (k3==1)) ccount<=10000000; if(count 一、组合逻辑实验 (2) 实验13X8译码器程序 (2) 实验2二-十进制译码器 (2) 实验3BCD码—七段数码管显示译码器 (3) 实验48-3编码器 (4) 实验58-3优先编码器 (4) 实验6十—二进制编码器 (5) 实验7三选一数据选择器 (5) 实验8半加器 (6) 实验9全加器 (7) 实验10半减器 (8) 实验11全减器 (8) 实验12多位数值比较器 (9) 实验13奇偶校验 (9) 实验14补码生成 (10) 实验158位硬件加法器的设计 (10) 实验164位并行乘法器 (10) 实验17七人表决器 (10) 实验18格雷码变换 (11) 二、时序逻辑实验 (11) 实验1D触发器 (11) 实验2JK触发器 (12) 实验3四位移位寄存器 (12) 实验4异步计数器 (13) 实验5同步计数器 (14) 实验6可逆计数器 (15) 实验7步长可变的加减计数器 (16) 实验8含异步清0和同步时钟使能的4位加法计数器 (17) 实验9顺序脉冲发生器 (18) 实验10序列信号发生器 (18) 实验11用状态机实现串行数据检测器 (19) 实验12分频器 (20) 实验13Moore状态机 (21) 实验14Mealy状态机 (23) 实验15三层电梯 (24) 实验16性线反馈移位寄存器(LFSR)设计 (32) 实验17正负脉宽数控调制信号发生器 (32) 三、存储器设计 (34) 实验1只读存储器(ROM) (34) 实验2SRAM (34) 实验3FIFO (35) 四、扩展接口实验 (39) 实验1流水灯 (39) 实验2VGA彩色信号显示控制器设计 (40) 个人总结Verilog编程27条经验 1.强烈建议用同步设计; 2.在设计时总是记住时序问题; 3.在一个设计开始就要考虑到地电平或高电平复位、同步或异步复位、上升沿 或下降沿触发等问题,在所有模块中都要遵守它; 4.在不同的情况下用if和case,最好少用if的多层嵌套(1层或2层比较合 适,当在3层以上时,最好修改写法,因为这样不仅可以reduce area,而且可以获得好的timing); 5.在锁存一个信号或总线时要小心,对于整个design,尽量避免使用latch, 因为在DFT时很难test; 6.确信所有的信号被复位,在DFT时,所有的FlipFlop都是controllable; 7.永远不要再写入之前读取任何内部存储器(如SRAM); 8.从一个时钟到另一个不同的时钟传输数据时用数据缓冲,他工作像一个双时 钟FIFO(是异步的),可以用Async SRAM搭建Async FIFO; 9.在VHDL中二维数组可以使用,它是非常有用的。在VERILOG中他仅仅可以使 用在测试模块中,不能被综合; 10.遵守register-in register-out规则; 11.像synopsys的DC的综合工具是非常稳定的,任何bugs都不会从综合工具中 产生 12.确保FPGA版本与ASIC的版本尽可能的相似,特别是SRAM类型,若版本一致 是最理想的,但是在工作中FPGA版本一般用FPGA自带的SRAM,ASIC版本一般用厂商提供的SRAM; 13.在嵌入式存储器中使用BIST; 14.虚单元和一些修正电路是必需的; 15.一些简单的测试电路也是需要的,经常在一个芯片中有许多测试模块; 16.除非低功耗不要用门控时钟,强烈建议不要在design中使用gate clock; 17.不要依靠脚本来保证设计。但是在脚本中的一些好的约束能够起到更好的性 能(例如前向加法器); 18.如果时间充裕,通过时钟做一个多锁存器来取代用MUX; 19.不要用内部tri-state, ASIC需要总线保持器来处理内部tri-state,如IO cell; 20.在top level中作pad insertion; 21.选择pad时要小心(如上拉能力,施密特触发器,5伏耐压等),选择合适的 IO cell; 22.小心由时钟偏差引起的问题; 23.不要试着产生半周期信号; 24.如果有很多函数要修正,请一个一个地作,修正一个函数检查一个函数; 25.在一个计算等式中排列每个信号的位数是一个好习惯,即使综合工具能做; 26.不要使用HDL提供的除法器; 27.削减不必要的时钟。它会在设计和布局中引起很多麻烦,大多数FPGA有1- 4个专门的时钟通道; 【例3.1】4位全加器 module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 【例3.2】4位计数器 module count4(out,reset,clk); output[3:0] out; input reset,clk; reg[3:0] out; always @(posedge clk) begin if (reset) out<=0; //同步复位 else out<=out+1; //计数 end endmodule 【例3.3】4位全加器的仿真程序 `timescale 1ns/1ns `include "adder4.v" module adder_tp; //测试模块的名字 reg[3:0] a,b; //测试输入信号定义为reg型 reg cin; wire[3:0] sum; //测试输出信号定义为wire型 wire cout; integer i,j; adder4 adder(sum,cout,a,b,cin); //调用测试对象 always #5 cin=~cin; //设定cin的取值 initial begin a=0;b=0;cin=0; for(i=1;i<16;i=i+1) #10 a=i; //设定a的取值 end - 1 - initial begin for(j=1;j<16;j=j+1) #10 b=j; //设定b的取值 end initial//定义结果显示格式 begin $monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum); #160 $finish; end endmodule 【例3.4】4位计数器的仿真程序 `timescale 1ns/1ns `include "count4.v" module coun4_tp; reg clk,reset; //测试输入信号定义为reg型 wire[3:0] out; //测试输出信号定义为wire型 parameter DELY=100; count4 mycount(out,reset,clk); //调用测试对象 always #(DELY/2) clk = ~clk; //产生时钟波形 initial begin//激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end //定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule 【例3.5】“与-或-非”门电路 module AOI(A,B,C,D,F); //模块名为AOI(端口列表A,B,C,D,F) input A,B,C,D; //模块的输入端口为A,B,C,D output F; //模块的输出端口为F - 2 - /* AD0809 module v1.0 work up to 5M sample = 25us 40khz for normal clk = 2.5M sample = 30us 33khz */ module ad0809( clkin, adclk, eoc, st, ale, datain, oe, dataout ); input clkin; input eoc; input [7:0]datain; output st; output ale; output oe; output adclk; output [7:0]dataout; reg adclk; reg [7:0]dataout; reg st; reg oe; reg ale; //frequence divider for AD parameter Div_adclk = 8'd9;//(9+1)*2=20 adclk=2.5M parameter Div_clk_state = 4'd4;//(4+1)*2=10 clk_state=5M reg [8:0]div_cnt_ad;//frequence div cnt reg [3:0]div_cnt_state; reg clk_state; always@(negedge clkin)begin if(div_cnt_ad != Div_adclk) div_cnt_ad <= div_cnt_ad + 1'b1; else begin div_cnt_ad <= 0; adclk <= ~adclk; end if(div_cnt_state != Div_clk_state) div_cnt_state <= div_cnt_state + 1'b1; else begin div_cnt_state <= 0; clk_state <= ~clk_state; end end /*AD convert*/ reg [3:0]state; reg [7:0]delay; initial begin state <= 4'd0; end always@(negedge clk_state)begin case(state) 4'd0:begin //clear all st <= 1'b0; oe <= 1'b0; ale <= 1'b0; verilog学习心得 1.数字电路基础知识:布尔代数、门级电路的内部晶体管结构、组合逻辑电路分析与设计、触发器、时序逻辑电路分析与设计 2.数字系统的构成:传感器AD 数字处理器DA 执行部件 3.程序通在硬件上的执行过程: C语言(经过编译)-->该处理器的机器语言(放入存储器)-->按时钟的节拍,逐条取出指令、分析指令、执行指令 4.DSP处理是个广泛概念,统指在数字系统中做的变换(DFT)、滤波、编码解码、加密解密、压缩解压等处理 5.数字处理器包括两部分:高速数据通道接口逻辑、高速算法电路逻辑 6.当前,IC产业包括IC制造和IC设计两部分,IC设计技术发展速度高于IC设计 7.FPGA设计的前续课程:数值分析、DSP、C语言、算法与数据结构、数字电路、HDL语言计算机微体系结构 8.数字处理器处理性能的提高:软件算法的优化、微体系结构的优化 9.数字系统的实现方式: 编写C程序,然后用编译工具得到通用微处理器的机器指令代码,在通用微处理器上运行(如8051/ARM/PENTUIM) 专用DSP硬件处理器 用FPGA硬件逻辑实现算法,但性能不如ASIC 用ASIC实现,经费充足、大批量的情况下使用,因为投片成本高、周期长 10.FPGA设计方法:IP核重用、并行设计、层次化模块化设计、top-down思想 FPGA设计分工:前端逻辑设计、后端电路实现、仿真验证 11.matlab的应用: matlab中有许多现成的数学函数可以利用,节省了复杂函数的编写时间 matlab可以与C程序接口 做算法仿真和验证时能很快生成有用的数据文件和表格 DSP builder可以直接将simulink模型转换成HDL代码,跳过了中间的C语言改写步骤 12.常规从算法到硬件电路的开发过程: 算法的开发 C语言的功能描述 并行结构的C语言改写 verilog的改写 仿真、验证、修正 综合、布局布线、投入实用 13.C语言改写成verilog代码的困难点: 并行C语言的改写,因为C本身是顺序执行,而不是并行执行 不使用C语言中的复杂数据结构,如指针 目前有将C语言转换成verilog的工具? 14.HDL HDL描述方法是从电路图描述方法演化来的,相比来说更容易修改 符合IEEE标准的有verilog HDL和VHDL VHDL由美国国防部开发,有1987和1993两个版本 verilog由cadence持有,有1995、2001、2005三个版本 verilog较VHDL更有前景:具有模拟电路描述能力、不仅可以开发电路还可以验证电路、门级以下描述比VHDL强 Verilog HDL Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象 设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。 Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。 Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操作符和结构。Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。 =============================== 中文版Verilog HDL简明教程:第1章简介 Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。 Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。 Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操作符和结构。Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。 历史 Verilog HDL语言最初是于1983年由Gateway Design Automation公司为其模 几个常用的Verilog小程序 (1) 8位串并转换 module haidaoqi(clk,rst,din,dout); input clk,rst,din; output [7:0] dout; reg[7:0] data,dout; reg[2:0] cnt; always@(posedge clk or posedge rst) if(rst) //复位高有效 data <=8'b0; else data<= {data[7:0],din};//din是输入串行数据,假设输入数据高位在前 //这是一个移位寄存器 always@(posedge clk or posedge rst) if(rst) cnt <= 3'b0; else if(cnt == 3'b111) cnt <= 3'b0; else cnt <= cnt +1;//计数器,用来计算移位次数,移位8次在以 后产生一个有效数据 always@(posedge clk or posedge rst) if(rst) dout <= 8'b0; else if(cnt == 3'b111) dout <= data;//如果计数器记到7,那么输出一个有效的8位数据 else dout <= 0; endmodule (2) 8 位数据寄存器 module reg8(out_data,in_data,clk,clr); output[7:0] out_data; input[7:0] in_data; input clk,clr; reg[7:0] out_data; always @(posedge clk or posedge clr) begin 1.设计一个产生010*******的序列信号发生器。module generator(out,clk,state); output [3:0]state; output out; input clk; reg [3:0]state; reg out; always@(posedge clk) begin if(state==9) state<=0; else state<=state+1; case(state) 4'b0000:out<=0; 4'b0001:out<=1; 4'b0010:out<=0; 4'b0011:out<=0; 4'b0100:out<=1; 4'b0101:out<=0; 4'b0110:out<=0; 4'b0111:out<=1; 4'b1000:out<=1; 4'b1001:out<=1; default:out<=0; endcase end endmodule 2.设计一个8位的加减计数器。时钟信号为clk,同步清零信号为rst。Clk上升沿时刻,当inc=1计数器加二,其他情况计数器保持不变。 module counter(rst,clk,q,inc,dec); input rst,clk,inc,dec; output [7:0]q; reg [7:0]q; always@(posedge clk) if(rst) q<=0; else case({inc,dec}) 2'b10:begin if(q==254) q<=0;else q<=q+2;end// 2'b01:begin if(q==0) q<=254;else q<=q-2;end// default:q<=q; endcase jtag的经典例子 module jtag(TCK,TMS, TDI, PROGRAM_COUNT, SFR_DATA, SOURCE_DI, XRAMDI, PROGDI, TRESET, SCLK, //Output TDO, //SOURCE_AJ, DESTIN_AJ, XRAMAJ, PROGAJ, DESTIN_DOJ, XRAMDOJ, PROGRAM_COUNTJ, PROGDOJ, NXRAMRJ, nXRAMWJ, NPSENJ ,PROGWE, SFR_WRITEJ, Write_SFR, Read_SFR , Read_RAM, NDESTIN_WEJ, nDESTIN_WEJ, Write_PC, ICReset,ICDisable,ICClock_Disable,ICClock_Enable ); //Input input TCK; input TMS; input TDI; input TRESET; input SCLK; //IC stop feedback signal at step_into state input [15:0] PROGRAM_COUNT; //present PC value input [7:0] SFR_DATA; input [7:0] SOURCE_DI; input [7:0] XRAMDI; input [7:0] PROGDI; //Output output ICReset; output ICDisable; output ICClock_Disable; output TDO; //output [7:0] SOURCE_AJ; //output [15:0] XRAMAJ; //output [15:0] PROGAJ; //output [7:0] DESTIN_DOJ; //output [7:0] XRAMDOJ; //output [7:0] PROGDOJ; //output [15:0] PROGRAM_COUNTJ; output Write_PC; output NXRAMRJ; output nXRAMWJ;//NXRAMWJ, output NPSENJ; module antitwitter (clock,keyin,keyout; input clock,keyin; output keyout; reg [3:0] count; reg keyout; always @(posedge clock begin if ( keyin == 1 begin count <= count +4'h1; if (count <= 8 keyout<= 1'b0; else begin keyout <= keyin; count <= 4'h9; end end else begin count <= 4'h0; keyout <= 1'b0; end end endmodule module discode38(g1,g2a,g2b,a,b,c,y; input g1,g2a,g2b,a,b,c; output [7:0] y; reg [7:0] y; always @(g1 or g2a or g2b or a or b or c // 当输入信号有变化时,执行块语句begin if ( (g1==1&&(g2a==0&&(g2b==0 // 门控信号满足条件时,输出有效begin case ( {c,b,a} 3'b000 : y <=8'b11111110; 3'b001 : y <=8'b11111101; 3'b010 : y <=8'b11111011; 3'b011 : y <=8'b11110111; 3'b100 : y <=8'b11101111; 3'b101 : y <=8'b11011111;verilog_FPGA实例

个人总结FPGA设计中Verilog编程的27条经验

Verilog的135个经典设计实例

ADDA等一些芯片的verilog程序

verilog学习心得

Verilog语言基础教程

几个常用的Verilog小程序

verilog语言基本程序

jtag的经典例子,verilog

Verilog程序解析