利用verilog硬件语言设计一个数字频率计电路

用verilog HDL设计的4位频率计

简单4位数字频率计设计一、 设计要求(1)、利用Verilog HDL 语言行为描述方法,设计一个简单的4位数字频率计; (2)、要求输入标准时钟信号频率为1MHz ,系统可计数频率范围为1Hz~9999Hz ; (3)、系统具有复位信号,且当计数频率发生溢出时能够给出指示信号,计数的频率通过4个共阴数码管进行显示(动态扫描显示)。

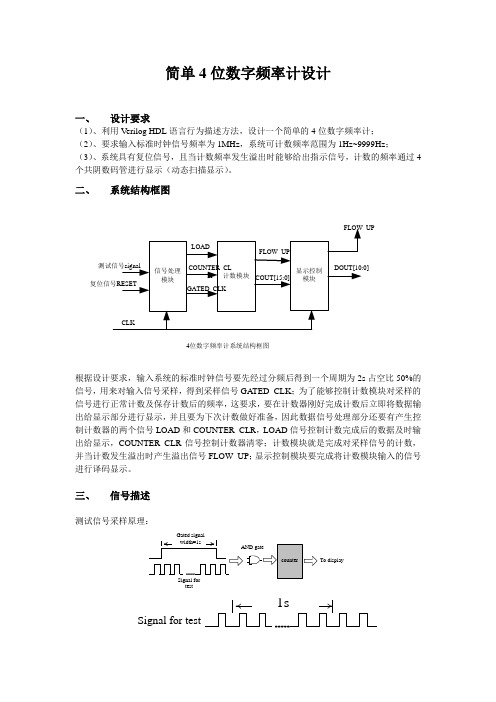

二、 系统结构框图4位数字频率计系统结构框图根据设计要求,输入系统的标准时钟信号要先经过分频后得到一个周期为2s 占空比50%的信号,用来对输入信号采样,得到采样信号GA TED_CLK ;为了能够控制计数模块对采样的信号进行正常计数及保存计数后的频率,这要求,要在计数器刚好完成计数后立即将数据输出给显示部分进行显示,并且要为下次计数做好准备,因此数据信号处理部分还要有产生控制计数器的两个信号LOAD 和COUNTER_CLR ,LOAD 信号控制计数完成后的数据及时输出给显示,COUNTER_CLR 信号控制计数器清零;计数模块就是完成对采样信号的计数,并当计数发生溢出时产生溢出信号FLOW_UP ;显示控制模块要完成将计数模块输入的信号进行译码显示。

三、 信号描述测试信号采样原理:Signal for testTo displaySignal for testGA TED_CLK 、LOAD 、COUNTER_CLR 信号的关系:COUNTER_CLRGATED_CLKLOAD四、 Verilog 程序各子模块verilog 程序:(1)信号处理模块_verilog : moduleFREQUENCY_COUNTROL_BLOCK(GATED_CLK,LOAD,COUNTER_CLR,CLK_IN,SIGNA L_TEST,RESET); output GATED_CLK; output LOAD; output COUNTER_CLR; input CLK_IN; input SIGNAL_TEST; input RESET; reg LOAD; reg COUNTER_CLR; reg DIVIDE_CLK; reg[19:0] cn; reg A1,A2;//信号分频:由CLK_IN 得到分频后的信号DIVIDE_CLK(0.5Hz) always @(posedge CLK_IN) begin if(RESET) begin DIVIDE_CLK<=0; cn<=0;endelse if(cn==1000000)begincn<=0;DIVIDE_CLK<=~DIVIDE_CLK;endelsecn<=cn+1;end//频率计数控制信号的产生:产生LOAD信号和COUNTER_CLR信号always @(posedge SIGNAL_TEST)beginA1<=~DIVIDE_CLK;endalways @(posedge SIGNAL_TEST)beginA2=A1;endalways @(A1 or A2)beginLOAD=A1&&(!A2);endalways @(posedge SIGNAL_TEST)COUNTER_CLR=LOAD;//产生驱动计数模块的信号GATED_CLK,也就是被计数模块检测的信号assign GATED_CLK=SIGNAL_TEST&DIVIDE_CLK;endmodule(2)、计数器模块:moduleFREQUENCY_COUNTER_BLOCK(COUT,FLOW_UP,CLOCK_IN,RESET,LOAD,COUNTER _CLR);output[15:0] COUT;output FLOW_UP;input CLOCK_IN;input LOAD;input COUNTER_CLR;input RESET;reg[15:0] TEMP;reg FLOW_UP;parameter B_SIZE=16; //二进制位宽,为便于移植,所有定义了成参数reg[B_SIZE+3:0] bcd; //转换后的BCD码的位数要比二进制多4位reg[B_SIZE-1:0] binary;reg[B_SIZE-1:0] bin;reg[B_SIZE+3:0] result;//计数器完成计数得到二进制表示的频率数值always @(CLOCK_IN or RESET or LOAD or COUNTER_CLR)beginif(RESET|COUNTER_CLR)beginTEMP<=0;FLOW_UP<=0;endelse if(LOAD)binary<=TEMP;else if(TEMP>9999)beginFLOW_UP<=1;binary<=9999;endelseif(CLOCK_IN)TEMP<=TEMP+1;end//将二进制表示(或十六进制表示)的数转换为BCD码的形式,便于数码管译码显示always @(binary or RESET)beginbin=binary;result=0;if(RESET)bcd<=0;elsebeginrepeat(B_SIZE-1)beginresult[0]=bin[B_SIZE-1];if(result[3:0]>4)result[3:0]=result[3:0]+4'd3;if(result[7:4]>4)result[7:4]=result[7:4]+4'd3;if(result[11:8]>4)result[11:8]=result[11:8]+4'd3;if(result[15:12]>4)result[15:12]=result[15:12]+4'd3;if(result[19:16]>4)result[19:16]=result[19:16]+4'd3;result=result<<1;bin=bin<<1;endresult[0]=bin[B_SIZE-1];bcd<=result;endendassign COUT=bcd[15:0];endmodule(3)信号显示处理:module FREQUENCY_DISPL Y_BLOCK(DOUT,DCLK_IN,RESET,CDIN);output[10:0] DOUT;input[15:0] CDIN;input DCLK_IN;input RESET;reg[10:0] DOUT;reg[3:0] Temp1;reg[1:0] cn;always @(posedge DCLK_IN) //设置成动态扫描beginif(RESET)cn<=0;elsebegincn<=cn+1;case(cn)2'b00: begin DOUT[10:7]<=4'b0001; Temp1<=CDIN[3:0];end2'b01: begin DOUT[10:7]<=4'b0010; Temp1<=CDIN[7:4];end2'b10: begin DOUT[10:7]<=4'b0100; Temp1<=CDIN[11:8];end2'b11: begin DOUT[10:7]<=4'b1000; Temp1<=CDIN[15:12];endendcaseendendalways @(Temp1) //译码显示begincase(Temp1)4'b0000: DOUT[6:0]<=7'b0111111; //3fh=04'b0001: DOUT[6:0]<=7'b0000110; //06h=14'b0010: DOUT[6:0]<=7'b1010110; //56h=24'b0011: DOUT[6:0]<=7'b1001111; //4fh=34'b0100: DOUT[6:0]<=7'b1100110; //66h=44'b0101: DOUT[6:0]<=7'b1101101; //6dh=54'b0110: DOUT[6:0]<=7'b1111101; //7dh=64'b0111: DOUT[6:0]<=7'b0000111; //07h=74'b1000: DOUT[6:0]<=7'b1111111; //7fh=84'b1001: DOUT[6:0]<=7'b1101111; //6fh=9default: DOUT[6:0]<=7'b0111111; //3fhendcaseendendmodule顶层verilog程序:moduleFREQUENCY_COUNTER_DISPL Y_BLOCK(DOUT,FLOW_UP,CLK,TEST_CLK_IN,RESET) ;output[10:0] DOUT;output FLOW_UP;input CLK;input TEST_CLK_IN;input RESET;wire gated_clk,load,counter_clr;wire[15:0] cout_cdin;FREQUENCY_COUNTROL_BLOCKu1(.GATED_CLK(gated_clk),.LOAD(load),.COUNTER_CLR(counter_clr),.CLK_IN(CLK),.SIG NAL_TEST(TEST_CLK_IN),.RESET(RESET));FREQUENCY_COUNTER_BLOCKu2(.COUT(cout_cdin),.FLOW_UP(FLOW_UP),.CLOCK_IN(gated_clk),.RESET(RESET),.LOA D(load),.COUNTER_CLR(counter_clr));FREQUENCY_DISPL Y_BLOCKu3(.DOUT(DOUT),.DCLK_IN(CLK),.RESET(RESET),.CDIN(cout_cdin));endmodule五、仿真结果分析仿真结果如图所示,输入标准时钟频率为1MHz,经过分频后变成频率为0.5Hz的信号,将其与测试信号相与得到采样信号GATED_CLK,同时利用测试信号和0.5Hz的分频信号可以产生LOAD信号和COUNTER_CLR信号,它们和采样信号的关系在图上可以清楚的看出。

根据Verilog的数字频率计的设计

根据Verilog的数字频率计的设计以下是一个使用Verilog设计并仿真的数字频率计的示例:```verilogmodule frequency_counterinput reset,input clk,output reg [31:0] frequencyreg [31:0] count;reg [31:0] prev_count;reg counting;if (reset) begincounting <= 0;count <= 0;prev_count <= 0;end else beginprev_count <= count;count <= count + 1;if (prev_count == 0) begincounting <= 1;counting <= 0;frequency <= count;count <= 0;endendendendmodule```为了仿真该模块,可以使用任何支持Verilog仿真的工具,如ModelSim。

以下是一个对该模块进行仿真的示例测试台代码:```verilogmodule frequency_counter_tb;reg reset;reg clk;wire [31:0] frequency;frequency_counter dut.reset(reset),.clk(clk),.frequency(frequency)initial beginreset = 1;;reset = 0;endalways begin;clk = ~clk;endendmodule```在上述测试台代码中,引脚`reset`和`clk`通过不断的切换来产生复位和时钟信号。

然后,通过监视`frequency`引脚,可以检查计算的频率是否正确。

完成设计和测试台代码后,可以使用仿真工具对其进行仿真,以验证设计的正确性和性能。

基于Verilog的数字频率计的设计(包含代码及仿真)

一、实验名称数字频率计的设计二、实验地点211楼303三、实验目的和任务(1) 了解数字电路设计的基本特点(2) 了解数字频率计电路的基本原理(3) 基本掌握ISE 软件的使用(设计输入、仿真、实现)(4) 了解可编程逻辑器件(FPGA )的一般情况(5) 基本掌握HDL 的使用四、实验内容(1) 设计出符合设计要求的解决方案(2) 设计出单元电路(3) 利用EDA 软件对各单元电路及整体电路进行仿真(4)利用EDA 软件在ELB 电子课程设计实验板实现设计(5) 观察实验结果五、项目需用仪器设备名称以及所需主要元器件PC 机、EDA教学实验系统一台,带有(SPARTAN -3A XC3S200A芯片,LED 管, 七段数码管等)的实验板一块, 跳线、下载电缆一根,函数发生器。

六、实验任务与要求频率测量范围为10Hz~10MHz,用6只数码管以kHz为单位显示测量结果;有三个带锁按键开关(任何时候都只会有一个被按下)用来选择1S、0.1S和0.01S三个闸门时间中的一个;有一个按钮开关用来使频率计复位;有两只LED,一只用来显示闸门的开与闭,另一只当计数器溢出时做溢出指示。

数字频率计的相关技术指标如下:1、位数:测量频率通过LED数码管为六位十进制数显示。

2、测试频率范围为:10HZ-10MHZ。

3、计数器溢出时要有溢出标志over。

4、需要有闸门标志gate。

5、显示工作方式:a、用BCD七段共阳极数码管显示读数,只有在读数不发生跳变时才是正确的结果。

b、采用记忆显示方法,即在一次测试结束时,显示测试结果,此显示值一直保留到下次测量显示数到来,才将上次显示更新。

用第二次测试结果,更新显示值。

6、要求被测输入信号应是符合数字电路要求的脉冲波。

七、verilog设计环境介绍VerilogVerilog HDL是目前应用最为广泛的硬件描述语言.Verilog HDL可以用来进行各种层次的逻辑设计,也可以进数字系统的逻辑综合,仿真验证和时序分析等。

Verilog-数字频率计

摘要本文介绍了基于FPGA的数字频率计的设计方法,设计采用硬件描述语言Verilog,在软件开发平台ISE上完成,可以在较高速时钟频率(48MHz)下正常工作。

该数字频率计采用测频的方法,能准确的测量频率在10Hz到100MHz之间的信号。

使用ModelSim仿真软件对Verilog程序做了仿真,并完成了综合布局布线,最终下载到芯片Spartan3A上取得良好测试效果。

关键词:FPGA,Verilog,ISE,测频方法IAbstractThis paper introduces the design method of digital frequency meter based on FPGA,which use hardware description language-Verilog in software development platform ISE and can word in relatively high-speed clock of48MHz.The frequency meter uses the method of frequency measurement,which could accurately measure the frequency of signals between10Hz to100MHz.This system uses the simulation tool-ModelSim to run and debug the Verilog program,and design the circuit placement.A good result can be achieved when the program was burnt on the chip Spartan3A.KeywordsKeywords::FPGA,Verilog,ISE,Frequency MeasurementIIII目录第一章测量原理与方法................................................................................................................................................................................................441.1测频方法.............................................................................................................41.2测周方法.............................................................................................................51.3等精度测量法....................................................................................................51.4放大整形电路....................................................................................................61.5时基信号产生. (7)第二章任务要求..........................................................................................................................................................................................................................88第三章各模块功能及介绍....................................................................................................................................................................................883.1分频器..................................................................................................................84.2闸门选择器........................................................................................................104.3频率计数器........................................................................................................124.4锁存器................................................................................................................144.5扫描显示控制译码系统.. (15)第四章顶层电路及总体仿真............................................................................................................................................................................16164.1顶层电路.. (16)4.2总体仿真结果 (16)4.3测试结果 (19)第一章测量原理与方法所谓“频率”,就是周期性信号在单位时间(秒)内变化的次数。

Verilog 频率计 电子实验报告

电子科技大学设计论文论文题目:基于Verilog HDL频率计设计与实现指导老师:学生姓名:学号:专业:摘要在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

电子计数器测频有两种方式:一是直接测频法,即在一定闸门时间内测量被测信号的脉冲个数;二是间接测频法,如周期测频法。

直接测频法适用于高频信号的频率测量,间接测频法适用于低频信号的频率测量。

本文阐述了用V erilogHDL语言设计了一个简单的数字频率计的过程关键词:周期;EDA;VerilogHDL;数字频率计;波形仿真SummaryIn electronics, the frequency is one of the most basic parameters, and m easurement program with a lot of electric parameters, the measurement re sult-s have a very closerelationship, and frequency measurement become s more important. There are several ways of measuring frequency, the elec tronic counter to measure frequency with high precision, easy to use, rapi d measurement, and easy to automate the measurement process, etc., is o ne of the important means of frequency measurement. Electroniccounter freq uency measurement in two ways: First, the direct frequency measurement method to measure the number of pulses of the measured signal, that is, in a certain gatetime; indirect frequency measurement method, such as the cycl e frequency measurement method. Direct frequency measurement method f or high-frequency signal frequency measurement, frequency measurements i ndirectly measured the frequency method is suitable for low-frequency sign als. This paper describes the design of a simple digital frequency meter usi ng Verilog HDL languageKeywords: period; the EDA; the Verilog HDL; digital frequency meter; wavef orm simulation目录1引言 (1)1.1频率计概述 (1)1.2设计目的 (2)1.3设计内容 (2)1.4频率测量的思想和方法 (2)2 Verilog HDL 简介 (4)3 数字频率计系统框图 (5)3.1数字频率计系统部件介绍 (5)3.2数字频率计系统模块划分结构 (6)4 数字频率计程序设计及实现 (7)4.1分频模块div_clk (7)4.2基准频率选择模块sw_sel (8)4.3门控模块gate_ctrl (8)4.4计数模块counter (9)4.5锁存器模块latch (11)4.6显示模块 display (13)4.7顶层模块 topfile (14)5 设计实现 (16)5.1实验设备 (16)5.2管脚分布 (17)5.3下载过程 (17)6 系统测试与结果分析 (18)6.1系统测试 (18)6.2 结果分析: (19)7总结 (20)7.1 结束语 (20)7.2谢辞 (21)参考文献 (21)附录 (21)1引言在电子测量领域中,频率测量的精确度是最高的,可达10—10E-13数量级。

Verilog频率计(低频))

日志档案发表于2010/5/17 23:45:37标签:无标签Verilog频率计(低频)小弟最近弄了个频率计,主要测量工频50HZ的。

代码附在下边。

下面的代码,功能实现了,通过了modelsim仿真,实际测试也成功。

还是存在一些问题,不是功能上的,而是实现方法上了,我总感觉我的这个设计肯定不是最好的,有一些除法,还有十进制书转化成BCD码的问题还须要很大的优化。

但是小弟,刚学FPGA,一些问题也搞不清楚,。

就发在网上,分享一下,也让大家指正一下。

//// Description 测量频率(工频50HZ 13~ 59.9HZ)// Create Date: 2010- 05 -17// Engineer: 张书腾// Module Name: frequency////nate:该设计只是适用于50HZ左右的频率测量,采用的是测周发module frequency(clk, rst_n, fre,sm_bit, segment);input clk; //50M系统时钟input rst_n; //异步复位端input fre;//频率输入端output [3:0] sm_bit;//数码管位码output[7:0] segment; //数码管位码reg [3:0] sm_bit;//数码管位码寄存器reg [7:0] segment;//数码管位码寄存器////////////////////标准信号F="100K",测周///////////////////////////reg [9:0]count;//100K时钟分频计数器always @ (posedge clk or negedge rst_n) beginif(!rst_n)count <= 1'b0;else if(count< 10'd499)count <= count+1'b1;elsecount <= 1'b0;endreg clk_100K;//100K时钟输出寄存器always @ (posedge clk or negedge rst_n) beginif(!rst_n)clk_100K <= 1'b0;else if(count<=249) //时钟的占空比为50%clk_100K <= 1'b0;else clk_100K <= 1'b1;end///////////////////////////////////////////////待测频率进行2分频,2分频后,就可以只计二分频后信号的高电平或低电平//就可以了,如果不2分频,只记高电平或低电平的话,信号的占空比不同会导致结果不准确reg fre_2;always @ (posedge fre or negedge rst_n) beginif(!rst_n)fre_2 <= 1'b0;else if(fre)fre_2 <= ~fre_2;//2分频end//////////////测周计数模块,计2分频后的待测频的高电平或低电平/////////////////////// //相当于在待测频率的整个周期内计数//////////////////////////////////////////////////////reg [12:0] cnt;//计数寄存器//由于位宽的限制,最大计数值8192,所以测低频(低于14HZ时会出错)always @ (posedge clk_100K or negedge rst_n) beginif(!rst_n) begincnt <= 13'd0;endelse if(!fre_2) //低电平计数cnt <= cnt + 1'b1;else begincnt <= 13'd0;//不为低电平时清零endend////////锁存信号,上升沿有效//////////////////////////reg load;always @ (posedge fre_2 or negedge rst_n) beginif(!rst_n) beginload <= 1'b0;endelse load <= ~load;//产生上升沿end//////////////////////////////////reg [12:0] cnt_r;//存储锁存的值always @ (posedge load)//load上升沿锁存begincnt_r <= cnt;//将计数值锁存end/////////////////////////数据处理单/////////////////////////////////////////////////////////////////////////////reg [23:0] temp; //暂存数据//(将一个十进制的四位数各个位取出),fre_r 中的数为实际频率是100倍,是为了后面的计算方便always @ (posedge clk or negedge rst_n)if(!rst_n) beginfre_r <= 13'd0;endelse begintemp <= (24'd1*******)/cnt_r;//fre_r=(1/(10us * cnt_r ))*100实际频率扩大100倍//采用了一个除法运算符,不清楚效率如何,但是能工作fre_r <= temp[12:0]; //取出低位消除警告//////////////////////////////////////end//////////////////////////////////reg [12:0] fre_r , temp1, temp2,temp3;//fre_r , temp1, temp2,temp3用于计算reg [3:0] count1,count2,count3,count4;//数码管要显示的每位十进制数reg [3:0] state;///状态机的状态寄存器///////////////////////状态机编码//////////////////parameter shiwei = 4'b0001, //十位gewei = 4'b0010,//个位shifenwei = 4'b0100,//十分位baifenwei = 4'b1000;//百分位always @ (posedge clk or negedge rst_n) ////状态机,取出一个四位数的各个位的值,用比较法if(!rst_n) beginstate <= shiwei;count1 <= 4'd0;count2 <= 4'd0;count3 <= 4'd0;count4 <= 4'd0;endelse begincase(state)shiwei: beginstate <= gewei; /////////////// //十位//用比较发对照出每位的十进制数if((fre_r>=5000)&&(fre_r<6000)) begin count1 <=4'd5; temp1<=fre_ r-13'd5000; endelse if((fre_r>=4000)&&(fre_r<5000)) begin count1 <=4'd4; temp1<=fre_ r-13'd4000; endelse if((fre_r>=3000)&&(fre_r<4000)) begin count1 <=4'd3; temp1<=fre_ r-13'd3000; endelse if((fre_r>=2000)&&(fre_r<3000)) begin count1 <=2; temp1<=fre_r-1 3'd2000; endelse if((fre_r>=1000)&&(fre_r<2000)) begin count1 <=1; temp1<=fre_r-1 3'd1000; endelse if(fre_r<1000) begin count1 <=0; temp1<=fre_r; endelse begin count1 <=5; temp1<=fre_r-13'd5000;end endgewei: beginstate <= shifenwei; ////////////////////////个位//用比较发对照出每位的十进制数 if(temp1>=900) begin count2 <=9; temp2<=temp1-13'd90 0; endelse if((temp1>=800)&&(temp1<900)) begin count2 <=8; temp2<=temp1 -13'd800; endelse if((temp1>=700)&&(temp1<800)) begin count2 <=7; temp2<=temp1 -13'd700; endelse if((temp1>=600)&&(temp1<700)) begin count2 <=6; temp2<=temp1 -13'd600; endelse if((temp1>=500)&&(temp1<600)) begin count2 <=5; temp2<=temp1 -13'd500; endelse if((temp1>=400)&&(temp1<500)) begin count2 <=4; temp2<=temp1 -13'd400; endelse if((temp1>=300)&&(temp1<400)) begin count2 <=3; temp2<=temp1 -13'd300; endelse if((temp1>=200)&&(temp1<300)) begin count2 <=2; temp2<=temp1 -13'd200; endelse if((temp1>=100)&&(temp1<200)) begin count2 <=1; temp2<=temp1 -13'd100; endelse if(temp1<100) begin count2 <=0; temp2<=temp1; endelse begin count2 <=0; temp2<=temp1-13'd900; end endshifenwei: beginstate <= baifenwei;///////////////////////////十分位//用比较发对照出每位的十进制数if(temp2>=90) begin count3 <=9; temp3<=temp2-13'd90; endelse if((temp2>=80)&&(temp2<90)) begin count3 <=8; temp3<=temp2-1 3'd80; endelse if((temp2>=70)&&(temp2<80)) begin count3 <=7; temp3<=temp2-1 3'd70; endelse if((temp2>=60)&&(temp2<70)) begin count3 <=6; temp3<=temp2-1 3'd60; endelse if((temp2>=50)&&(temp2<60)) begin count3 <=5; temp3<=temp2-13'd50; endelse if((temp2>=40)&&(temp2<50)) begin count3 <=4; temp3<=temp2-1 3'd40; endelse if((temp2>=30)&&(temp2<40)) begin count3 <=3; temp3<=temp2-1 3'd30; endelse if((temp2>=20)&&(temp2<30)) begin count3 <=2; temp3<=temp2-1 3'd20; endelse if((temp2>=10)&&(temp2<20)) begin count3 <=1; temp3<=temp2-1 3'd10; endelse if(temp2<10) begin count3 <=0; temp3<=temp2; endelse begin count3 <=0; temp3<=temp2-13'd90; end endbaifenwei: beginstate <= shiwei;/////////////////百分位///////////////////////////////////count4 <= temp3[3:0];enddefault: beginstate <= shiwei;endendcaseend////////////////////////////////////////////////////////////////显示模块 ///////////////reg [18:0] count_1ms; //用来产生数码管动态显示的位变化的驱动时钟always @ (posedge clk or negedge rst_n)if(!rst_n) begincount_1ms <= 19'd0;endelse begincount_1ms <= count_1ms + 1'b1;end//////////数码管动态扫描的位产生单元always @ (posedge clk or negedge rst_n)if(!rst_n)sm_bit=4'b0000;else begincase(count_1ms[18:16]) //数码管动态显示的位扫描//基本上是每一位亮1m s3'b000: sm_bit=4'b1110;3'b001: sm_bit=4'b1101;3'b010: sm_bit=4'b1011;3'b011: sm_bit=4'b0111;default: sm_bit=4'b1111;endcaseendalways @ (posedge clk or negedge rst_n)if(!rst_n) beginsegment =8'h03;endelse begincase(sm_bit)4'b1110: segment=convent(count1); //十位4'b1101: segment=convent(count2)-8'd1;///个位//显示小数点4'b1011: segment=convent(count3); //十分位4'b0111: segment=convent(count4); //百分位default: segment=8'b1111_1111;endcaseendfunction [7:0] convent;//将自然数转化成共阳数码管的函数input [3:0] bcd; //输入为自然数case(bcd)4'd0: convent="8"'h03; //数码管段码,a为最高位,dp为最低位 4'd1: convent="8"'h9f;4'd2: convent="8"'h25;4'd3: convent="8"'h0d;4'd4: convent="8"'h99;4'd5: convent="8"'h49;4'd6: convent="8"'h41;4'd7: convent="8"'h1f;4'd8: convent="8"'h01;4'd9: convent="8"'h09;default: convent = 8'hff;endcaseendfunction///////////////////////////////////////////////////////////。

基于verilog语言的数字频率计设计

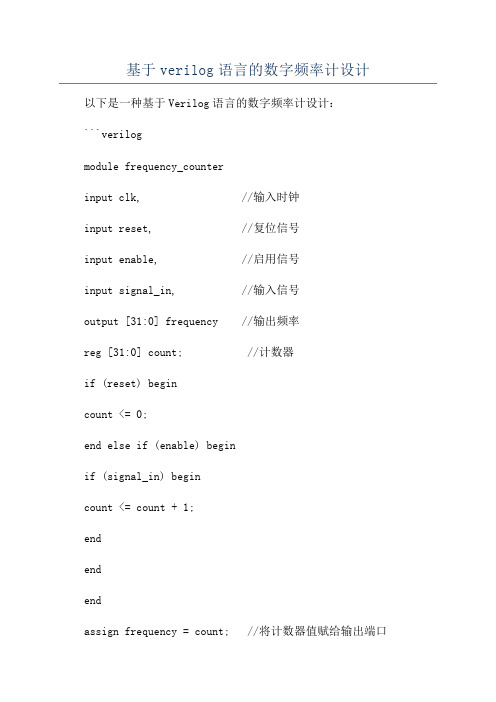

基于verilog语言的数字频率计设计以下是一种基于Verilog语言的数字频率计设计:```verilogmodule frequency_counterinput clk, //输入时钟input reset, //复位信号input enable, //启用信号input signal_in, //输入信号output [31:0] frequency //输出频率reg [31:0] count; //计数器if (reset) begincount <= 0;end else if (enable) beginif (signal_in) begincount <= count + 1;endendendassign frequency = count; //将计数器值赋给输出端口endmodule```在此设计中,我们使用一个32位的计数器(count)来计算输入信号(signal_in)的高电平脉冲数。

输入时钟(clk)用于同步计数器的操作。

复位信号(reset)用于将计数器复位为0。

启用信号(enable)用于控制计数器的启用与禁用。

当reset为高电平时,计数器会被复位为0。

当enable为高电平时,计数器会逐渐增加,直到输入信号(signal_in)为低电平。

此时,计数器的值会保持不变。

最终,计数器的值会通过输出端口frequency输出。

在这个设计中,frequency是一个32位的输出端口,表示输入信号的高电平脉冲数。

这个设计可以通过Verilog仿真工具进行仿真,并且可以综合到FPGA芯片中进行硬件实现。

Verilog频率计

数字频率计的设计学号:2905101012姓名:袁浩指导老师:皇小辉摘要本文介绍了基于FPGA的数字频率计的设计方法,设计采用硬件描述语言Verilog ,在软件开发平台ISE上完成,可以在较高速时钟频率(48MHz)下正常工作。

该数字频率计采用测频的方法,能准确的测量频率在10Hz到100MHz之间的信号。

使用ModelSim仿真软件对Verilog程序做了仿真,并完成了综合布局布线,最终下载到芯片Spartan3A上取得良好测试效果。

关键词:FPGA,Verilog,ISE,测频方法目录目录1 引言..................................................................................................................... - 4 -1.1数字频率计概述 .. (5)1.2频率测量的思想和方法 (5)第二章任务要求 .................................................................................................... - 7 -第三章基于VERILOG HDL数字频率计程序设计........................................ - 8 -3.1数字频率计系统模块划分结构 (8)3.2计数模块COUNTER (9)3.3门控模块GATE_CONTROL (12)4.4分频模块FDIV (13)3.5寄存器模块FLIP_LATCH (15)4.6多路选择模块DATA_MUX (17)3.7动态位选模块DISPSELECT (18)3.8BCD译码模块DISPDECODER (19)3.9顶层电路TOP (22)第四章综合分析 ................................................................................................ - 25 -4.1总体仿真结果 .. (25)4.2误差分析 (26)参考文献 ................................................................................................................ - 27 -1 引言在电子测量领域中,频率测量的精确度是最高的,可达10—10E-13数量级。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA实验报告

一.实验目的

利用verilog硬件语言设计一个数字频率计电路,掌握采用顶层原理图设计复杂逻辑电路的方法,熟悉原理图的仿真和信号的检测方法。

二.实验内容

利用verilog语言编写十进制计数器、数字频率计控制电路和四位二进制锁存器,然后将他们分别生成原理图,最后构成一个数字频率及电路并进行仿真。

三.实验总结

通过本次实验,我学会了如何使用Quartus进行verilog语言的编程,也学会了如何对verilog的程序进行仿真,在仿真过程中还学会了如何对几个端口进行编组,以及如何对一组端口设置波形,还有设置时钟的波形。

最重要的是这次实验主要是生成block原理图,我也掌握采用顶层原理图设计复杂逻辑电路的方法,我还学会了如何由verilog程序生成block图,也学会了如何对block图进行仿真。

总的来说,这次实验让我学到了很多知识,我获益匪浅!。