Verilog硬件描述语言参考手册

Verilog硬件描述语言

第9页/共151页

➢等式运算符(= =,!=,= = =,!= =) •= =:逻辑相等 •!=:逻辑不等 •= = =:全等(对x和z严格按位比较) •!= =:非全等 •说明 = = 与= = = 的差别:

9

第10页/共151页

➢运算的优先级

10

第11页/共151页

➢Verilog的层次结构

•过程块是行为建模的基础 •有两种过程块 –initial 过程块:只执行一次。 –always 过程块:反复执行。 •过程块可以包含如下内容: –过程赋值:描述块内的数据流。 –高级结构(循环,条件):描述块的功能。 –时间控制:控制块中语句的执行情况。

13

第14页/共151页

➢过程赋值 •过程赋值:在过程块内的赋值 •过程赋值针对variable类型的数据 •要赋予的值可以是任何合法的表达式 •过程赋值可以分成: –阻塞赋值:串行执行,只有执行完了前一条语句,后一条语句才能执行。 –非阻塞赋值:并行执行,一组赋值语句之间没有前后顺序关系,它们在同一时刻开 始计算右值表达式,即不等当前语句执行完,即开始执行下一条语句。

7

第8页/共151页

➢运算符(Operators)

•算术运算符(+,-,*,/,%) •关系运算符(>,<,>=,<=) •等式运算符(= =,!=,= = =,!= =) •逻辑运算符(&&,||,!) •条件运算符(?:) •位运算符(~,|,^,&,~^,^~) •移位运算符(<<,>>) •拼接运算符({}) •赋值运算符(=,<=)

endmodule

15

第16页/共151页

➢非阻塞过程赋值举例(<=) module swap_ vals;

硬件描述语言 Verilog HDL

`include指令

变量声明(wire,reg及其它类型) 数据流语句(assign) 低层模块的实例 过程块always和initial(包含所有的行为语句) 任务(task)和函数(function)

endmodule; 模块结束语句

16

4.3.3 模块和端口

17

4.3.3 模块和端口

3.$stop任务和$finish任务

۞ $stop任务使得仿真被挂起(例:暂停仿真以检查 信号值 )

۞ $finish任务将结束仿真,并退出仿真环境

21

4.3.3 系统任务和系统函数

常用的几个系统任务和系统函数:

4.时间函数:$time ,$stime ,$realtime 5.$random函数

32

4.4.2 数据类型

2.变量(Variable)类型 (reg、integer、time、real、realtime) 数据存储单元的抽象,下一次赋值前,变量的值保持不变 (1)寄存器(reg)变量类型

۞ 对应具有状态保持作用的硬件电路,如触发器、锁存器等

۞ 声明形式:reg [msb:lsb] reg1,reg2,...regN;

3

4.1 HDL简介

4.1.1 关于HDL(硬件描述语言)

使用HDL ۞用一种高级语言来表达大规模集成电路的功能,隐藏

其具体实现的细节,对数字电路和数字逻辑系统能够 进行形式化的描述。 ۞提高逻辑设计效率,降低设计成本,缩短设计周期。 ۞多方位的仿真可以在设计完成之前检测到其错误,减 少设计重复的次数,使第一次投片便能成功实现芯片 成为可能。 ۞使检测各种设计方案变得容易和方便,对方案的修改 只需要修改HDL程序,比修改原理图容易得多。

VerilogHDL硬件描述-2

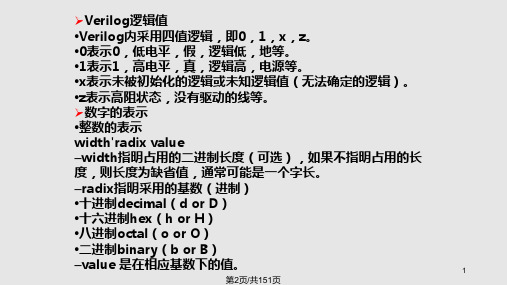

数字表达方式有以下三种:

1) [size] 'base value:这是一种全面的描述方式。 size :位宽,定义了以位(bit) 计的常量的位宽,位宽以十进制数字表示; 如:一个4位二进制数的位宽为4; 一个4位十六进制数的位宽为16(每十六进制数用4位二进制数表示)。 base:为o或O,b或B,d或D,h或H之一; value:base进制下的常量的数值。 2) 'base value:数的位宽采用缺省位宽(由具体的机器系统决定,但至少32位)。 3) Value:在这种描述方式中,采用缺省进制十进制。

wire或者reg向量名[常数表达式1:常数表达式2]

reg [5:0] State; wire [0:3] Prt; State [4:1] Prt [3:2] //寄存器部分选择。 //线网部分选择。

2013年7月25日

15

存储器

通过对reg型变量建立数组来对存储器建模。

reg [n-1:0] 存储器名[m-1:0];

2013年7月25日

2

整数

例:

4'b1111 12'habc 16'd255 (2+3)„b10 'hc3 'o21 // This is a 4-bit binary number // This is a 12-bit hexadecimal number // This is a 16-bit decimal number. //非法:位长不能够为表达式 // This is a 32-bit hexadecimal number // This is a 32-bit octal number

参数(parameters)

systemverilog标准手册

SystemVerilog标准手册一、概述SystemVerilog是一种硬件描述和验证语言,它结合了Verilog HDL和VHDL的特性,并增添了许多新的功能和特性。

SystemVerilog的标准手册是SystemVerilog语言的权威参考资料,它详细说明了SystemVerilog的语法、语义和用法规范。

二、内容1. 语言基础SystemVerilog标准手册包含了SystemVerilog语言的基础知识,如数据类型、变量定义、控制结构、函数和任务等。

在这一部分,读者可以了解到SystemVerilog的基本语法和语言特性,为后续的学习和应用打下坚实的基础。

2. 对象和类SystemVerilog引入了面向对象的编程思想,允许用户定义自定义类型、类和对象。

SystemVerilog标准手册详细介绍了对象和类的定义、成员函数、继承和多态等相关内容,为用户提供了丰富的编程工具和技巧。

3. 验证方法SystemVerilog不仅可以用于硬件描述,还可以用于硬件验证。

SystemVerilog标准手册介绍了SystemVerilog的验证方法和工具,包括assertion、coverage、constrained randomization等内容,帮助用户编写高效且可靠的验证代码。

4. 高级特性除了基本的语言特性外,SystemVerilog还提供了许多高级的功能和特性,如接口、多线程、并发控制等。

SystemVerilog标准手册深入介绍了这些高级特性的用法和原理,帮助用户更好地理解和应用SystemVerilog语言。

5. 应用实例除了语法和特性的介绍外,SystemVerilog标准手册还提供了大量的实际应用示例,包括硬件描述、验证代码和仿真模型等。

这些应用实例可以帮助用户更直观地了解SystemVerilog语言的实际应用场景,加深对SystemVerilog的理解和掌握。

三、重要性SystemVerilog标准手册是学习和使用SystemVerilog语言的重要参考资料。

第3章——Verilog硬件描述语言3资料

任务(task)

语句格式: task 任务名; <输入输出端口声明>; <任务中数据类型声明>; 语句1; 语句2; … endtask

说明: (1) 式子左边的“赋值目标线网”只能是线网 变量。 (2) 式子右边表达式的操作数可以是线网,可 以是寄存器,也可以是函数。 (3) 一旦等式右边任何一个操作数发生变化, 右边的表达式就会立刻被重新计算,再进行一次 新的赋值。 (4) assign可以使用条件运算符进行条件判断 后赋值assign data_out = sel? a : b;

initial begin a = 1; b = 0; #10 begin a=2; b=3; end #10 begin a=0; b=2; end end

initial c = 1;

always 语句

语句格式: always @ <触发事件> 语句或语句组 说明: 1) always的触发事件可以是控制信号的变化、时钟边沿 的跳变等。always块的触发控制信号可以是一个,也 可以是多个,其间用or连接 例:always @ (posedge clock or posedge reset)

module pipe(q3,d,clk); output [7:0] q3; input [7:0] d; input clk; reg [7:0] q3,q2,q1; always @ (posedge clk) begin q3 = q2; q2 = q1; q1 = d; end endmodule

always @ (a or b or c or d)

2)只要 always的触发事件产生一次, always就 会执行一次。在整个仿真过程中,如果触发事件 不断产生,则always中的语句将被反复执行

Verilog硬件描述语言

Verilog HDL硬件描述语言2.1 Verilog HDL概述2.1.1 Verilog HDL的特点Verilog HDL和VHDL一样,是目前大规模集成电路设计中最具代表性、使用最广泛的硬件描述语言之一。

作为硬件描述语言,Verilog HDL具有如下特点:1. 能够在不同的抽象层次上,如系统级、行为级、RTL(Register Transfer Level)级、门级和开关级,对设计系统进行精确而简练的描述;2. 能够在每个抽象层次的描述上对设计进行仿真验证,及时发现可能存在的设计错误,缩短设计周期,并保证整个设计过程的正确性;3. 由于代码描述与具体工艺实现无关,便于设计标准化,提高设计的可重用性。

如果有C语言的编程经验,只需很短的时间内就能学会和掌握Verilog HDL,因此,Verilog HDL可以作为学习HDL设计方法的入门和基础。

2.1.2 Verilog HDL的基本结构Verilog HDL描述是由模块(module)构成的,每个模块对应的是硬件电路中的逻辑实体。

因此,每个模块都有自己独立的功能或结构,以及用于与其它模块之间相互通信的端口。

例如,一个模块可以代表一个简单的门,一个计数器,一个存储器,甚至是计算机系统等。

例2-1-1 加法器的verilog描述module adder (in1, in2, sum);input in1,in2;output [1:0] sum;wire in1,in2;reg [1:0] sum;always @ (in1 or in2)beginsum=in1+in2;endendmodule从这个例子中可以看出,一段完整的代码主要由以下几部分组成:可以了解到一些基本信息,如代码中加法器的主要功能、设计工程师、完成的日期及版本。

例2-1-1的模块名是adder,有两个输入端口in1,in2和一个输出端口sum。

其中,输入信号是一位的,其数据类型声明为连线型(wire);输出是两位的寄存器类型。

verilog硬件描述语言(共178张)

3

第3页,共178页。

3.1 引言(yǐnyán)

二、Verilog HDL的发展历史

▪ 1983年,由GDA(GateWay Design Automation)公 司的Phil Moorby首创;

▪ 1989年,Cadence公司收购了GDA公司; ▪ 1990年, Cadence公司公开发表Verilog HDL; ▪ 1995 年 , IEEE 制 定 并 公 开 发 表 Verilog HDL1364-

信号类型声明

begin

if(load)

out <= data;

else

// 同步预置数据

功能描述

out < = out + 1 + cin; // 加1计数

end

assign cout = &out & cin; //若out为8‘hFF,cin为1,则cout为1

endmodule

9

缩减运算符

位运算符

❖ 注2:“always” 块可用多种手段来表达逻辑关系, 如用if-else语句或case语句。

❖ 注3: “always” 块语句与assign语句是并发执行的16 , assign语句一定要放在“always” 块语句之外!

第16页,共178页。

3.2 Verilog HDL基本(jīběn)结构

❖ Verilog HDL模块的模板(仅考虑用于逻辑综合的部分)

module <顶层模块名> (< 输入输出端口列表>) ;

output 输出端口列表;

input 输入端口列表;

verilog_ieee官方标准手册

verilog_ieee官方标准手册

Verilog是一种硬件描述语言(HDL),是用于电子设计自动化(EDA)的语言之一。

Verilog从20世纪80年代开始发展,最初由Gateway Design Automation 公司开发,后来被Cadence Design Systems收购。

Verilog被广泛应用于数字电路的设计和仿真。

IEEE标准的全称是IEEE Std 1364,是Verilog的官方标准手册。

这个标准由IEEE Verilog标准工作组制定,其中包含了Verilog语言的语法和语义规范。

这个标准包含了3个部分:

1. Verilog语言参考手册:这个部分包含了Verilog语言的语法和语义规范。

其中包含了Verilog的基本语法、数据类型、运算符、控制结构、模块和端口等方面的内容,对于初学者来说非常重要。

2. Verilog模拟器标准接口:这个部分定义了与Verilog编译器和模拟器交互的标准接口。

如果你想自己实现一个Verilog编译器或模拟器,那么这个部分非常重要。

3. Verilog验证标准接口:这个部分定义了与Verilog验证工具交互的标准接口。

如果你想自己实现一个Verilog验证工具,那么这个部分非常重要。

总的来说,IEEE标准是Verilog语言的权威参考,所有的Verilog编译器和模拟器都应该遵循这个标准。

如果你想深入学习Verilog语言,那么这个标准是不可或缺的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Verilog 语言标准化的目的是将现存的通过 Verilog-XL 仿真器体现的 Verilog 语言标准化。 IEEE 的 Verilog 标准与事实上的标准有一些区别。因此,仿真器有可能不完全支持以下的一 些功能:

y 在UDP(用户自定义原语)和模块实例中使用数组(见Instantiation说明)。

编译

Verilog的原代码通常键入到计算机的一个或多个文本文件上。然后把这些文本文件交给 Verilog编译器或解释器处理,编译器或解释器就会创建用于仿真和综合必需的数据文件。 有时候,编译完了马上就能进行仿真,没有必要创建中间数据文件。

-----------------------------------------------------------------------------

1

在Verilog HDL 中,我们可通过高层模块调用低层和基本元件模块,再通过线路连接(即下 文中的NET)把这些具体的模块连接在一起,来描述一个极其复杂的数字逻辑电路的结ห้องสมุดไป่ตู้。 所谓基本元件模块就是各种逻辑门和用户定义的原语模块(即下文中的UDPs)。而所谓NET 实质上就是表示电路连线或总线的网络。端口连接列表用来把外部NET连接到模块的端口(即 引脚)上。寄存器可以作为输入信号连接到某个具体模块的输入口。NET和寄存器的值可取 逻辑值0,1,x(不确定)和 z(高阻)。除了逻辑值外,NET还需要有一个强度(Strength) 值。在开关级模型中,当NET的驱动器不止一个时,还需要使用强度值来表示。逻辑电路的 行为可以用Initial和Always 的结构和连续赋值语句,并结合设计层次树上各种层次的模块 直到最底层的模块(即UDP及门)来描述。

三. 语法总结

-----------------------------------------------------------------------------

典型的 Verilog 模块的结构:

module M (P1, P2, P3, P4); input P1, P2; output [7:0] P3; inout P4; reg [7:0] R1, M1[1:1024]; wire W1, W2, W3, W4; parameter C1 = “This is a string”; initial begin : 块名 // 声明语句

Verilog 硬件描述语言 参考手册

-------------------------------------------------------------------------------

一. 关于 IEEE 1364 标准

-------------------------------------------------------------------------------

-----------------------------------------------------------------------------

二. Verilog 简介

-----------------------------------------------------------------------------

模块中每个Initial块、Always块、连续赋值、UDP 和各逻辑门结构块都是并行执行的。而 Initial及Always块内的语句与软件编程语言中的语句在许多方面非常类似,这些语句根据 安排好的定时控制(如时延控制)和事件控制执行。在Begin-End块内的语句按顺序执行, 而在Fork-Join块中的语句则并行执行。 连续赋值语句只可用于改变NET的值。寄存器类型 变量的值只能在Initial及Always块中修改。Initial及Always块可以被分解为一些特定的任 务和函数。PLI (即可编程语言接口的英语缩写)是完整的Verilog语言体系的一个的组成 部分,利用PLI便可如同调用系统任务和函数一样来调用C语言编写的各种函数。

y 含参数的宏定义(见‘define)。 y ‘undef.

y IEEE标准不支持用数字表示的强度值(见编译预处理命令)。 y 有许多Verilog-XL支持的系统任务、系统函数和编译处理命令在IEEE标准中

不支持。 y 若在模块中其Net或寄存类型变量只有一个驱动,IEEE标准允许在一个指定

块中, 延迟路径的最终接点可以是一个寄存器或Net类型的变量。而在此标 准推出之前,对最终接点的类型有着严格得多的要求(见Specify说明)。 y 指定路径的延迟表达式最多可以达到12个延迟表达式,表达式之间需用逗号 隔开。而在此标准推出之前,最多只允许六个表达式(见Specify说明)。 y 在Net类型变量的定义中,标量保留字scalared与矢量保留字 vectored的位置 也做了改动。原先,保留字位于矢量范围的前面。在IEEE标准中,它应位于 Net类型的后面(见Net说明)。 y 在最小-典型-最大常量表达式中,对于最小、典型与最大值的相对大小并无 限制。而原先最小值必须小于或等于典型值,典型值必须小于或等于最大值。 y 在IEEE标准中,表示延迟的最小-典型-最大表达式不必括在括号里。而原先, 它必需括在括号里。