ADM3232E

串口电平转换芯片数据手册SP3222_3232E

DESCRIPTIONs Meets true EIA/TIA-232-F Standards from a +3.0V to +5.5V power supplys 235KBps Transmission Rate Under Load s 1µA Low-Power Shutdown with Receivers Active (SP3222E )s Interoperable with RS-232 down to +2.7V power sources Enhanced ESD Specifications: ±15kV Human Body Model±15kV IEC1000-4-2 Air Discharge ±8kV IEC1000-4-2 Contact DischargeThe SP3222E/3232E series is an RS-232 transceiver solution intended for portable or hand-held applications such as notebook or palmtop computers. The SP3222E/3232E series has a high-efficiency, charge-pump power supply that requires only 0.1µF capacitors in 3.3V operation. This charge pump allows the SP3222E/3232E series to deliver true RS-232performance from a single power supply ranging from +3.3V to +5.0V. The SP3222E/3232E are 2-driver/2-receiver devices. This series is ideal for portable or hand-held applications such as notebook or palmtop computers. The ESD tolerance of the SP3222E/3232E devices are over ±15kV for both Human Body Model and IEC1000-4-2 Air discharge test methods. The SP3222E device has a low-power shutdown mode where the devices' driver outputs and charge pumps are disabled. During shutdown, the supply current falls to less than 1µA.SELECTION TABLEL E D O M s e i l p p u S r e w o P 232-S R s r D e v i r 232-S R sr e v i e c e R l a n r e t x E st n e n o p m o C nw o d t u h S L T T a S -3e t t f o .o N s n i P 2223P S V 5.5+o t V 0.3+224s e Y s e Y 02,812323P S V5.5+o t V 0.3+224oN oN 61RE T E M A R A P .N I M .P Y T .X A M ST I N U SN O I T I D N O C S C I T S I R E T C A R A H C C D tn e r r u C y l p p u S 3.00.1A m T ,d a o l o n B M A 52+=o V ,C C C V 3.3=tn e r r u C y l p p u S n w o d t u h S 0.101µA,D N G =N D H S T B M A 52+=o V ,C C C V3.3+=S T U P T U O R E V I E C E R D N A S T U P N I C I G O L W O L d l o h s e r h T c i g o L t u p n I 8.0V 2e t o N ,N D H S ,N E ,N I x T H G I H d l o h s e r h T c i g o L t u p n I 0.24.2V V C C 2e t o N ,V 3.3=V C C 2e t o N ,V 0.5=t n e r r u C e g a k a e L t u p n I 10.0±0.1±µA ,N D H S ,N E ,N I x T T B M A 52+=o C t n e r r u C e g a k a e L t u p t u O 50.0±01±µA d e l b a s i d s r e v i e c e r W O L e g a t l o V t u p t u O 4.0V I T U O A m 6.1=H G I H e g a t l o V t u p t u O V C C 6.0-V C C 1.0-VI T U O Am 0.1-=S T U P T U O R E V I R D gn i w S e g a t l o V t u p t u O 0.5±4.5±Vk 3Ω,s t u p t u o r e v i r d l l a t a d n u o r g o t d a o l T B M A 52+=o Cec n a t s i s e R t u p t u O 003ΩV C C T ,V 0=-V =+V =T U O =+V 2t n e r r u C t i u c r i C -t r o h S t u p t u O 53±07±06±001±A m A m V T U O V 0=V T U O =+V51tn e r r u C e g a k a e L t u p t u O 52±µAV T U O =+V ,V 21C C de l b a s i d s r e v i r d ,V 5.5o t V 0=NOTE 1: V+ and V- can have maximum magnitudes of 7V, but their absolute difference cannot exceed 13V.ABSOLUTE MAXIMUM RATINGSThese are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the device.V CC ................................................................-0.3V to +6.0V V+ (NOTE 1)................................................-0.3V to +7.0V V- (NOTE 1)................................................+0.3V to -7.0V V+ + |V-| (NOTE 1)....................................................+13V I CC (DC V CC or GND current).................................±100mAInput VoltagesTxIN, EN .....................................................-0.3V to +6.0V RxIN.............................................................................±25V Output VoltagesTxOUT.....................................................................±13.2V RxOUT..............................................-0.3V to (V CC + 0.3V)Short-Circuit DurationTxOUT...............................................................Continuous Storage Temperature.................................-65°C to +150°C Power Dissipation Per Package20-pin SSOP (derate 9.25mW/o C above +70o C).....750mW 18-pin PDIP (derate 15.2mW/o C above +70o C)....1220mW 18-pin SOIC (derate 15.7mW/o C above +70o C)...1260mW 20-pin TSSOP (derate 11.1mW/o C above +70o C)..890mW 16-pin SSOP (derate 9.69mW/o C above +70o C).....775mW 16-pin PDIP (derate 14.3mW/o C above +70o C)....1150mW 16-pin Wide SOIC (derate 11.2mW/o C above +70o C)900mW 16-pin TSSOP (derate 10.5mW/o C above +70o C)..850mW 16-pin nSOIC (derate 13.57mW/°C above +70°C)..1086mWSPECIFICATIONSUnless otherwise noted, the following specifications apply for V CC = +3.0V to +5.0V with T AMB = T MIN to T MAXR E T E M A R A P .N I M .P Y T .X A M ST I N U SN O I T I D N O C S T U P N I R E V I E C E R e g n a R e g a t l o V t u p n I 51-51+V W O L d l o h s e r h T t u p n I 6.08.02.15.1V V C C V 3.3=V C C V 0.5=H G I H d l o h s e r h T t u p n I 5.18.14.24.2V V C C V 3.3=V C C V0.5=s i s e r e t s y H t u p n I 3.0V ec n a t s i s e R t u p n I 357k ΩS C I T S I R E T C A R A H C G N I M I T e t a R a t a D m u m i x a M 021532s p b k R L k 3=ΩC ,L g n i h c t i w s r e v i r d e n o ,F p 0001=y a l e D n o i t a g a p o r P r e v i r D 0.10.1µs µs t L H P R ,L K 3=ΩC ,L F p 0001=t H L P R ,L K 3=ΩC ,L F p 0001=y a l e D n o i t a g a p o r P r e v i e c e R 3.03.0µs t L H P C ,T U O x R o t N I x R ,L F p 051=t H L P C ,T U O x R o t N I x R ,L Fp 051=e m i T e l b a n E t u p t u O r e v i e c e R 002s n e m i T e l b a s i D t u p t u O r e v i e c e R 002s n w e k S r e v i r D 001005s n t |L H P t -H L P T ,|B M A 52=o C we k S r e v i e c e R 0020001s n t |L H P t -H L P |et a R w e l S n o i g e R -n o i t i s n a r T 03/V µsV C C R ,V 3.3=L K 3=ΩT ,B M A 52=o ,C V 0.3+o t V 0.3-m o r f n e k a t s t n e m e r u s a e m V0.3-o t V 0.3+r o SPECIFICATIONS (continued)Unless otherwise noted, the following specifications apply for V CC = +3.0V to +5.0V with T AMB = T MIN to T MAX .Typical Values apply at V CC = +3.3V or +5.0V and T AMB = 25o C.NOTE 2: Driver input hysteresis is typically 250mV.Capacitance for the SP3222 and the SP3232SP3222 and the SP3232Transmitting Data for the SP3222 and the SP3232TYPICAL PERFORMANCE CHARACTERISTICSUnless otherwise noted, the following performance characteristics apply for V CC = +3.3V, 235kbps data rates, all drivers loaded with 3k Ω, 0.1µF charge pump capacitors, and T AMB = +25°C.DESCRIPTIONThe SP3222E/3232E transceivers meet the EIA/TIA-232 and V.28/V.24 communication proto-cols and can be implemented in battery-pow-ered, portable, or hand-held applications such as notebook or palmtop computers. The SP3222E/3232E devices all feature Sipex's proprietary on-board charge pump circuitry that generates 2x V CC for RS-232 voltage levels from a single +3.0V to +5.5V power supply. This series is ideal for +3.3V-only systems, mixed +3.3V to +5.5V systems, or +5.0V-only systems that re-quire true RS-232 performance. The SP3222E/3232E series have drivers that operate at a typi-cal data rate of 235Kbps fully loaded.The SP3222E and SP3232E are 2-driver/2-re-ceiver devices ideal for portable or hand-held applications. The SP3222E features a 1µA shutdown mode that reduces power consump-tion and extends battery life in portable systems.Its receivers remain active in shutdown mode,allowing external devices such as modems to be monitored using only 1µA supply current.THEORY OF OPERATIONThe SP3222E/3232E series are made up of three basic circuit blocks: 1. Drivers, 2. Receivers,and 3. the Sipex proprietary charge pump.DriversThe drivers are inverting level transmitters that convert TTL or CMOS logic levels to ±5.0V EIA/TIA-232 levels inverted relative to the in-put logic levels. Typically, the RS-232 output voltage swing is ±5.5V with no load and at least ±5V minimum fully loaded. The driver outputs are protected against infinite short-circuits to ground without degradation in reliability. Driver outputs will meet EIA/TIA-562 levels of ±3.7V with supply voltages as low as 2.7V.The drivers typically can operate at a data rate of 235Kbps. The drivers can guarantee a data rate of 120Kbps fully loaded with 3K Ω in parallel with 1000pF, ensuring compatibility with PC-to-PC communication software.The slew rate of the driver output is internally limited to a maximum of 30V/µs in order to meet the EIA standards (EIA RS-232D 2.1.7, Para-graph 5). The transition of the loaded output from HIGH to LOW also meets the monotonic-ity requirements of the standard.The SP3222E/3232E drivers can maintain high data rates up to 240Kbps fully loaded. Figure 8shows a loopback test circuit used to test the RS-232 drivers. Figure 9 shows the test results of the loopback circuit with all drivers active at 120Kbps with RS-232 loads in parallel with 1000pF capacitors. Figure 10 shows the test results where one driver was active at 235Kbps and all drivers loaded with an RS-232 receiver in parallel with a 1000pF capacitor. A solid RS-232 data transmission rate of 120Kbps provides compatibility with many designs in personal computer peripherals and LAN applications.The SP3222E driver's output stages are turned off (tri-state) when the device is in shutdown mode. When the power is off, the SP3222E device permits the outputs to be driven up to ±12V. The driver's inputs do not have pull-up resistors. Designers should connect unused inputs to V CC or GND.In the shutdown mode, the supply current falls to less than 1µA, where SHDN = LOW. When the SP3222E device is shut down, the device's driver outputs are disabled (tri-stated) and the charge pumps are turned off with V+ pulled down to V CC and V- pulled to GND. The time required to exit shutdown is typically 100µs.Connect SHDN to V CC if the shutdown mode is not used. SHDN has no effect on RxOUT or RxOUTB. As they become active, the two driver outputs go to opposite RS-232 levels where one driver input is HIGH and the other LOW. Note that the drivers are enabled only when the magnitude of V- exceeds approximately 3V.ReceiversThe receivers convert EIA/TIA-232 levels to TTL or CMOS logic output levels. All receivers have an inverting tri-state output. These receiver outputs (RxOUT) are tri-stated when the enable control EN = HIGH. In the shutdown mode, the receivers can be active or inactive. EN has no effect on TxOUT. The truth table logic of the SP3222E/3232E driver and receiver outputs can be found in Table 2.Since receiver input is usually from a transmis-sion line where long cable lengths and system interference can degrade the signal, the inputs have a typical hysteresis margin of 300mV. This ensures that the receiver is virtually immune to noisy transmission lines. Should an input be left unconnected, a 5k Ω pulldown resistor to ground will commit the output of the receiver to a HIGH state.Charge PumpThe charge pump is a Sipex –patented design (5,306,954) and uses a unique approach com-pared to older less–efficient designs. The charge pump still requires four external capacitors, but uses a four–phase voltage shifting technique to attain symmetrical 5.5V power supplies. The internal power supply consists of a regulated dual charge pump that provides output voltages 5.5V regardless of the input voltage (V CC ) over the +3.0V to +5.5V range.In most circumstances, decoupling the power supply can be achieved adequately using a 0.1µF bypass capacitor at C5 (refer to Figures 6 and 7).In applications that are sensitive to power-sup-ply noise, decouple V CC to ground with a capaci-tor of the same value as charge-pump capacitor C1. Physically connect bypass capacitors as close to the IC as possible.The charge pumps operate in a discontinuous mode using an internal oscillator. If the output voltages are less than a magnitude of 5.5V, the charge pumps are enabled. If the output voltage exceed a magnitude of 5.5V, the charge pumps are disabled. This oscillator controls the four phases of the voltage shifting. A description of each phase follows.Phase 1— V SS charge storage — During this phase of the clock cycle, the positive side of capacitors C 1and C 2 are initially charged to V CC . C l + is then switched to GND and the charge in C 1– is trans-ferred to C 2–. Since C 2+ is connected to V CC , the voltage potential across capacitor C 2 is now 2times V CC .Phase 2— V SS transfer — Phase two of the clock con-nects the negative terminal of C 2 to the V SS storage capacitor and the positive terminal of C 2to GND. This transfers a negative generated voltage to C 3. This generated voltage is regu-lated to a minimum voltage of -5.5V. Simulta-neous with the transfer of the voltage to C 3, the positive side of capacitor C 1 is switched to V CC and the negative side is connected to GND.Phase 3— V DD charge storage — The third phase of the clock is identical to the first phase — the charge transferred in C 1 produces –V CC in the negative terminal of C 1, which is applied to the negative side of capacitor C 2. Since C 2+ is at V CC , the voltage potential across C 2 is 2 times V CC .Table 2. Truth Table Logic for Shutdown and Enable ControlN D H S N E T U O x T T U O x R 00e t a t s -i r T e v i t c A 01e t a t s -i r T e t a t s -i r T 10e v i t c A e v i t c A 11ev i t c A et a t s -i r TPhase 4— V DD transfer — The fourth phase of the clock connects the negative terminal of C 2 to GND,and transfers this positive generated voltage across C 2 to C 4, the V DD storage capacitor. This voltage is regulated to +5.5V. At this voltage,the internal oscillator is disabled. Simultaneous with the transfer of the voltage to C 4, the positive side of capacitor C 1 is switched to V CC and the negative side is connected to GND, allowing the charge pump cycle to begin again. The charge pump cycle will continue as long as the opera-tional conditions for the internal oscillator are present.Since both V + and V – are separately generated from V CC ; in a no–load condition V + and V – will be symmetrical. Older charge pump approaches that generate V – from V + will show a decrease in the magnitude of V – compared to V + due to the inherent inefficiencies in the design.The clock rate for the charge pump typically operates at 250kHz. The external capacitors can be as low as 0.1µF with a 16V breakdown voltage rating.ESD ToleranceThe SP3222E/3232E series incorporates ruggedized ESD cells on all driver output and receiver input pins. The ESD structure is improved over our previous family for more rugged applications and environments sensitive to electro-static discharges and associated transients. The improved ESD tolerance is at least ±15kV without damage nor latch-up.There are different methods of ESD testing applied:a) MIL-STD-883, Method 3015.7b) IEC1000-4-2 Air-Discharge c) IEC1000-4-2 Direct Contact The Human Body Model has been the generally accepted ESD testing method for semiconduc-tors. This method is also specified in MIL-STD-883, Method 3015.7 for ESD testing. The premise of this ESD test is to simulate the human body’spotential to store electro-static energy and discharge it to an integrated circuit. The simulation is performed by using a test model as shown in Figure 17. This method will test the IC’s capability to withstand an ESD transient during normal handling such as in manufacturing areas where the ICs tend to be handled frequently.The IEC-1000-4-2, formerly IEC801-2, is generally used for testing ESD on equipment and systems. For system manufacturers, they must guarantee a certain amount of ESD protection since the system itself is exposed to the outside environment and human presence.The premise with IEC1000-4-2 is that the system is required to withstand an amount of static electricity when ESD is applied to points and surfaces of the equipment that are accessible to personnel during normal usage.The transceiver IC receives most of the ESD current when the ESD source is applied to the connector pins. The test circuit for IEC1000-4-2is shown on Figure 18. There are two methods within IEC1000-4-2, the Air Discharge method and the Contact Discharge method.With the Air Discharge Method, an ESD voltage is applied to the equipment under test (EUT) through air. This simulates an electrically charged person ready to connect a cable onto the rear of the system only to find an unpleasant zap just before the person touches the back panel. The high energy potential on the person discharges through an arcing path to the rear panel of the system before he or she even touches the system. This energy, whether discharged directly or through air, is predominantly a function of the discharge current rather than the discharge voltage.Variables with an air discharge such as approach speed of the object carrying the ESD potential to the system and humidity will tend to change the discharge current. For example, the rise time of the discharge current varies with the approach speed.Figure 14. Charge Pump WaveformsThe Contact Discharge Method applies the ESD current directly to the EUT. This method was devised to reduce the unpredictability of the ESD arc. The discharge current rise time is constant since the energy is directly transferred without the air-gap arc. In situations such as hand held systems, the ESD charge can be directly discharged to the equipment from a person already holding the equipment. The current is transferred on to the keypad or the serial port of the equipment directly and then travels through the PCB and finally to the IC.The circuit models in Figures 17 and 18 represent the typical ESD testing circuits used for all three methods. The C S is initially charged with the DC power supply when the first switch (SW1) is on. Now that the capacitor is charged, the second switch (SW2) is on while SW1 switches off. The voltage stored in the capacitor is then applied through R S, the current limiting resistor, onto the device under test (DUT). In ESD tests, the SW2 switch is pulsed so that the device under test receives a duration of voltage.Figure 17. ESD Test Circuit for Human Body ModelFigure 18. ESD Test Circuit for IEC1000-4-2Figure 19. ESD Test Waveform for IEC1000-4-230AI ¥0A15At=30nst ¥t=0nsFor the Human Body Model, the current limiting resistor (R S ) and the source capacitor (C S ) are 1.5k Ω an 100pF, respectively. For IEC-1000-4-2, the current limiting resistor (R S )and the source capacitor (C S ) are 330Ω an 150pF,respectively.The higher C S value and lower R S value in the IEC1000-4-2 model are more stringent than the Human Body Model. The larger storage capacitor injects a higher voltage to the test point when SW2 is switched on. The lower current limiting resistor increases the current charge onto the test point.Device Pin Human Body IEC1000-4-2Tested Model Air Discharge Direct Contact LevelDriver Outputs ±15kV ±15kV ±8kV 4Receiver Inputs ±15kV±15kV±8kV4Table 3. Transceiver ESD Tolerance LevelsPACKAGE:PLASTIC SHRINKPACKAGE:PLASTICDUAL–IN–LINE (NARROW)PACKAGE:PLASTICPACKAGE:PLASTICSMALL OUTLINE (SOIC)(NARROW)DIMENSIONSin inches (mm) Minimum/Maximum Symbol16 Lead20 Lead D0.193/0.2010.252/0.260(4.90/5.10)(6.40/6.60)e0.026 BSC0.026 BSC(0.65 BSC)(0.65 BSC)PACKAGE:PLASTIC THINSMALL OUTLINE(TSSOP)ORDERING INFORMATIONModel Temperature Range Package Type SP3222ECA.............................................0˚C to +70˚C..........................................20-Pin SSOP SP3222ECP.............................................0˚C to +70˚C............................................18-Pin PDIP SP3222ECT.............................................0˚C to +70˚C...........................................18-Pin SOIC SP3222ECY.............................................0˚C to +70˚C........................................20-Pin TSSOP SP3222EEA............................................-40˚C to +85˚C........................................20-Pin SSOP SP3222EEP............................................-40˚C to +85˚C..........................................18-Pin PDIP SP3222EET............................................-40˚C to +85˚C.........................................18-Pin SOIC SP3222EEY............................................-40˚C to +85˚C......................................20-Pin TSSOP SP3232ECA.............................................0˚C to +70˚C..........................................16-Pin SSOP SP3232ECP.............................................0˚C to +70˚C............................................16-Pin PDIP SP3232ECT.............................................0˚C to +70˚C..................................16-Pin Wide SOIC SP3232ECN.............................................0˚C to +70˚C.........................................16-Pin nSOIC SP3232ECY.............................................0˚C to +70˚C........................................16-Pin TSSOP SP3232EEA............................................-40˚C to +85˚C........................................16-Pin SSOP SP3232EEP............................................-40˚C to +85˚C..........................................16-Pin PDIP SP3232EET............................................-40˚C to +85˚C................................16-Pin Wide SOIC SP3232EEN............................................-40˚C to +85˚C.......................................16-Pin nSOIC SP3232EEY............................................-40˚C to +85˚C......................................16-Pin TSSOP。

adm202参数

adm202参数ADM202是一种常见的双路RS-232驱动器/接收器,用于将逻辑电平转换为RS-232电平。

它通常用于串行通信中,将数字信号转换为可以在电缆上传输的电压。

ADM202具有多种应用领域,例如计算机网络、工业自动化和通信设备等。

ADM202的工作原理非常简单。

它接收来自逻辑电路的输入信号,并将其转换为符合RS-232标准的电平。

这样,它可以将来自计算机或其他设备的数字信号转换为适合串行通信的电压。

ADM202还具有保护电路,可以保护输入和输出免受电压浪涌和静电放电的损害。

ADM202的设计使其非常适合在工业环境中使用。

它具有较高的电压转换能力和较强的抗干扰能力,能够在恶劣的工作条件下稳定运行。

此外,ADM202还具有低功耗和小尺寸的特点,使其易于集成到各种设备中。

ADM202不仅具有出色的性能,还具有广泛的兼容性。

它可以与各种RS-232设备配合使用,如计算机、打印机、调制解调器等。

ADM202还支持多种通信速率,从低速的300bps到高速的115.2kbps都可以实现可靠的数据传输。

除了常见的应用领域外,ADM202还在一些特殊的领域中得到了广泛的应用。

例如,在医疗设备中,ADM202可以用于将传感器数据传输到计算机,实时监测患者的生命体征。

在工业自动化中,ADM202可以用于控制系统之间的数据交换,实现智能化生产。

在通信设备中,ADM202可以用于将数字信号转换为模拟信号,实现语音通信。

ADM202作为一种双路RS-232驱动器/接收器,具有广泛的应用领域和出色的性能。

它的设计使其适用于各种工作环境,并且与其他设备兼容性强。

无论是在计算机网络、工业自动化还是通信设备中,ADM202都发挥着重要的作用,为数据传输提供可靠的解决方案。

无论是在医疗设备中监测患者的生命体征,还是在工业自动化中实现智能化生产,ADM202都是不可或缺的关键组件。

相信随着技术的不断发展,ADM202将继续在各个领域中发挥重要作用,推动着人类社会的进步与发展。

MEMORY存储芯片MAX232EEPE中文规格书

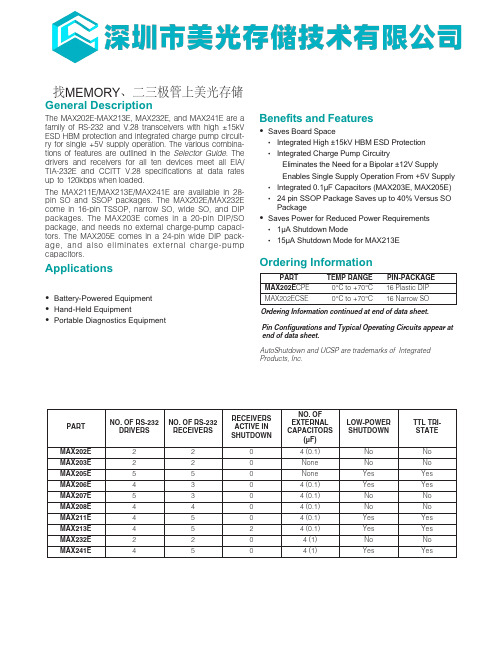

General Description The MAX202E-MAX213E, MAX232E, and MAX241E are afamily of RS-232 and V.28 transceivers with high ±15kVESD HBM protection and integrated charge pump circuit-ry for single +5V supply operation. The various combina-tions of features are outlined in the Selector Guide. Thedrivers and receivers for all ten devices meet all EIA/TIA-232E and CCITT V.28 specifications at data ratesup to 120kbps when loaded.The MAX211E/MAX213E/MAX241E are available in 28-pin SO and SSOP packages. The MAX202E/MAX232Ecome in 16-pin TSSOP, narrow SO, wide SO, and DIPpackages. The MAX203E comes in a 20-pin DIP/SOpackage, and needs no external charge-pump capaci-tors. The MAX205E comes in a 24-pin wide DIP pack-age, and also eliminates external charge-pumpcapacitors.Applications•Battery-Powered Equipment•Hand-Held Equipment•Portable Diagnostics Equipment Benefits and Features •Saves Board Space •Integrated High ±15kV HBM ESD Protection •Integrated Charge Pump Circuitry Eliminates the Need for a Bipolar ±12V Supply Enables Single Supply Operation From +5V Supply •Integrated 0.1µF Capacitors (MAX203E, MAX205E)•24 pin SSOP Package Saves up to 40% Versus SO Package •Saves Power for Reduced Power Requirements •1µA Shutdown Mode •15µA Shutdown Mode for MAX213E Yes PART NO. OF RS-232DRIVERSNO. OF RS-232RECEIVERS RECEIVERS ACTIVE IN SHUTDOWNNO. OF EXTERNAL CAPACITORS (µF)LOW-POWER SHUTDOWNTTL TRI-STATE MAX202E 220 4 (0.1)No No MAX203E 220None No No MAX205E 550None Yes Yes MAX206E 430 4 (0.1)Yes Yes MAX207E 530 4 (0.1)No No MAX208E 440 4 (0.1)No No MAX211E 450 4 (0.1)Yes Yes MAX213E 452 4 (0.1)Yes Yes MAX232E 220 4 (1)No No MAX241E450 4 (1)Yes Ordering Information Ordering Information continued at end of data sheet.Pin Configurations and Typical Operating Circuits appear atend of data sheet.AutoShutdown and UCSP are trademarks of IntegratedProducts, Inc.找MEMORY 、二三极管上美光存储MAX202E–MAX213E, MAX232E/MAX241E±15kV ESD-Protected, 5V RS-232 TransceiversFigure 3. Transition Slew-Rate CircuitDetailed DescriptionThe MAX202E–MAX213E, MAX232E/MAX241E consist of three sections: charge-pump voltage converters, dri-vers (transmitters), and receivers. These E versions provide extra protection against ESD. They survive ±15kV discharges to the RS-232 inputs and outputs, tested using the Human Body Model. When tested according to IEC1000-4-2, they survive ±8kV contact-discharges and ±15kV air-gap discharges. The rugged E versions are intended for use in harsh environments or applications where the RS-232 connection is fre-quently changed (such as notebook computers). The standard (non-“E”) MAX202, MAX203, MAX205–MAX208, MAX211, MAX213, MAX232, and MAX241 are recommended for applications where cost is critical.+5V to ±10V Dual Charge-PumpVoltage ConverterThe +5V to ±10V conversion is performed by dual charge-pump voltage converters (F igure 4). The first charge-pump converter uses capacitor C1 to double the +5V into +10V, storing the +10V on the output filter capacitor, C3. The second uses C2 to invert the +10V into -10V, storing the -10V on the V- output filter capaci-tor, C4.In shutdown mode, V+ is internally connected to V CC by a 1kΩpull-down resistor, and V- is internally connected to ground by a 1kΩpull up resistor.RS-232 DriversWith V CC= 5V, the typical driver output voltage swing is ±8V when loaded with a nominal 5kΩRS-232 receiv-er. The output swing is guaranteed to meet EIA/TIA-232E and V.28 specifications that call for ±5V minimum output levels under worst-case conditions. These include a 3kΩload, minimum V CC, and maximum oper-ating temperature. The open-circuit output voltage swings from (V+ - 0.6V) to V-.Input thresholds are CMOS/TTL compatible. The unused drivers’ inputs on the MAX205E–MAX208E, MAX211E, MAX213E, and MAX241E can be left uncon-nected because 400kΩpull up resistors to V CC are included on-chip. Since all drivers invert, the pull up resistors force the unused drivers’ outputs low. The MAX202E, MAX203E, and MAX232E do not have pull up resistors on the transmitter inputs.Integrated | 9。

ADM3232EARNZ中文资料

ground

Output Voltage Swing (RS-562) ±3.7

V

VCC = 3.0 V

Transmitter Output Resistance 300

元器件交易网

ADM3232E

TABLE OF CONTENTS

Features .............................................................................................. 1 Applications....................................................................................... 1 Functional Block Diagram .............................................................. 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Specifications..................................................................................... 3 Absolute Maximum Ratings............................................................ 4

ADM2682E_2687E_cn

应用

隔离式RS-485/RS-422接口 工业现场网络 多点数据传输系统

功能框图

VCC

isoPower DC-TO-DC CONVERTER

VISOOUT

OSCILLATOR

RECTIFIER

REGULATOR

修订历史

2011年7月—修订版0:初始版

开关特性 .......................................................................................... 15 电路描述 .......................................................................................... 16

信号隔离..................................................................................... 16 电源隔离..................................................................................... 16 真值表 ......................................................................................... 16 热关断 ......................................................................................... 16 开路和短路故障保护接收器输入......................................... 16 直流正确性和磁场抗扰度 ...................................................... 16 应用信息 .......................................................................................... 18 PCB布局...................................................................................... 18 EMI考虑因素............................................................................. 18 隔离寿命..................................................................................... 19 隔离电源考虑因素 ................................................................... 19 典型应用..................................................................................... 20 外形尺寸 .......................................................................................... 22 订购指南..................................................................................... 22

sp3232中文资料说明书

注释 1:V+和 V-幅值最大可达 7V,但他们的绝对差值不能超过 13V。

参数规范

除 非 特 别 规 定 , 以 下 规 范 适 用 于 Vcc = +3.0V~5.0V ; TAMB=TMIN~TMAX 。 典 型 值 的 适 用 条 件 :

VCC=+3.3V~5.0V 和 TAMB=25℃。

参数

图 5 SP3222E 管脚配置

VCC

+ C5 0.1u F

19 VCC

u

2 C1+ +

3

V+

+

C1 0.1u F

*C3 0.1u F

u

u

4 C1-

5 C2+

V- 7

+

C2 0.1 u F 6 C2-

C4 0.1 u F

u

+

u

13 T1IN 12 T2IN

T1OUT 17 T2OUT 8

RS-232

ns

ns

|tPHL-tPLH|, TAMB=25℃

ns

|tPHL-tPLH|

3

续上表 参数

转换区中的电压 变化速度

最小

典型

最大 30

单位 V/µS

条件 VCC=3.3V,RL=3KΩ,TAMB=25 ℃ , 测 量 范 围 -3.0V~+3.0V 或 +3.0V~-3.0V

注释 2:驱动器输入滞后典型值为 250mV。

VCC=5.0V, 注释 2

µA

TXIN, EN , SHDN ,

TAMB=+25℃

µA

接收器禁用

V

IOUT=1.6mA

半导体芯片ADM3202ARNZ-REEL中文规格书

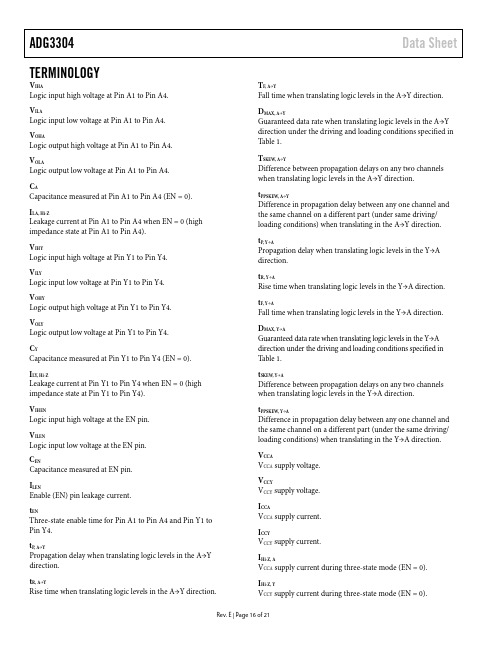

ADG3304Data Sheet Rev. E | Page 16 of 21TERMINOLOGYV IHALogic input high voltage at Pin A1 to Pin A4. V ILALogic input low voltage at Pin A1 to Pin A4. V OHA Logic output high voltage at Pin A1 to Pin A4. V OLA Logic output low voltage at Pin A1 to Pin A4. C A Capacitance measured at Pin A1 to Pin A4 (EN = 0). I LA, Hi-ZLeakage current at Pin A1 to Pin A4 when EN = 0 (high impedance state at Pin A1 to Pin A4).V IHYLogic input high voltage at Pin Y1 to Pin Y4. V ILYLogic input low voltage at Pin Y1 to Pin Y4. V OHY Logic output high voltage at Pin Y1 to Pin Y4. V OLY Logic output low voltage at Pin Y1 to Pin Y4. C Y Capacitance measured at Pin Y1 to Pin Y4 (EN = 0). I LY , Hi-ZLeakage current at Pin Y1 to Pin Y4 when EN = 0 (high impedance state at Pin Y1 to Pin Y4).V IHENLogic input high voltage at the EN pin.V ILENLogic input low voltage at the EN pin.C ENCapacitance measured at EN pin.I LENEnable (EN) pin leakage current.t ENThree-state enable time for Pin A1 to Pin A4 and Pin Y1 to Pin Y4.t P , A→YPropagation delay when translating logic levels in the A→Y direction.t R, A→YRise time when translating logic levels in the A→Y direction. T F, A→Y Fall time when translating logic levels in the A→Y direction. D MAX, A→Y Guaranteed data rate when translating logic levels in the A→Y direction under the driving and loading conditions specified in Table 1. T S KEW , A→Y Difference between propagation delays on any two channels when translating logic levels in the A→Y direction. t PPSKEW , A→Y Difference in propagation delay between any one channel and the same channel on a different part (under same driving/ loading conditions) when translating in the A→Y direction. t P , Y→A Propagation delay when translating logic levels in the Y→A direction. t R, Y→A Rise time when translating logic levels in the Y→A direction. t F, Y→A Fall time when translating logic levels in the Y→A direction. D MAX, Y→A Guaranteed data rate when translating logic levels in the Y→A direction under the driving and loading conditions specified in Table 1. t S KEW , Y→A Difference between propagation delays on any two channels when translating logic levels in the Y→A direction. t PPSKEW , Y→A Difference in propagation delay between any one channel and the same channel on a different part (under the same driving/ loading conditions) when translating in the Y→A direction. V CCA V CCA supply voltage. V CCY V CCY supply voltage. I CCA V CCA supply current. I CCY V CCY supply current. I Hi-Z, A V CCA supply current during three-state mode (EN = 0). I Hi-Z, Y V CCY supply current during three-state mode (EN = 0).Data SheetADG3304 Rev. E | Page 17 of 21THEORY OF OPERATIONThe ADG3304 level translator allows the level shifting necessary for data transfer in a system where multiple supply voltages are used. The device requires two supplies, V CCA and V CCY (V CCA ≤ V CCY ). These supplies set the logic levels on each side of the device. When driving the A pins, the device translates the V CCA -compatible logic levels to V CCY -compatible logic levels available at the Y pins. Similarly, because the device is capable of bidirectional translation, when driving the Y pins, the V CCY -compatible logic levels are translated to V CCA -compatible logic levels available at the A pins. When EN = 0, Pin A1 to Pin A4 and Pin Y1 to Pin Y4 are three-stated. When EN is driven high, the ADG3304 goes into normal operation mode and performs level translation. LEVEL TRANSLATOR ARCHITECTURE The ADG3304 consists of four bidirectional channels. Each channel can translate logic levels in either the A→Y or the Y→A direction. It uses a one-shot accelerator architecture, which ensures excellent switching characteristics. Figure 39 shows a simplified block diagram of a bidirectional channel.Y 04860-053Figure 39. Simplified Block Diagram of an ADG3304 Channel The logic level translation in the A→Y direction is performed using a level translator (U1) and an inverter (U2), while the translation in the Y→A direction is performed using Inverter U3 and Inverter U4. The one-shot generator detects a rising or falling edge present on either the A side or the Y side of the channel. It sends a short pulse that turns on the PMOS transistors (T1 to T2) for a rising edge, or the NMOS transistors (T3 to T4) for a falling edge. This charges/discharges the capacitive load faster, which results in faster rise and fall times.The inputs of the unused channels (A or Y) should be tied to their corresponding V CC rail (V CCA or V CCY ) or to GND. INPUT DRIVING REQUIREMENTS To ensure correct operation of the ADG3304, the circuit that drives the input of the ADG3304 channels should have an output impedance of less than or equal to 150 Ω and a minimum peak current driving capability of 36 mA. OUTPUT LOAD REQUIREMENTS The ADG3304 level translator is designed to drive CMOS-compatible loads. If current-driving capability is required, it is recommended to use buffers between the ADG3304 outputs and the load. ENABLE OPERATIONThe ADG3304 provides three-state operation at the A and Y I/O pins by using the enable pin (EN), as shown in Table 5. Table 5. Truth TableENY I/O Pins A I/O Pins 0Hi-Z 1 Hi-Z 1 1Normal operation 2Normal operation 21High impedance state.2 In normal operation, the ADG3304 performs level translation.While EN = 0, the ADG3304 enters into three-state mode. In this mode, the current consumption from both the V CCA and V CCY supplies is reduced, allowing the user to save power, which is critical, especially on battery-operated systems. The EN input pin can be driven with either V CCA -compatible or V CCY -compatible logic levels.POWER SUPPLIESFor proper operation of the ADG3304, the voltage applied to the V CCA must be less than or equal to the voltage applied to V CCY . To meet this condition, the recommended power-up sequence is V CCY first and then V CCA . The ADG3304 operates properly only after both supply voltages reach their nominal values. It is not recommended to use the part in a system where, during power-up, V CCA can be greater than V CCY due to a significant increase in the current taken from the V CCA supply. For optimum performance, the V CCA pin and V CCY pin should be decoupled to GND as close as possible to the device.。

MEMORY存储芯片MAX232AESE+T中文规格书

Integrated | 10Shutdown and Enable Control (MAX205E/MAX206E/MAX211E/MAX213E/MAX241E)In shutdown mode, the charge pumps are turned off,V+ is pulled down to V CC , V- is pulled to ground, and the transmitter outputs are disabled. This reduces sup-ply current typically to 1µA (15µA for the MAX213E).The time required to exit shutdown is under 1ms, asshown in Figure 5.Receivers All MAX213E receivers, except R4 and R5, are put into a high-impedance state in shutdown mode (see Tables 1a and 1b). The MAX213E’s R4 and R5 receivers still function in shutdown mode. These two awake-in-shut-down receivers can monitor external activity while main-taining minimal power consumption.The enable control is used to put the receiver outputs into a high-impedance state, to allow wire-OR connection of two EIA/TIA-232E ports (or ports of different types) at the UART. It has no effect on the RS-232 drivers or the charge pumps.Note: The enable c ontrol pin is ac tive low for the MAX211E/MAX241E (EN ), but is ac tive high for theMAX213E (EN). The shutdown control pin is active highFigure 4. Charge-Pump DiagramWhen in low-power shutdown mode, the MAX205E/MAX206E/MAX211E/MAX213E/MAX241E driver outputsare turned off and draw only leakage currents—even ifthey are back-driven with voltages between 0V and12V. Below -0.5V in shutdown, the transmitter output isdiode-clamped to ground with a 1k Ω series imped-ance.RS-232 ReceiversThe receivers convert the RS-232 signals to CMOS-logicoutput levels. The guaranteed 0.8V and 2.4V receiverinput thresholds are significantly tighter than the ±3Vthresholds required by the EIA/TIA-232E specification.This allows the receiver inputs to respond to TTL/CMOS-logic levels, as well as RS-232 levels.The guaranteed 0.8V input low threshold ensures thatreceivers shorted to ground have a logic 1 output. The5k Ω input resistance to ground ensures that a receiverwith its input left open will also have a logic 1 output.Receiver inputs have approximately 0.5V hysteresis.This provides clean output transitions, even with slowrise/fall-time signals with moderate amounts of noiseand ringing.In shutdown, the MAX213E’s R4 and R5 receivers haveno hysteresis.找MEMORY 、二三极管上美光存储Integrated | 13MAX202E–MAX213E,MAX232E/MAX241E ±15kV ESD-Protected, 5V RS-232 Transceivers outputs. Therefore,after PC board assembly,theMachine Model is less relevant to I/O ports.Applications InformationCapacitor SelectionThe capacitor type used for C1–C4 is not critical forproper operation. The MAX202E, MAX206–MAX208E,MAX211E, and MAX213E require 0.1µF capacitors,and the MAX232E and MAX241E require 1µF capaci-tors, although in all cases capacitors up to 10µF canbe used without harm. Ceramic, aluminum-electrolytic,or tantalum capacitors are suggested for the 1µFcapacitors, and ceramic dielectrics are suggested forthe 0.1µF capacitors. When using the minimum recom-mended capacitor values, make sure the capacitancevalue does not degrade excessively as the operatingtemperature varies. If in doubt, use capacitors with alarger (e.g., 2x) nominal value. The capacitors’ effec-tive series resistance (ESR), which usually rises at lowtemperatures, influences the amount of ripple on V+and V-.Use larger capacitors (up to 10µF) to reduce the outputimpedance at V+ and V-. This can be useful when“stealing” power from V+ or from V-. The MAX203E andMAX205E have internal charge-pump capacitors.Bypass V CC to ground with at least 0.1µF. In applica-tions sensitive to power-supply noise generated by the charge pumps, decouple V CC to ground with a capaci-tor the same size as (or larger than) the charge-pump capacitors (C1–C4).V+ and V- as Power Supplies A small amount of power can be drawn from V+ and V-,although this will reduce both driver output swing and noise margins. Increasing the value of the charge-pump capacitors (up to 10µF ) helps maintain performance when power is drawn from V+ or V-.Driving Multiple Receivers Each transmitter is designed to drive a single receiver.Transmitters can be paralleled to drive multiple receivers.Driver Outputs when Exiting Shutdown The driver outputs display no ringing or undesirable transients as they come out of shutdown.High Data Rates These transceivers maintain the RS-232 ±5.0V mini-mum driver output voltages at data rates of over 120kbps. F or data rates above 120kbps, refer to the Transmitter Output Voltage vs. Load Capacitance graphs in the Typical Operating Characteristics .Communication at these high rates is easier if the capacitive loads on the transmitters are small; i.e.,short cables are best.Table 2. Summary of EIA/TIA-232E, V.28 Specifications PARAMETERCONDITIONS EIA/TIA-232E, V.28 SPECIFICA-TIONS 0 Level3k Ωto 7k Ωload +5V to +15V Data Rate 3k Ω≤R L ≤7k Ω, C L ≤2500pFUp to 20kbps +3V to +15V Instantaneous Slew Rate, Max 3k Ω≤R L ≤7k Ω, C L ≤2500pF 30V/µsDriver Output Short-Circuit Current, Max 100mATransition Rate on Driver Output V.281ms or 3% of the period Driver Output Resistance-2V < V OUT < +2V 300ΩEIA/TIA-232E4% of the period Driver Output Level, Max No load±25V Driver Output Voltage 3k Ωto 7k Ωload-5V to -15V 0 Level1 Level 1 Level Receiver Input Level ±25VReceiver Input Voltage -3V to -15V。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

T1

T2

+

+ +

C3 0.1µF 6.3V

C4 0.1µF 10V

C5 0.1µF

T1OUT T2OUT

RS-232 OUTPUTS

TTL/CMOS OUTPUTS

R1OUT R2OUT

R1 R2 GND

R1IN

5kΩ

RS-232

INPUTS*

R2IN

5kΩ

*INTERNAL 5kΩ PULL-DOWN RESISTOR ON EACH RS-232 INPUT.

FUNCTIONAL BLOCK DIAGRAM

+3.3V INPUT

C1 + 0.1µF

10V

C2 + 0.1µF

10V

TTL/CMOS INPUTS

T1IN T2IN

ADM3232E

C1+

+3.3V TO +6.6V VOLTAGE

VCC

C1– DOUBLER V+

C2+ +6.6V TO –6.6V V– VOLTAGE

ADM3232E

TABLE OF CONTENTS

Features .............................................................................................. 1 Applications....................................................................................... 1 Functional Block Diagram .............................................................. 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Specifications..................................................................................... 3 Absolute Maximum Ratings............................................................ 4

GENERAL DESCRIPTION

The ADM3232E transceiver is a high speed, 2-channel RS-232/V.28 interface device that operates from a single 3.3 V power supply. Low power consumption makes it ideal for battery-powered portable instruments. The ADM3232E conforms to the EIA-232E and ITU-T V.28 specifications and operates at data rates up to 460 kbps. All RS-232 (TxOUT and RxIN) and TTL/CMOS (TxIN and RxOUT) inputs and outputs are protected against electrostatic discharges (up to ±15 kV ESD protection). This ensures compliance with IEC 1000-4-2 requirements. This device is ideally suited for operation in electrically harsh environments or where RS-232 cables are frequently plugged/ unplugged, with the ±15 kV ESD protection of the ADM3232E input/output pins.

±15 kV ESD Protected, 3.3 V, RS-232 Line Driver/Receiver ADM3232E

FEATURES

Data rate: 460 kbps 2 Tx and 2 Rx Meets EIA-232E specifications 0.1 μF charge pump capacitors ESD protection to IEC 1000-4-2 (801.2) on TTL/CMOS and

RS-232 I/Os Contact discharge: ±8 kV Air gap discharge: ±15 kV

APPLICATIONS

General-purpose RS-232 data link Portable instruments Handsets Industrial/telecom diagnostic ports

Rev. A | Page 2 of 12

ADM3232E

SPECIFICATIONS

VCC = 3.3 V ± 0.3 V, C1 to C4 = 0.1 μF; all specifications TMIN to TMAX, unless otherwise noted.ogic Pull-Up Current

5

10

μA

TIN = GND to VCC

Transmitter Input Hysteresis

0.5

V

RS-232 RECEIVER

Input Voltage Range

−30

+30 V

Input Threshold Low

0.6

1.2

V

Input Threshold High

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113 ©2006–2008 Analog Devices, Inc. All rights reserved.

ESD Caution.................................................................................. 4

REVISION HISTORY

7/08—Rev. 0 to Rev. A Added 16-Lead SOIC .........................................................Universal Updated Outline Dimensions ......................................................... 9 Changes to Ordering Guide ...........................................................10 12/06—Revision 0: Initial Version

Min

Typ Max Unit Test Conditions/Comments

DC CHARACTERISTICS

Operating Voltage Range

3.0

3.3

5.5 V

VCC Power Supply Current

1.3

3

mA No load

LOGIC

Input Logic Threshold Low, VINL

0.8 V

TIN

Input Logic Threshold High, VINH

2.0

V

TIN

TTL/CMOS Output Voltage Low, VOL

0.4 V

IOUT = 1.6 mA

TTLCMOS Output Voltage High, VOH VCC − 0.6

V

IOUT = −1 mA

Four external 0.1 μF charge pump capacitors are used for the voltage doubler/inverter, permitting operation from a single 3.3 V supply.

The ADM3232E is available in a 16-lead narrow and wide SOIC packages, as well as a space-saving 16-lead TSSOP.

Circuit Description .......................................................................8 High Baud Rate..............................................................................8 Outline Dimensions ..........................................................................9 Ordering Guide .......................................................................... 10