基于FPGA的高灵敏度数字磁通门设计

基于FPGA指纹识别的智能门禁系统设计

I

摘要

Abstract

In the rapid rise of the technology of modern life, one for identity authentication is no longer rude mechanical manipulation .Especially , in the rapid changing technology of the Internet , biometric technology , with reliability, practicality and safety advantages , is first brought into people's consideration. However, compared to other biometrics, the technology of fingerpr int identificatio, with its many good aspects ,can be used by people In most fields . At present, Internet devices, smart appliances, Bank & Financial, security and other sectors have tended to apply authentication based on the technology of fingerprint identificatio n. Intelligent Access Control System is the fusion of image recognition, control engineer ing, electronic locks and other products of modern science and technology. This system ,with it’sreliability, ease of operation, intelligence, has been more widely used in security. There are various control mode in intelligent entrance guard system.However, FPGA ,with its running speed, pin-rich (easyed to implement large-scale systems), internal processes run in parallel (handle more complex functions), and lots of soft core (conveniented for secondary development) ,have attracted more attention, and it has a bright prospect in the access control market! This was designed and implemented by FPGA technology,it can control fingerprint module, and make the fingerprint match the collecting, storing, deleting, and so on. Paper made a brief introduction of fingerprint processing and focused FPGA’s control of fingerprint module, and the analysis of some situation and how to solve it.. Keywords: FPGA, intelligent access control, fingerprint活中,人们对于身份的认证,已经不再是采取简单而粗暴的机 械操纵。尤其是在物联网技术日新月异的今天,拥有可靠性、实用性与安全性等优势条件 的生物识别技术,首当其冲的被纳入人们的考虑对象。然而,相比于其他生物识别 技术, 指纹识别技术以其诸多方面可利用性得到了人们的青睐。目前,互联网设备、智能 电器、 金融领域、保全等行业都已趋向于应用指纹识别技术为基础的身份验证。 智能门禁系统是融合图像识别、控制工程、电控锁等现代科技的产物。它操作的可靠 性、方便性、智能化也使其能够在安防得到了更加广泛的应用。智能门禁系统存在各种控 制方式,而 FPGA 以其运行速度快,管脚丰富(容易实现大规模系统) ,内部程序并行运行 (可以处理更复杂功能) ,拥有大量软核(可以方便进行二次开发)愈发受到人们关注,在 未来的门禁市场拥有广阔的前景! 本次设计通过 FPGA 技术实现了对指纹模块的控制,完成指纹的采集、存储、删除、匹 配等工作。论文对指纹处理做了简单介绍,重点突出 FPGA 对指纹模块的控制,并且对所出 现的情况加以分析解决。 关键字:FPGA ,智能门禁,指纹识别

高灵敏度的磁通门传感器

高灵敏度的磁通门传感器

张瑞平;刘俊;刘文怡

【期刊名称】《弹箭与制导学报》

【年(卷),期】2005(025)001

【摘要】文中提出了一种线圈为对称结构的磁通门传感器,介绍了其工作原理,检测电路采用检测与外磁场有关的多个偶次谐波,这样可以达到减小噪声的目的,从而提高了传感器的灵敏度.

【总页数】3页(P246-248)

【作者】张瑞平;刘俊;刘文怡

【作者单位】中北大学,教育部仪器科学与动态测试重点实验室,太原,030051;太原科技大学,太原,030024;中北大学,教育部仪器科学与动态测试重点实验室,太

原,030051;中北大学,教育部仪器科学与动态测试重点实验室,太原,030051

【正文语种】中文

【中图分类】TP2

【相关文献】

1.基于FPGA的高灵敏度数字磁通门设计 [J], 左超;杨晓非;刘腾飞

2.高灵敏度的磁通门传感器 [J], 张瑞平;刘俊;刘文怡

3.新型的高灵敏度低噪声微功耗磁通门磁强计 [J], 张法钧

4.江苏多维科技在国际传感器博览会推出超高灵敏度TMR磁开关传感器 [J], 江苏多维科技有限公司

5.基于磁通门和磁阻传感器的混合宽带磁传感器的研究与设计 [J], 许朋博;王鲜然;欧阳君;杨晓非

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的高灵敏度数字磁通门设计

基于FPGA的高灵敏度数字磁通门设计

左超;杨晓非;刘腾飞

【期刊名称】《仪表技术与传感器》

【年(卷),期】2010(000)009

【摘要】描述了一种基于FPGA的新型数字磁通门驱动电路.系统运用数字信号处理方法替代了传统的方波产生、相敏检波等模块,并且通过数字平滑滤波方法进行信号处理.系统分辨率高达19nT,线性区间为13 000~15 900nT.实验结果表明该设计在减少硬件开销的同时显著提高了系统输出的稳定性和精度.

【总页数】3页(P57-59)

【作者】左超;杨晓非;刘腾飞

【作者单位】华中科技大学电子科学与技术系,湖北武汉,430074;华中科技大学电子科学与技术系,湖北武汉,430074;华中科技大学电子科学与技术系,湖北武

汉,430074

【正文语种】中文

【中图分类】TP212

【相关文献】

1.基于FPGA的数字磁通门传感器系统设计和实现 [J], 刘仕伟;刘诗斌

2.基于异或运算相敏整流的数字磁通门设计 [J], 崔智军

3.基于FPGA的单轴数字磁通门传感电路设计 [J], 韦金芬

4.基于FPGA的数字磁通门信号处理 [J], 王建华;高卜;赵磊

5.一种基于改进型数字相敏整流电路的磁通门传感器设计 [J], ZHANG Yunshan;CUI Gongjun

因版权原因,仅展示原文概要,查看原文内容请购买。

(完整版)基于FPGA的等精度频率计的设计与实现毕业论文

第一章课题研究概述1.1课题研究的目的和意义在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

目前常用的测频方案有三种:方案一:完全按定义式F=N/T进行测量。

被测信号Fx经放大整形形成时标ГX,晶振经分频形成时基TR。

用时基TR开闸门,累计时标ГX的个数,则有公式可得Fx=1/ГX=N/TR。

此方案为传统的测频方案,其测量精度将随被测信号频率的下降而降低。

方案二:对被信号的周期进行测量,再利用F=1/T(频率=1/周期)可得频率。

测周期时,晶振FR经分频形成时标ГX,被测信号经放在整形形成时基TX控制闸门。

闸门输出的计数脉冲N=ГX/TR,则TX=NГX。

但当被测信号的周期较短时,会使精度大大下降。

方案三:等精度测频,按定义式F=N/T进行测量,但闸门时间随被测信号的频率变化而变化。

如图1所示,被测信号Fx经放大整形形成时标ГX,将时标ГX经编程处理后形成时基TR。

用时基TR开闸门,累计时标ГX的个数,则有公式可得Fx=1/ГX=N/TR。

此方案闸门时间随被测信号的频率变化而变化,其测量精度将不会随着被测信号频率的下降而降。

本次实验设计中采用的是第三种测频方案。

等精度频率计是数字电路中的一个典型应用,其总体设计方案有两种:方案一:采用数字逻辑电路制作,用IC拼凑焊接实现。

其特点是直接用现成的IC组合而成,简单方便,但由于使用的器件较多,连线复杂,体积大,功耗大,焊点和线路较多将使成品稳定度与精确度大打折扣,而且会产生比较大的延时,造成测量误差、可靠性差。

方案二:采用可编程逻辑器件(CPLD)制作。

随着现场可编程门阵列FPGA的广泛应用,以EDA工具作为开发手段,运用VHDL等硬件描述语言语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。

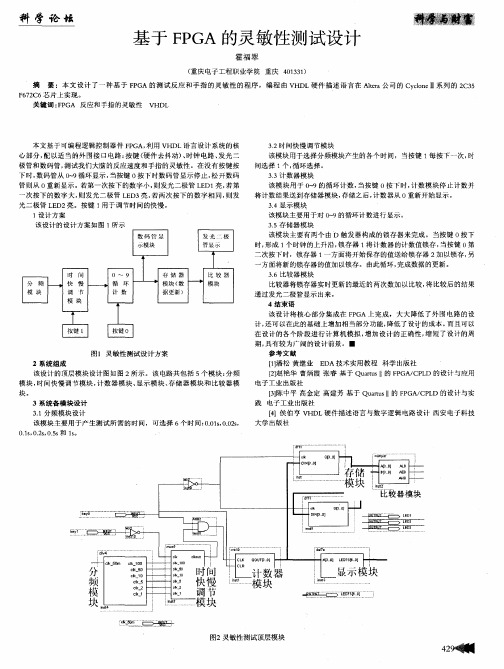

基于FPGA的灵敏性测试设计

3 . 2时间快慢 调节模块 该模块用于选择 分频模块产 生的各个 时间,当按键 1每按下一次, 时

间 选 择 1个 , 循环选择 。 3 . 3计 数 器 模 块

该模块用 于 0  ̄ 9的循环 计数, 当按键 0按 下时, 计数模块停 止计数并

将计数结果送到存储器模块, 存储 之 后 , 计 数 器 从 0重 新 开 始 显 示 。 3 . 4显 示模 块

该模块主要用于对 o  ̄ 9的循环计数进行显示 。

3 . 5存 储 器 模 块

该设计 的设计方案如 图 1所示

数 码 舒 显 示 模块 发 光 二 极

管 示

该模块主要有两个 由 D 触发器构成 的锁存器来完成 。当按键 0按下 时, 形成 1个时钟 的上升沿 , 锁 存器 1 将计 数器的计数值锁存, 当按键 0第 二次按下时,锁存器 1一方 面将 开始 保存 的值送 给锁存器 2加 以锁存, 另 方面将新的锁存器的值加以锁存 。由此循环 , 完成数据的更新。 3 . 6比较 器 模 块

F 6 7 2 C 6芯 片上 实 现 。

关键词 : F P G A 反应和手指 的灵敏性

本 文基于可编程逻辑控制器件 F P GA, 利用 VHDL语言设计系统的核 心部分, 配 以适 当的外 围接 口电路 : 按键 ( 硬件去抖 动) 、 时钟 电路 、 发光二 极管和 数码管 , 测试我们 大脑 的反应速度和手指 的灵 敏性。在没有按键按 下时, 数码管从 0 - - 9 循环 显示, 当按键 0按下 时数码 管显示停止, 松开数码 管则从 0重新 显示 。若第一次按下的数字小, 则发光二极 管 L E D1 亮, 若第 次按下的数字大, 则发光二极管 L E D3亮 , 若两 次按下的数字相同 , 则发 光二极管 L E D2亮。按键 1 用于调节时间的 ~ 9

基于FPGA的门禁系统设计

摘要门禁系统是集计算机技术、电子技术、数字密码技术为一体的机电一体化高科技产品,具有安全性高,使用方便等优点。

本论文从门禁系统系统整体功能,硬件电路设计、软件设计等方面阐述密码门禁系统设计过程。

密码门禁系统系统包括电子锁,电子钥匙,用户卡及用户卡生成器四部分。

电子锁里保存着当前开门密码,以及用户第一次使用用户卡时的用户卡号和加密位。

用户凭用户卡在门上随时更改开门密码,更新或配制钥匙里的开门密码。

本系统考虑到门禁系统成本及体积因素,在设计门禁系统部分时,以FPGA 为核心;由多个数码管,按键和发光二极管组成外围电路。

本文采用VHDL语言使用自顶而下的方法对系统进行了描述。

采用FPGA开发设计,所有算法完全由硬件电路来实现,使得系统的工作可靠性大为提高,同时由于FPGA 具有在系统可编程功能,当设计需要更改对,只需更改FPGA中的控制和接口电路,利用EDA工具将更新后的设计下载到FPGA中即可,无需更改外部电路的设计,大大提高了设计的效率。

因此,采用FPGA开发的数字系统,不仅具有很高的工作可靠性,其升级与改进也极其方便。

关键词:门禁系统FPGA VHDLAbstractThe technology of access control system combines computer, electronics and digital coding technology together, and seems to be a high-tech electromechanical integration product, can be used safely and easily. This paper discussed the whole system architecture of the access control system; hardware design and software design were presented separately.The whole password access control system consists of four parts: electronic lock, electronic key, user card and user card generator. The electronic lock is used to preserve the current unlock password, the user card numbers and encrypted spaces. Users can use the card to unlock the lock, update or preparation the unlock password at any time.The cost and size are put most emphasis in the design of access control system. Design based on FPGA is presented. The system then is designed and verified through some external circuit components, such as keyboard and LEDs.The paper is described with VHDL using the top-down approach.FPGA-based development and design which is achieved all entirely by the hardware circuit algorithm,makes the system work much more reliability,as well as because FPGA in the system can be made available for the in-system programmable function,when the design needs to be changed,the control and the interface circuit can be restructured in the FPGA conveniently,using EDA tools,to download the updated design to the FPGA without changing the external circuit design.So the efficiency of the design Can be proved.Thus,the digital system implemented by FPGA is of high reliability,and the upgrade and improvement is extremely convenient.Key words:access control system FPGA VHDLII目录摘要 (I)Abstract (II)目录 ..................................................................................................................... I II 绪论 .. (1)1 门禁系统的分类及特点 (2)1.1门禁系统的分类及特点 (2)1.1.1 按进出识别方式分类 (2)1.1.2 按设计原理分类 (3)1.1.3 按与微机通汛方式分类 (3)2 开发工具简介 (4)2.1M AX+PLUSⅡ开发系统的特点 (4)2.2FPGA简介 (5)2.21 FPGA基本工作原理 (5)2.22 FPGA的基本特点 (5)2.23 FPGA设计流程 (5)2.3芯片选择 (6)3 门禁系统总体方案 (7)3.1系统概述 (7)4 门禁系统实现 (9)4.1门禁系统输入电路的设计 (9)4.1.1 矩阵式键盘的工作原理 (9)4.1.2 门禁系统输入电路各主要功能模块的设计 (11)4.2门禁系统控制电路的设计 (15)4.2.1 数字按键输入的响应控制 (15)4.2.2 功能按键输入的响应控制 (15)4.3门禁系统显示电路的设计 (16)III4.4门禁系统的整体组装设计 (17)5 主要VHDL源程序 (18)5.1键盘输入去抖电路的VHDL源程序 (18)5.2键盘输入去抖电路的仿真 (20)5.3门禁系统输入电路的VHDL源程序 (20)5.4门禁系统输入电路的仿真 (24)5.5门禁系统控制电路的VHDL源程序 (25)5.6门禁系统控制电路的仿真 (28)结论 (29)致谢 (30)参考文献 (31)IV绪论据有关资料介绍,电子锁门禁系统的研究从上世纪30年代就开始了,在某些特殊场所早就有所应用。

一种基于改进型数字相敏整流电路的磁通门传感器设计

一种基于改进型数字相敏整流电路的磁通门传感器设计ZHANG Yunshan;CUI Gongjun【摘要】在全面分析了数字电路磁通门特点的基础上,构建得到一种经过改进的数字相敏整流电路.之后采用此数字相敏整流电路设计出一款具有高分辨精度的数字磁通门传感器.经测试发现磁通门的输出测量范围是:X轴等于162800 nT,Y轴等于162900 nT,Z轴等于162700 nT,磁通门输出值和测量磁场之间具有线性关系.利用数字万用表测试激励信号的电流,采用示波器测试了激励信号频率与磁通门传感器的反馈电阻电压,测试发现磁通门分辨力小于2 nT.【期刊名称】《工业仪表与自动化装置》【年(卷),期】2019(000)001【总页数】5页(P55-58,22)【关键词】数字磁通门传感器;相敏整流;异或运算;分辨力【作者】ZHANG Yunshan;CUI Gongjun【作者单位】;【正文语种】中文【中图分类】TP212.130 引言磁通门传感器是利用磁饱和效应制作的一种改进型变压器器件。

当铁芯磁导率随激励磁场强度而变时,感应电动势中就会出现随被测磁场强度而变化的偶次谐波信号。

相比于其他类型的磁场测量器件,磁通门传感器在灵敏度、线性度、性价比和稳定性等方面均有无可比拟的优势[1-2]。

常用磁通门传感器按输出信号可以分为电流型式、时间差和电压型式,与之对应的常用磁通门处理电路也分为电流型磁通门应用电路、时间差型磁通门应用电路和电压型磁通门应用电路。

时间差型磁通门传感器通过测量输出信号中所包含的正负脉冲的时间差完成对被测磁场的测量[3-5]。

但是想要获得较高的分辨力,需要准确地测量出脉冲的尖峰时刻,同时必须要降低激励频率。

通常时间差型磁通门传感器的分辨力能达到60 nT,但这还不能够称为高分辨力[6-8]。

该文综合数字电路磁通门和模拟电路磁通门的优缺点提出一种改进型的数字相敏整流电路。

基于该数字相敏整流电路设计一款高分辨力数字磁通门传感器,该系统既能改善温度特性,同时也可以节约数字接口,减少数字处理器的运算负担。

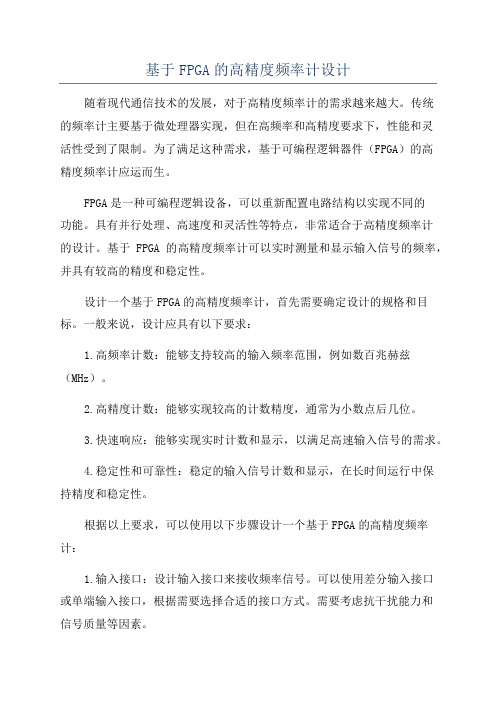

基于FPGA的高精度频率计设计

基于FPGA的高精度频率计设计随着现代通信技术的发展,对于高精度频率计的需求越来越大。

传统的频率计主要基于微处理器实现,但在高频率和高精度要求下,性能和灵活性受到了限制。

为了满足这种需求,基于可编程逻辑器件(FPGA)的高精度频率计应运而生。

FPGA是一种可编程逻辑设备,可以重新配置电路结构以实现不同的功能。

具有并行处理、高速度和灵活性等特点,非常适合于高精度频率计的设计。

基于FPGA的高精度频率计可以实时测量和显示输入信号的频率,并具有较高的精度和稳定性。

设计一个基于FPGA的高精度频率计,首先需要确定设计的规格和目标。

一般来说,设计应具有以下要求:1.高频率计数:能够支持较高的输入频率范围,例如数百兆赫兹(MHz)。

2.高精度计数:能够实现较高的计数精度,通常为小数点后几位。

3.快速响应:能够实现实时计数和显示,以满足高速输入信号的需求。

4.稳定性和可靠性:稳定的输入信号计数和显示,在长时间运行中保持精度和稳定性。

根据以上要求,可以使用以下步骤设计一个基于FPGA的高精度频率计:1.输入接口:设计输入接口来接收频率信号。

可以使用差分输入接口或单端输入接口,根据需要选择合适的接口方式。

需要考虑抗干扰能力和信号质量等因素。

2.时钟同步:使用FPGA内部或外部的时钟信号来同步输入信号。

通过与时钟信号同步,可以实现准确稳定的计数和显示。

3.计数逻辑:设计计数逻辑电路来对输入信号进行计数。

可以使用计数器模块实现计数功能。

FPGA内部计数器可以满足较低频率要求,但对于较高频率,可能需要使用外部计数器模块。

4.频率计算:根据计数结果和计数时间,计算输入信号的频率。

可以使用FPGA内部的时钟模块来计算时间间隔,然后使用计数结果和时间间隔来计算频率。

高精度频率计可以通过多次计数和平均来提高计算精度。

5.显示和输出:设计输出接口来显示和输出测量结果。

可以使用FPGA内部的显示模块来显示频率值,也可以通过外部接口输出频率值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 T 2L B DfV S 3 1( s ) 1 S

BI 4R F O A S ] T E C M( V s

图5 A DC 电 路

臣

E H

图 3 功率放大电路

2 2 滤波 放大 电路 . 由于磁通 门激励信号频率为 1. 2 Hz因此 为了提取感 5 6 5k , 应线 圈端 的二次谐 波 分量 , 采用 滤波 器设 计 软件 ft oui ie slt n lr o

23 转 换 电路 .

考虑到磁通门感应信号频率较 高 , 而且 F G P A输入输 出 口

充足 , 为了便于 电路驱 动 , 选取 1 并行输 出高精 度 A 2位 D芯片

A 92 D 24搭建 A D转换 电路 j 电路 图如图 5所示 , , 检测 信号频

励信号 。

4 实 验及 结 果 分 析

Ul

CL K

BI l Tl BI O Tl BI T9 BI c 8 I BI T7 BI T6 BI T5 BI T3 BI T2 Br 1 r OTR AD 2 4 9 2

DR VDD

A VDD AV S S Ⅵ NB Ⅵ NA CM L C AP T C PB A V REF S ENS E A VS S AVDD

图 4 带通 滤 波 电路

正弦波 幅度 的数字量信号 , 以驱动 I A转换 电路 。在实际应用 ) /

当 中经 过 对 比实 验 , 现 方 波 驱 动 效 果 最 佳 , 此 将 D S模 块 发 因 D 进 行 了相 关 简 化 , 接 采 用 系 统 时 钟 分 频 得 到 1.2 H 的 激 直 5 6 5k z

压信号 , 该直流信号与外界磁场 大小线性 对应 。由于图 1所示 电路 当中, 相敏检波 电路 中凋相 电路很难 保证进 入乘 法器 的 2 路信号严格 同相 , 中设计使用 F G 文 P A代替 图 1中虚线框 部分 ,

原理框 图如 图 2所示 , 用 A C将模拟信号转换为数字信号处 采 D 理 , 替了相敏检波 电路 等模拟 电路模 块 , 代 系统 的调试 更加 方

电路设计低功耗 、 型化 、 小 高集 成 的趋势 。而 现 场可 编程 门 阵 列 ( P A) F G 是一种采用 电子设 计 自动 化工 具 ( D 进 行编 程 、 E A) 仿真 、 测试 和校验 的可 编程数 字逻 辑器 件 , 其最 大 的优点 就在 于信号处理速度快 , 设计灵 活性 高 , 可以 自由地 定制各 种 电路 ,

ZUO a YANG a f i LI Te g f i Ch o, Xio—e , U n -e

( a h n ies yo c n e& T cn lg , u a 3 04, hn ) Hu zo gUnvri f i c t Se eh oo y W h n4 0 7 C ia

图1 所示 的磁通 门开环 系统 , 其工作原 理是 波形 产生 电路 产生激励信号 , 经过功 率放 大模块 , 动磁 通 门探 头 的激励 线 驱

2 硬 件 设 计

2 1 功 率 放大 电 路 .

要使 F G P A输 出的激励 的信号功率 足够 大 , 磁芯处 于周 使

收稿 日期 :0 0—0 2 21 3— 6

圈, 在感应线 圈端 产生 激励 信号 , 外界 磁场转 换成 二次谐 波 电

压信号 , 感应线 圈产生 的感应 电动势 中含 有激励信 号的偶次谐

波 分 量 , 过 选 频 放 大 将 其 中 的 二 次 谐 波 选 择 出来 作 为 磁 通 门 通

信号, 然后经相敏检波 以及积分 电路转化 为 比较平 整的直流 电

s oh d b i e i g T es se rs l t n i u 9 n n n a e t n i f m 3 0 0 n 5 9 0 n . p r n a e u t mo t e yf tr . h y tm e ou i p t 1 T a d l e rs c i s r l n o s O i o o 1 0 T t 1 0 T Ex e me tl s l o i r s

2 1 年 00

仪 表 技 术 与 传 感 器

I s u n T c n q e a d S n o n t me t r e h iu n e s r

2 0 01 No 9 .

第 9期

基 于 F GA 的 高 灵敏 度 数 字磁 通 门设计 P

左 超 , 晓非, 杨 刘腾 飞

Fn X・ m :( ) ( /2) () 1

1 .O n 0O k

式 中: 为输出波形频率 ; 为频率控制 字 ; 为 系统 时钟频 F F

率; Ⅳ为累加器 的位宽 。

波形一个周期 的数 据信 息存 于 R M 表 中, 中包 含不 同 O 表 相位 的幅值信息 , 查找表时即是把输 入的地址 相位 信息 映射 成

密数控直流 电流 源、 蔽箱 、 屏 高精 度磁 通 门传感 器 。精 密 电流

源配合一维 He h l l oz线 圈产 生 稳定 磁 场 , 场 范 围 0~2 G m t 磁 s ( 步进 2 T 、 0 2G ( 0n ) 0~ . s 步进 2n ) 屏蔽箱 中心磁 场低于环 T ;

期性过饱和状态 , 必须对激励信号进行 功率放大 。电路 图如

58

I tu n c n q e a n o nsr me tTe h i u nd Se s r所示 , 同时为 了最大程 度地 消除激 励信 号的 干扰 , 需要 采 用 电气隔离技术 , 一般在 U 0 12的正 向输入端设置 隔离变压器 。

407 ) 3 04 ( 中科 技 大 学 电 子 科 学 与 技 术 系 , 北 武 汉 华 湖

摘要 : 述 了一种基 于 F G 的新 型数 字磁 通 门驱动 电路 。 系统运 用数字信 号 处理 方法替 代 了传 统的方 波产生 、 描 PA 相 敏检波等模块 , 并且通过数字平滑 滤波方法进行 信号处理。 系统分辨 率高达 1n , 9 T 线性 区间为 1 0 300~1 0 n . 590 T 实验 结 果表 明该设计在减 少硬件 开销 的 同时显著提 高了 系统输 出的稳 定性和精度 。

.

换 为 B D码 , C 再对应为 L D数 码管 的位码 、 E 段码 , 驱动 L D数 E

码管输 出磁 场大小 。 D S 块通过频率控制字 x作 为相位累加器的增量 , D模 系统

时钟则对相位 累加器 , 实现查找地址 的循 环 , 相应 的 R M 查找 O 表循环输 出周期性波形 , 通过式 ( ) 1 计算输 出频率 。

图 6 基 于 F GA 的 控 制 采 集 单 元 结 构 框 图 P

V1. 0 0设计 了一款 B tr ot 阶带通滤波 器 , 中心 频率 为 ut w r e h一 其 3 . 1k , 12 Hz带通宽 度为 4k z 品质 因素 Q值 为 8 2 电路图如 H , .,

图 4所 示 。

关 键 词 : 通 门 ;P A; D 相 敏 检 波 磁 F G A C;

中 图分 类 号 :P 1 T 22

文献标识码 : A

文 章 编 号 :02—14 (0 0 0 0 5 0 10 8 1 2 1 )9— 07— 3

De i n o ih e stvt g t lFl x a e Ba e n FPG A sg fH g S n iiiy Diia u g t s d o

感应信号 中的偶次谐波 与外磁 场大小线 性对应 , 因此可 以通过

特定 的检测 电路来 提取 二次谐 波从而测量外界被测磁场大小 。 文中设计 电路 以典 型的二次谐波法 为基础 , 传统 的二次谐

波法 原 理 图如 图 1 示 。 所

图 2 基 于 F GA 的 磁 通 门 驱 动 原理 框 图 P

便可控 。

避免系统受制 于专用 芯片 。文 中设计 采用 F G P A来实 现磁 通

门驱动电路的数字信 号处 理 , 在提 高系统 集成 度 的同 时, 过 通 引入信号处理算法 , 使系统测量精度得 到了很大的提高 。

1 系统 结 构 及 工 作 原 理

磁通 门传 感器 的基本原 理 是利 用磁 芯材料 的非线性 磁 化特性 , 通过交变 电流激发 围绕在 磁芯上 的激励线 圈产生交 变 激励信号 , 从而使磁 芯 的磁 导率 发生 周期性 饱 和与非 饱 和 , 使 得围绕在磁 芯 上 的感 应 线 圈能 感应 出外界 被 测磁 场 的大 小 。

Ab t a t T i p p rd s rb d a d gtlf x ae d i e cr u tb s d o P sr c : hs a e e ci e ii u g t r i i a e n F GA. gt in lp o e sn to s u e o a l v c Dii s a rc s i g meh d wa s d t l a g

0 引 言

传统磁通 门传感 器驱 动 电路主 要采用 模拟 电路 进行 信 号

激励 与感 应 , 统设计 一 般采 用多 个小 规模 集 成 电路元 件 实 系 现, 在开发过程 中需要 进行 复杂 的布 线 , 电磁兼 容设 计复 杂 度 高, 调试工作量 大 , 在测量外部磁 场时受 温度 影 响较大 , 而且 针 对不 同探头 , 电路 模块 设计 方法 没有标 准 规范 , 因此 针对 不 同

薹 卜

r … 三 匝匦

H三亟 竺I 至

… … I… … … ~ r i… … . . … … … 一 一一… … … . . … .

L—— 相敏检波 卜一 平滑滤波 卜 直流输出 _

图 1 二 次 谐 波 法 原 理 框 图