PoP封装芯片的返修

堆叠封装(PoP)结构中芯片热翘曲变形的研究

堆叠封装(PoP)结构中芯片热翘曲变形的研究伴随着智能手机等高集成度电子产品的普及,PoP封装结构已经成为了业界主流的逻辑器件与存储器件的组合方式,在不断改进PoP生产工艺的过程中,人们逐渐认识到影响封装结构成品率及产品可靠性的最重要因素就是芯片在回流

焊过程中热失配所导致的翘曲变形。

本文针对这一问题,运用弹性力学薄板理论,对典型芯片结构进行简化,建立了芯片热翘曲变形的弹性曲面微分方程,最终得出了满足边界条件的解析解。

然后,运用有限元分析软件ANSYS对典型芯片结构的受热变形进行仿真分析,并将分析结果与芯片热变形翘曲理论计算所得数据及实测结果进行对比,验证了芯片热变形翘曲解析解的正确性。

集成电路封装与测试复习题(含答案)

集成电路封装与测试复习题(含答案)第1章集成电路封装概论2学时第2章芯片互联技术3学时第3章插装元器件的封装技术1学时第4章表面组装元器件的封装技术2学时第5章BGA和CSP的封装技术4学时第6章POP堆叠组装技术2学时第7章集成电路封装中的材料4学时第8章测试概况及课设简介2学时一、芯片互联技术1、引线键合技术的分类及结构特点?答:1、热压焊:热压焊是利用加热和加压力,使焊区金属发生塑性形变,同时破坏压焊界面上的氧化层,使压焊的金属丝与焊区金属接触面的原子间达到原子的引力范围,从而使原子间产生吸引力,达到“键合”的目的。

2、超声焊:超声焊又称超声键合,它是利用超声波(60-120kHz)发生器产生的能量,通过磁致伸缩换能器,在超高频磁场感应下,迅速伸缩而产生弹性振动经变幅杆传给劈刀,使劈刀相应振动;同时,在劈刀上施加一定的压力。

于是,劈刀就在这两种力的共同作用下,带动Al丝在被焊区的金属化层(如Al膜)表面迅速摩擦,使Al丝和Al膜表面产生塑性形变。

这种形变也破坏了Al层界面的氧化层,使两个纯净的金属面紧密接触,达到原子间的“键合”,从而形成牢固的焊接。

3、金丝球焊:球焊在引线键合中是最具有代表性的焊接技术。

这是由于它操作方便、灵活,而且焊点牢固,压点面积大,又无方向性。

现代的金丝球焊机往往还带有超声功能,从而又具有超声焊的优点,有的也叫做热(压)(超)声焊。

可实现微机控制下的高速自动化焊接。

因此,这种球焊广泛地运用于各类IC和中、小功率晶体管的焊接。

2、载带自动焊的分类及结构特点?答:TAB按其结构和形状可分为Cu箔单层带:Cu的厚度为35-70um,Cu-PI双层带Cu-粘接剂-PI三层带Cu-PI-Cu双金属3、载带自动焊的关键技术有哪些?答:TAB的关键技术主要包括三个部分:一是芯片凸点的制作技术;二是TAB载带的制作技术;三是载带引线与芯片凸点的内引线焊接和载带外引线的焊接术。

制作芯片凸点除作为TAB内引线焊接外,还可以单独进行倒装焊(FCB)4.倒装焊芯片凸点的分类、结构特点及制作方法?答:蒸镀焊料凸点:蒸镀焊料凸点有两种方法,一种是C4 技术,整体形成焊料凸点;电镀焊料凸点:电镀焊料是一个成熟的工艺。

POP制程说明及管控因应

融化的錫膏浸潤 性更好,彌補了 上述形成的Crack 不良。

POP制程说明及管控因应

POP贴装工艺参数

1.使用POP锡膏时蘸取高度的设定: (POP TOP元件锡球高度-复合型模块高度)*(50%至70%) 2.使用POP组焊剂时蘸取高度的设定: (POP TOP元件锡球高度-复合型模块高度)*(90%至100%)

在受熱的時候flux會爬向上層 物料的錫球。

裂縫變小了, 但是裂縫很難 被flux充滿,因 此裂縫很容易 出現。

POP焊接辅料

Flux VS 锡膏 锡膏焊接原理圖解

POP制程说明及管控因应

錫球表面

錫膏 裂縫

底部BGA受熱后變 形,所以在上下兩 層之間會有裂縫出 現

但是在受熱的過程中,錫膏中 的金屬物質會先融化,融化的 錫膏會把上層變形的物料拖拉 過來

POP制程说明及管控因应

POP制程不良分析(虚焊)

3.虚焊不良原因分析

POP制程说明及管控因应

POP制程不良分析(虚焊)

4.POP 虚焊不良的解决对策

対策 A

在焊球沾锡时增加沾锡的焊锡量

问题点

接合焊接不良

.对POP接合一般来说是有效的。由于熔融的焊锡表面张力会抑制变形

・对间隙大的地方特别有效

対策 B

POP Feeder中添加錫膏。

膜厚測厚器

1.管裝內錫膏開封有效期:48H,轉印台錫膏有效期12H. 2.POP FEEDER每班進行清洗一次,工作台殘留錫膏必須報廢處理. 3.膜厚由ME進行測試并記錄.測試頻率:1H/次.如測量值偏下限及時加錫處理. 4.加錫頻率:2H/次,添加錫膏后必須測量錫膏厚度.

POP制程不良分析(少锡,短路)

改善對策: 在實際量測過程中,錫槽錫膏厚度不穩定,最厚可達250mm,已經超過 了錫球的高度,並且有時會出現刮槽局部無錫的現象,針對以上倆种問 題在多方面分析研究通過實踐驗證總結出以下有效改善措施: 1 POP Feeder錫槽錫量管控在175-185um 2 POP沾錫量測頻率每2h/次量測改為1h/次量測. 3 POP錫槽如有加錫/修改POP設定參數/更換物料都應將前后各 2panel進行X-ray全檢OK后才能進行生產. 4 50Panel生技人員手動檢查一次POP實物沾錫狀況,保證POP錫 球沾錫深度在1/2~2/3個錫球之間. 5 制程抽照X-ray由原來的1H/panel改為5panel/H

PoP封装介绍

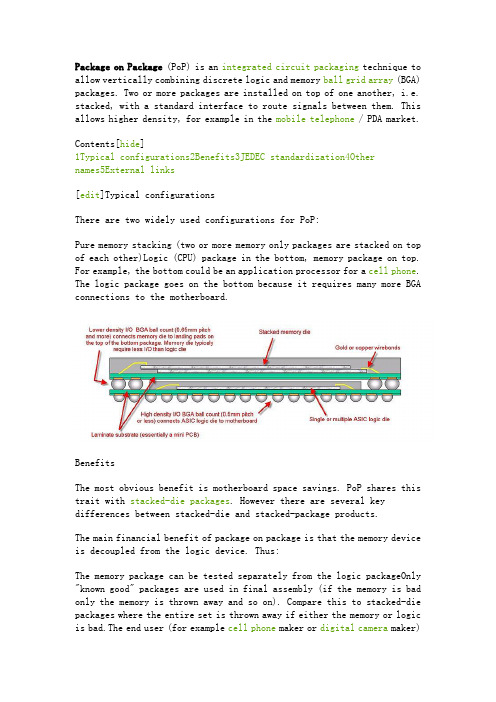

Package on Package(PoP) is an integrated circuit packaging technique to allow vertically combining discrete logic and memory ball grid array(BGA) packages. Two or more packages are installed on top of one another, i.e. stacked, with a standard interface to route signals between them. This allows higher density, for example in the mobile telephone/ PDA market.Contents[hide]1Typical configurations2Benefits3JEDEC standardization4Othernames5External links[edit]Typical configurationsThere are two widely used configurations for PoP:Pure memory stacking (two or more memory only packages are stacked on top of each other)Logic (CPU) package in the bottom, memory package on top. For example, the bottom could be an application processor for a cell phone. The logic package goes on the bottom because it requires many more BGA connections to the motherboard.BenefitsThe most obvious benefit is motherboard space savings. PoP shares this trait with stacked-die packages. However there are several key differences between stacked-die and stacked-package products.The main financial benefit of package on package is that the memory device is decoupled from the logic device. Thus:The memory package can be tested separately from the logic packageOnly "known good" packages are used in final assembly (if the memory is bad only the memory is thrown away and so on). Compare this to stacked-die packages where the entire set is thrown away if either the memory or logic is bad.The end user (for example cell phone maker or digital camera maker)controls the logistics. This means memory from different suppliers can be used at different times without changing the logic. The memory becomes a commodity to be sourced from the lowest priced supplier. This particular point is also a benefit compared to PiP (package in package) which requires a specific memory device to be designed in and sourced upstream of the end user.Because the construction is like Lego, any mechanically mating top package can be used. For a low-end phone, a smaller memory configuration may be used on the top package. For a high-end phone, more memory could be used with the same bottom package. This simplifies inventory control by the OEM. For a stacked-die package or even PiP (package in package), the exact memory configuration needs to be known weeks (or months) in advance.Because the memory only comes into the mix at final assembly, there is no reason for logic suppliers to source any memory. With a stacked-die device, the logic provider would need to buy wafers of memory from a memory supplier.Electrically, PoP offers benefits by minimizing track length between, for example, a controller and a memory. This results in better electrical performance of the devices, since the shorter routing of interconnections between circuits results in faster signal propagation and reduction in noise and cross-talk.公司要做Omap4的第三方软件合作商,看了下pandaboard的结构与布局,发现这个POP memory 与CPU 堆叠在一起。

PoP叠层封装的组装工艺(上篇)

数码相机和个 人多媒体播放器等产 品 现代智能手机 、数码相机和个人 的有效解决方案 。 多媒体播放器等 电子产品的发展要求 2 0 0 3 年前元件堆叠技术 大部分还

板 电脑将大量采用此技术。

基于手持式 电子设备功能集成 的 需 要 ,体积 更 小 ,更 薄和 高 密度 的

具有高性能处理器及 高密度大容量存 只是 应用 在 闪存 及 一 些移 动 记忆 卡 储器的支持,该类产品的关键是要解 中,2 0 0 4 年开始 出现 了移动 电话 的逻

更高的数据传输速率 、更 宽总线和更

大存储容量 的要求 ,要求叠层封装能

2

熙蒸 3 2 0 1 3 年 2 月 第1 期

国 家 全 自动水基超声 波钢网清 洗机 全 能 系 列 水 基 清 洗 剂

够有 更 细 的 引脚 间距 ,高密 度 的接 度 的 互连 。

制。

口。理想的下一代底部封装要求存储 器接 口在尺 寸上 匹配 B G A 封装 间距 , 器件的发展趋势导致 了运行在更 高时

● 超过I G H z 的高速处 理器 ,该

● 在 不需要开发 新 的工具 或工 序 的情 况下 ,P o P 底 部封装可 以支 持 器件集成的要求 。

处理器有更复杂的 内存管理和控 制、

(t i g h t e r s i g n a l i n t e g r i t y a n d

● 具有 在低能耗 下更 高的C M O S

决 ”带宽 ”的 问题 ,通俗 的讲就是高 辑运算单元和存储单元之 间的堆叠装 P o P 封 装设计 超越 了 目前底 部封装 的 速处理信号的能力。这就 需要新 型的 配 。在2 0 0 4 年度 内整个堆叠技术市场 叠层 技 术 要求 ,下一 代 的底 部封 装 数字信号处理器和存储器件 ,以实现 的平均 增长 率达6 0 % 。其 中移动 电话 P o P 要求能够 兼容 高密度 ,低 能耗 的 了小型化 ,同时功能也得 到强化 ,解 对 于堆 叠装配技术 的应用将 占整个技

POP 制程管控作业指导书

POP 制程管控作业指导书1目的:通过对POP制程各环节的操作手法以及各制程参数进行定义与量化,规范作业流程,提升POP制程的稳定性与可靠性,减少不良品的产出。

2适用范围:适用于POP制作的作业。

3参考文件:无4定义:POP:元件堆叠技术(PoP, Package on Pa ckage) 为提高逻辑运算功能及存储空间而产生的一种元器件小型化高密度的芯片封装方式。

5 内容:5.1POP的SMT工艺流程:PCB表面锡浆印刷→底部及其它零件贴装→顶部零件浸渍助焊剂或锡浆顶部零件贴装→回流焊接→检测。

5.1.1 POP 锡浆:POP制程中的一种焊接辅料,与现有的模板印刷工艺中使用的锡膏有很大区别。

5.1.2 POP flux:POP制程中的一种焊接辅料,作用等同于维修所用的助焊剂。

(目前导入的POP flux 型号为乐泰 EU2454)。

5.1.3 POP Feeder:目前我们使用的POP feeder有FUJI桥式浸漬助焊剂器件与siemens旋转式浸漬助焊剂器件。

FUJI桥式浸漬助焊剂器件Siemens旋转式浸漬助焊剂器件5.1.4涂覆厚度量测规:用于POP元件焊料涂覆厚度量测的一种治具。

5.2POP制程工艺参数:5.2.1焊接辅料的选择:5.2.1.1POP锡膏:一般来POP 制程工艺中选用锡膏时必须满足以下三个前提条件: 5.2.1.1.1POP锡膏中的合金成分需与实装板中所采用的印刷锡膏成分一致或尽量接近,以保证两种锡膏的制程水平的差异不会太大。

由于POP锡膏一般都采用Type 5锡球,锡球的暴露面积加大,有加剧氧化作用,不利于制程环节的管控;有一定的制程局限性,不适用于细小间距制程。

5.2.1.1.2使用POP锡膏时蘸取元件的锡球间距(Pitch)应≧0.5mm。

5.2.1.1.3复合型模块的安全间隙应≧0.15mm。

5.2.2蘸取高度参数的设定:5.2.2.1使用POP锡膏时蘸取高度的设定:(POP TOP元件锡球高度-复合型模块高度)*(70%至80%)5.2.2.2使用POP组焊剂时蘸取高度的设定:(POP TOP元件锡球高度-复合型模块高度)*(90%至100%)5.3POP硬件设备的安装与调试5.3.1FUJI桥式浸漬助焊剂器件安装:5.3.2打开模组正前方供料平台下方的盖子拆除红色区域的罩板。

POP工艺(中文) XXXX0531

①可以一定程度地补偿元件及基板 的翘曲变形;②无须额外工艺,可以与现

有工艺很好兼容;③焊接后器件离板高度稍高,有利于可靠性。但 也有其缺

点:①会放大焊球本来存在的大小的差异;②可供选择的这类锡膏有限,价 格也贵。

•

浸蘸用的锡膏不同于普通印刷锡膏,其黏度为⒛Pa·s左右,比普通的锡膏

低,金属颗粒直径在5~25 gm 左右,比普通锡膏金属颗粒细,助焊剂百分含

• 底层元件以整板基准点来矫正没有问题,上层元件是以整板基 准点还是以其底层元件背面上的局部基准点 来矫正就需要斟酌

了。如果同样选择整板基准点,会很方便,不需要任何变更, 产出率也会高,但贴装精度 成了争论的焦点。事实上,贴装的 精度会受到影响。而选择其底层元件背面上的局部基准点,贴 片周期会长 产出率受到影响,对处理基准点的相机提出了挑战 (焦距的问题)。但是贴片的精度会得以保证。这时贴装 压力

5 回流焊接工艺的控制

• 由于无铅焊接的温度较高,较薄的元件和基板(厚度可达0.3 mm)在回流焊接过程中很容易热变形,需要 细致的优化回流 焊接温度曲线。同时,监控顶层元件表面与底层元件内部温度 非常重要,既要考虑顶层元件 表面温度不要过高,又要保证底

层元件焊球和锡膏充分熔化形成良好的焊点(有时底层元件焊 球可能是高铅 材料,此时焊球可能不熔或部分熔融,锡膏则熔 化冷却形成焊点)。对于多层堆叠装配,升温速度建议控制 在 1,5OC/s以内,防止热冲击及炉内移位或其他焊接缺陷。在保 证焊接品质的前提下,让回流温度尽量的低 ,最大程度的降低 热变形的可能。

•

·脱模的速度极为关键,一般来说需要较低的脱模速度,如0.25~0.5 mm/s,

但也有些锡膏要求快速脱模 ,需要仔细阅读技术说明:

SMT-POP技术介绍

5、治具介绍

吸嘴、助焊剂、锡膏刮刀准备

松下 Nozzle型号: 1003、1004

刮刀規格: 30#,40#,50#

钢板准备

0.162mm 0.238mm

钢板厚度:0.08~0.1mm 开口:激光电拋光倒圆角 孔璧精度: 2 μm

6、验证方法

U5 Group 1

U6

U3

U4

Group 4

Group 2

沾取Flux 转印Flux保持平面度

2

1

1、贴装下层 2、贴装上层

完成贴片

1. 上層

2、物料介绍

2. 下層

上层BGA:Pad直径:0.30mm Pad间距:0.50mm

下层BGA:Pad直径:0.25mm Pad间距:0.4mm

3、生产流程

印刷机

高速机

AOI

松下COM602/NPM 下层沾Flux

允许偏差

Sigma

印刷机

+/-0.225mm

0.0048

多功能机

+/-0.05mm

0.0170

回流炉

+/-5℃

0.7

ERSA—W3-20

CPK 1.70 1.82 1.82

8、炉温设定

回流焊接参数设定及测温板制作

预热升温要求 <165°C

165°C~217°C

≤2°C/s 70~90s

>217 °C時間

POP封装技术介绍

1、组装介绍 2、物料介绍 3、生产流程 4、辅料介绍 5、治具介绍 6、验证方法 7、设备能力

目录

8、炉温设定 9、测试介绍 10、维修介绍 11、实验验证 12、结果分析 13、实验结论

1、组装介绍

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights resena Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.