数字电子技术第7章

阎石《数字电子技术基础》(第5版)笔记和课后习题(含考研真题)详解(7-11章)【圣才出品】

圣才电子书 十万种考研考证电子书、题库视频学习平台

存储矩阵中选出指定单元,并把其中数据送到输出缓冲器。 (3)输出缓冲器的作用是提高存储器带负载能力,实现对输出状态的三态控制,便与 系统的总线连接。

图 7-1 ROM 的电路结构框图

2.可编程只读存储器(PROM) PROM 初始时所有存储单元中都存入了 1,可通过将所需内容自行写入 PROM 而得到 要求的 ROM。PROM 的总体结构与掩模 ROM 一样,同样由存储矩阵、地址译码器和输出 电路组成。 PROM 的内容一经写入以后,就不可能修改了,所以它只能写入一次。因此,PROM 仍不能满足研制过程中经常修改存储内容的需要。

3 / 127

圣才电子书 十万种考研考证电子书、题库视频学习平台

分组成,如图 7-4 所示。 ①存储矩阵由许多存储单元排列而成,每个存储单元能存储 1 位二值数(1 或 0),既 可以写入 1 或 0,又可以将存储的数据读出; ②地址译码器一般都分成行地址译码器和列地址译码器。行地址译码器将输入地址代码 的若干位译成某一条字线的输出高、低电平信号,从存储矩阵中选中一行存储单元;列地址 译码器将输入地址代码的其余几位译成某一根输出线上的高、低电平信号,从字线选中的一 行存储单元中再选 1 位(或几位),使这些被选中的单元经读/写控制电路与输入/输出端接 通,以便对这些单元进行读、写操作;

圣才电子书 十万种考研考证电子书、题库视频学习平台

第 7 章 半导体存储器

7.1 复习笔记

一、概述 半导体存储器是一种能存储大量二值信息(或称为二值数据)的半导体器件。半导体存 储器的种类很多,从存、取功能上可以分为只读存储器(ROM)和随机存储器(RAM)。 只读存储器在正常工作状态下只能从中读取数据,不能快速地随时修改或重新写入数 据。ROM 的优点是电路结构简单,而且在断电以后数据不会丢失。它的缺点是只适用于存 储那些固定数据的场合。只读存储器中又有掩模 ROM、可编程 ROM(PROM)和可擦除 的可编程 ROM(EPROM)几种不同类型。 随机存储器与只读存储器的根本区别在于,正常工作状态下就可以随时快速地向存储器 里写入数据或从中读出数据。根据所采用的存储单元工作原理的不同,又将随机存储器分为 静态存储器(SRAM)和动态存储器(DRAM)。

(数字电子技术)第7章数模与模数转换

第7章 数/模与模/数转换

7.1 概述 7.2 数/模转换 7.3 模/数转换 7.4 本章小结 7.5 例题精选 7.6 自我检测题

第7章 数/模与模/数转换

7.1 概 述

随着以数字计算机为代表的各种数字系统的广泛普及和 应用,模拟信号和数字信号的转换已成为电子技术中不可或 缺的重要组成部分。数/模转换指的是把数字信号转换成相 应的模拟信号,简称D/A转换,同时将实现该转换的电路称 为D/A转换器,简称DAC;模/数转换指的是把模拟信号转 换为数字信号,简称A/D转换,并将实现该转换的电路称为 A/D转换器,简称ADC。

当Rf=R时

uo=

uR 2n

n-1

di zi

i= 0

由上式可以看出,此电路完成了从数字量到模拟量的转 换,并且输出模拟电压正比于数字量的输入。

第7章 数/模与模/数转换

2. 集成DAC电路AD7524 AD7524(CB7520)是采用倒T型电阻网络的8位并行D/A 转换器,功耗为20 mW,供电电压UDD为5~15 V。 AD7524典型实用电路如图7.2.5所示。

第7章 数/模与模/数转换

7.3.4 常见的ADC电路

1. 逐次逼近型ADC 逐次逼近型ADC是按串行方式工作的,即转换器输出 的各位数码是逐位形成的。图7.3.6为原理框图,该电路由电 压比较器、逻辑控制器、D/A转换器、逐次逼近寄存器等组 成。

第7章 数/模与模/数转换

图 7.3.6 பைடு நூலகம்次逼近型ADC原理图

第7章 数/模与模/数转换

(2) 四舍五入法:取最小量化单位Δ=2Um/(2n-1-1), 量化时将0~Δ/2之间的模拟电压归并到0·Δ,把Δ/2~3·Δ/2之 间的模拟电压归并到1·Δ,依此类推,最大量化误差为Δ/2。 例如,需要把0~+1 V之间的模拟电压信号转换为3位二进制 代码,这时可取Δ=(2/15)V,那么0~(1/15)V之间的电压就 归并到0·Δ,用二进制数000表示;数值在(1/15)~(3/15)V之 间的电压归并到1·Δ,用二进制数001表示,并依此类推,如 图7.3.5(b)

数字电子技术 7-3多谐振荡器

uI1

显然: 任何≥3 奇 首尾接 可形成环

(uO)

(a)

tPd

数个反相器 在一起 形振荡器

振荡频率: f 1

O

uI2

tPd

t

2ntPd

---式中n为串联门的个数,n=3、5、7、…

uIO3 tPd

t

优点:电路简单

O

缺点:频率太高不可调不实用 tPd只有几十纳秒到一二百纳秒

t (b)

工作波形图

R

R1 Rs

R1 R

UOL1

R u13

UOH2

RS

C

uI3

可求得电容C充电时间T1

T1

RECln

UE

UTH UOH UE UTH

U OL

RECln

2UOH UTH UOH UTH

O

VCC R1

G3

UE

RE

u13

C UOL

UTH+(UOH UOL)

UTH t

UTH (UOH UOL )

7.3.1

获得较大电

VDD

压放大倍数

uI1

uI2

uO2

使uO1↓到UOL ,而uO2↑至UOH,电路进入暂稳态

1/2VDD

直线uO1=uI1

O

P

G1静态

工作点

1/2VDD

uI

电压传输特性

7.3.1

用门电路构 成的振荡器

➢ 随着C放电uI1↓=UTH时: 另一正反馈过程发生

uI1

uI2

uO2

使uO1↓UOH,

品质因数高 选频特性好

由阻抗频率特性知:

当外加电压 信号的频率

等于

数字电子技术基础第四版课后答案

第七章半导体存储器[题7.1] 存储器和寄存器在电路结构和工作原理上有何不同?[解] 参见第7.1节。

[题7.2] 动态存储器和静态存储器在电路结构和读/写操作上有何不同?[解] 参见第7.3.1节和第7.3.2节。

[题7.3] 某台计算机的内存储器设置有32位的地址线,16位并行数据输入/输出端,试计算它的最大存储量是多少?[解] 最大存储量为232×16=210×210×210×26=1K×1K×1K×26=64G[题7.4] 试用4片2114(1024×4位的RAM)和3线-8线译码器74LS138(见图3.3.8)组成4096×4位的RAM。

[解] 见图A7.4。

[题7.5] 试用16片2114(1024×4位的RAM)和3线-8线译码器74LS138(见图3.3.8)接成一个8K×8位的RAM。

[解] 见图A7.5。

[题7.6] 已知ROM 的数据表如表P7.6所示,若将地址输入A 3A 2A 1A 0作为4个输入逻辑变量,将数据输出D 3D 2D 1D 0作为函数输出,试写出输出与输入间的逻辑函数式。

[解] D 3=0123012301230123A A A A A A A A A A A A A A A A +++D 2=01230123012301230123A A A A A A A A A A A A A A A A A A A A +++++0123A A A AD 1=0123012301230123A A A A A A A A A A A A A A A A +++D 0=01230123A A A A A A A A +[题7.7] 图P7.7是一个16×4位的ROM ,A 3、、A 2、A 1、A 0为地址输入,D 3、D 2、D 1、D 0是数据输出,若将D 3、D 2、D 1、D 0视为A 3、、A 2、A 1、A 0的逻辑函数,试写出D 3、D 2、D 1、D 0的逻辑函数式。

电子教案《数字电子技术(第5版_杨志忠)》教学资源第7章练习题参考答案

C1

已知 R3 = 3 、 kΩ R2 = 3 6 、 kΩ C1 = 0 1 μF, 将 这 些 参 数 代 入 上 式 进 行 计 算, 并 求 出

tw2 = 0 7R2 C = 0 7 × 24 × 103 × 0 1 × 10 - 6 s = 1 68 ms

所以

( ) f =

1 2 73 + 1 68

× 10 - 3 Hz≈226 75 Hz

(2) 画 uC 和 uO 的波形,见图[题 7 8]。

(3) RD端加停振信号。当在置 0 端RD加上低电平时,多谐振荡器被强迫停止振荡。

(2) 对应画出 uI、uC 和 uO 的电压波形。 [解] (1) 求输出电压 uO 的脉冲宽度 tw

tw = 1 1RC = 1 1 × 33 × 103 × 0 1 × 10 - 6 s = 3 63 ms

(2) 对应画出 uI、uC 和 uO 的电压波形,如图[题 7 7]所示。

波形。试求:

(1 (2

) )

计 画

算 出

输

uI

出脉 、ud

冲的 和u

宽O 的度波tw形。。

第 7 章 脉冲信号的产生与整形 145

图 P7 3

(3) 输入脉冲的下限幅度为多大? [解] (1) 求输出脉冲宽度 tw

tw = 1 1RC = 1 1 × 27 × 103 × 0 01 × 10 - 6 s≈297μs

R min

=

tw(min) = 0 7C 0

7

10 × 10 - 6 × 0 01 × 10

- 6 Ω≈1428

57Ω

(2) 求最大值电阻 Rmax

R max

=

tw(max) = 0 7C

数字电子技术基础 周良权 3版 第7章

第7章 数/模和模/数转换器7.1 二 模拟电压 7.2 R7.3 REF 1082VN -⨯7.4 c 7.5 a 7.6 b 7.7 × 7.8 √ 7.9 √7.10 A/D 转换器电子产品有电子秤、数字式电压表、数字式电子温度计、数字式血压计等;D/A 转换器电子产品有VCD 播放机、DVD 播放机、MP3音乐播放机、数字电视机等.7.11 单极性输出电压计算公式为式REF O 1010(7.2.8):2Vu N =-⋅,双极性输出电压为式()B O REF (7.2.10):1024N u V =⋅补.211027C(H)21671612(636)=⨯+⨯+=211006F(H)01661615(111)=⨯+⨯+= 21101BD(H)=116111613(445)⨯+⨯+=补码最高位为1,为负数;最高位为0为正数即为原码[]2181010(27C(H))07C(H)1(182)(1168162)(386)=-+=-=-⨯+⨯+=-补反()()21101006F(H)01661615(111)=⨯+⨯+=补 ()()2110101BD(H)=116111613(445)⨯+⨯+=补单极性输出电压:O 1027C(H):636 6.21V 1024u =-⨯=- O 1006F(H):111 1.084V 1024u =-⨯=-O 101BD(H):445 4.346V 1024u =-⨯=-双极性输出电压:O 386(27C(H)):10 3.77V 1024u -=⨯=-补()O 11106F(H):10 1.084V 1024u =⨯=补 ()O 4451BD(H):10 4.346V 1024u =⨯=补 7.12 (1)在2°R 支路上电流为1REF REF n 111222n n n V V I D R R ----==⋅ 依次可得各电阻支路上电流为2REF REF 221222n n n n V V I D R R ----==⋅3REF REF 3321222n n n n V V I D R R----==⋅⋅1REF 11122n V I D R -=⋅⋅0REF 00122n V I D R -=⋅⋅流向运算反相端的总电流为1REFN i B B 10,2n n i V I I N N R--====∑⋅2°11o 1122n n D D D --+++⋅ 故O N f u I R =-⋅(2)当REF f 110V,2V R R =+=,位数为n =8时,输入数码为D9(H ) 其10B 101316916(217)N =⨯+⨯=故O 1810V 110V 10V2172172178.47V 225622n u R R -=-=-⨯=-⨯=-⋅分辨率为:REF 81110V =0.039V =39mV 2562V =⨯绝对精度为:1110VLSB =0.0195V =19.5mV 22256±±=±±7.13 (1)设D 9~D 0的10位二进制数对应的十进制数值N B 则REFB O1B B 10B ,2V V I N I R R==⋅()REFB O O1B f B f 10B 2V V u I I R N R R R ⎛⎫=-+=-+ ⎪⎝⎭⋅⋅,而R B =10k Ω(2)当D 9~D 0为全1时,要求O 5V u =-则10REF B O 10B (21)105V 210V V u R ⎡⎤=--+⨯=-⎢⎥⨯⎣⎦ ①R 为AD7520内的等效电阻10k Ω当D 9~D 0为全0,要求O 5V u =+°则REF B O 100105V 10210VV u ⎛⎫=-⨯+=+ ⎪⨯⎝⎭⋅ ②由式②B 105V 10V-⨯=+,故B 5V V =-,代入①得()10REF 10521105V 10210V-⎡⎤--+=-⎢⎥⨯⎣⎦⋅⋅,解得REF 10V V ≈+因而()REF 9REF REF O B B 101012102V 102102V V V u N N ⎛⎫- ⎪=-+⨯=-- ⎪⨯ ⎪⎝⎭⋅输入数码与O u 极性及数位如下表所示B 补补210作为单极性输出电路的输入代码,代入式(7.2.8)REF O110(380)380 3.711V 10241024V u =-=-⨯=-⋅再按照电路图7.2.5可计算出双极性输出电压o1REF O f 11 3.7111010 1.289V 210210u V u R R R ⎛⎫-⎛⎫=-+=-+⨯=- ⎪ ⎪⨯⎝⎭⎝⎭⋅(2)当(N B )补为17C(H)=(010*******)补,最高位取反后,为210(1101111100)(892)=作为单极性输出电路的输入代码,代入式(7.2.8)REF O1B 108928.711V 10241024V u N =-=-⨯=-再按电路图7.2.5可计算出双极性输出电压为o1REF O f 118.7111010 3.711V 210210u V u R R R ⎛⎫-⎛⎫=-+=-+⨯= ⎪ ⎪⨯⎝⎭⎝⎭⋅上述结果与[例2.2.2]计算结果相同. 7.15 根据图题7.15电路可知REF O B B B 1010101010222V u N N N -=-=-=⋅ 而54LS192为可逆十进制计数器,即当Q 3Q 2Q 1Q 0为全0时,或非门出1,使D 触发器Q 翻转一次,若Q 为1,则CP U 有时钟脉冲信号,而CP D =1,LS192进行加法计数,而AD7520的D 3D 2D 1D 0由0000~1001逐步递增变化,当由1001变为0000时,D 触发器又翻转一次使Q =0,使可逆计数器CP U =1,而CP D 有时钟脉冲信号,执行减法计数,由1001~0000逐步递减变化计数. 而O u 值根据D 3~D 0的数码每变化递增或递减一位,输出O u 变化值为REF 101019.765mVV ⨯==的级差.其u O 输出模拟电压与数码关系如下表所示 其输出u O 的波形如图题解7.15所示.图题解7.157.16 (1)()O(max)102120000.005n u δ-≥==,故n =11位. (21)n -为n 位全1,即输出满刻度值的输入数码.(2)85V 5V0.0196V =19.6mV 256121==--为分辨率因()8REF 8215V 2V -=,故REF 5V V =. (3)即分辨率121n -≤0.2%故()1215000.002n -≥=. 应取n =9位 7.17 (1)根据图示电路,当被转换的输入模拟电压I u 大于某一个比较器反相输入端的基准电压i u -,则在此比较器的输出oi u 以下均为1,再通过编码器输出,其相应数码为D 2~D 0. 根据电路可列出下式关系:D 2=Q 4、1642642D Q Q Q Q Q Q ==+⋅⋅,07654321D Q Q Q Q Q Q Q =⋅⋅⋅⋅⋅⋅ =7654321Q Q Q Q Q Q Q +++⋅⋅⋅(2)按表题解7.17列出输入电压I u 与寄存器状态和输出数字关系:出电压O 0u >的情况,这时在O 0u >时刻,输出数字量为全0并产生溢出,而比较器输出O 0u =(若比较器用双电源会使O 0u <),则门控G 与非门被封,计数器不再计数. 计数器输出全0. 7.19 (1)当双积分A/D 转换器,计数器为n =10,在n 位计数器Q n =1,其所需时间为cp cp122n n T t f ==⋅,则转换一次最长时间为222n T ⨯=. 当cp 频率cp 120kHz f =,故最长时间为10cp 331204822220.017517ms 1201012010n t ⨯=⨯⨯===⨯⨯⋅ (2)当运放的最大输出电压为om 10V U =±,在最大输入模拟电压I 10V U =+时,运放积分器在第一次积分最大值也为10V -. 因此:()O 1I cp 1210V n u t u t RC=-=-⋅⋅⋅故10I cp 631111*********0.11012010n R u t C -=⨯=⨯⨯⨯⨯⨯⨯⋅⋅85.3k =Ω (3)由式(7.3.3)可知I REF2nN u V =⋅ 当I 4V u =时,1010224(409.6)(110011001)10N =⨯== 当I 1.5V u =时,101022 1.5(153.6)(10011001)10N =⨯== 7.20 (1)偏移电压REF 44118110.25V 22222V s =⨯=⨯=(2)因量化单480.5V 2s ==则(0.50.25)V 5.9V N ⨯-≤故1025.90.25(12.3)(1100)0.5N +≤==(3)电子输出数字量为4位数,需时钟脉冲周期数2426T n CP =+=+=,而脉冲周期cp 120s20s 6t μ==μ故时钟频率:cp 6cp110.05MHz =50kHz 2010f t -===⨯。

数字电子技术及应用教程第7章 数模与模数转换电路

内容提要:

本章系统地讲述了数字量转换模拟量和模拟量 转换数字量的基本原理以及几种常用典型电路。在 数字模拟转换器中,主要讲解权电阻网络数模转换 与倒 T 形数模转换电路。在模数转换器中,对模数 转换的步骤、取样定理进行详细的说明,然后又介 绍了并行比较型、逐次渐近型和双积分型三种各具 特色的模数转换电路。

7.2.5 集成DAC及其应用举例

常 用 的 集 成 DAC 有 AD7520 、 DAC0832 、 DAC0808 、 DAC1230 、 MC1408 等 , 这 里 仅 对 AD公司生产的AD7520作简要介绍。 如图 7.2.7 所示的电路为 AD7520 组成的锯齿波 发生器,其原理为10位二进制加法计数器从全0加 到全 1 ,电路的模拟输出电压 uo 由 0V 逐渐增加到 最大值。如果计数脉冲不断,则可在电路的输出 端得到周期性的锯齿波。

图7.3.7 积分型ADC的电路原理图

2.工作原理

转换开始前,先将计数器清零,接通S2使电容 C完全放电。转换开始时,断开S2。整个转换过程 分为两个阶段进行。其工作波形如图7.3.8所示。

图7.3.8 双积分型A/D转换器各点工作波形

7.3.5 ADC的转换精度和转换速度 1.ADC的转换精度

如图7.3.5为3位并行比较型A/D转换原理电路, 它由电压比较器、寄存器和优先编码器三部分组成。

图7.3.5 3位并行比较型A/D转换原理电路

7.3.3 逐次渐近型ADC 逐次渐近型A/D转换器属于直接型A/D转换器, 它能把输入的模拟电压直接转换为输出的数字代码。 逐次渐近型A/D转换器框图如图7.3.5所示,它 由控制逻辑电路、寄存器、电压比较器及D/A转换 器组成。

图7.3.10 ADC0809引脚图

数字电子技术基础习题册答案

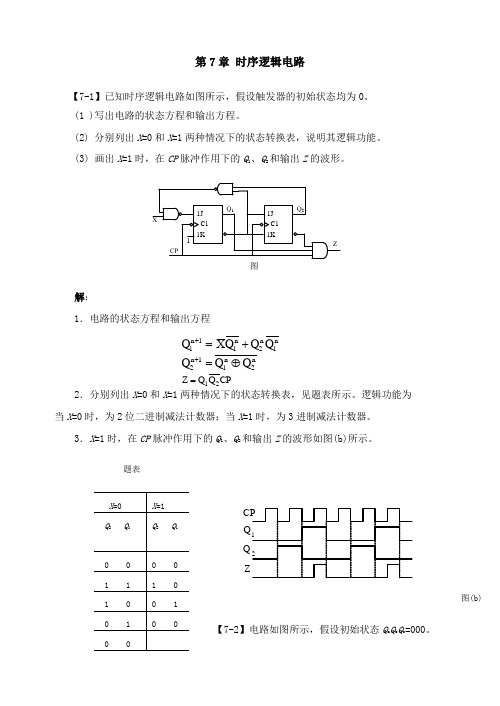

第7章 时序逻辑电路【7-1】已知时序逻辑电路如图所示,假设触发器的初始状态均为0。

(1 )写出电路的状态方程和输出方程。

(2) 分别列出X =0和X =1两种情况下的状态转换表,说明其逻辑功能。

(3) 画出X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形。

1J 1KC11J 1KC1Q 1Q 2CPXZ1图解:1.电路的状态方程和输出方程n 1n2n 11n 1Q Q Q X Q +=+n 2n 11n 2Q Q Q ⊕=+ CP Q Q Z 21=2.分别列出X =0和X =1两种情况下的状态转换表,见题表所示。

逻辑功能为 当X =0时,为2位二进制减法计数器;当X =1时,为3进制减法计数器。

3.X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形如图(b)所示。

题表Q Q Z图(b)【7-2】电路如图所示,假设初始状态Q a Q b Q c =000。

(1) 写出驱动方程、列出状态转换表、画出完整的状态转换图。

(2) 试分析该电路构成的是几进制的计数器。

Q c图解:1.写出驱动方程1a a ==K J ncn a b b Q Q K J ⋅== n b n a c Q Q J = n a c Q K = 2.写出状态方程n a 1n a Q Q =+ n a n a n a n a n c n a 1n b Q Q Q QQ Q Q +=+ nc n a n c n b n a 1n b Q Q Q Q Q Q +=+3.列出状态转换表见题表,状态转换图如图(b)所示。

图7.2(b)表7.2状态转换表CP na nbc Q Q Q 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 16 0 0 0n4.由FF a 、FF b 和FF c 构成的是六进制的计数器。

【7-3】在二进制异步计数器中,请将正确的进位端或借位端(Q 或Q )填入下表解:题表7-3下降沿触发 由 Q 端引出进位 由Q 端引出借位触发方式 加法计数器 减法计数器上升沿触发 由Q 端引出进位 由Q 端引出借位【7-4】电路如图(a)所示,假设初始状态Q 2Q 1Q 0=000。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

对应于输入数字信号最低

分辨率=

ULSB UMAX

1 2n 1

位为1,其余各位为0时的 输出电压

DAC 的位数越多,分辨 率值就越小,能分辨的最 小输出电压值也越小。

对应于输入数字 信号的各位全是 1时的输出电压

2.转换精度

绝对误差(或绝对精度)是指输入端加入最

大数字量(全1)时,D/A转换器的理论值与 实际值之差。该误差值应低于ULSB/2。相对 精度是绝对精度与满量程输出电压之比,通

f max

(2)采样定理 当采样频率 fs 大于或等于输入模拟信号uI中最高频率

整数倍表示。 编码:把量化的结果用二进制代码表示。

(1)采样-保持电路

跟随器,起缓 C冲P采隔样离脉作冲用

VT采样门 采样电容

图7-9 采样-保持电路及波形

CP=1,VT导通 ,uI向电容充 电,由于充电

时间常数很小

(场效应晶体

管的导通电阻

很小),因此C 上的充电电压

能及时跟上uI 的采样值。

采样结束,VT迅速截止,电容上的充电电压就保持了 前一采样时的输入电压uI值。

7.1.4 集成D/A转换器

1. DAC0808 DAC0808是权电 流型D/A转换器

正向参 考电压

8位并行数字 量输入端

求和电流 的输出端

负向参 考电压

图7-5 DAC0808的电路结构框图

供外接补偿

电容之用,

与UEE之间接 补偿电容

在应用DAC0808时,需要外接运算放大器和产生基准

电流用的电阻R1。

数据传送控 0 制信号,低 电平有效

1 图7-7 DAC0832逻辑框图

2.DAC0832

WR2 写信号2,即 数据传送选通信 号,低电平有效, 当 =W0R,2 且 =0时XF,ER将输入寄 存器中的数据锁 存到8位DAC寄 存器中。

0 0

1 图7-7 DAC0832逻辑框 2n

n1

(Di 2i )

i0

要求

1)基准电压稳定性好。 2)倒T形电阻网络中R和2R电阻的比值精度要高。 3)每个模拟开关的开关电压降要相等。为实现 电流从高位到低位按2的整倍数递减,模拟开关 的导通电阻也相应地按2的整倍数递增。

优点:速度较快

7.1.2 权电流型D/A转换器

常用百分数表示。

转换精度是一个综合指标,包括零点误差,它不仅与D/A 转换器中的元件参数的精度有关,而且还与环境温度、求 和运算放大器的温度漂移、及转换器的位数有关。

3.转换速度 D/A转换器的转换时间是指在输入数字信号开始转换,

到输出电压(或电流)达到稳定时所需要的时间。转换 时间越小,转换速度就越高。转换时间一般为几纳秒到 几微秒。

u o

I 2n

RF

n 1 i0

( Di

2i )

I U REF R1

在UREF=10V、R1=5kΩ、 RF=5kΩ的情况下

图7-6 DAC0808典型应用电路

uo

RF 2n

U REF R1

n 1

(Di 2i )

i0

10

28

7 i0

( Di

2i )

2.DAC0832

由权电流恒流源、 运算放大器和电子 模拟开关组成

uo i RF

图7-4 4位权电流采型用D/A了转恒换流器源原理电图

RF

I

(

D0 24

D1 23

D2 22

D3 21

)

路之后,各支路 权电流的大小均

RF

I 24

(D3

23

D2

22

D1

21

D0

20)

I 24

7.1 数/模转换器

将数字信号转换成模拟信号的电路称为数/模转换器( 简称D/A转换器或DAC)。

数模转换器的基本思路 :将数字量每一位的代码按其 权的大小转换成相应的模拟量,然后将这些模拟量相加, 即可得到与数字量成正比的总模拟量。

输入的n位 二进制数

D0 D1

D n-1

D/A转 换器

输出与输入

二进制数成

DAC0832的核心部分采用了倒T形电阻网络

8写数低号位信据电输数号选平入字1通有端信,信效即号,输,的电入流8位输D出/A,转使换用器时,需内外部接无运运算算放放大大器器。,是

输允平当且入入入许有I数寄WLR寄,效E据存1==存高锁器01,时器电存中C,S到。=将输0,输

片选信号, 1 低电平有效 0

uo 比例的模拟 电压

图7-1 数模转换器的输入、输出关系框图

7.1.1 倒T形电阻网络DAC

倒T形电阻网络D/A转换器由倒T形R-2R电阻网络、模

拟开关、运算放大器和基准电压(也称参考电压)UREF共

4部分组成。

图7-3 4位倒T形电阻网络D/A转换器原理图

7.1.1 倒T形电阻网络DAC

D0=0,S0接地; D0=1,S0虚地

图7-7 DAC0832逻辑框图

基准电压-10~+10V

DAC输出电流

集成在片内的外接 运放的反馈电阻 模拟地 电源电压 +5~+15V 数字地

7.2 模/数转换器

7.2.1 模/数转换的一般步骤

一般的A/D转换过程:采样、保持、量化和编码.

图7-8 模拟量到数字量的转换过程

采样:把时间连续变化的信号变换为时间离散的信号。 保持:保持采样信号,使有充分时间转换为数字信号。 量化:把采样保持电路的输出信号用单位量化电压的

3

(Di 2i )

i0

uo

i RF

- RF R

UREF 24

3

( Di 2i

i0

)

uo

- RF R

UREF 24

3

( Di 2i

i0

)

将输入数字量扩展到n位可得 uo

RF R

U REF 2n

n1

(Di 2i )

i0

当RF=R时,

等效为R

电阻

等效为2R

网络

等效为R

I= U REF R

7.1.1 倒T形电阻网络DAC

I= U REF R

i

D0I

16

D1I

8

D2I

4

D3I=

2

UREF R

(

D0 24

D1 23

D2 22

D3 21

)

UREF 24 R

(D3

23

D2

22

D1

21

D0

20

)

U REF 24 R

RF

3 i0

( Di

2i )

不受开关导通电 阻和压降的影响 ,提高了转换精 度。

7.1.3 D/A转换器主要技术指标

1.分辨率

分辨率是指D/A转换器模拟输出电压可能被 分离的等级数,其值为D/A转换器能分辨的 最小输出电压变化量(ULSB)与最大输出电 压(UMAX)即满量程输出电压之比。