verilog串并转换并串转换

verilog串并转换并串转换

当ena为低电平时,无论a为何值,总是输出000,当ena为高电平时,输出即随a的数值变化而变化,当a为01000000时,b为110,当a为00100000是,b为101以此类推,同时最后一个波形为,当a为10100000时,b为111,体现了优先译码的功能,此结果和当初设计的功能一致的。

if(!ena)

begin

b=8'b00000000;

end

else

begin

case(a)

3'b000: b=8'b00000001;

3'b001: b=8'b00000010;

3'b010: b=8'b00000100;

3'b011: b=8'b00001000;

3'b100: b=8'b00010000;

reg ena;

wire [7:0] b;

initial begin

a = 3'b000;

ena = 1'b0;

#50;

ena = 1'b1;

#50;

a=3'b001;

#50;

a=3'b010;

#50;

a=3'b011;

#50;

a=3'b100;

#50;

a=3'b101;

#50;

a=3'b110;

#50;

仿真代码:

module tb;

reg [7:0] a;

reg ena;

wire [2:0] b;

initial begin

a = 8'b10000000;

verilog string类型

verilog string类型在Verilog中,并没有内置的"string"数据类型。

Verilog 是一种硬件描述语言,主要用于描述数字电路和系统。

它主要使用整数、实数、逻辑值(如0、1、X、Z)等基本数据类型以及数组、结构体等复合数据类型。

如果你需要处理字符串,你可能需要自己定义一个字符串数据类型或者使用一些现有的库。

例如,有些Verilog库提供了字符串操作的功能,你可以使用这些库来处理字符串。

如果你需要在Verilog中处理字符串,一种常见的方法是将字符串转换为整数数组,然后使用数组进行操作。

例如,你可以将每个字符转换为其ASCII码,然后将这些码存储为整数数组。

下面是一个简单的示例,展示如何在Verilog中将字符串转换为整数数组:verilog复制代码:module StringToArray (input wire [7:0] str, // 假设字符串是一个8位无符号整数output reg [7:0] arr // 输出整数数组);integer i;always @(*) beginfor (i = 0; i < 8; i = i + 1) begincase (str[i])8'h30: arr[i] = 8'h30 - 8'h30; // '0'8'h31: arr[i] = 8'h31 - 8'h30; // '1'// 其他字符...default: arr[i] = 8'h0; // 未定义的字符设置为0endcaseendendendmodule请注意,这只是一个简单的示例,并不适用于所有情况。

实际应用中,你可能需要根据具体需求进行更复杂的处理。

verilog 16进制转换成字符串

verilog 16进制转换成字符串在数字电路设计中,常常需要对16进制数进行转换和处理。

而其中一个常见的应用就是将16进制数转换成字符串。

本文将以Verilog语言为例,介绍如何将16进制数转换成字符串。

我们需要了解什么是16进制数和字符串。

16进制数是一种表示数字的方式,它使用0-9和A-F来表示0-15这16个数字。

字符串是由字符组成的序列,它可以包含任意字符,例如字母、数字、符号等。

在Verilog中,我们可以使用内置函数$display来实现16进制数转换成字符串的功能。

$display函数可以将指定的变量以字符串的形式输出。

下面是一个简单的例子:```verilogmodule hex_to_str;reg [7:0] hex_num;initial beginhex_num = 8'h41; // 16进制数'A'$display("转换后的字符串为:%s", hex_num);endendmodule```在上面的例子中,我们定义了一个8位的寄存器hex_num,并将其赋值为16进制数'A'。

然后使用$display函数将hex_num转换成字符串并输出。

可以看到,当我们运行这段代码时,输出的结果是转换后的字符串为:"A"。

这说明我们成功地将16进制数转换成了字符串。

除了使用$display函数,我们还可以使用其他方法来实现16进制数转换成字符串的功能。

例如,我们可以使用$strobe函数来控制输出字符串的时机,或者使用$write函数来实现更灵活的输出方式。

下面是一个使用$write函数的例子:```verilogmodule hex_to_str;reg [7:0] hex_num;initial beginhex_num = 8'h41; // 16进制数'A'$write("转换后的字符串为:%s", hex_num);endendmodule```在上面的例子中,我们使用了$write函数来输出转换后的字符串。

EDA技术与Verilog_HDL(潘松)第6章习题答案

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同方法,它们是什么,如何实现?答:同步清零、异步清零,在过程语句敏感信号表中的逻辑表述posedge CLK用于指明正向跳变,或negedge用于指明负向跳变实现6-2 哪一种复位方法必须将复位信号放在敏感信号表中?给出这两种电路的Verilog 描述。

答:异步复位必须将复位信号放在敏感信号表中。

同步清零:always @(posedge CLK) //CLK上升沿启动Q<=D; //当CLK有升沿时D被锁入Q异步清零:always @(posedge CLK or negedge RST) begin //块开始if(!RST)Q<=0; //如果RST=0条件成立,Q被清0else if(EN) Q<=D;//在CLK上升沿处,EN=1,则执行赋值语句end//块结束6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

module Statistics8(sum,A); output[3:0]sum;input[7:0] A;reg[3:0] sum;integer i;always @(A)beginsum=0;for(i=0;i<=8;i=i+1) //for 语句if(A[i]) sum=sum+1;else sum=sum;endendmodule module Statistics8(sum,A); parameter S=4;output[3:0]sum;input[7:0] A;reg[3:0] sum;reg[2*S:1]TA;integer i;always @(A)beginTA=A; sum=0;repeat(2*S)beginif(TA[1])sum=sum+1;TA=TA>>1;endendendmodulerepeat循环语句for循环语句module Statistics8(sum,A);parameter S=8;output[3:0]sum;input[7:0] A;reg[S:1] AT;reg[3:0] sum;reg[S:0] CT;always @(A) beginAT={{S{1'b0}},A}; sum=0; CT=S;while(CT>0) beginif(AT[1])sum=sum+1;else sum=sum;begin CT= CT-1; AT=AT>>1; end end endendmodule6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

verilog 16进制转换成字符串

verilog 16进制转换成字符串Verilog语言是一种硬件描述语言,常被用于数字电路的设计与仿真。

在Verilog中,数值可以使用16进制表示,这样的表示方式在一些场景下更加直观和方便。

本文将以"16进制转换成字符串"为标题,讨论该过程的具体实现和应用。

在数字电路设计中,经常会遇到需要将16进制数转换成字符串的情况。

这种转换的过程涉及到将16进制数的每一位转换成对应的字符,最终得到一个字符串表示。

Verilog提供了一些内置函数和操作符,可以方便地进行这种转换。

我们需要将16进制数的每一位提取出来,并转换成对应的字符。

在Verilog中,可以使用位选择操作符"[]"来实现。

例如,对于一个16位的16进制数,可以使用以下代码将每一位提取出来:```verilogreg [15:0] hex_num = 16'hABCD;reg [3:0] hex_digits [0:15] = {4'h0, 4'h1, 4'h2, 4'h3,4'h4, 4'h5, 4'h6, 4'h7,4'h8, 4'h9, 4'hA, 4'hB,4'hC, 4'hD, 4'hE, 4'hF};reg [3:0] digit_0 = hex_digits[hex_num[3:0]];reg [3:0] digit_1 = hex_digits[hex_num[7:4]];// ...```这样,我们就可以将16进制数的每一位转换成对应的十六进制字符。

接下来,我们需要将这些字符拼接起来,得到最终的字符串表示。

在Verilog中,可以使用连接操作符"{}"来实现。

例如:```verilogreg [15:0] hex_num = 16'hABCD;reg [3:0] hex_digits [0:15] = {4'h0, 4'h1, 4'h2, 4'h3,4'h4, 4'h5, 4'h6, 4'h7,4'h8, 4'h9, 4'hA, 4'hB,4'hC, 4'hD, 4'hE, 4'hF};reg [31:0] str_num;always @* beginstr_num = {hex_digits[hex_num[3:0]], hex_digits[hex_num[7:4]], hex_digits[hex_num[11:8]], hex_digits[hex_num[15:12]]};end```这样,我们就可以得到一个包含16进制数对应字符的字符串。

关于串并转换的VERILOG代码

关于串并转换的VERILOG代码设计题目:8位数据总线,能实现串行数据到8位并行数据的转换,以及8位并行数据到串行数据的转换.具体是哪种转换由sp控制端决定,当sp=1时,是串行输入/并行输出;当sp=0时,是并行输入/串行输出.一,模块定义以及功能描述输入端口输入说明rst 复位信号clk 时钟信号sp 使能信号输出端口输出说明ack 连接应答信号I/O端口 I/O说明data 数据总线二. 代码1.功能模块部分module ptosda(clk,rst,sp,dataack);input clk,rst,sp;inout ack;input [7:0] data;reg [3:0] state_out;reg [7:0] databuf;wire [7:0] data;parameter bing=1'b0,chuan=1'0;parameter bit0=4'b0000,bit1=4'b0001,bit2=4'b0010,bit3=4'b0011,bit4=4'b0100,bit5=4'b0101,bit6=4'b0110,bit7=4'b0111,idel=4'b1000;assign data[7]=link_write?databuf[7]:1'bz;assign data=link_write?databuf:8'bz;always@(posedge clk)beginif(!rst)beginack <= 0;link_write <=0;state_out <= idle;databuf <= 0;endelsebegincase(sp)bing:beginif(finish_flag == 0) beginDtoS;endelsebeginstate_out <= idel; databuf <= data; finish_flag = 0; endendchuan:beginif(finish_flag == 0) beginStoD;endelsebeginstate_out <= idel; finish_flag = 0;endendcaseendendtask StoD;case(state_out)idle:beginlink_write <= 0;ack <= 1;databuf[7] <= data[7]; databuf <= databuf>>1; state_out <= bit7;endbit7:beginack <=1;databuf[7] <= data[7]; databuf <= databuf>>1; state_out <= bit6;endbit6:beginack <=1;databuf[7] <= data[7]; databuf <= databuf>>1; state_out <= bit5;endbit5:beginack <=1;databuf[7] <= data[7]; databuf <= databuf>>1; state_out <= bit4;endbit4:beginack <=1;databuf[7] <= data[7]; databuf <= databuf>>1; state_out <= bit3;endbit2:beginack <=1;databuf[7] <= data[7]; databuf <= databuf>>1; state_out <= bit1;bit1:beginack<=1;databuf[7] <= data[7]; databuf <= databuf>>1; state_out <= bit0;endbit0:beginlink_write <= 1;finish_flag=1;ack <= 0;state_out <= 4'b111;enddefault:beginlink_write <= 0;state_out <= 4'b111;endendcaseendendtasktask DtoS;begincase(state_out)idle:beginlink_write <=1;state_out <= bit7;endbit7:begindatabuf <= databuf << 1; state_out <= bit6;endbit6:begindatabuf <= databuf << 1; state_out <= bit5;endbit5:begindatabuf <= databuf << 1; state_out <= bit4;endbit4:begindatabuf <= databuf << 1; state_out <= bit3;endbit3:begindatabuf <= databuf << 1; state_out <= bit2;endbit2:begindatabuf <= databuf << 1; state_out <= bit1;endbit1:begindatabuf <= databuf << 1; state_out <= bit0;endbit0:beginlink_write <= 0;finish_flag = 1;ack <= 1;state_out <= 4'b1111; enddefault:beginlink_write <= 0;state_out <= 4'b1111; endendcaseendendtaskendmodule。

串并转换VHDL

ready <= '1';

data_valid <= '0';

shift_start <= '0';

next_state <= shift;

when shift =>

reg_en <= '1';

ready : out std_logic; --low active,ready to recieve data

q : out std_logic

);

end p2s;

architecture Behavioral of p2s is

signal reg : std_logic_vector(7 downto 0);

-- Description: This module is designed to implement parallel to serial conversion

--------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity p2s is

port(

reset : in std_logic;

begin

counter: process(reset,clk,shift_start)

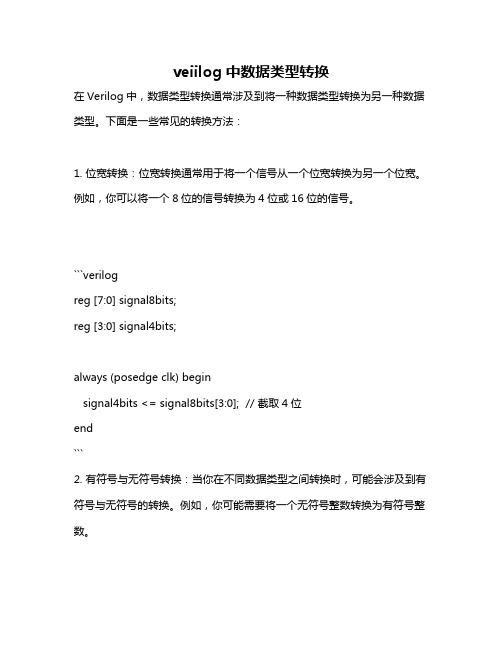

veiilog中数据类型转换

veiilog中数据类型转换在Verilog中,数据类型转换通常涉及到将一种数据类型转换为另一种数据类型。

下面是一些常见的转换方法:1. 位宽转换:位宽转换通常用于将一个信号从一个位宽转换为另一个位宽。

例如,你可以将一个8位的信号转换为4位或16位的信号。

```verilogreg [7:0] signal8bits;reg [3:0] signal4bits;always (posedge clk) beginsignal4bits <= signal8bits[3:0]; // 截取4位end```2. 有符号与无符号转换:当你在不同数据类型之间转换时,可能会涉及到有符号与无符号的转换。

例如,你可能需要将一个无符号整数转换为有符号整数。

```verilogreg [7:0] unsigned_num;reg signed_num;always (posedge clk) beginsigned_num <= signed'(unsigned_num); // 转换有符号整数end```3. 定点数与整数之间的转换:在数字信号处理和通信中,经常需要将定点数转换为整数或反之。

这通常涉及到移位和缩放操作。

4. 强制类型转换:你可以使用`<类型名称>`来强制类型转换。

例如,如果你想将一个无符号整数转换为有符号整数,你可以这样做:```verilogreg [7:0] unsigned_num;reg signed_num;always (posedge clk) beginsigned_num <= <signed> unsigned_num; // 强制类型转换end```5. 使用内置函数进行转换:Verilog也提供了一些内置函数来进行数据类型转换,如`$signed`和`$unsigned`。

这些函数可以用于将一个信号转换为有符号或无符号版本。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

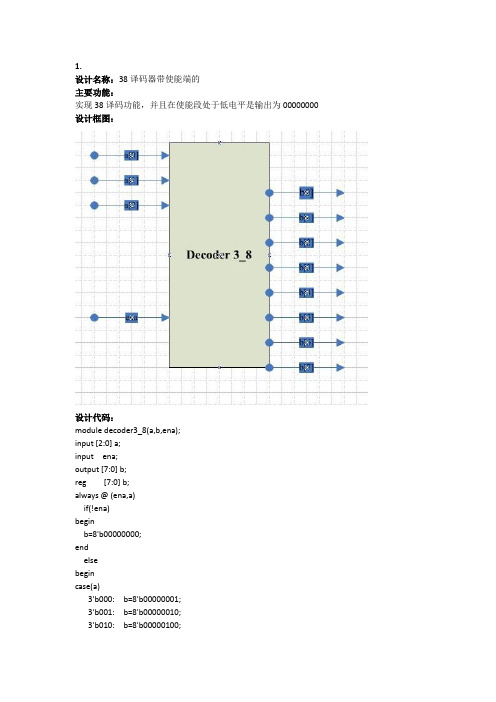

1.设计名称:38译码器带使能端的主要功能:实现38译码功能,并且在使能段处于低电平是输出为00000000 设计框图:设计代码:module decoder3_8(a,b,ena);input [2:0] a;input ena;output [7:0] b;reg [7:0] b;always @ (ena,a)if(!ena)beginb=8'b00000000;endelsebegincase(a)3'b000: b=8'b00000001;3'b001: b=8'b00000010;3'b010: b=8'b00000100;3'b011: b=8'b00001000;3'b100: b=8'b00010000;3'b101: b=8'b00100000;3'b110: b=8'b01000000;3'b111: b=8'b10000000;default: b=8'b00000000; endcaseendendmodule仿真代码:`timescale 1ns/1nsmodule tb;reg [2:0] a;reg ena;wire [7:0] b;initial begina = 3'b000;ena = 1'b0;#50;ena = 1'b1;#50;a=3'b001;#50;a=3'b010;#50;a=3'b011;#50;a=3'b100;#50;a=3'b101;#50;a=3'b110;#50;a=3'b111;#50;$ stop;enddecoder3_8 udecoder3_8(.a(a),.ena(ena),.b(b));endmodule仿真结果:辅助说明:当ena为低电平时,无论a为何值,总是输出00000000,当ena为高电平时,输出即随a 的数值变化而变化,当a为001时,b的值变为00000010;当a为010时,b的值变为00000100,这与设计时的功能是一致的。

_______________________________________________________________________________ 2.设计名称:83编码器带使能端的和优先级主要功能:实现83编码功能,并且在使能段处于低电平是输出为000,同时最高位的优先级最高设计框图:设计代码:module undecoder8_3(a,b,ena);input [7:0] a;input ena;output [3:0] b;reg [3:0] b;always @ (ena,a)if(!ena)beginb=3'b000;endelseif(a[7]) b=3'b111;elseif(a[6]) b=3'b110;elseif(a[5]) b=3'b101;elseif(a[4]) b=3'b100;elseif(a[3]) b=3'b011;elseif(a[2]) b=3'b010;elseif(a[1]) b=3'b001;elseif(a[0]) b=3'b000;else b=3'b000;endmodule仿真代码:module tb;reg [7:0] a;reg ena;wire [2:0] b;initial begina = 8'b10000000;ena = 1'b0;#50;ena = 1'b1;#50;a=8'b01000000;#50;a=8'b00100000;#50;a=8'b00010000;#50;a=8'b00001000;#50;a=8'b00000010;#50;a=8'b00000001;#50;a=8'b10100000;#50;$stop;endundecoder8_3 unit1_undecoder8_3(.a(a),.ena(ena),.b(b));endmodule仿真结果:辅助说明:当ena为低电平时,无论a为何值,总是输出000,当ena为高电平时,输出即随a的数值变化而变化,当a为01000000时,b为110,当a为00100000是,b为101以此类推,同时最后一个波形为,当a为10100000时,b为111,体现了优先译码的功能,此结果和当初设计的功能一致的。

_______________________________________________________________________________ 3.设计名称:设计一个1:1的3分频器主要功能:实现3分频,同时高低电平比为1:1设计框图:设计代码:这个设计可以利用模三计数器分别在时钟的上升和下降沿设计一个高低电平为1:2的3分频,然后将两个波形相或即能得到结果。

代码一:module Devider2_1(//inputsclk,rst_n,//outputsopt1,opt2,opt);input clk;input rst_n;output opt;output opt1;output opt2;reg opt1;reg [1:0] temp1;reg opt2;reg [1:0] temp2;always@(posedge clk)beginif(!rst_n)begintemp1 <= 2'd0;opt1 <= 1'b0;endelse if(temp1==1)beginopt1 <=1'b1;temp1 <= temp1 + 2'd1;endelse if(temp1==2'd2) beginopt1 <= 1'b0;temp1 <= 2'd0;endelsebegintemp1 <= temp1+2'd1; endendalways@(negedge clk)beginif(!rst_n)temp2 <= 2'd0;opt2 <= 1'b0;endelse if(temp2==1) beginopt2 <=1'b1;temp2 <= temp2 + 2'd1;endelse if(temp2==2'd2)beginopt2 <= 1'b0;temp2 <= 2'd0;endelsebegintemp2 <= temp2+2'd1;endendassign opt = opt1 || opt2;endmodule同时也可以用同样的方法设计一个在上升和下降沿高低电平2:1的3分频器,将两个波形相与即可。

代码二:module Devider2_1(//inputsclk,rst_n,//outputsopt1,opt2,opt);input clk;input rst_n;output opt;output opt1;output opt2;reg opt1;reg opt2;reg [1:0] temp1;reg [1:0] temp2;always@(posedge clk)if(!rst_n)begintemp1 <= 2'd0;opt1 <= 1'b0;end //resetelse if(temp1==2'd0)beginopt1<=1'b1;temp1 <= temp1 + 2'd1; endelse if(temp1==2'd1)beginopt1 <=1'b1;temp1 <= temp1 + 2'd1; endelse if(temp1==2'd2)beginopt1 <= 1'b0;temp1 <= 2'd0;endendalways@(negedge clk)beginif(!rst_n)begintemp2 <= 2'd0;opt2 <= 1'b0;end //resetelse if(temp2==2'd0)beginopt2<=1'b1;temp2 <= temp2 + 2'd1; endelse if(temp2==2'd1)beginopt2 <=1'b1;temp2 <= temp2 + 2'd1; endelse if(temp2==2'd2)beginopt2 <= 1'b0;temp2 <= 2'd0;endassign opt = opt1&&opt2; endmodule仿真代码:上面两个代码的仿真代码是一样的。

`timescale 1ns/1nsmodule tb;//inputsreg clk;reg rst_n;//outputswire opt1;wire opt2;wire opt;//generate clkalways #10 clk = ~clk;//tb startsInitialbeginclk = 1'b0;rst_n = 1'b0;#100;rst_n = 1'b1;#500;$stop;end//Instant DUTDevider2_1 uDevider2_1(//inputs.clk(clk),.rst_n(rst_n),//outputs.opt1(opt1),.opt2(opt2),.opt(opt));endmodule仿真结果:(a)高低电平为1:2设计的(b)高低电平为2:1设计的辅助说明:(a)中opt1为上升沿触发的高低电平1:2的3分频,opt2为下降沿触发的高低电平为1:2的3分频,可以看出在rst_n为0进行清复位,之后在rst_n为1是进行分频,最后所得opt结果为1:1的3分频,符合设计要求。

(b)中opt1为上升沿触发的高低电平2:1的3分频,opt2为下降沿触发的高低电平为2:1的3分频,可以看出在rst_n为0进行清复位,之后在rst_n为1是进行分频,最后所得opt结果为1:1的3分频,符合设计要求。