0954@52RD_手机数字基带处理芯片中的静态时序分析

FPGA静态时序分析

FPGA静态时序分析在FPGA设计中,静态时序分析是一个非常重要的步骤,用于评估电路在不同工作条件下的时序要求是否能够满足。

本文将介绍FPGA静态时序分析的概念、步骤、工具以及常见的优化技术,以帮助读者更好地理解和应用静态时序分析。

1.概念静态时序分析是指在FPGA设计中,通过分析电路中各个时序元素(如时钟、延迟等)之间的关系,来确定电路是否能够满足设计要求的一种分析方法。

它能够预测电路在各种工作条件下的最快和最慢工作频率,从而保证电路能够正确运行。

2.步骤静态时序分析通常包括以下几个步骤:(1)设计综合:首先将设计描述(如Verilog或VHDL)综合成门级电路表示,得到与FPGA相关的逻辑网表。

(2)时钟约束设置:设置设计中的时钟频率和时钟边沿等约束条件。

时钟约束对于时序分析非常关键,它告诉工具如何处理时钟信号以及如何计算时钟间的延迟等。

(3)路径分析:对电路中的各个时序路径进行分析,包括从时钟到寄存器的路径(称为注册路径)和从寄存器到输出的路径(称为组合路径)。

路径分析主要用于确定时序路径上的关键路径和最长路径。

(4)时序缺陷检测:对设计中存在的潜在时序缺陷进行检测,例如时序冒险、信号捕获问题等。

时序缺陷可能导致电路不能按照设计要求正确工作,因此在分析过程中需要及时检测和解决这些问题。

(5)时序优化:根据静态时序分析的结果,对电路进行优化,以满足设计要求。

常见的优化技术包括添加额外的时钟约束、优化逻辑电路结构、调整时钟频率等。

3.工具在进行FPGA静态时序分析时,通常使用专门的时序分析工具,如Xilinx的TimeQuest和Altera的TimeQuest等。

这些工具能够自动识别设计中的时序路径和时序要求,并进行全面的时序分析和优化。

4.优化技术静态时序分析的结果可以指导电路的优化,以满足设计要求。

常见的优化技术包括:(1)添加额外的时钟约束:通过设置更严格的时钟约束,可以减小时钟间的延迟、提高时钟频率,并且可以帮助工具更准确地评估时序关系。

非常详细的静态时序分析教程

非常详细的静态时序分析教程静态时序分析是电子设计自动化领域中的重要方法之一,用于评估数字电路中的时序性能。

本教程将介绍静态时序分析的基本概念、方法和步骤,并提供一些实例来帮助读者深入了解这个领域。

一、静态时序分析的基本概念在进行静态时序分析之前,我们需要了解一些基本概念:1.时钟边沿:时钟是数字电路中的基本信号之一,它的边沿可以分为上升沿和下降沿。

时序分析通常以时钟的上升沿作为参考边沿进行分析。

2.关键路径:在一个数字电路中,存在多条路径可以连接输入和输出。

关键路径是指在特定时钟频率下,数据从输入到输出的延时最长的路径。

时序分析的目标之一就是找到并优化关键路径,以提高电路的性能。

3.时序约束:时序约束是对数字电路的时序性能要求的规定。

通常由设计者在进行时序分析之前进行设置,用于指导分析工具进行正确的分析和优化。

二、静态时序分析的方法和步骤静态时序分析的主要方法是通过对电路中的时钟域、数据路径和约束条件进行建模和分析,从而判断关键路径和优化方案。

下面是静态时序分析的基本步骤:1. 建立电路模型:首先,需要将数字电路转化为时序分析工具可以理解的模型,通常可以使用硬件描述语言(如Verilog或VHDL)对电路进行描述。

2.设定时序约束:根据设计规范和目标性能要求,制定适当的时序约束,如最大延时、最小脉冲宽度等。

时序约束的制定需要根据具体的电路应用和设计要求进行。

3.进行静态时序分析:使用时序分析工具对电路进行分析,找到关键路径,并计算出关键路径的延时。

关键路径上的最大延时指示了电路的最坏情况性能。

4.优化关键路径:在找到关键路径后,可以通过各种手段进行优化,如增加缓冲器、减少逻辑门延时等。

优化的目标是减小关键路径的延时,以提高整个电路的性能。

5.重新进行时序分析:在优化关键路径之后,需要重新进行时序分析,确保所做的优化在整个电路中得到正确应用,并满足时序约束。

三、实例分析让我们通过一个简单的例子来说明静态时序分析的具体过程。

手机数字基带处理芯片中的静态时序分析

手机数字基带处理芯片中的静态时序分析

葛维;郑建宏

【期刊名称】《微计算机信息》

【年(卷),期】2007(023)023

【摘要】本文首先以Synopsys公司的工具Prime Time SI为基础,介绍了ASIC 设计中主流的时序分析方法:静态时序分析及其基本原理和操作流程;接着分析了它与门级仿真之间的关系,提出了几个在TDS-CDMA数字基带处理芯片设计中遇到的疑难问题,并解释其原因;最后,介绍了TDS-CDMA数字基带处理芯片中的静态时序分析过程.

【总页数】3页(P284-285,82)

【作者】葛维;郑建宏

【作者单位】400065,重庆,重庆邮电大学3G研究院;400065,重庆,重庆邮电大学3G研究院

【正文语种】中文

【中图分类】TP303

【相关文献】

1.供电切换在多媒体手机基带芯片中的应用研究 [J], 唐佳廉;于海林

2.苏州灵芯发布集成Wi-Fi基带处理器IP [J],

3.Tensilica扩大海思半导体对数据处理器、ConnX基带引擎和HiFi音频数字信号处理IP核的授权 [J],

4.中大容量数字微波系统的基带数字处理载波恢复环 [J], 梅顺良

5.802.11基带处理芯片中GFSK调制解调系统的实现 [J], 沈力为;杨莲兴

因版权原因,仅展示原文概要,查看原文内容请购买。

静态时序分析(StaticTimingAnalysis)基础及应用

静态时序分析(StaticTimingAnalysis)基础及应⽤静态时序分析(Static Timing Analysis)基础及应⽤◎陈麒旭前⾔在制程进⼊深次微⽶世代之后,芯⽚(IC)设计的⾼复杂度及系统单芯⽚(SOC)设计⽅式兴起。

此⼀趋势使得如何确保IC 质量成为今⽇所有设计从业⼈员不得不⾯临之重⼤课题。

静态时序分析(Static Timing Analysis简称STA)经由完整的分析⽅式判断IC是否能够在使⽤者的时序环境下正常⼯作,对确保IC质量之课题,提供⼀个不错的解决⽅案。

然⽽,对于许多IC设计者⽽⾔,STA是个既熟悉却⼜陌⽣的名词。

本⽂将⼒求以简单叙述及图例说明的⽅式,对STA的基础概念及其在IC设计流程中的应⽤做详尽的介绍。

什么是STA?STA的简单定义如下:套⽤特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

以分析的⽅式区分,可分为Path-Based及Block-Based两种。

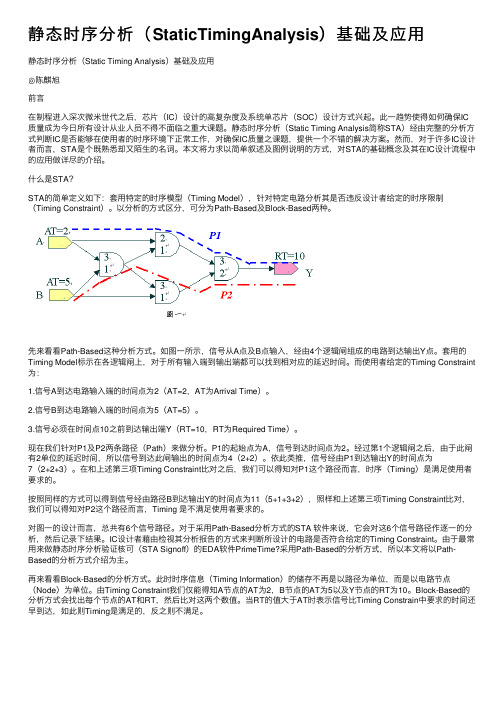

先来看看Path-Based这种分析⽅式。

如图⼀所⽰,信号从A点及B点输⼊,经由4个逻辑闸组成的电路到达输出Y点。

套⽤的Timing Model标⽰在各逻辑闸上,对于所有输⼊端到输出端都可以找到相对应的延迟时间。

⽽使⽤者给定的Timing Constraint 为:1.信号A到达电路输⼊端的时间点为2(AT=2,AT为Arrival Time)。

2.信号B到达电路输⼊端的时间点为5(AT=5)。

3.信号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

现在我们针对P1及P2两条路径(Path)来做分析。

P1的起始点为A,信号到达时间点为2。

经过第1个逻辑闸之后,由于此闸有2单位的延迟时间,所以信号到达此闸输出的时间点为4(2+2)。

依此类推,信号经由P1到达输出Y的时间点为7(2+2+3)。

静态时序分析

静态时序分析或称静态时序验证,是电子工程中,对数字电路的时序进行计算、预计的工作流程,该流程不需要通过输入激励的方式进行仿真。

在一个同步数字系统中,数据的流动应当以一致的步伐进行,即时间脉冲信号每改变一次,数据能够改变一次。

这种运作方式是通过同步的数字电路器件,例如触发器或锁存器来实现的,这类器件以时钟信号为指示将其输入端的数据复制到其输出端。

在同步电路中,只存在两种时序错误:

保持时间违例:时钟信号有效变化之后,如果输入信号没能保持足够长的时间,数据将不能在下一个时钟信号变化时被记录下来;

建立时间违例:时钟信号有效变化之前,如果输入信号没能保持足够长的时间,数据将不能在那个时钟信号变化时被记录下来。

静态时序分析(Static

静态时序分析(Static Timing Analysis)基础与应用前言在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。

此一趋势使得如何确保IC品质成为今日所有设计从业人员不得不面临之重大课题。

静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者的时序环境下正常工作,对确保IC品质之课题,提供一个不错的解决方案。

然而,对于许多IC设计者而言,STA 是个既熟悉却又陌生的名词。

本文将力求以简单叙述及图例说明的方式,对STA 的基础概念及其在IC设计流程中的应用做详尽的介绍。

什么是STA?STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

以分析的方式区分,可分为Path-Based及Block-Based两种。

先来看看Path-Based这种分析方式。

如图一所示,讯号从A点及B点输入,经由4个逻辑闸组成的电路到达输出Y 点。

套用的Timing Model标示在各逻辑闸上,对于所有输入端到输出端都可以找到相对应的延迟时间。

而使用者给定的Timing Constraint为:1.讯号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。

2.讯号B到达电路输入端的时间点为5(AT=5)。

3.讯号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

现在我们针对P1及P2两条路径(Path)来做分析。

P1的起始点为A,讯号到达时间点为2。

经过第1个逻辑闸之后,由于此闸有2单位的延迟时间,所以讯号到达此闸输出的时间点为4(2+2)。

依此类推,讯号经由P1到达输出Y的时间点为7(2+2+3)。

在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。

静态时序分析(Static Timing Analysis)基础(5)

前言在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。

此一趋势使得如何确保IC品质成为今日所有设计从业人员不得不面临之重大课题。

静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者指定的时序下正常工作,对确保IC 品质之课题,提供一个不错的解决方案。

在「静态时序分析(Static Timing Analysis)基础及应用(上)」一文中笔者以简单叙述及图例说明的方式,对STA的基础概念做了详尽的说明。

接下来,就让我们藉由实际设计范例来了解STA在设计流程的应用。

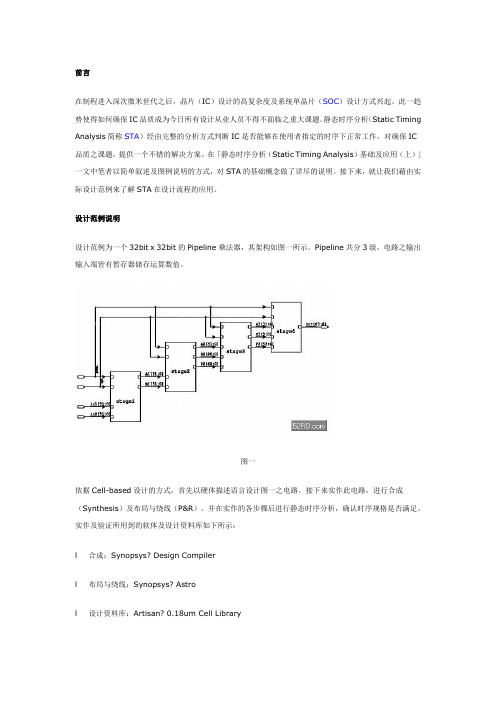

设计范例说明设计范例为一个32bit x 32bit的Pipeline乘法器,其架构如图一所示。

Pipeline共分3级,电路之输出输入端皆有暂存器储存运算数值。

图一依据Cell-based设计的方式,首先以硬体描述语言设计图一之电路。

接下来实作此电路,进行合成(Synthesis)及布局与绕线(P&R)。

并在实作的各步骤后进行静态时序分析,确认时序规格是否满足。

实作及验证所用到的软体及设计资料库如下所示:l 合成:Synopsys? Design Compilerl 布局与绕线:Synopsys? Astrol 设计资料库:Artisan? 0.18um Cell Library在接下来的文章中,各位将会看到静态时序分析在实作过程中的应用。

藉由实际产生的数据了解在不同实做步骤上时序分析的差异。

时序限制(Timing Constraint)要作静态时序分析,首先要有时序限制。

此设计范例的时序限制如下所述。

(后为设定时序限制之SDC 指令)1 时脉规格(Clock Specification)1.1 周期:6nscreate_clock -name "MY_CLOCK" -period 6 -waveform {0 3} [get_ports {clk}]1.2 Source Latency:1nsset_clock_latency -source 1 [get_clocks {MY_CLOCK}]1.3 Network Latency:1nsset_clock_latency 1 [get_clocks {MY_CLOCK}]1.4 Skew:0.5nsset_clock_uncertainty 0.5 [get_clocks {MY_CLOCK}]2 周边状况(Boundary Condition)2.1 输入延迟(Input Delay):1.2nsset allin_except_CLK [remove_from_collection [all_inputs] [get_ports clk] ]set_input_delay $I_DELAY -clock MY_CLOCK $allin_except_CLK2.2 输出延迟(Output Delay):1.2nsset_output_delay $O_DELAY -clock MY_CLOCK [all_outputs]2.3 输出负载(Output Loading):0.5pFset_load $O_LOAD 0.5 [all_outputs]3 时序例外(Timing Exception):无合成软体之时序报告当Synopsys? Design Compiler将电路合成完毕后,执行下面指令可以产生时序报告:report_timing -path full -delay max -max_paths 10 -input_pins-nets -transition_time -capacitance > timing_syn.txt时序报告会储存在timing_syn.txt此档案中。

计算机硬件设计中的时序分析方法

计算机硬件设计中的时序分析方法时序分析是计算机硬件设计过程中非常重要的一环。

它可以帮助设计师确保系统中各个元件的工作时序满足预期的要求,从而保证系统的正确性和稳定性。

本文将介绍几种常见的时序分析方法,包括静态时序分析、动态时序分析以及时钟域分析。

一、静态时序分析静态时序分析是在不考虑信号传输延迟和时钟周期的情况下进行的时序分析。

它主要依赖于电路元件的逻辑关系和布局设计来进行分析。

在进行静态时序分析时,需要提供设计的电路原理图、信号路径以及逻辑关系等信息。

常用的静态时序分析工具包括VHDL等硬件描述语言,它们可以帮助设计师对电路进行建模、仿真和验证,从而找到潜在的时序问题。

静态时序分析可以帮助设计师发现电路中的时序冲突、时序违约和时序不确定性等问题。

通过对电路进行静态时序分析,设计师可以提前预测并解决可能出现的时序问题,从而减少后期测试的工作量和风险。

二、动态时序分析动态时序分析是指考虑信号传输延迟和时钟周期的情况下进行的时序分析。

它主要依赖于电路的时钟边沿和时钟周期等信息进行分析。

在进行动态时序分析时,需要提供设计的时钟频率、延迟模型以及电路中的时钟约束等信息。

常用的动态时序分析工具包括模拟器和时序分析器等。

动态时序分析可以帮助设计师检测电路中的时序故障、时序偏差和时序违规等问题。

通过对电路进行动态时序分析,设计师可以模拟真实的工作环境,准确评估电路的时序性能,从而提前发现并解决时序问题。

三、时钟域分析时钟域分析是指对电路中不同时钟域的信号传输进行分析。

在现代的计算机硬件设计中,通常存在多个时钟域,每个时钟域都有自己的时钟信号和时钟延迟特性。

时钟域之间的信号传输需要进行专门的时序分析,以保证信号的正确传递和同步。

时钟域分析可以帮助设计师解决时钟间的异步问题、时序冲突和时序不一致等。

通过对不同时钟域的信号传输进行分析,设计师可以确定时钟域之间的接口逻辑,优化时钟插入和同步方法,确保电路的正常工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

手机数字基带处理芯片中的静态时序分析内容摘要:动态时序分析时不可能产生完备的测试向量,覆盖门级网表中的每一条路径。

因此在动态时序分析中,无法暴露一些路径上可能存在的时序问题;而静态时序分析,可以方便地显示出全部路径的时序关系,因此逐步成为集成电路设计签字认可的标准。

1.引言随着深亚微米技术的发展,数字电路的规模已经发展到上百万门甚至上千万门。

工艺也从几十um提高到65nm甚至45nm。

这样的电路规模做验证的时间在整个芯片的开发周期所占的比例会越来越重。

通常,在做验证的时候,我们都会采用动态验证的方法。

现在,用静态验证方法(STA Static Timing Analysis),不仅能够完成验证的工作,而且还能大大节省验证所需要的时间。

静态时序分析简称它提供了一种针对大规模门级电路进行时序验证的有效方法。

静态时序分析是相对于动态时序分析而言的。

动态时序分析时不可能产生完备的测试向量,覆盖门级网表中的每一条路径。

因此在动态时序分析中,无法暴露一些路径上可能存在的时序问题;而静态时序分析,可以方便地显示出全部路径的时序关系,因此逐步成为集成电路设计签字认可的标准。

2.静态时序分析工作原理本文以Synopsys公司的Prime Time SI作为时序分析的工具,介绍静态时序分析的工作原理。

Prime Time把整个设计电路打散成从主要的输入端口到电路触发器、从触发器到触发器、从触发器到主要输出端口、从主要的输出端口到主要的输出端口、四种类型的时序路径,分析不同路径的时序信息,得到建立时间(setup time)和保持时间(hold time)的计算结果。

而Prime time SI又在Prime time的基础上加入串扰分析(Crosstalk analy sis)。

串扰是由两个或者多个物理相邻连线之间的容性交叉耦合(capacitive cross-coupli ng)产生的相互作用。

随着工艺越来越进步,在130nm或者90nm的工艺下,串扰的影响已经变得与单元延迟和线延迟一样重要。

2.1 时序路径的分析整个电路的静态时序分析都是由时序路径分析组成。

时序路径分析就是检查从发射沿(l unching edge)到捕获沿(capturing edge)的时间是否满足设计的需要。

它主要可以分为两类:建立时间路径这种路径用于检查信号在到达捕获沿之前的一段稳定时间(setup time),也就是确定从发射沿到捕获沿的过程是否足够快。

建立路径包括普通的数据到时钟的建立路径、数据到数据以及时钟门的路径。

如果最晚的一个发射沿到最早的一个捕获沿之间的时间满足时序要求(没有timing violation),才能确保这条建立路径都满足条件。

保持时间路径这种路径用于检查信号在到达捕获沿之后的一段稳定时间的(hold time),也就是确定从发射沿到捕获沿的时间是否太短。

包括普通的数据到时钟的建立路径、数据到数据以及时钟门的路径、异步信号同步化的检查。

为了正确的分析,我们检查保持路径时必须检查最早的一个发射沿到最晚的一个捕获沿之间的时间满足时序要求。

图1 建立/保持路径示意图如图1中发射部分由所有的时钟端口到触发器FF2的D端口之间的单元(包括U1、U 2、FF1、U4)和线组成;捕获部分由所有的时钟端口到触发器FF2 的时钟端口之间的单元(U1、U3、FF2)和线组成。

其中U1既属于建立路径又属于保持路径。

那么,建立路径就应该结合到FF2的D端口最慢的路径和到其时钟端口最快的路径来看。

保持路径则相反,我们应该找到达FF2D端口最快的路径和到其时钟端口最慢的路径。

对于Setup Time 验证来说:Slack=Required Time – Arrival Time对于Hold Time验证来说:Slack= Arrival Time –Required TimeSlack为正值,表示满足时序要求PT工作流程图2 PT工作流程图2为PT的工作流程,我们可以看出静态时序分析是一个反复进行的过程。

直到结果满足要求为止。

芯片在工作时所处的环境是不同的,然而环境的不同导致芯片内部的单元和线的延迟不同。

为了使芯片在大多数环境下都能正常工作,PT中提供了三种分析模式:single、bc_w c、on_chip_variation。

我们平时常用的是bc_wc模式,它把环境用工艺制程(process)、温度(temperature)、电压(voltage)分为以下3种情况:1、best case:工艺制程:1;理想温度零下40摄氏度;电压1 .32V(此芯片额定电压为1.2V)2、typical case:工艺制程:1;室温环境25摄氏度;电压1.2V3、worst case:工艺制程:1;125摄氏度;电压1.08v为了测试芯片在投片生产和封装整个制造过程是否出现物理等方面的缺陷导致功能不正确。

现在的超大规模集成电路的设计中,都加入了可测性设计(DFT:Design for Test)电路。

当芯片工作于测试模式时,时钟树的结构与功能模式完全不同。

我们必须在测试模式下也要分以上3种情况做静态时序分析。

3.静态时序分析与门级仿真的关系静态时序分析也有自己的弱点,它无法验证电路功能的正确性。

值得注意的是,静态时序分析只能有效地验证同步时序的正确性,大部分设计中可能包含地异步电路的时序验证,则必须通过门级仿真来保证其时序的正确性。

根据以上对静态时序分析的介绍,我们做门级仿真也应该分别仿真功能模式和测试模式下的best case、typical case、worst case三种情况,但是侧重点有所不同。

功能模式下,大部分电路我们只需要验证worst case和best case就可以认为是正确的,但是在我们芯片的设计中,曾经过出现worst case和best case通过而typical case仿真失败的情况。

这是因为有的电路中寄存器级数太多,时钟偏移(clock skew)对电路的影响造成的。

虽然这种情况即使在百万门级以上的设计中也很少见,但为了提高芯片成功率,对于关键路径,关键模块,需要仿真3中情况。

测试模式一般工作在室温环境,它的仿真我们只需要关心t ypical case就可以了。

静态时序分析工具无法验证异步时钟的电路。

然而现在芯片中可能存在异步时钟电路,如我们的TDS-CDMA数字基带处理芯片中,就有二十几个异步时钟域。

在PT中,所有异步时钟域的路径都必须被设为false_path(表示不关心该路径)。

由于RTL级功能仿真也不能发现异步时钟域之间信号的错误,我们在门级仿真时需要特别注意异步时钟域之间的信号的验证。

我们还可能遇到门级仿真失败,但是PT中并没有报错的情况。

经过反复试验分析,可能会有以下几种情况导致它们的结果不一致:1、VCS不支持负的输入输出路径延迟,但是PT是支持的。

当VCS遇到负输入输出路径延迟,它就自动认为它是0。

这样就导致了错误2、新版本的PT产生的SDF文件有关于信号沿的信息。

如果我们用老版本的库或存储器模型没有包含这种沿的信息,PT将会认为它是一条更长的路径。

而 VCS仍然用标准的延迟来计算,就导致结果不一致。

可见,一套完善的EDA工具很复杂,不同版本之间的细微差别也可能导致我们验证的失败。

3、最常见的原因是`timescale不同。

如果设计和SDF文件中所设的`timescale不同,那么SDF文件中的反标值可能被舍去。

这就导致了静态时序分析和动态仿真的不匹配。

所以,保证RTL代码、库文件、存储器模型、SDF文件中的`timescale一致非常重要。

门级仿真是芯片流片前的最后一道验证。

虽然能够很好的反映芯片工作的真实情况,但是资源占用严重、时间长。

只有综合利用动态验证和静态验证的优点,才能高效准确的完成一块芯片的设计。

4.TDS-CDMA数字基带处理芯片中的应用我们实验的对象TDS-CDMA数字基带处理芯片,是一块规模在1000万门以上,130n m工艺的超大规模集成电路,其中包含ARM、DSP等硬核。

在门级做全功能测试需要大量的人力物力资源,是很不现实的。

我们在实际芯片中设计中采用静态时序的分析加门级仿真的方法。

在芯片的设计过程中,我们在几个阶段做静态时序分析。

1)综合之后先做一次STA。

此时主要检查:1、电路设计的时序有没有问题。

如两个寄存器之间有过多的组合逻辑,使电路不能运行在需要的时钟频率上。

2、由于综合工具(设计中用Design Complier)的算法限制,每一次综合出的网表都不同。

需要反复做综合,直到网表的时序达到我们的期望。

用这一版网表再继续往下做。

因为没有具体的布局布线信息,此时的时序分析建立在线上负载模型(wire load mod el)上。

线上负载模型是一种比较悲观的模型,所以可能出现一些不是很严重的Violation。

现阶段我们不需要关心这些,它们可以在布局布线时得到解决。

2)预布局之后:这时候,元件的大概位置关系已经确定。

可以通过静态时序分析来解决布局中不合理的地方,以便修改。

3)布局布线完成后布局布线后可以从版图中提取精确的器件和网络延迟得到SPEF (Standard Parasitic Exchange Format ) 文件,反标到Prime Time SI中再做一次时序分析,这时可以得到基于版图的精确的时序分析结果。

布局布线的过程中,需要不停的用STA来分析布局布线的结果。

我们的芯片采用SMI C提供的0.13微米工艺的元件库。

他们提供了标准元件库和HVT元件库两种。

HVT元件的特点是漏电低,但是延时比较大。

所以,刚开始的时候我们用HVT元件,做STA之后发现有的路径不能满足时序要求。

我们再用一些标准元件来替代这些HVT元件,反复不停比较,直到所有路径都满足时序要求为止。

这样,既最大程度的实现了低功耗,也满足了时序要求。

在完成时序分析之后,用PT SI生成SDF(standard delay format)文件反标到网表中做门级仿真。

此时的SDF文件不仅包含单元延迟和线延迟,也包含了版图信息,串扰信息等。

门级仿真可以得到最真实,最接近实际情况的结果。

5.结束语静态时序分析以它运行速度很快、占用内存较少,可以对芯片设计进行全面的时序功能检查,并利用时序分析的结果来优化设计等优点,很快地被用到数字集成电路设计的验证中。

然而门级仿真也由于它不可取代的地位在ASIC设计中仍有一席之地。

结合在TDS-CDMA 数字基带处理芯片设计中的经验,我们可以得出这样的结论:静态时序分析和门级时序仿真是从不同的侧重点来分析电路以保证电路的时序正确,它们是相辅相成的。

现在,实验中的TDS-CDMA数字基带处理芯片已经成功流片。

本文作者创新点:在实践中寻找到一种STA和门级仿真结合的新方法。