ChipScope Pro实例教程

chipscope例程

ChipScope例程ISE13.1简介FPGA的在线调试,一般是在FPGA中嵌入一个类似于逻辑分析仪的模块,在满足触发条件时,对需观测的信号进行采集,并通过JTAG线缆将存储的波形上传至计算机,供调试人员检查。

Xilinx在线调试工具为ChipScope,Altera为SignalTap。

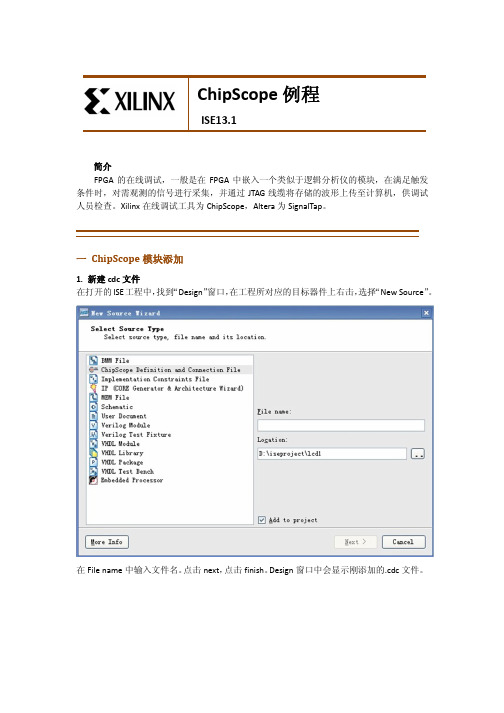

一ChipScope模块添加1. 新建cdc文件在打开的ISE工程中,找到“Design”窗口,在工程所对应的目标器件上右击,选择“New Source”。

在File name中输入文件名。

点击next,点击finish。

Design窗口中会显示刚添加的.cdc文件。

双击*.cdc。

进入编辑界面。

在新的界面中点击next。

在上图所示的界面中,选中“Trigger Parameters”窗口,然后在“Number of Input Ports”后面的下拉列表中选择触发通道的个数。

简单起见这里设为1。

在TRIG0对应的选项中选择位宽(Trigger Width)及触发类型(Match Type)。

点击“Next”,或是中“Capture Parameters”窗口。

在上图中,勾选需要用到的Trigger Port,设置采样深度。

点击“Next”,或是中“Net Connections”窗口。

为clock通道和Trigger通道指定网络标号。

在上图中双击CLOCK PORT。

在“Net Name”对应的列表中找到待指定的信号,也可以在Pattern中输入*clk*,点击Fitter 找到clk信号,选中该信号,然后点击右侧的“make connections”按钮,则该信号便与时钟通道对应起来。

点击OK。

添加成功后会在Net Connection中显示。

双击Trigger Ports。

用相同的方法添加信号。

注意右上角的Net Selection这时要选中Trigger/Data Signals。

所有通道的信号均定完成之后,点击菜单栏的“File”->“Save”,或是在工具栏找到快捷图标,单击保存cdc文件,然后关闭此窗口。

Xilinx ISE 13 笔记06 Chipscope Pro调试工具

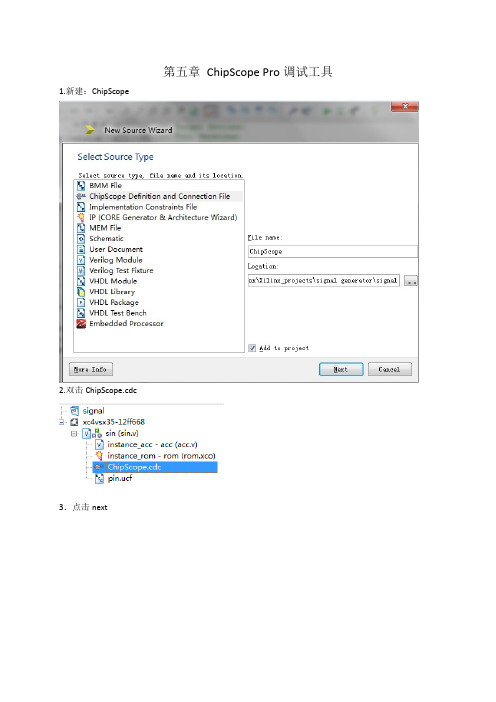

第五章ChipScope Pro调试工具1.新建:ChipScope

2.双击ChipScope.cdc

3.点击next

4.点next

5.设置相应参数,并且next

6.设置,next

7.单击“Modify Connection”,弹出”Select Net”配置界面

8.Make Connections

9,配置完成后,保存退出,然后双击Analyze Design Using ChipScope

10.出现如下界面

11.点击,初始化边界扫描链。

12.右击DEV:1 MyDevice 1(XC4VSX36)---Configure. 注意,重新配置ChipScope的时候一定再执行

或者单击菜单栏“Device”菜单下的选项进行设置,只有当JTAG链扫描正确后,菜单项Device才能由灰色变为正常。

点击OK,Analyzer的右下角会给出配置状态,配置成功后显示“Done”标志。

配置Trigger,设置触发信号值

配置Waveform,将各个比特位汇成总线的方式

按住shift键,依次点击DataPort[0]和DataPort[15],将0~15全部选中,右击Move to BUS。

配置完成后,单击工具栏。

OVER。

片内逻辑分析仪工具——ChipScopePro

第11章片内逻辑分析仪工具——ChipScope Pro11.1 ChipScope Pro工具介绍在FPGA调试阶段,传统的信号分析手段要求在设计时保留一定数量的FPGA管脚作为测试管脚,这种方法灵活性差,对PCB布线也有一定的影响。

当今先进的FPGA器件所具有的规模、速度和板级要求使得利用传统逻辑分析方法来调试采用FPGA器件进行的设计几乎是不可能的。

Xilinx公司推出的片内逻辑分析仪ChipScope Pro能够通过JTAG口,实时地读出FPGA的所有内部信号,而只需要片内的少量BlockRAM和逻辑资源,使得逻辑分析灵活方便。

ChipScope Pro是与ISE配套使用的,其版本经过了ChipScope 4.1i,ChipScope 4.2i,ChipScope Pro 5.1i,ChipScope Pro 5.2i和ChipScope Pro 6.1i的升级过程,ChipScope Pro 6.1i是与ISE 6.1配套使用的最新版本。

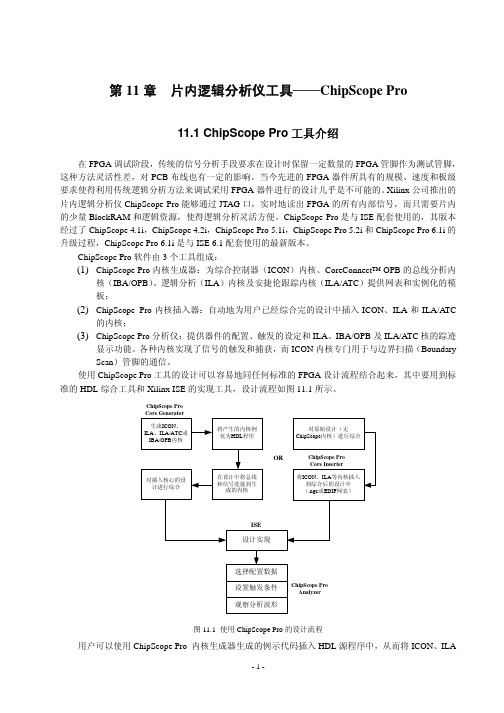

ChipScope Pro软件由3个工具组成:(1) ChipScope Pro内核生成器:为综合控制器(ICON)内核、CoreConnect™ OPB的总线分析内核(IBA/OPB)、逻辑分析(ILA)内核及安捷伦跟踪内核(ILA/ATC)提供网表和实例化的模板;(2) ChipScope Pro内核插入器:自动地为用户已经综合完的设计中插入ICON、ILA和ILA/ATC的内核;(3) ChipScope Pro分析仪:提供器件的配置、触发的设定和ILA、IBA/OPB及ILA/ATC核的踪迹显示功能。

各种内核实现了信号的触发和捕获,而ICON内核专门用于与边界扫描(Boundary Scan)管脚的通信。

使用ChipScope Pro工具的设计可以容易地同任何标准的FPGA设计流程结合起来,其中要用到标准的HDL综合工具和Xilinx ISE的实现工具,设计流程如图11.1所示。

FPGA设计开发软件ISE使用技巧之:片上逻辑分析仪(ChipScope Pro)使用技巧

FPGA设计开发软件ISE使用技巧之:片上逻辑分析仪(ChipScope Pro)使用技巧6.7 片上规律分析仪(ChipScope Pro)用法技巧在的调试阶段,传统的办法在设计FPGA的板时,保留一定数量的FPGA 管脚作为测试管脚。

在调试的时候将要测试的信号引到测试管脚,用规律分析仪观看内部信号。

这种办法存在无数弊端:一是规律分析仪价格昂扬,每个公司拥有的数量有限,在研发期间往往供不应求,影响进度;二是PCB布线后测试脚的数量就确定了,不能灵便地增强,当测试脚不够用时会影响测试,测试管脚太多又影响PCB布局布线。

ChipScope Pro是ISE下一款功能强大的在线调试工具。

面向这些问题,ChipScope Pro都可以有效地解决。

6.7.1 ChipScope Pro概述ChipScope Pro是针对 Virtex-II pro/ Virtex/ Virtex-II/ Virtex-EM/ Spartan-IIE/ Spartan-IIE 系列FPGA的在线片内信号分析工具。

它的主要功能是通过JTAG口,在线实时读取FPGA的内部信号。

ChipScope Pro的基本原理是利用FPGA中未用法的BlockRam,按照用户设定的触发条件将信号实时地保存到这些BlockRam中,然后通过JTAG口传送到计算机,最后在计算机屏幕上显示出时序波形。

ChipScope Pro应用的框图6.34所示。

图6.34 ChipScope Pro应用框图其中ILA、ICON是为了用法ChipScope Pro观看信号而插入的核。

ChipScope Pro工作时普通需要用户设计中实例化两种核:一是集成规律分析仪核(ILA core,Integrate Logic Analyzer core),该核主第1页共11页。

Chipscope实例教程

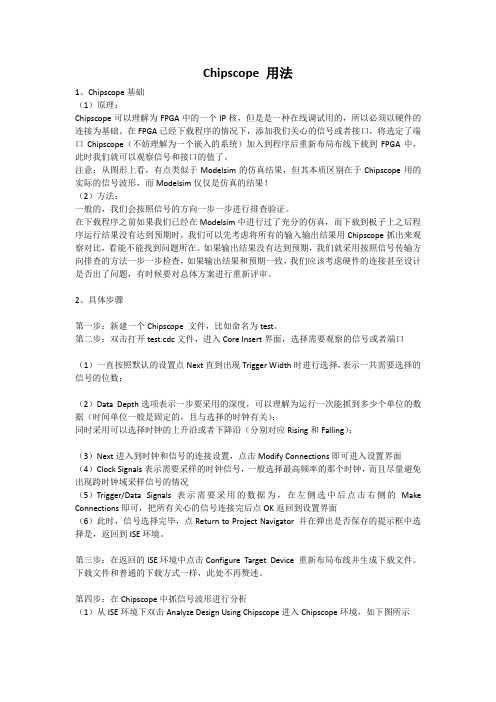

Chipscope 用法1、Chipscope基础(1)原理:Chipscope可以理解为FPGA中的一个IP核,但是是一种在线调试用的,所以必须以硬件的连接为基础。

在FPGA已经下载程序的情况下,添加我们关心的信号或者接口,将选定了端口Chipscope(不妨理解为一个嵌入的系统)加入到程序后重新布局布线下载到FPGA中,此时我们就可以观察信号和接口的值了。

注意:从图形上看,有点类似于Modelsim的仿真结果,但其本质区别在于Chipscope用的实际的信号波形,而Modelsim仅仅是仿真的结果!(2)方法:一般的,我们会按照信号的方向一步一步进行排查验证。

在下载程序之前如果我们已经在Modelsim中进行过了充分的仿真,而下载到板子上之后程序运行结果没有达到预期时,我们可以先考虑将所有的输入输出结果用Chipscope抓出来观察对比,看能不能找到问题所在。

如果输出结果没有达到预期,我们就采用按照信号传输方向排查的方法一步一步检查,如果输出结果和预期一致,我们应该考虑硬件的连接甚至设计是否出了问题,有时候要对总体方案进行重新评审。

2、具体步骤第一步:新建一个Chipscope 文件,比如命名为test。

第二步:双击打开test.cdc文件,进入Core Insert界面,选择需要观察的信号或者端口(1)一直按照默认的设置点Next直到出现Trigger Width时进行选择,表示一共需要选择的信号的位数;(2)Data Depth选项表示一步要采用的深度,可以理解为运行一次能抓到多少个单位的数据(时间单位一般是固定的,且与选择的时钟有关);同时采用可以选择时钟的上升沿或者下降沿(分别对应Rising和Falling);(3)Next进入到时钟和信号的连接设置,点击Modify Connections即可进入设置界面(4)Clock Signals表示需要采样的时钟信号,一般选择最高频率的那个时钟,而且尽量避免出现跨时钟域采样信号的情况(5)Trigger/Data Signals表示需要采用的数据为,在左侧选中后点击右侧的Make Connections即可,把所有关心的信号连接完后点OK返回到设置界面(6)此时,信号选择完毕,点Return to Project Navigator 并在弹出是否保存的提示框中选择是,返回到ISE环境。

Chipscope教程

Xilinx的Chipscope类似于Altera的Signaltap。

下面记录一下Chipscope的使用方法。

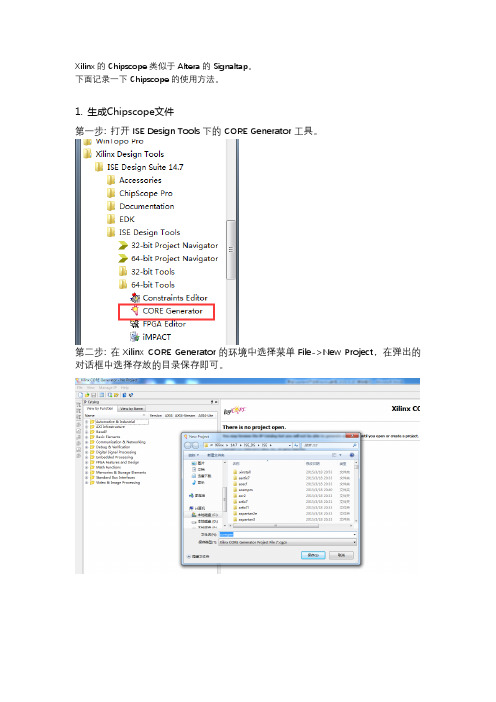

1. 生成Chipscope文件第一步: 打开ISE Design Tools下的CORE Generator工具。

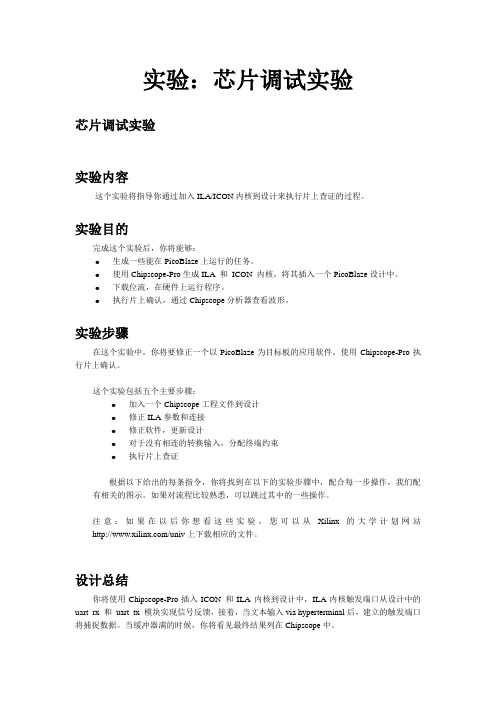

第二步: 在Xilinx CORE Generator的环境中选择菜单File->New Project,在弹出的对话框中选择存放的目录保存即可。

设置如下。

些,呵呵!选完后Apply一下OK关闭。

第五步: 双击IP Catalog窗口的Debug&Verification下的ICON(chipscope Pro –integrated Controller) 。

第六步: 在弹出的窗口中点击Generate就可以了。

第七步: ICON生成完成后,再双击IP Catalog窗口的Debug&Verification下的ILA(Chipscope Pro –Integrate Logic Analyzer)。

第八步: 在ILA的配置可以根据自己的需要来选择,我们这里不强求,我们这里选择一个触发Group,选择数据的采样深度为2048,就是一次采样2048个点,这个深度当然越大越好,但FPGA资源有限啊!设置完后点击Next。

也会用到Chipscope, 这样程序中基本上的信号都能观察了。

设置完后再Generate。

第十步: 这样我们所需的Chipscope文件都已经生成好了,我们可以在eeprom_test 的目录下看到生成的文件,特别要注意下图中我用红色圈出来的文件,如果在其它的工程中我们需要使用Chipscope的话,只要把这四个文件拷过去就好了,不要费老大力气的再重新生成一边。

接下来是Analyzer:点击Open cable按钮建立JTAG连接。

如果开发板和JTAG连接正常的话,Chipscope能找到开发板使用的FPGA芯片。

点击OK把Data Port里的CH0 ~CH7组合成一个组,方法是按Ctrl键,再选择Data port 里的CH0~CH7, 点击右键,选择Move to Bus->New Bus。

FPGA设计开发软件ISE使用技巧之:片上逻辑分析仪(ChipScope Pro)使用技巧

FPGA 设计开发软件ISE 使用技巧之:片上逻辑分析仪(ChipScope Pro)使用技巧6.7 片上逻辑分析仪(ChipScope Pro)使用技巧在FPGA 的调试阶段,传统的方法在设计FPGA 的PCB 板时,保留一定数量的FPGA 管脚作为测试管脚。

在调试的时候将要测试的信号引到测试管脚,用逻辑分析仪观察内部信号。

这种方法存在很多弊端:一是逻辑分析仪价格高昂,每个公司拥有的数量有限,在研发期间往往供不应求,影响进度;二是PCB 布线后测试脚的数量就确定了,不能灵活地增加,当测试脚不够用时会影响测试,测试管脚太多又影响PCB 布局布线。

ChipScope Pro 是ISE 下一款功能强大的在线调试工具。

面对这些问题,ChipScope Pro 都可以有效地解决。

6.7.1 ChipScope Pro 概述ChipScope Pro 是针对Xilinx Virtex-II pro/ Virtex/ Virtex-II/ Virtex-EM/ Spartan-IIE/ Spartan-IIE 系列FPGA 的在线片内信号分析工具。

它的主要功能是通过JTAG 口,在线实时读取FPGA 的内部信号。

ChipScope Pro 的基本原理是利用FPGA 中未使用的BlockRam,根据用户设定的触发条件将信号实时地保存到这些BlockRam 中,然后通过JTAG 口传送到计算机,最后在计算机屏幕上显示出时序波形。

ChipScope Pro 应用的框其中ILA、ICON 是为了使用ChipScope Pro 观察信号而插入的核。

ChipScope Pro 工作时一般需要用户设计中实例化两种核:一是集成逻辑分析仪核(ILA core,Integrate Logic Analyzer core),该核主要用于提供触发和捕获的功。

实验【chipscope使用】:芯片调试实验

实验:芯片调试实验芯片调试实验实验内容这个实验将指导你通过加入ILA/ICON内核到设计来执行片上查证的过程。

实验目的完成这个实验后,你将能够:●生成一些能在PicoBlaze上运行的任务。

●使用Chipscope-Pro生成ILA 和ICON 内核,将其插入一个PicoBlaze设计中。

●下载位流,在硬件上运行程序。

●执行片上确认,通过Chipscope分析器查看波形。

实验步骤在这个实验中,你将要修正一个以PicoBlaze为目标板的应用软件,使用Chipscope-Pro执行片上确认。

这个实验包括五个主要步骤:●加入一个Chipscope工程文件到设计●修正ILA参数和连接●修正软件,更新设计●对于没有相连的转换输入,分配终端约束●执行片上查证根据以下给出的每条指令,你将找到在以下的实验步骤中,配合每一步操作,我们配有相关的图示。

如果对流程比较熟悉,可以跳过其中的一些操作。

注意:如果在以后你想看这些实验,您可以从Xilinx的大学计划网站/univ上下载相应的文件。

设计总结你将使用Chipscope-Pro插入ICON 和ILA 内核到设计中,ILA内核触发端口从设计中的uar t_rx 和uart_tx 模块实现信号反馈,接着,当文本输入via hyperterminal后,建立的触发端口将捕捉数据。

当缓冲器满的时候,你将看见最终结果列在Chipscope中。

产生一个新的Chipscope-Pro工程步骤1启动ISE™ Project Navigator,打开工程文件。

1.打开Xilinx ISE软件,选择Start → Programs → Xilinx ISE 8.2i → Project Navigator2.选择File → Open ProjectVerilog users: Browse to c:\xup\fpgaflowlabs\verilog\lab4VHDL users: Browse to c: \xup\fpgaflow\labs\vhdl\lab43. 选择chipscope.ise点击Open通过Project Navigator生成一个新的Chipscope-Pro工程1.在Project Navigator中选择Project New Source,打开新的源文件对话框,点击ChipscopeDefinition and Connection,命名为loopback_c s.点击<Next>继续2. 选择loopback作为源文件,点击<next>,然后点击<finish>,一个Chipscope-Pro源文件将被增加到Sources in Project窗口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ChipScope Pro实例教程宋存杰1. ChipScope Pro简介ChipScope Pro的主要功能是通过JTAG口、在线实时地读出FPGA的内部信号。

基本原理是利用FPGA中未使用的BlockRAM,根据用户设定的触发条件将信号实时地保存到这些BlockRAM中,然后通过JTAG口传送到PC机,显示出时序波形。

一般来说,ChipScope Pro在工作时需要在用户设计中实例化两种核:一是集成逻辑分析仪核(ILA core,Integrated Logic Analyzer core),提供触发和跟踪捕获的功能;二是集成控制器核(ICON core,Integrated Controller core),负责ILA核和边界扫描端口的通信,一个ICON核可以连接1~15个ILA核。

ChipScope Pro工具箱包含3个工具:ChipScope Pro Core Generator(核生成器)、ChipScope Pro Core Inserter(核插入器)和ChipScope Pro Analyzer(分析器)。

ChipScope Pro Core Generator的作用是根据设定条件生成在线逻辑分析仪的IP核,包括ICON核、ILA核、ILA/ATC2核和IBA/OPB核等,设计人员在原HDL代码中实例化这些核,然后进行布局布线、下载配置文件,就可以利用ChipScope Pro Analyzer设定触发条件、观察信号波形。

ChipScope Pro Core Inserter除了不能生成IBA/OPB核和ILA/ATC2核以外,功能与ChipScope Pro Core Generator类似,可以生成ICON核和ILA核,但是它能自动完成在设计网表中插入这些核的工作,不用手工在HDL代码中实例化,在实际工作中用得最多。

下图为ChipScope的两种使用流程图,左侧为使用ChipScope Pro Core Generator流程。

右侧为使用ChipScope Pro Core Inserter的流程。

两种方法各有优缺点,但由于ChipScope Pro Core Inserter更方便一些,可以较好地满足大多数调试要求,建议优先掌握。

本次练习中,第3、4两章主要描述了ChipScope Pro Core Inserter的流程。

第5章简要描述了使用ChipScope Pro Core Generator的流程。

附录中位实验例程的源代码。

2. 创建简单的ISE工程2.1 新建工程ISE启动Xilinx-ISE。

新建Project。

File -> New Project。

填入工程的名字以及所在路径。

Next。

选择工程所对应的开发板的器件类型。

Next。

创建源文件窗口。

因为我们已有了源文件,所以这里直接点击Next。

添加已有的源文件到工程中。

选择源文件led.v与led_top.v,打开。

由于事先已经把两个源文件都放到了工程目录下,所以不用选择Copy to Project,Next。

直接点击Finish,完成工程的创建。

选择默认的Synthesis/Imp + Simulation即可。

OK。

2.2 绑定管脚在Processes区域中,选择User Constraints下面的Assign Package Pins,右键点击Run。

绑定管脚的约束,需要建立UCF文件,点击Yes。

与switch[0]L13相连,led的输出信号diode与开发板上8个led灯相连。

Ctrl+S,保存,在弹出框中选择XST Defalut即可,OK。

然后关闭Xilinx PACE软件。

2.3 综合在Processes区域中,选择Synthesize – XST,右键点击Run。

综合完成后,Synthesize –XST前面会出现绿色的对勾。

表示综合完成且没有任何错误和警告。

2.4 实现在Processes区域中,选择Implement Design,右键点击Run。

连续执行翻译Translate、映射Map、布局布线Place & Route工作。

2.5 产生编程文件在Processes区域中,选择Generate Programming File,右键点击Run。

2.6 下载编程文件在Processes区域中,选择Generate Programming File下面的Configure Device(iMPACT),右键点击Run。

打开iMPACT软件。

选择使用JTAG扫描链配置设备。

为FPGA芯片选择编程文件led_top.bit。

启动时钟切换为JtagClk。

另外两个直接点击Cancel即可。

同上。

右键点击FPGA芯片图标,选择编程Program。

点击OK。

下载成功。

可以看到开发板上的LED灯开始流动点亮。

3. 配置ChipScope Pro Core Inserter3.1 添加ChipScope Core Inserter工程文件选择ChipScope Definition and Connection File,设置文件名称。

选择需要观察内部信号的源文件。

工程中出现led.cdc文件。

打开led.cdc文件在ISE中启动Core Inserter,网表的输入输出目录是ISE自动设置的,且其参数只能在ISE中改变,不能在Core Inserter中修改。

3.4 配置ICON核ICON核是所有核和JTAG扫描电路的通信控制器,因此首先对其进行说明,如下图所示,要指定是否禁止在JTAG时钟上插入BUFG。

如果选中此项,JTAG时钟将使用普通布线资源,而不是全局时钟布线,这样会在JTAG时钟线上产生较大的布线延时差别,因此,在全局时钟资源足够的情况下,应该尽量使JTAG时钟使用BUFG资源。

这里不选中此项,使用BUFG资源。

3.5 配置ILA核ILA核的配置分为3个部分:触发参数、捕获参数、网线连接。

Trigger Parameters选项卡用于设置触发输入信号和触发条件判断单元。

Number of Input Trigger Ports下拉列表中可以选择ILA核输入触发端口的数目。

每个ILA核最多可以有16个输入触发端口。

每个触发端口都有位宽(触发端口的信号线总数)、触发条件判断单元的类型和数目等。

Capture Parameters选项卡用于对存储深度、数据位宽、采样时刻等参数的设置。

ChipScope存储缓冲区所能够存储的最大采样值个数成为存储深度,与数据宽度共同决定了Block RAM的占用数。

如果选中Data Same As Trigger选项,则数据与触发信号相同,这是一种很常用的模式,可以捕获和采集触发逻辑分析仪的任何数据。

在这种模式下,ILA核省略了数据输入端口,可以减小CLB和布线资源的占用,但总的数据宽度不能大于256bit。

不选中Data Same As Trigger选项时,数据和触发信号完全独立,当采样的数据位宽小于触发宽度时,能减少采集的数据,节省Block RAM资源。

在本次练习中,我们选择Data Same As Trigger这种常用模式,存储深度选择8192,在时钟上升沿采样。

完成捕获参数的设置后,Core Inserter能够根据相应配置准确给出Block RAM的个数,如下图左侧中Core Utilization框所示。

Net Connections选项卡用于将在线逻辑分析仪的输入信号和设计中的网线连接起来。

由于目前尚未建立连接,所以Net Connections中的所有信号都为红色显示。

点击ModifyConnection,会弹出Select Net配置界面。

利用Select Net对话框,可以把ChipScope的工作时钟、触发信号、数据信号与设计中的网线连接起来,方法是在右侧选中ChipScope的信号,在左侧下方选中需要连接的网线,单击Make Connections按钮,即可完成一条信号线的连接。

所有信号都连接好之后,单击Ok按钮。

需要注意的是,ChipScope Pro只能分析FPGA设计的内部信号,因此不能直接连接输入信号的网表,所以输入信号网表全部以灰色显示。

如果要采样输入信号,可通过连接其输入缓冲信号来实现,时钟信号选择相应的BUFGP,普通信号选择相应的IBUF。

在本次练习中,我们将led设计中的count[16]选择为采样时钟,而没有选择led设计本身的时钟信号clock。

这是因为我们在设计中使用了25位宽的计数器,计数满一次之后,led 灯才移动一次。

由于采样深度只有8192,如果使用clock来采样,只能采样8192个时钟周期,这明显是不够的。

根据测算,我们选择count[16]为采样时钟,在8192次采样后,能采样到led循环4次。

触发和数据端口与设计中的diode输出信号相连。

端口名字为黑色,否则为红色。

最后,返回工程中。

4. 启动ChipScope Pro Analyzer4.1 重新运行Implement DesignChipScope Core Inserter产生的网表要被插入到原来的设计网表中,需要重新实现设计Implement Design,完成翻译、映射、布局布线后生成BIT文件,下载到FPGA中后,利用ChipScope Pro Analyzer分析信号波形。

以后每次通过Core Inserter修改网表之后,都需要重新运行Implement Design,重新生成编程文件。

4.2 重新生成编程文件选择Analyze Design Using ChipScope,右键点击Run。

ChipScope Pro Analyzer启动后,界面如下图所示。

4.4 配置目标芯片在常用工具栏上点击图标,初始化边界扫描链,成功完成扫描后,项目浏览器将会列出JTAG链上的器件。

选择我们使用的开发板FPGA芯片型号XC3S500E。

点击“DEV:0 MyDevice0(XC3S500E)-> Configure”进行配置。

在弹出的配置对话框中,选择需要下载的.bit文件。

需要注意的是:ChipScope利用JTAG 链来观察芯片内部逻辑,因此在生成配置文件时只能利用.bit格式的配置文件,且时钟选择“JTAG CLK”,选择“CCLK”可能会配置失败。

4.5 设置触发条件把ChipScope 设计和工程下载到FPGA 中以后,还需要设定触发条件才能在Analyzer 中捕获到有效波形。

Analyzer 的触发设置由Match (匹配)、Trig (触发)以及Capture (捕获)三部分。

其中Match 用于设置匹配函数,Trig 用于把一个或多个触发条件组合起来构成最终的触发条件,Capture 用于设定窗口的数目和触发位置,双击Trigger Setup ,典型的配置界面如下图所示。