四川大学数字逻辑期末考题精选答案

《数字逻辑》期末考试A卷参考答案

《数字逻辑》期末考试 A 卷参考答案、判断题:下面描述正确的打’/,错误的打‘X’(每小题1分,共10 分)1、为了表示104个信息,需7位二进制编码[V ]2、BCD码能表示0至15之间的任意整数[X ]3、余3码是有权码[X ]4、2421码是无权码[X ]5、二值数字逻辑中变量只能取值6、计算机主机与鼠标是并行通信7、计算机主机与键盘是串行通信8、占空比等于脉冲宽度除于周期0和1,且表示数的大小[X ][X ][V ][V ]9、上升时间和下降时间越长,器件速度越慢[V ]10、卡诺图可用来化简任意个变量的逻辑表达式[X ]、写出图中电路的逻辑函数表达式。

(每小题5分,共10分)1、F=A B2、F= AB CD2分,共20分)1、在图示电路中.能实现逻辑功能F = ATH 的电路是 A °TTL 电路(A) F = ABCD(B) F = AH ・ CD -(C) F= A + B + C + D(D) F = A + B • C + D (E) F= A BCD4 . 己知F 二ABC + CD ■可以肯定使F = 0的情况是 _°(A) A=0, BC= 1; (B) B= 1 , C= 1 } (C) AB= 1, CD=Q.(D) BC= 1 , D= 15、逻辑函数A B+BCD+A C+ B C 可化简为A,B,C,D 。

(A) AB + AC + BC (B) AB + C (A4-B)(C) AB + CABA — O ?=11 QA |— I1 F •-&1 Q AB L Il —(B)悬0----空。

—A — &Bo —Co- &BA3 •满足如图所示电路的输岀函数F 的表达式为丄3B 1 o — VOF(D) AB +C (E) 19.图示电路中,当各触发器的状态为C 时.再输入一个CP 脉冲,融发器的 状态为QiQ 严0 0。

2021-2022学年数字逻辑与数字系统期末试卷(B卷)

2021—2022学年春季学期

课程名称:数字逻辑与数字系统

一.(10分)逻辑电路如图1-1所示。

试回答如下问题: (1) 在图1-1中的74161实现的是几进制计数器? (2) 已知输入波形CP ,Q 2Q 1Q 0初始值为000,

在图1-2中画出Q 2、Q 1、Q 0、以及输出F 波形; (3) 说明图1-1逻辑电路的功能?

F

图1-1

图1-2

二.(8分)逻辑电路的状态转换图如图2所示。

试回答如下问题: (1) 说明该电路的功能;

(2) 用74160和必要的逻辑门实现该电路。

图2

三.(15分)逻辑电路的状态转换图如图3所示。

试回答如下问题:

(1)说明该电路的功能;

(2)用3个上升沿有效的D触发器和必要的逻辑门实现该电路,要求写出状态方

程、输出方程和驱动方程,判断能否自启动。

图3

四.(15分)时序逻辑电路如图4所示,写出驱动方程、输出方程,状态方程,列状态转换表,画出状态转换图,说明电路功能。

X

图4

五.(13分)逻辑电路的状态转换图如图5-1所示,其中X为输入,Z为输出,Q2Q1Q0为状态。

试回答如下问题:

(1)说明该电路的功能;

(2)根据图5-1状态转换图,以及给出的Verilog源程序,填写图5-2中a1~a10、

b1~b2、c1~c3的Verilog源程序;

(3)已知输入波形,如图5-3所示,画出Q2、Q1、Q0、Z波形。

图5-1

图5-2

图5-3

六.(9分)时序逻辑电路如图6所示,X为输入,F为输出;写出输出方程,状态方程,列状态转换表,画出状态转换图,说明逻辑电路功能。

图6。

数字逻辑试卷及答案

数字逻辑试卷及答案0(共5页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--《数字电路与逻辑设计》模拟试卷1试题卷注意:1.试卷保密,考生不得将试卷带出考场或撕页,否则成绩作废。

请监考老师负责监督。

2.请各位考生注意考试纪律,考试作弊全部成绩以零分计算。

3.本试卷满分100分,答题时间为90分钟。

4.本试卷分为试题卷和答题卷,所有答案必须答在答题卷上,答在试题卷上不给分。

一、单项选择题(本大题共10小题,每小题2分,共20分)在每小题列出的四个选项中只有一个选项是符合题目要求的,请将正确选项前的字母填在答题卷相应题号处。

1. 下列四个数中,最大的数是 。

[A] (AF)16 [B] (0010)8421BCD[C] ()2 [D] (198)104. 对于钟控RS 触发器,若要求其输出“0”状态不变,则输入的RS 信号应为 。

[A] 2 [B] 8 [C] 16 [[A] OC 门[B] PMOS [C] NMOS [D] CMOS[A] RS=X0[B] RS=0X[C] RS=X1[D] RS=1X5. 以下各电路中,可以产生脉冲定时。

[A] 多谐振荡器[B] 单稳态触发器[C] 施密特触发器[D] 石英晶体多谐振荡器[A] 变量译码器[B] 加法器[C] 数码寄存器[D] 数据选择器7. 同步时序电路和异步时序电路比较,其差异在于后者。

[A] 没有触发器[B] 没有统一的时钟脉冲控制[C] 没有稳定状态[D] 输出只与内部状态有关[A] 触发器[B] 晶体管[C] MOS管[D] 电容9. 当用异步I/O输出结构的PAL设计逻辑电路时,它们相当于。

[A] 组合逻辑电路[B] 时序逻辑电路[C] 存储器[D] 数模转换器[A] 2[B] 4[C] 8[D] 32二、多项选择题(本大题共5小题,每小题3分,共15分)在每小题列出的四个选项中有二至四个选项是符合题目要求的,请将正确选项前的字母填在答题卷相应题号处。

数字逻辑试卷及答案

计算机学院 第二学期《数字逻辑》 期未考试试卷 A 卷学号 班级 姓名 成绩一、填空(每空1分,共14分)1、(21.5)10=( )2=( )8=( )162、若0.1101x =-,则[]x 补=( )3、十进制数809对应的8421BCD 码是( )4、若采用奇校验,当信息位为10011时,校验位应是( )5、数字逻辑电路分为( )和( )两大类6、电平异步时序逻辑电路的描述工具有( )、( )、( )7、函数()()F A B C D =+⋅+的反函数是( )8、与非门扇出系数N O 的含义是( )9、若要消除函数(,,)F A B C AB AC =+对应的逻辑电路可能存在的险象,则应增加的冗余项是( )二、选择题(每空2分,共16分)从下列各题的四个答案中,选出一个正确答案,并将其代号填入括号内1、数字系统采用( )可以将减法运算转化为加法运算A .原码B .余3码C .Gray 码D .补码2、欲使J-K 触发器在CP 脉冲作用下的次态与现态相反,JK 的取值应为( ) A .00 B .01 C .10 D .113、对完全确定原始状态表中的6个状态,A 、B 、C 、D 、E 、F 进行比简,若有(A ,B ),(D 、E )等效,则最简状态表中只有( )个状态A .2B .4C .5D .6 4、下列集成电路芯片中,( )属于组合逻辑电路 A .计数器74290 B .寄存器74194 C .三一八译码器74138 D .集成定时器5G555 5、设计一个20进制同步计数器,至少需要( )个触发器 A .4 B .5 C .6 D .20 6、用5G555构成的多谐振荡器有( )A .两个稳态B .两个暂稳态C .一个稳态,一个暂稳态D .既没有稳态,也没有暂稳态 7、可编程逻辑阵列PLA 的与、或陈列是( )A .与阵列可编程、或阵列可编程B .与阵列不可编程、或阵列可编程C .与阵列可编程、或阵列不可编程D .与阵列不可编程、或阵列不可编程 8、最大项和最小项的关系是( )A .i i m M =B .i i m M =C .1i i m M ⋅=D .无关系 三、逻辑函数化简(6分)把(,,,)(0,1,5,14,15)(4,7,10,11,12)F A B C D m d =∑+∑化成最简与—或式 四、分析题(每小题12分,共24分)1、分析图1所示组合逻辑电路① 写出输出函数表达式 ② 列出真值表 ③ 说明电路功能2、分析图2所示脉冲异步时序逻辑电路① 写出输出函数和激励函数表达式 ② 列出次态真值表,作出状态表和状态图 ③ 说明电路功能④ 设初态2100y y =,作出x 输入4个异步脉冲后的状态y 2y 1和输出z 的波形图。

数字电路与数字逻辑(0202182) 期末考试复习题及参考答案

A、有10根输入线,4根输出线 B、有16根输入线,4根输出线 C、有4根输入线,16根输出线 D、有4根输入线,10根输出线

答案:A

11.4位倒T型电阻网络DAC的电阻网络的电阻取值有()种。

A、与非门 B、三态输出门 C、集电极开路门 D、漏极开路门

答案:CD

16.以下代码中为恒权码的为()。

A、8422BCD码 B、5422BCD码 C、余三码 D、格雷码

答案:AB

17.一个容量为1K×8的存储器有()个存储单元。

A、8 B、8K C、8000 D、8192

答案:BD

一、单项选择题 1.半加器的逻辑功能是()

A、两个同位的二进制数相加 B、两个二进制数相加 C、两个同位的二进制数及来自低位的进位三者相加 D、两个二进制数的和的一半

答案:A

2.把一个五进制计数器与一个四进制计数器串联可得到()进制计数器。

A、4 B、5 C、9 D、20

答案:D

3.实现单输入、多输出逻辑函数,应选()

答案:CD

11.与八进制数(47.3)8等值的数为:()。

A、(100111.011)2 B、(27.6)16 C、(27.3)16 D、(100111.11)2

答案:AB

12.组合逻辑电路消除竞争冒险的方法有()。

A、修改逻辑设计

B、在输出端接入滤波电容 C、后级加缓冲电路 D、屏蔽输入信号的尖峰干扰

A、编码器 B、译码器 C、数据选择器 D、数据分配器

答案:D

4.数字电路中的三极管工作在()。

A、饱和区 B、截止区 C、饱和区或截止区 D、放大区

答案:C

5.实现多输入、单输出逻辑函数,应选()

《数字逻辑》期末考试A卷参考答案

《数字逻辑》期末考试 A 卷参考答案

一、判断题:下面描述正确的打‘√’,错误的打‘×’ (每小题1 分,共 10 分)

1、为了表示 104 个信息,需 7位二进制编码 [√ ]

2、 BCD码能表示0 至 15 之间的任意整数[× ]

3、余 3码是有权码[× ]

4、 2421 码是无权码 [ × ]

5、二值数字逻辑中变量只能取值0 和 1,且表示数的大小 [ × ]

6、计算机主机与鼠标是并行通信[× ]

7、计算机主机与键盘是串行通信[√ ]

8、占空比等于脉冲宽度除于周期[√ ]

9、上升时间和下降时间越长,器件速度越慢

10、卡诺图可用来化简任意个变量的逻辑表达式[√]

[×]

二、写出图中电路的逻辑函数表达式。

(每小题 5 分,共10 分)

1、 F=A B

2、 F=AB CD

三、选择题:(多选题,多选或少选不得分,每小题 2 分,共 20 分)。

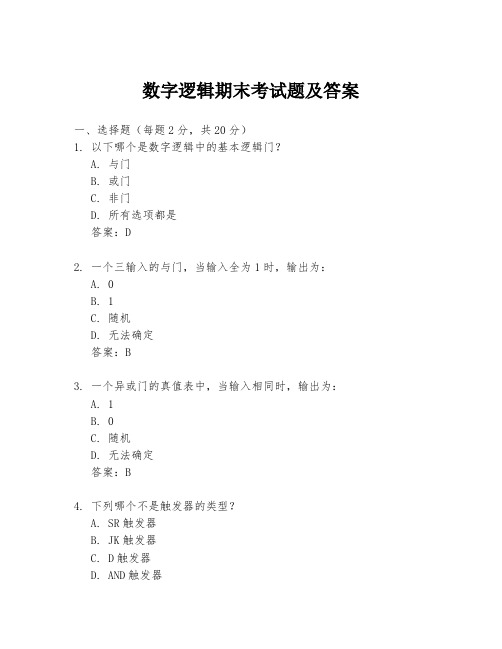

数字逻辑期末考试题及答案

数字逻辑期末考试题及答案一、选择题(每题2分,共20分)1. 以下哪个是数字逻辑中的基本逻辑门?A. 与门B. 或门C. 非门D. 所有选项都是答案:D2. 一个三输入的与门,当输入全为1时,输出为:A. 0B. 1C. 随机D. 无法确定答案:B3. 一个异或门的真值表中,当输入相同时,输出为:A. 1B. 0C. 随机D. 无法确定答案:B4. 下列哪个不是触发器的类型?A. SR触发器B. JK触发器C. D触发器D. AND触发器答案:D5. 在数字电路中,同步计数器和异步计数器的主要区别在于:A. 计数范围B. 计数速度C. 计数精度D. 计数方式答案:B6. 一个4位二进制计数器,其最大计数值为:A. 15B. 16C. 32D. 64答案:A7. 以下哪个不是数字逻辑设计中常用的简化方法?A. 布尔代数简化B. 卡诺图简化C. 逻辑门替换D. 逻辑表简化答案:C8. 在数字电路中,一个信号的上升沿指的是:A. 信号从0变为1的瞬间B. 信号从1变为0的瞬间C. 信号保持不变D. 信号在变化答案:A9. 一个D触发器的Q输出端在时钟信号上升沿时:A. 保持不变B. 翻转状态C. 跟随D输入端D. 随机变化答案:C10. 以下哪个不是数字逻辑中的状态机?A. Moore机B. Mealy机C. 有限状态机D. 无限状态机答案:D二、填空题(每空2分,共20分)11. 在布尔代数中,逻辑与操作用符号______表示。

答案:∧12. 一个布尔函数F(A,B,C)=A∨B∧C的最小项为______。

答案:(1,1,1)13. 在数字电路设计中,卡诺图是一种用于______的工具。

答案:布尔函数简化14. 一个4位二进制加法器的输出端最多有______位。

答案:515. 一个同步计数器在计数时,所有的触发器都______时钟信号。

答案:接收16. 一个JK触发器在J=K=1时,其状态会发生______。

《数字逻辑设计》期末考试 试题及参考解答

………密………封………线………以………内………答………题………无………效……电子科技大学2013 -2014学年第 二 学期期 末 考试 A 卷课程名称:_数字逻辑设计及应用__ 考试形式: 闭卷 考试日期: 20 14 年 07 月 10 日 考试时长:_120___分钟课程成绩构成:平时 30 %, 期中 30 %, 实验 0 %, 期末 40 % 本试卷试题由___六__部分构成,共__8___页。

题号 一 二 三 四 五 六 七 八 九 十 合计得分I. Fill out your answers in the blanks (3’ X 10=30’)1. A circuit with 10 flip-flops can store ( 10 ) bit binary numbers, that is, include ( 1024 或 210 ) states at most.2. A 5-bit linear feedback shift-register (LFSR) counter with no self-correction can have ( 31 或 25-1 ) normal states.3. A modulo-24 counter circuit needs ( 5 ) D filp-flops at least. A modulo-500 counter circuit needs ( 3 ) 4-bit counters of 74x163 at least.4. If an 74x148 priority encoder has its 1, 3, 4, and 5 inputs at the active level, the active LOW binary output is ( 010 ) .5. State/output table for a sequential circuit is shown as Table 1. X is input and Z n is output. Assume that the initial state is S 0, if the input sequence is X = 01110101, the output sequence should be ( 11001100 或110011000 ). 【可以确定的输出序列应该有9位】.6. Transition/output table for a sequential circuit is shown in Table 2, X is input and Y is output, the sequential circuit is a modulus ( 3 ) up/down counter.n+1n 21………密………封………线………以………内………答………题………无………效……7. A serial sequence generator by feedback shift registers 74x194 is shown in Figure 1, assume the initial state is Q 2Q 1Q 0 = 100, the feedback function LIN = Q 2’Q 1’ + Q 2Q 0’, the output sequence in Q 2 is ( 100110 循环输出 ).Figure 18. When the input is 01100000 of an 8 bit DAC, the corresponding output voltage is 3.76V . The output voltage range for the DAC is ( 0 ~ 9.99 或 568221276.3+−× 或 9625576.3× )V . 【本题并未对误差范围进行要求,一般可保留2位小数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字逻辑考试题答案及评分标准数字逻辑考试题答案及评分标准(一)一、填空(共20分,每空1分)1. 11.75 B.C2. 000101103. 高电平 低电平 高阻状态 6. AB+AC 7. 2n 10. 0100 11. JK12. S=2N13. 原函数 反函数二、选择题(共10分,每题1分) 1. B 3. C 4. A 5. A 6. B 9. D 10. C三、简答题(共15分)1. n 位无符号二进制数的取值最小可以是全为0,最大是全为1,对应的十进制数的范围是0~2n-1。

最大的2位十进制数为99,由于27>99>26,所以表示一个最大2位十进制数至少需要7位二进制数。

3.(1)0110010100100001 (2)010*********.00000011 四、计算(共20分)1. (1)AB AB ABC A BC AB =+=+)( (3分) (2)B A B A B A =+))(( (3分)2.(3分)∑=++++++++=++++=+++++)14,12,11,9,6,5,4,1()()()(5414614129111__________m m m m m m m m m m C B A D BC D AB D C B CD B A C B A D B C A D C B D CD B A (1分)D B A D C A D B Y ++= (1分)3. (5分)CA D C D ABC B B C A B AD C D A C B B A B A C B D B C A ABBC BD AC AB BC BD AC +++=+++++++=+++++=⋅+⋅=⋅⋅⋅))(())((__________________________________________________________________________________________4. 模为6(4分) 五、1.当没有车辆行驶时,道路的状态设为0,有车辆行驶时,道路的状态为1;通道允许行驶时的状态设为1,不允许行驶时的状态设为0。

设A 表示通道A 有无车辆的状态,B1、B2表示通道B1、B2有无车辆的情况,LA 表示通道A 的允许行驶状态,LB 表示通道B 的允许行驶状态。

由此列出。

(5分)真值表(5分)2121A LA += ()21______________21______B B A B B A LA LB +=⋅+== (5分)(此答案缺逻辑图)数字逻辑考试题答案及评分标准(二)一、填空题(共20分,每空1分) 1. 与 或 非2. 高电平为“1”,低电平为“0”3. 逻辑状态4. A+BC5. 逻辑图、卡诺图6. 2n7. (13)D =(1101)B =(D)H =(00010011)8421BCD 码 二、选择(共10题,每题1分) 2. B 5. B 6. A 9. D 10、B三、证明(共10分,每小题5分) (1) B A B A A +=+由交换律 ))((C A B A BC A ++=+,得B A B A A A B A A +=++=+))(((2) AC AB C AB C B A ABC +=++ACAB B C A C B C A C B C B BC A C AB C B A ABC +=+=+=++=++)()()(四、化简题,将下列逻辑函数化成最小项。

(共10分,每小题5分)(1)C B A BC A F +++=C B A C B A +++=)(C B A C A B A +++=))(()())((A A B B C B B C A C C B B A +++++++= ABC B A BC A C B A C B A C B A +++++= 75310m m m m m ++++=∑=)7,5,3,2,1,0(m(2)C B AB F +=C B A C B A C AB ABC +++= 7651m m m m +++= ∑=)7,6,5,1(m五、用卡诺图法化简下列逻辑函数。

(共10分,每小题5分) (1)AB CD101101000001111011111111D C A D C A D B A ABD F +++=(2)5CDAB0011011110X XX 11XX 1X1D B C A D C A D C B A F ++=),,,(六、设计(40分) 1、电路功能描述:设三个输入变量分别对应:主裁判为变量A ,副裁判分别为B 和C ;表示对应输出变量为F 。

裁判按下按钮,表示认定成功举起,输入变量取值为1,否则为0;当成功与否的信号灯亮时,F 为1,否则为0。

根据逻辑要求列出真值表,如下表所示。

(5分) A B C F 0 0 0 0 0 0 0 011 真值表根据真值表得到逻辑表达式 ABC C AB C B A F ++=用卡诺图化简逻辑函数,见下图,化简后得到的逻辑表达式为 AC AB F +=(3分)采用与非门实现逻辑线路,将逻辑表达式利用摩根定律变换为:AC AB F ⋅= 根据逻辑表达式,可得到逻辑电路图。

(2分)A BCAF2、解:令数据选择器的输入接成 A1=A 、A0=B 、D0=C 、D1=1、D2=C 、D3=C (1分) 电路图如下所示。

(15分)数字逻辑考试题答案及评分标准(三)一、填空(共20分,每空1分)1. 数值 状态2. 0 高阻3. 10000110 10111001 7. 3 8. 97 1100001 141 9. 与运算 或运算 非运算 11. 翻转二、选择题(每题1分,共10分)1. D2. C 4. C 5. C三、计算题(共10分,每题1分)(1) 43D=101011B=53O=2BH ; 43的BCD 编码为0100 0011BCD 。

(2) 127D=1111111B=177O=7FH ; 127的BCD 编码为0001 0010 0111BCD 。

四、化简题(共25分,每题5分) (1)C A AB C B F ++= (2)B F =(3)C B D C A D C A ABD F +++= (4)D C A D B C A F ++= (5)D B D C B A F ++=五、分析下图所示逻辑电路的功能。

(10分)C B A S ⊕⊕=C B A AB AB C B A C )()(_____________________________________⊕+=⊕= 此电路功能为全加器。

五、试用2输入与非门和反相器设计一个4位的奇偶校验器,即当4位数中有奇数个1时输出为0,否则输出为1。

(10分) D C B A L ⊕⊕⊕=_______________________B A B A B A B A L ⋅=+=六、(1)根据题目要求,列出真值表如下表所示。

(5分)余3码变换成8421BCD 码的真值表(2)用卡诺图进行化简,如图所示。

有4个输入量、4个输出量,故分别画出4个4变量卡诺图。

化简后得到的逻辑表达式为: 00A L = 0110011A A A A A A L ⊕=+= 01301202013012022A A A A A A A A A A A A A A A A L ⋅⋅=++= 01323013233A A A A A A A A A A L ⋅=+=(5分)(3)由逻辑表达式画出逻辑图如下图所示。

(5分)数字逻辑考试题答案及评分标准(四)一、填空(共20分,每空1分) 1. 高电平 低电平 高阻状态 5. 10000110 10111001 6. 扇出系数N0 9. 3 10. 24.1 14.2 11. AB+C12. 高电平有效 13. 编码A 00011110000111103A 1A 0L 3A 32AA 10AA 000111100001111032A 1A 0A A 3A 2A 01A A 000111100001111032A 1A 0A 1L A 3A 2A01A A 000111100001111032A 1A 0A A 3A 2A 01A ××××××××××××××××××××××××1111111111111100000000000001000000000002L 0L 2AA 0A 1A 2A 3L 0123二、选择题(共10分,每题1分) 2. D 3. B三、用代数法化简下列等式(共20分,每题5分) (1) )(ABC AB + =AB AB ABC A BC AB =+=+)((2) ))((B A B A + =B A B A B A =+))(( (3) )(_______C B BC A +=))(()(_______C B C B A C B BC A +++=+C AB C C B C A C B AB +=++++=(4)B C CB BC A ABC A ++++_____=C A B C CB BC A ABC A +=++++_____四、 (1)该电路有两个输入变量A 、B 和一个输出变量F 。

F 的逻辑表达式为B AB A AB F ⋅⋅⋅=(2分)(2)进行化简:B A B A B A B B A A B A B AB A AB F ⊕=+=+++=⋅+⋅=)()((3分)(3)由化简后的逻辑表达式可知,该电路实现异或门的功能。

(5分) 五、用译码器74138和适当的逻辑门实现函数(10分) 7640m m m m ABC C AB C B A C B A F +++=+++=六、(10分)七、(1)时钟方程CP 0=CP 1=CP 2=CP 输出方程nnnQ Q Q Y 012=驱动方程n Q J 20=、、n Q K 20=、n Q J 01=、n Q K 01=、n Q J 12=、nQ K 12=。

(2分) (2)状态方程(3分)将J 、K 代入JK 触发器特征方程n n n Q K JQ Q +=+1得各触发器状态方程:nn Q Q 210=+、n n Q Q 011=+、n n Q Q 112=+ (3)计算得到状态表(现 态次 态输 出Y 0 0 00 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 1 0 0 0 0 1 0 1 0 0 1 1 011 1 1 0 1 1 1n 2Q n 1Q n 0Q 1|n 2Q +1n 1Q +1n 0Q +(4)画状态图及时序图(5分)(5)逻辑功能(5分)这是一个有六个工作状态的同步工作电路,属Moore 型电路。