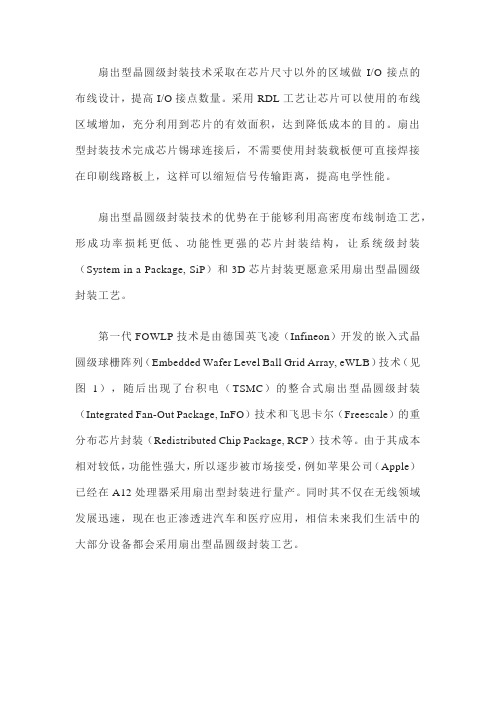

各种晶圆级制程的封装技术比较表

晶圆级扇出型封装工艺详解

扇出型晶圆级封装技术采取在芯片尺寸以外的区域做I/O接点的布线设计,提高I/O接点数量。

采用RDL工艺让芯片可以使用的布线区域增加,充分利用到芯片的有效面积,达到降低成本的目的。

扇出型封装技术完成芯片锡球连接后,不需要使用封装载板便可直接焊接在印刷线路板上,这样可以缩短信号传输距离,提高电学性能。

扇出型晶圆级封装技术的优势在于能够利用高密度布线制造工艺,形成功率损耗更低、功能性更强的芯片封装结构,让系统级封装(System in a Package, SiP)和3D芯片封装更愿意采用扇出型晶圆级封装工艺。

第一代FOWLP技术是由德国英飞凌(Infineon)开发的嵌入式晶圆级球栅阵列(Embedded Wafer Level Ball Grid Array, eWLB)技术(见图1),随后出现了台积电(TSMC)的整合式扇出型晶圆级封装(Integrated Fan-Out Package, InFO)技术和飞思卡尔(Freescale)的重分布芯片封装(Redistributed Chip Package, RCP)技术等。

由于其成本相对较低,功能性强大,所以逐步被市场接受,例如苹果公司(Apple)已经在A12处理器采用扇出型封装进行量产。

同时其不仅在无线领域发展迅速,现在也正渗透进汽车和医疗应用,相信未来我们生活中的大部分设备都会采用扇出型晶圆级封装工艺。

图1 英飞凌eWLB工艺技术示例图传统的封装技术如倒装封装、引线键合等,其信号互连线的形式包括引线、通孔、锡球等复杂的互连结构。

这些复杂的互连结构会影响芯片信号传输的性能。

在扇出型封装中(见图2),根据重布线的工序顺序,主要分为先芯片(Chip first)和后芯片(Chip last)两种工艺,根据芯片的放置方式,主要分为面朝上(Face up)和面朝下(Face down)两种工艺,综合上述四种工艺,封装厂根据操作的便利性,综合出以下三种组合工艺,分别是面朝上的先芯片处理(Chip first-face up)、面朝下的先芯片处理(Chip first-face down)和面朝下的后芯片处理(Chip last-face down)。

晶圆级封装(WLP)方案(一)

晶圆级封装(WLP)方案一、实施背景随着微电子产业的快速发展,封装技术正面临着严峻的挑战。

传统的封装技术由于尺寸大、电性能和热性能较差等问题,已经难以满足高性能集成电路的封装需求。

而晶圆级封装(WLP)技术的出现,为产业结构的改革提供了新的解决方案。

二、工作原理晶圆级封装(WLP)是一种将集成电路直接封装在晶圆片上的技术。

它通过在晶圆片上制造出多个集成电路,然后通过切割和封装,将这些集成电路分别封装在独立的封装体中。

具体来说,WLP技术首先在晶圆片上制造出多个集成电路,这些集成电路可以是数字电路、模拟电路、混合信号电路等。

然后,使用切割机将晶圆片切割成单个集成电路,再将这些集成电路分别封装在独立的封装体中。

三、实施计划步骤1.设备采购:需要采购制造集成电路所需的设备,如光刻机、刻蚀机、薄膜沉积设备等。

2.工艺研发:需要研发适合WLP技术的制造工艺,包括光刻工艺、刻蚀工艺、薄膜沉积工艺等。

3.样品制作:在研发阶段,需要制作样品以验证工艺的可行性。

4.测试与验证:对制作的样品进行测试和验证,确保其性能符合要求。

5.批量生产:当样品测试通过后,可以开始批量生产。

四、适用范围WLP技术适用于各种高性能集成电路的封装,如CPU、GPU、FPGA等。

它具有以下优点:1.体积小:由于WLP技术将集成电路直接封装在晶圆片上,因此可以大大减小封装体积。

2.电性能和热性能优异:WLP技术可以提供更好的电性能和热性能,从而提高集成电路的性能和可靠性。

3.制造成本低:由于WLP技术可以在晶圆片上制造多个集成电路,因此可以分摊制造成本,降低单个集成电路的制造成本。

4.可扩展性强:WLP技术可以轻松扩展到更大的晶圆尺寸和更高的产量。

五、创新要点1.制造工艺的创新:WLP技术需要研发适合其特点的制造工艺,包括光刻工艺、刻蚀工艺、薄膜沉积工艺等。

2.封装技术的创新:WLP技术需要开发新的封装技术,以实现集成电路的高性能、小型化和可靠性。

芯片封装类型图解

芯片封装类型图解本文介绍了常见的集成电路封装形式,包括BGA、CPGA、FBGA、JLCC、LDCC、LQFP100L、PCDIP、PLCC、PPGA、PQFP、TQFP100L、TSBGA217L、TSOP、CSP、SIP、ZIP、S-DIP、SK-DIP、PGA、SOP、MSP和QFP等。

SIP是单列直插式封装,引脚在芯片单侧排列,与DIP基本相同。

ZIP是Z型引脚直插式封装,引脚比SIP粗短些,节距等特征也与DIP基本相同。

S-DIP是收缩双列直插式封装,引脚在芯片两侧排列,引脚节距为1.778mm,芯片集成度高于DIP。

SK-DIP是窄型双列直插式封装,除了芯片的宽度是DIP的1/2以外,其它特征与DIP相同。

PGA是针栅阵列插入式封装,封装底面垂直阵列布置引脚插脚,插脚节距为2.54mm或1.27mm,插脚数可多达数百脚,用于高速的且大规模和超大规模集成电路。

SOP是小外型封装,表面贴装型封装的一种,引脚端子从封装的两个侧面引出,字母L状,引脚节距为1.27mm。

MSP是微方型封装,表面贴装型封装的一种,又叫QFI等,引脚端子从封装的四个侧面引出,呈I字形向下方延伸,没有向外突出的部分,实装占用面积小,引脚节距为1.27mm。

QFP是四方扁平封装,表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈L字形,引脚节距为1.0mm、0.8mm、0.65mm、0.5mm、0.4mm、0.3mm,引脚可达300脚以上。

SVP是一种表面安装型垂直封装,其引脚端子从封装的一个侧面引出,中间部位弯成直角并与PCB键合,适用于垂直安装,实装占有面积很小。

其引脚节距为0.65mm和0.5mm。

LCCC是一种无引线陶瓷封装载体,其四个侧面都设有电极焊盘而无引脚,适用于高速、高频集成电路封装。

PLCC是一种无引线塑料封装载体,适用于高速、高频集成电路封装,是一种塑料封装的LCC。

SOJ是一种小外形J引脚封装,其引脚端子从封装的两个侧面引出,呈J字形,引脚节距为1.27mm。

扇出型晶圆级封装技术国内外对比

扇出型晶圆级封装技术国内外对比

扇出型晶圆级封装技术(Fan-Out Wafer Level Packaging,FOWLP)是一种先进的封装技术,它将多个芯片集成在一个封装体内,以提高系统的性能和可靠性。

这种技术特别适用于便携式消费电子领域,如智能手机、平板电脑等。

在国内外对比方面,扇出型晶圆级封装技术的发展都呈现出蓬勃的态势。

国内方面,随着半导体产业的快速发展,一些企业如中芯长电、盛合晶微等已经开始投入研发和生产扇出型晶圆级封装技术。

其中,盛合晶微在2022年8月份正式投产了RDL重布线扇出型晶圆级封装产线,这标志着在国内率先成功实现以晶圆级扇出封装代替传统的基板封装。

与此同时,国外在扇出型晶圆级封装技术方面也取得了显著的进展。

例如,Amkor和日月光(ASE)等封测代工厂已经能够提供封装尺寸为1×1mm~12×12mm的扇出封装技术,并正在研发更大尺寸的封装技术。

此外,一些国际知名的半导体企业如英飞凌(Infineon)、高通等也在积极投入研发和生产扇出型晶圆级封装技术。

在技术方面,国内外都面临着一些挑战。

例如,封装厚度的减薄、异质材料间热膨胀系数(CTE)失配导致的晶圆翘曲(Warpage)、加热冷却、晶圆模塑化合物膨胀收缩导致芯片偏移(Die shift)以及多道制程累积的残余应力导致材料间界面分层甚至破裂等问题都需要解决。

此外,焊点实现芯片和PCB板互连是整个封装结构中最关键、薄弱的地方,也是技术研发的重点之一。

总体来说,国内外在扇出型晶圆级封装技术方面都取得了显著的进展,但仍需要不断研发和创新来克服技术挑战和提高封装性能。

(整理)最全的芯片封装方式图文对照

芯片封装方式大全各种IC封装形式图片精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档各种封装缩写说明BGA精品文档BQFP132BGA精品文档BGA精品文档BGABGA精品文档BGACLCCCNR精品文档PGADIPDIP-tabBGA精品文档DIPTOFlat Pack精品文档HSOP28TO精品文档精品文档TOJLCCLCCCLCC(ceramic leaded chip carrier) 带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,呈丁字形 。

带有窗口的用于封装紫外线擦除型EPROM 以及带有EPROM 的微机电路等。

此封装也称为 QFJ 、QFJ -G(见QFJ)。

BGALQFPDIP精品文档PGAPLCCPQFP精品文档DIPLQFP精品文档LQFP精品文档PQFPQFP精品文档QFPTQFPBGA精品文档SC-70 5LDIP精品文档SIPSOSOH精品文档SOJSOJ精品文档SOPTO精品文档SOPSOP精品文档CANTOTO精品文档TOTO3CAN精品文档CANCANCANCAN精品文档TO8TO92CAN精品文档CANTSOPTSSOP or TSOP精品文档BGABGAZIP精品文档PCDIP以下封装形式未找到相关图片,仅作简易描述,供参考:DIM单列直插式,塑料例如:MH88500QUIP蜘蛛脚状四排直插式,塑料例如:NEC7810DBGA BGA系列中陶瓷芯片例如:EP20K400FC672-3CBGA BGA系列中金属封装芯片例如: EP20K300EBC652-3MODULE方形状金属壳双列直插式例如:LH0084RQFP QFP封装系列中,表面带金属散装体例如:EPF10KRC系列DIMM电路正面或背面镶有LCC封装小芯片,陶瓷,双列直插式例如:X28C010DIP-BATTERY电池与微型芯片内封SRAM芯片,塑料双列直插式例如:达拉斯SRAM系列(五)按用途分类集成电路按用途可分为电视机用集成电路。

先进封装技术完整版

先进封装技术目录:1.BGA技术2.CSP封装技术1倒装焊技术1晶圆级封装技术(WLP) 13D封装技术1SiP1柔性电子2.CSP封装技术WB -CSP 剖面示意图和外形图CSP•什么是CSP?─CSP--Chip Scale (Size) Package ─封装外壳的尺寸不超过裸芯片尺寸1.2倍(JEDEC 等共同制定的标准)─按互连方式,CSP 可分为WB 和FC 两种─缺乏标准化─引脚间距: 1.0, 0.75, 0.5mm 1.有效减小封装厚度和面积,利于提高组装密度2.有效降低电容、电感的寄生效应,大幅提高电性能3. 可利用原有的表面安装设备和材料4.散热性能优良特点:•结构特征─在IC的引出焊区的基础上,将引脚再分布(redistribution)─结构主要包括IC芯片, 互连层,保护层及焊球(凸点)刚性基板CSP引线框架式CSP焊区阵列式CSP2. CSP封装技术– 微小模塑封型CSP•微小模塑封型CSP①结构①结构②工艺再布线工艺流程•几种CSP互连的比较•CSP技术的应用情况•CSP发展仍需解决的问题:– 产品标准化问题– 二次布线技术– 封装材料– 组装CSP产品的印制电路板问题– 成本控制3. 倒装焊技术4. 晶圆级封装(Wafer level packaging)4.晶圆级封装•定义在通常制作IC芯片的Al焊区完成后,继续完成CSP的封装制作,称之为晶圆级CSP(WLCSP),又称作晶圆级封装。

它是一种以BGA技术为基础,是一种经过改进和提高的CSP,综合了BGA、CSP的技术优势。

•WLP 的主要技术种类•工艺5. 3D封装技术5. 3D封装技术• 3D封装的基本概念3D封装技术又称立体封装技术。

与传统封装技术相比,在原有基础上向Z方向即向空间发展的微电子封装高密度化。

• 3D封装技术的特点:– 更有效的利用基板,提高硅效率– 通过更短的互联获得更高的电性能– 有效降低系统成本•3D封装的主要类型:─ 芯片堆叠封装(Die stacking)以芯片叠层为特色,在单一封装衬底上叠加上两层或者多层芯片Samsung公司 6-Die 叠层封装芯片–封装体堆叠(Package stacking)在其内部经过完整测试的封装被堆叠到另一个经过完整测试的封装上部–晶圆级堆叠(Wafer-level stacking)3-D晶圆堆叠是通过对具有特殊功能的完整晶圆的生产达到的,这些晶圆垂直互连。

晶圆级封装技术说课讲解

重布线层(RDL)的目的是对芯片的铝焊区 位置进行重新布局,使新焊区满足对焊料球 最小间距的要求,并使新焊区按照阵列排布。

第二种结构如图(b)所示,焊球 置于在RDL 层上,并通过2 层 聚合物介质层与Si 芯片相连, 此种结构中没有焊点下金属层。 两层聚合物层作为钝化和再布线 层。这种结构不同于第一种结构, 尽管两种结构均有再布线层。如 图b所示,高分子介电薄膜层置 于焊球和硅衬底。这种高分子层 能够作为缓冲层来降低由于温度 变化所引起的PCB 和硅的热失 配产生的热-机械应力。这种 WLP 结构能拓展到间距为0.5 mm 的12×12焊球阵列。

所示为典型的晶圆凸点制作 的工艺流程。 首先在晶圆上完成UBM 层 的制作。然后沉积厚胶并曝 光,为电镀焊料形成模板。 电镀之后,将光刻胶去除并 刻蚀掉暴露出来的UBM 层。 最后一部工艺是再流,形成 焊料球。

电镀技术可以实现很窄的凸点节 距并维持高产率。并且该项技术 应用范围也很广,可以制作不同 尺寸、节距和几何形状的凸点, 电镀技术已经越来越广泛地在晶 圆凸点制作中被采用,成为最具 实用价值的方案。

不同的WLP 结构

第三种WLP 结构如图(c)所示,是在图(b)结构的基础 上,添加了UBM 层。由于添加了这种UBM 层,相应 增加了制造成本。这种UBM 能稍微提高热力学性能。

图(d)所示的第四种WLP 结构,采用了铜柱结构, 首先电镀铜柱,接着用环氧树脂密封。

40种常用的芯片封装技术

40种常用的芯片封装技术封装,Package,是把集成电路装配为芯片最终产品的过程,简单地说,就是把Foundry生产出来的集成电路裸片(Die)放在一块起到承载作用的基板上,把管脚引出来,然后固定包装成为一个整体。

作为动词,“封装”强调的是安放、固定、密封、引线的过程和动作;作为名词,“封装”主要关注封装的形式、类别,基底和外壳、引线的材料,强调其保护芯片、增强电热性能、方便整机装配的重要作用。

1、芯片面积与封装面积之比为提高封装效率,尽量接近1:1;2、引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能;3、基于散热的要求,封装越薄越好。

封装主要分为DIP双列直插和SMD贴片封装两种。

从结构方面,封装经历了最早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP公司开发出了SOP小外型封装,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

从材料介质方面,包括金属、陶瓷、塑料,很多高强度工作条件需求的电路如军工和宇航级别仍有大量的金属封装。

1、BGA封装(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配 LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360引脚 BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且 BGA不用担心 QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

一文看懂半导体制造工艺中的封装技术

一文看懂半导体制造工艺中的封装技术共读好书半导体制造工艺流程半导体制造的工艺过程由晶圆制造(Wafer Fabr ication)、晶圆测试(wafer Probe/Sorting)、芯片封装(Assemble)、测试(T est)以及后期的成品(Finish Goods)入库所组成。

半导体器件制作工艺分为前道和后道工序,晶圆制造和测试被称为前道(Front End)工序,而芯片的封装、测试及成品入库则被称为后道(Back End)工序,前道和后道一般在不同的工厂分开处理。

前道工序是从整块硅圆片入手经多次重复的制膜、氧化、扩散,包括照相制版和光刻等工序,制成三极管、集成电路等半导体元件及电极等,开发材料的电子功能,以实现所要求的元器件特性。

后道工序是从由硅圆片分切好的一个一个的芯片入手,进行装片、固定、键合联接、塑料灌封、引出接线端子、按印检查等工序,完成作为器件、部件的封装体,以确保元器件的可靠性,并便于与外电路联接。

半导体制造工艺和流程晶圆制造晶圆制造主要是在晶圆上制作电路与镶嵌电子元件(如电晶体、电容、逻辑闸等),是所需技术最复杂且资金投入最多的过程。

以微处理器为例,其所需处理步骤可达数百道,而且所需加工机器先进且昂贵。

虽然详细的处理程序是随着产品种类和使用技术的变化而不断变化,但其基本处理步骤通常是晶圆先经过适当的清洗之后,接着进行氧化及沉积处理,最后进行微影、蚀刻及离子植入等反复步骤,最终完成晶圆上电路的加工与制作。

晶圆测试晶圆经过划片工艺后,表面上会形成一道一道小格,每个小格就是一个晶片或晶粒(Die),即一个独立的集成电路。

在一般情况下,一个晶圆上制作的晶片具有相同的规格,但是也有可能在同一个晶圆上制作规格等级不同的晶片。

晶圆测试要完成两个工作:一是对每一个晶片进行验收测试,通过针测仪器(Probe)检测每个晶片是否合格,不合格的晶片会被标上记号,以便在切割晶圆的时候将不合格晶片筛选出来;二是对每个晶片进行电气特性(如功率等)检测和分组,并作相应的区分标记。

40种常用的芯片封装技术

40种常用的芯片封装技术封装,Package,是把集成电路装配为芯片最终产品的过程,简单地说,就是把Foundry生产出来的集成电路裸片(Die)放在一块起到承载作用的基板上,把管脚引出来,然后固定包装成为一个整体。

作为动词,“封装”强调的是安放、固定、密封、引线的过程和动作;作为名词,“封装”主要关注封装的形式、类别,基底和外壳、引线的材料,强调其保护芯片、增强电热性能、方便整机装配的重要作用。

1、芯片面积与封装面积之比为提高封装效率,尽量接近1:1;2、引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能;3、基于散热的要求,封装越薄越好。

封装主要分为DIP双列直插和SMD贴片封装两种。

从结构方面,封装经历了最早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP公司开发出了SOP小外型封装,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

从材料介质方面,包括金属、陶瓷、塑料,很多高强度工作条件需求的电路如军工和宇航级别仍有大量的金属封装。

1、BGA 封装(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Existing Ics

1997

Flip Chip

Technolory

(FCT)

Ultra CSP

經由兩層高分子(BCB)介電層與一層金屬層,使得I/O重新佈局。然後再印上錫膏形成凸塊

Flash,

DRAM,

SRAM

1998

Fujitsu

Super CSP

(SCSP)

先將I/O重新佈局後再將整片晶片(正面)進行模壓(Molding),然後再進行植球(Ball Mount)、切割等步驟

各種晶圓級製程的封裝技術比較表

公司名稱

產品名稱

封裝技術特點

應用產品

發表時間

Chipscale

Micro SMT

(MSMT)

晶片正面封膠並加蓋(cap),只適用於四週引腳銲墊(pad)及低腳數的產品。

Microwave Diode,

TransLeabharlann stor,RFIC1994

EPIC

在晶片上再製作兩層積層(built-up)電路,使得I/O重新佈局(Redistribution),再製作銅凸塊(bump)並鍍上Ni/Au

Flash

SRAM

Other Memory

1998

National Semicondustor

(NS)

ΜSMD

晶片的背面以封膠保護,正面再以Polyimide保護,接點處製作錫鉛凸塊

Low-pin-count

Application

1998

Sandia

MBGA

經由兩層高分子(Polyimide)介電層與兩層金屬導電層,使得I/O重新佈局,然後製作金屬凸塊(金或錫鉛凸塊)

1996

ASICs

Memory

DSPs

Microcontroller

1995

ShellCase

Shell-PACK

Shell-BGA

晶粒上下均有玻璃保護的三明治結構,金屬導線由package的側面引至玻璃上再重新佈局,再於玻璃表面製作外接引腳或印上錫膏形成凸塊

ASICS

EEPROM

Memory

Optical Devices