数字电路-计数器-74LVC161

74 161 计数器

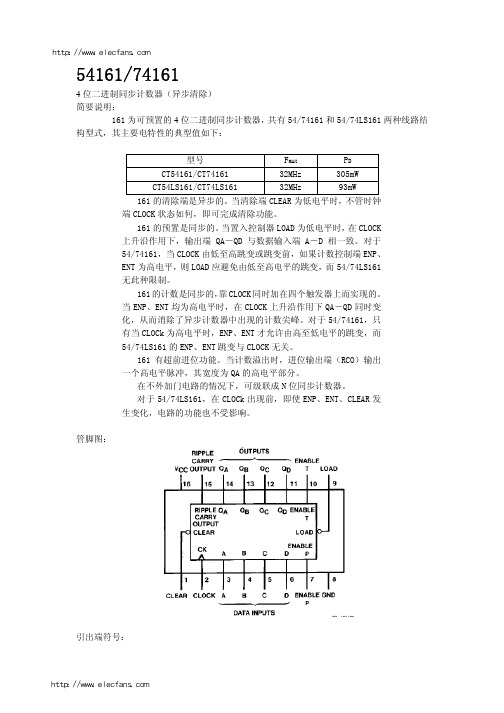

54161/741614位二进制同步计数器(异步清除)简要说明:161为可预置的4位二进制同步计数器,共有54/74161和54/74LS161两种线路结构型式,其主要电特性的典型值如下:型号 F MAX P DCT54161/CT74161 32MHz 305mWCT54LS161/CT74LS161 32MHz 93mW161的清除端是异步的。

当清除端CLEAR为低电平时,不管时钟端CLOCK状态如何,即可完成清除功能。

161的预置是同步的。

当置入控制器LOAD为低电平时,在CLOCK上升沿作用下,输出端QA-QD与数据输入端A-D相一致。

对于54/74161,当CLOCK由低至高跳变或跳变前,如果计数控制端ENP、ENT为高电平,则LOAD应避免由低至高电平的跳变,而54/74LS161无此种限制。

161的计数是同步的,靠CLOCK同时加在四个触发器上而实现的。

当ENP、ENT均为高电平时,在CLOCK上升沿作用下QA-QD同时变化,从而消除了异步计数器中出现的计数尖峰。

对于54/74161,只有当CLOCk为高电平时,ENP、ENT才允许由高至低电平的跳变,而54/74LS161的ENP、ENT跳变与CLOCK无关。

161有超前进位功能。

当计数溢出时,进位输出端(RCO)输出一个高电平脉冲,其宽度为QA的高电平部分。

在不外加门电路的情况下,可级联成N位同步计数器。

对于54/74LS161,在CLOCk出现前,即使ENP、ENT、CLEAR发生变化,电路的功能也不受影响。

管脚图:引出端符号:PCO 进位输出端CLOCK 时钟输入端(上升沿有效)CLEAR 异步清除输入端(低电平有效)ENP 计数控制端ENT 计数控制端ABCD 并行数据输入端LOAD 同步并行置入控制端(低电平有效)QA-QD 输出端功能表:说明:H-高电平L-低电平X-任意↑-低到高电平跳变极限值电源电压------------------------------------------------7V输入电压54/74161-----------------------------------------5.5V54/74LS161---------------------------------------7VENP与ENT间电压54/74161-----------------------------------------5.5V 工作环境温度54×××------------------------------ -55~125℃74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃推荐工作条件:CT54161/CT74161 CT54LS161/CT74LS161单位最小额定最大最小额定最大54 4.5 5 5.5 5.5V 电源电压Vcc74 4.75 5 5.25 4.75 5 5.25输入高电平电压V IH 2 2 V54 0.80.7V 输入低电平电压V IL74 0.80.8输出高电平电流I OH-800-400 μA54 16 4mA 输出低电平电流I OL74 16 8时钟频率f CP0 25 0 25 MHzCLOCK 25 25ns 脉冲宽度tWCLEAR 20 20A-D、ENP 20 20ns 建立时间t setLOAD 25 20保持时间t H0 0 ns 时序图:逻辑图静态特性(T A 为工作环境温度范围)`161 `LS161参数测试条件【1】最小最大最小最大单位I IK =-12mA -1.5V IK 输入钳位电压 Vcc 最小I IK =-18mA-1.5 V54 2.4 2.5V OH 输出高电平电压Vcc=最小,V IH =2V ,V IL =最大, I OH =最大74 2.42.7V54 0.4 0.4V OL 输出低电平电压 V CC =最小,V IH =2V ,V IL =最大,I OL =最大740.40.5VA -D,ENP,CLEAR1 0.1I I 最大输入电压时输入电流 LOAD,CLOCk,ENT Vcc=最大 V I =5.5V (‘LS161为7V )1 0.2 mAA -D,ENP,CLEAR40 20LOAD 40 40 I IH 输入高电平电流 CLOCK,ENT Vcc=最大 V IH =2.4V (‘LS161为2.7V )80 40 μA A -D,ENP,CLEAR-1.6-0.4 LOAD -1.6 -0.8 V IL 输入低电平电流CLOCK,ENTVcc=最大 V IL =0.4V-3.2-0.8 mA 54-20-57-20 -100I OS 输出短路电流 Vcc=最大74-18-57-20 -100mA54 85 31IccH 输出高电平时电源电流Vcc=最大,LOAD 先接高电平,再接低电平,其余输入接高电平 74 94 31 mA54 91 32IccL 输出低电平时电源电流Vcc=最大,CLOCK 先接高电平,再接低电平,其余输入接低电平74101 32mA【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

74LS161 实验讲解

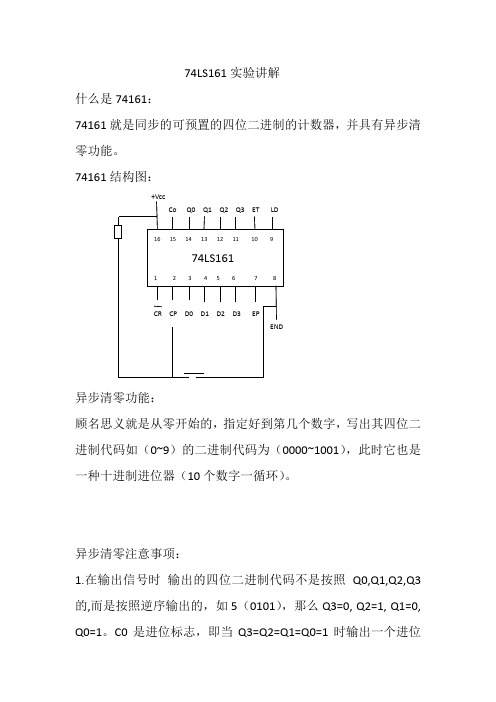

74LS161实验讲解什么是74161:74161就是同步的可预置的四位二进制的计数器,并具有异步清零功能。

74161结构图:异步清零功能:顾名思义就是从零开始的,指定好到第几个数字,写出其四位二进制代码如(0~9)的二进制代码为(0000~1001),此时它也是一种十进制进位器(10个数字一循环)。

异步清零注意事项:1.在输出信号时输出的四位二进制代码不是按照Q0,Q1,Q2,Q3的,而是按照逆序输出的,如5(0101),那么Q3=0, Q2=1, Q1=0, Q0=1。

C0是进位标志,即当Q3=Q2=Q1=Q0=1时输出一个进位信号1,否则输出0。

9(1010),Q3=1, Q2=0, Q1=0, Q0=1。

2.当循环到数字9时,由于Q3=1,Q0=1,那么瞬时就会把“0”信号传入CR,数字“9”会被瞬时清零,很难被看清(除非相应慢)。

想要克服这种情况,必须把9改成10(1010)。

这样才能看清9,然后再变成0。

异步清零(十进制(0~9))结构实验图:因为到数字10时(1010)Q3=1, Q2=0, Q1=1, Q0=0,发现只有当Q3=Q1=1时才开始循环,那么依照《电工与电子技术》第198页的表8-9。

只有让CR为”L”,即”0”才开始清零操作。

可以吧Q3和Q1与非的结果送入+Vcc C0Q0 Q1 Q2 Q3 ET LD同步并行:1.同异步清零相似,但是同步并行的功能比异步清零更完善,即可以恢复到初始状态。

2.与异步清零不同,因为异步清零只能从零开始,到某个位置回复到零在开始循环。

二同步并行并没有这种局限,它能从任意位置开始,然后到指定的位置,在恢复到一开始设置的位置循环。

注意事项:1.与异步清零相似的注意事项,在输入输出的,都是按照逆序输入输出的d3,d2,d1,d0. Q3,Q2,Q1,Q0.2.因为下图的LD没有带上非号,而课本第198表8-9上的LD上有非号,所以连接电路时还是注意一下。

中职计数器74LS161功能及其应用

(2)74LS161构成16以内的任意进制加法计数器: ① 分析74LS161的功能:

②设Ⅰ计、方直法接:复位法; Ⅱ、反馈置零法; Ⅲ、反馈预置 法

③ 反馈信号的拾取: 可利用与非门拾取状态 可利用进位输出CO拾取状态1111

④ 电路举例(以十进制计数器为例)

十进制计数器的计数状态顺序表

Ⅰ、直接复位法 构成十进制计数器

Ⅲ、反馈预置法 构成十进制计数器

①利用进位输出CO取状态1111 ②令D3 D2 D1 D0=0110 ③实现十进制计数 (0110到1111) ④改变D3 D2 D1 D0的状态,可以实现其它进制计数。

小结: 1、74LS161的逻辑功能:

①异步清零; ②同步预置数; ③保持; ④计数。

2、用集成计数器构成任意进制计数器的方法

10.2.4 中规模集成计数器及其应用

同步四位二进制计数器74LS161

1. 74LS161的逻辑功能 2. 应用举例

复习

计数器设计有哪两种方法?

•(1)利用触发器和门电路构成。 •(2)利用现有集成计数器通过外部电路适当连接构成。

1. 74LS161的逻辑功能

引脚排列图

状态输出

逻辑符号

CP输入

①利用与非门拾取状态1010 ②实现十进制计数 (0000到1001) ③改变与非门的输入信号 ,可以实现其它进制计数。

Ⅱ、反馈置零法 构成十进制计数器

①利用与非门拾取状态1001 ②令D3 D2 D1 D0=0000 ③可实现从0开始计数的十进制计数 (0000到1001) ④改变与非门的输入信号, 可以实现其它进制计数。

①直接复位法; ②反馈置零法; ③反馈预置法。

作业题

P250 10题

计数器74LS161功能及其应用

用74LS161构成从0开始计数的十进制计数器

利用与非门拾取状态1010 实现十进制计数 (0000到1001)

改变与非门的输入信号 ,可以实现其它进制计数。 2018/10/22 11

(3)利用多片74LS161实现大容量计数 ① 先用级联法 计数器的级联是将多个集成计数器(如M1进制、 M2 进 制 ) 串 接 起 来 , 以 获 得 计 数 容 量 更 大 的 N (=M1×M2)进制计数器。 一般集成计数器都设有级联用的输入端和输出 端。

5-8 5-9 5-10

2018/10/22

15

异步清0功 能最优先 同步并 行置数 CP上升 沿有效

2018/10/22

CO= Q3 Q2 Q1 Q0 CTT

3

2018/10/22

图5-22 74LS161的时序图

2.应用举例 (1)同步二进制加法计数

实现四位二进制加法计数

2018/10/22 5

(2)构成16以内的任意进制加法计数器: ① 设计思想:利用脉冲反馈法 用 S0 , S1 , S2… , SM…SN 表 示 输 入 0 , 1 , 2,…,N个计数脉冲CP时计数器的状态。 SM可以为S0,但需小于SN。

对于异步置数:在输入第N个计数脉冲CP后,通 过控制电路,利用状态SN产生一个有效置数信号,送 给异步置数端,使计数器立刻返回到初始的预置数状 态SM,即实现了SM~SN-1计数。 对于同步置数:在输入第N-1个计数脉冲CP时, 利用状态SN-1产生一个有效置数信号,送给同步置数控 制端,等到输入第N个计数脉冲CP时,计数器返回到 初始的预置数状态 SM,从而实现SM~SN-1计数。 2018/10/22 6

数电作业-用74ls161设计同步加法计数器

H a r b i n I n s t i t u t e o f T e c h n o l o g y设计说明书(论文)课程名称:数字电子技术基础设计题目:同步加法计数器设计院系:航天学院自动化班级:0804101设计者:龚翔宇学号:24设计时间:【问题重述】试用同步加法计数器74LS161(或74LS160)和二4输入与非门74LS20构成百以内任意进制计数器,并采用LED数码管显示计数进制。

采用555定时器构成多谐振荡电路,为同步加法计数器提供时钟输入信号。

【设计思路】同步加法计数器74LS161为16进制计数器,要设计一个60进制的计数器,用555定时器设计多谐振荡电路,为同步加法计数器74LS161提供时钟输入信号并且用LED数码管显示结果。

要用16进制的161计时器设计60进制的,必须将其改装为10进制的。

将2个161联级,低位向高位进位6次,然后置零——即基本设计思路。

【基本元件】74LS161(两片)二4输入与非门74LS20(一片)555定时器【设计方案】555定时器提供时钟信号用555构成的多谐振荡器用555定时器构成的多谐振荡器如图所示。

555定时器可以方便的接成施密特触发器,在其基础上再改接成多谐振荡器。

o u可输出触发脉冲信号。

74LS161接为十进制计数器本方案使用置数法将161改装为十进制的计数器。

用如图所示。

D C B A Q Q Q Q 在经过1000时置数控制端LD =0,74LS161处在置数状态,D C B AQ Q Q Q 重新回到1111, 跳过了中间6个状态,由16进制转换为十进制计数器。

RCO 仍为进位输出。

对于低位芯片,全以0态作为起始状态,经过10-1=9状态后,产生置数控制信号1001。

这样,当第10个时钟的上升沿到达时,计数器置数为0000,每个芯片跳过剩余状态,成为10进制的计数器。

对于高位芯片,以取全0态作为起始状态,经过6个状态后,计数器清零,每个芯片跳过剩余状态,成为6进制的计数器。

74LS161中文资料

0.7

V

74

0.8

0.8

-800

-400 μA

电子器件采购平台: IC资料查询网站: 电子工程技术论坛:/bbs

http://www.elecfans.com

54

输出低电平电流 IOL

74

时钟频率fCP

0

脉冲宽度 tW

25

35

35 24 27 24 27 14 14 28

单位 MHz ns

ns ns ns ns

http://www.elecfans.com

(LOAD=L)

(‘LS161 为 2KΩ)

tPLH CLOCk->RCO tPHL

tPHL CLEAR->Q

【2】:fmax-最大时钟频率

tPLH-输出由低到高电平传输延迟时间

tPHL-输出由高到低电平传输延迟时间

‘161 最小 最大

25

35

35 20 23 25 29 16 16 38

‘LS161 最小 最大

74 -18 -57 -20 -100

Vcc=最大,LOAD 先接高电平,再接低 54

85

IccH 输出高电平时电源电流

电平,其余输入接高电平

74

94

31 mA

31

Vcc=最大,CLOCK 先接高电平,再接低 54

91

IccL 输出低电平时电源电流

电平,其余输入接低电平

74

101

32 mA

32

【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

VIH=2.4V(‘LS161 为 2.7V)

40

20

40

40 μA

74LS161计数器

74LS161计数器

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输⼊端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC.(TC=Q0·Q1·Q2·Q3·CET)

输⼊输出

C R CP L

D EP ET D3D2D1D0Q3Q2Q1Q0

0ФФФФФФФФ0000

1↑0ФФd c b a d c b a

1↑10ФФФФФQ3Q2Q1Q0

1↑1Ф0ФФФФQ3Q2Q1Q0

1↑111ФФФФ状态码加1

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0⽴即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作⽤后,74LS161

输出端Q3、Q2、Q1、Q0的状态分别与并⾏数据输⼊端D3,D2,D1,D0的状态⼀样,为同步置数功能。

⽽只有当

CR=LD=EP=ET=“1”、CP脉冲上升沿作⽤后,计数器加1。

74LS161还有⼀个进位输出端CO,其逻辑关系是

CO=Q0·Q1·Q2·Q3·CET。

合理应⽤计数器的清零功能和置数功能,⼀⽚74LS161可以组成16进制以下的任意进制分频器。

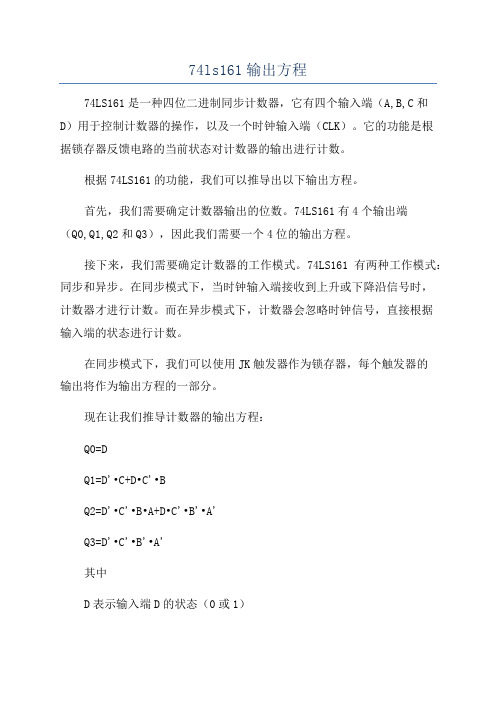

74ls161输出方程

74ls161输出方程74LS161是一种四位二进制同步计数器,它有四个输入端(A,B,C和D)用于控制计数器的操作,以及一个时钟输入端(CLK)。

它的功能是根据锁存器反馈电路的当前状态对计数器的输出进行计数。

根据74LS161的功能,我们可以推导出以下输出方程。

首先,我们需要确定计数器输出的位数。

74LS161有4个输出端(Q0,Q1,Q2和Q3),因此我们需要一个4位的输出方程。

接下来,我们需要确定计数器的工作模式。

74LS161有两种工作模式:同步和异步。

在同步模式下,当时钟输入端接收到上升或下降沿信号时,计数器才进行计数。

而在异步模式下,计数器会忽略时钟信号,直接根据输入端的状态进行计数。

在同步模式下,我们可以使用JK触发器作为锁存器,每个触发器的输出将作为输出方程的一部分。

现在让我们推导计数器的输出方程:Q0=DQ1=D'•C+D•C'•BQ2=D'•C'•B•A+D•C'•B'•A'Q3=D'•C'•B'•A'其中D表示输入端D的状态(0或1)D'表示输入端D的反状态(1或0)C表示输入端C的状态(0或1)C'表示输入端C的反状态(1或0)B表示输入端B的状态(0或1)B'表示输入端B的反状态(1或0)A表示输入端A的状态(0或1)A'表示输入端A的反状态(1或0)通过以上方程,我们可以根据输入端的状态来确定74LS161计数器的输出。

这些方程描述了计数器在每个时钟周期中的状态转换。

请注意,这只是74LS161计数器输出方程的一个示例。

根据具体的设计要求和工作模式,方程可能会有所不同。

因此,在实际应用中,我们需要根据具体的设计要求来确定计数器的输出方程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SF00656

LOGIC SYMBOL

15

15 16

LOGIC SYMBOL (IEEE/IEC)

1 Q0 Q1 Q2 Q3 14 13 12 11 9 7 10 2 R M1 G3 G4 C2 /1,3,4+ CTR4

TC 3 4 5 6 9 D0 D1 D2 D3 PE CEP CET CP MR

D0 9 PE

D1

D2

D3

Parallel load

PARALLEL LOAD CIRCUITRY

Count Hold (do nothing)

TC 15

10 CET

7 CEP

2

CP

BINARY COUNTER

1 MR Q0 Q1 Q2 Q3

14

13

12

11

NOTES: * = The TC output is High when CET is High and the counter is at Terminal Count (HHHH) H = High voltage level h = High voltage level one setup time prior to the Low-to-High clock transition L = Low voltage level l = Low voltage level one setup time prior to the Low-to-High clock transition q = Lower case letters indicate the state of the referenced output one setup time prior to the Low-to-High clock transition X = Don’t care ↑ = Low-to-High clock transition

74LVC161

FUNCTIONAL DIAGRAM

3 4 5 6

FUNCTION TABLE

OPERATING MODES Reset (clear) INPUTS MR L H H H H H CP X ↑ ↑ ↑ X X CEP X X X h l X CET X X X h X l PE X l l h h h Dn X l h X X X OUTPUTS Qn L L H count qn qn TC L L * * * L

1998 May 20

2

853-1864 19421

Philips Semiconductors

Product specification

Presettable synchronous 4-bit binary counter; asynchronous reset

Hale Waihona Puke 74LVC161PIN CONFIGURATION

The 74LVC161 is a synchronous presettable binary counter which features an internal look–head carry and can be used for high–speed counting. Synchronous operation is provided by having all flip–flops clocked simultaneously on the positive–going edge of the clock (CP). The outputs (Q0 to Q3) of the counters may be preset to a HIGH or LOW level. A LOW level at the parallel enable input (PE) disables the counting action and causes the data at the data inputs (D0 to D3) to be loaded into the counter on the positive–going edge of the clock (provided that the set–up and hold time requirements for PE are met). Preset takes place regardless of the levels at count enable inputs (CEP and CET). A low level at the master reset input (MR) sets all four outputs of the flip–flops (Q0 to Q3) to LOW level regardless of the levels at CP, PE, CET and CEP inputs (thus providing an asynchronous clear function). The look–ahead carry simplifies serial cascading of the counters. Both count enable inputs (CEP and CET) must be HIGH to count. The CET input is fed forward to enable the terminal count output (TC). The TC output thus enabled will produce a HIGH output pulse of a duration approximately equal to a HIGH level output of Q0. This pulse can be used to enable the next cascaded stage. The maximum clock frequency for the cascaded counters is determined by the CP to TC propagation delay and CEP to CP set–up time, according to the following formula:

fmax = 1 _______________________________

tp(max) (CP to TC) + tSU (CEP to CP)

QUICK REFERENCE DATA

GND = 0V; Tamb = 25°C; TR = TF 2.5ns SYMBOL PARAMETER Propagation delay CP to Qn CP to TC MR to Qn MR to TC CET to TC maximum clock frequency input capacitance power dissipation capacitance per gate notes 1 and 2 CONDITIONS CL = 50 pF VCC = 3.3V TYPICAL 4.9 5.7 5.2 5.7 4.5 200 5.0 39 UNIT

3 4

1,2 D

14 13 12 11 15

7

10

2

1

5 6

4 CT=15 VCC = Pin 16 GND = Pin 8

SY00065

SY00066

1998 May 20

3

Philips Semiconductors

Product specification

Presettable synchronous 4-bit binary counter; asynchronous reset

DESCRIPTION

The 74LVC161 is a high–performance, low–power, low–voltage, Si–gate CMOS device and superior to most advanced CMOS compatible TTL families.

INTEGRATED CIRCUITS

74LVC161 Presettable synchronous 4-bit binary counter; asynchronous reset

Product specification Supersedes data of 1996 Aug 23 IC24 Data Handbook 1998 May 20

Philips Semiconductors

Philips Semiconductors

Product specification

Presettable synchronous 4-bit binary counter; asynchronous reset

74LVC161

FEATURES

• Wide supply voltage range of 1.2 V to 3.6 V • In accordance with JEDEC standard no. 8–1A • Inputs accept voltages up to 5.5 V • CMOS low power consumption • Direct interface with TTL levels • Asynchronous reset • Synchronous counting and loading • Two count enable inputs for n–bit cascading • Positive edge–triggered clock • Output drive capability 50 W transmission lines @85_C

tPHL/tPLH

ns

fMAX CI CPD

MHz pF pF

NOTES: 1. CPD is used to determine the dynamic power dissipation (PD in µW) PD = CPD x VCC2 x fi +Σ (CL x VCC2 x fo ) where: fi = input frequency in MHz; CL = output load capacity in pF; fo = output frequency in MHz; VCC = supply voltage in V; Σ (CL x VCC2 x fo ) = sum of the outputs 2. The condition is V1 = GND to VCC