双端口存储器原理实验

8管 sram 工作原理

8管 sram 工作原理SRAM(Static Random Access Memory)是一种静态随机存取存储器,它是由一系列的存储单元组成的,用于存储和读取数据。

它的工作原理可以通过以下几个方面来解释。

SRAM的存储单元是由一对互补的存储节点组成的。

其中一个节点是一个存储电容器,另一个节点是一个放大器。

这种存储方式使得SRAM可以在不断电的情况下保持数据的存储状态,因此被称为静态存储器。

SRAM使用了一种称为“双端口”的存储器结构。

这意味着SRAM 可以同时进行读取和写入操作。

具体而言,SRAM的每个存储单元都有两个输入端口和一个输出端口。

其中一个输入端口用于写入数据,另一个输入端口用于控制写入操作;输出端口用于读取数据。

SRAM的读取操作是通过将读取地址应用到存储器中的存储单元来实现的。

当读取地址与存储单元的地址匹配时,存储单元中的数据将被放大器放大并输出。

这种方式使得SRAM的读取速度非常快,因为它不需要进行复杂的电荷传输操作。

SRAM的写入操作是通过将写入数据和写入地址应用到存储器中的存储单元来实现的。

当写入地址与存储单元的地址匹配时,写入数据将被存储在存储单元的电容器中。

在写入操作期间,存储单元的另一个输入端口用于控制写入操作,以确保数据被正确地写入。

SRAM还具有一种称为“刷新”的操作。

由于SRAM的存储单元是由电容器组成的,电容器会逐渐失去电荷,从而导致数据丢失。

为了防止数据丢失,SRAM需要定期进行刷新操作。

刷新操作的原理是将存储单元中的数据读取出来,然后重新写入,以恢复电容器的电荷。

总结一下,SRAM的工作原理可以归纳为以下几个关键点:静态存储方式、双端口结构、读取和写入操作、以及刷新操作。

这些特点使得SRAM成为一种快速、可靠的存储器,广泛应用于计算机和其他电子设备中。

计算机组成原理双端口存储器实验报告

计算机组成原理实验报告实验名称双端口存储器实验专业软件工程学院计算机与软件学院姓名徐振兴班级(2)学号20111344069 指导老师任勇军实验日期2013.5.24 得分一、实验类别原理性+分析性二、实验目的⑵了解双端口静态存储器IDT7132的工作特性及其使用方法;⑵了解半导体存储器怎样存储和读取数据;⑶了解双端口存储器怎样并行读写;⑷熟悉TEC-8模型计算机中存储器部分的数据通路。

三、实验设备⑴TEC-8 实验系统1台⑵双踪示波器1台⑵直流万用表1块⑷逻辑测试笔(在TEC-8 实验台上) 1 支四、实验电路双端口RAM 电路由1 片IDT7132 及少许附加电路组成,存放程序和数据。

IDT7132 有2 个端口,一个称为左端口,一个称为右端口。

2 个端口各有独立的存储器地址线、数据线和3 个读、写控制信号: CE#、R/W#和OE#,可以同时对器件内部的同一存储体同时进行读、写。

IDT7132 容量为2048 字节,TEC-8 实验系统只使用64 字节。

在TEC-8 实验系统中,左端口配置成读、写端口,用于程序的初始装入操作,从存储器中取数到数据总线DBUS,将数据总线DBUS 上的数写入存储器。

当信号MEMW 为1 时,在T2 为1 时,将数据总线DBUS 上的数D7~D0 写入AR7~AR0 指定的存储单元;当MBUS 信号为1 时,AR7~AR0 指定的存储单元的数送数据总线DBUS。

右端口设置成只读方式,从PC7~PC0 指定的存储单元读出指令INS7~INS0,送往指令寄存器IR。

程序计数器PC 由2 片GAL22V10(U53 和U54)组成。

向双端口RAM 的右端口提供存储器地址。

当复位信号CLR#为0 时,程序计数器复位,PC7~PC0 为00H。

当信号LPC 为1 时,在T3 的上升沿,将数据总线DBUS 上的数D7~D0 写入PC。

当信号PCINC 为1 时,在T3 的上升沿,完成PC 加1。

双端口存储器实验报告

双端口存储器实验报告实验目的:1.了解双端口存储器的结构和工作原理。

2.掌握Verilog HDL语言的基本应用。

3.掌握ModelSim软件的使用方法。

实验内容:双端口存储器是指具有两个读写口的存储器,它可以通过一个端口写入数据,同时通过另一个端口读出数据,常用于数字信号处理、图像处理等领域。

本实验将通过Verilog HDL语言编写程序,使用ModelSim软件进行仿真验证,实现一个简单的双端口存储器。

具体实验内容如下:2.编写Verilog HDL程序实现简单的双端口存储器。

在程序中,定义数据存储器、读写使能信号、读写数据等变量,并利用always语句实现对数据的读写操作。

3.使用ModelSim软件进行仿真验证。

在ModelSim中创建项目,导入设计文件和仿真波形文件,进行波形仿真,验证程序的正确性。

实验步骤:双端口存储器是指具有两个读写口的存储器,其中一个读写口用于读写存储器内部的数据,另一个用于与外部系统交换数据。

在双端口存储器的结构中,存储器数据的读写可以同时进行,而无需互斥。

在读数据端口和写数据端口的操作中,存在两个读写控制信号,一个是读写使能信号,用于控制读写操作是否有效;另一个是写使能信号,用于控制数据写入操作的触发。

2.编写Verilog HDL程序实现简单的双端口存储器。

module dual_port_memory (input clk,input [3:0] addr1,input [3:0] addr2,input [7:0] data_in,input rd_en1,input rd_en2,input wr_en,output [7:0] data_out1,output [7:0] data_out2);reg [7:0] mem[0:15]; // 定义存储器数组// 读写操作always @(posedge clk) beginif (wr_en) // 写操作mem[addr1] <= data_in;else if (rd_en1) // 读操作1data_out1 <= mem[addr1];else if (rd_en2) // 读操作2data_out2 <= mem[addr2];endendmodule在程序中定义了一个16位的存储器数组mem。

实验4:双端口存储器实验 ----独立方式

河北环境工程学院

《计算机组成原理》实验报告

作者:

系(部):

专业班级:

学号:

成绩:__________________

评阅教师:__________________

年月日

一、实验目的

1、了解双端口静态存储器IDT7132的工作特性及其使用方法;

2、了解半导体存储器怎样存储和读取数据;

3、了解双端口存储器怎样并行读写;

4、熟悉LK-TEC-9模型计算机存储器部分的数据通路;

二、预习内容

1.掌握双端口存储器的使用方法

2. 掌握TEC-8模型计算机存储器的部分的数据通路

三、实验环境及主要器件

1.TEC-8实验系统 1台

2. 逻辑测试笔 1支

3. 双踪示波器 1台

4. 逻辑测试笔 1支

四、实验内容

1、从存储器地址10H开始,通过左端口连续向双端口RAM中写入3个数:85H,60H,38H。

在写的过程中,在右端口检测写的数据是否正确。

2、从存储器地址10H开始,连续从双端口RAM的左端口和右端口同时读出存储器的内容。

五、实验步骤

六、实验结果分析与讨论。

TEC-8实验指导书

2

前 言……………………………………………………………………………………..1 第 1 章 TEC-8 计算机硬件综合实验系统…………………………………………….…..5 1.1 TEC-8 实验系统的用途…………………………………………………………….…5 1.2 TEC-8 实验系统技术特点…………………………………………………….………5 1.3 TEC-8 实验系统组成………………………………………………………….………6 1.4 逻辑测试笔……………………………………………………………………………6 1.5 TEC-8 实验系统结构和操作……………………………………………….…………7 1.5.1 模型计算机时序信号………………………………………………………………7 1.5.2 模型计算机组成……………………………………………………………………7 1.6 模型计算机指令系统………………………………………………………………… 10 1.7 开关、按钮、指示灯……………………………………………………..…………11 1.8 数字逻辑和数字系统实验部分…………………………………..…………………12 1.8.1 基本实验通用区…………………………………………………………………...12 1.8.2 大型综合设计实验装臵………………………………………………………..….13 2 1.9 E PROM 中微代码的修改………………………………………………….……….…13 第 2 章 计算机组织与体系结构基本实验………………………………………………18 2.1 运算器组成实验……………………………………………………………………..18 2.2 双端口存储器实验…………………………………………………………………..22 2.3 数据通路实验………………………………………………………………………..26 2.4 微程序控制器实验…………………………………………………………………..30 2.5 CPU 组成与机器指令的执行…………………………………………………………36 2.6 中断原理实验………………………………………………………………………..39 第 3 章 课程综合设计…………………………………………………………………....43 3.1 模型机硬连线控制器设计…………………………………………………………..43 3.2 模型机流水微程序控制器设计……………………………………………………..47 3.3 模型机流水硬连线控制器设计……………………………………………………..50 3.4 含有阵列乘法器的 ALU 设计………………………………………………………..51 第 4 章 数字逻辑与数字系统基本实验…………………………………………………55 4.1 基本逻辑门逻辑实验………………………………………………………………..55 4.2 TTL、HC 和 HCT 器件的电压传输特性实验………………………………………..56 4.3 三态门实验…………………………………………………………………….…….59 4.4 数据选择器和译码器实验……………………………………………………….….61 4.5 全加器构成及测试实验………………………………………………………….….63 4.6 组合逻辑中的冒险现象实验…………………………………………………….….64 4.7 触发器实验……………………………………………………………………….….66 4.8 简单时序电路实验…………………………………………………………………..69 4.9 计数器和数码管实验………………………………………………………………..70 4.10 四相时钟分配器实验………………………………………………………………74 第 5 章 数字逻辑与数字系统综合设计实验…………………………………………...76 5.1 简易电子琴实验……………………………………………………………………..76

双端口存储器原理实验报告

双端口存储器原理实验报告————————————————————————————————作者:————————————————————————————————日期:一、实验内容、方法和步骤1.接线IAR_BUS 接 GND,ALU_BUS接 GND,RS_BUS 接GND,禁止中断地址寄存器、运算器、多端口寄存器堆RF 向数据总线 DBUS 送数据。

AR1_INC 接 GND,M3 接VCC,使地址寄存器 AR1 和AR2 从数据总线DBUS 取得地址数据。

信号IAR_BUS ALU_BUS RS_BUS AR1_INC M3开关GND GND GND GND VCC信号LDIR SW_BUS LDAR2 LDAR1 CER LRW CEL开关K6 K5 K4 K3 K2 K1 K02.置 DP = 1,DB = 0,DZ = 0,使实验台处于单拍状态。

工作模式开关=“脱机”合上电源。

按复位按钮 CLR#,使实验系统处于初始状态。

置DP = 1,DB = 0,DZ = 0,使实验台处于单拍状态。

工作模式开关=“脱机”合上电源。

按复位按钮CLR#,使实验系统处于初始状态。

(1)写地址寄存器 AR1=00信号SW7~0 LDIR SW_BUS LDAR2 LDAR1 CER LRW CEL 开关K6 K5 K4 K3 K2 K1 K0状态 / 00H 0 10 1 0 0 0 值按一次 QD,将 00H 写入 AR1。

(2)向存储器 00H 地址写数 00H信SW7~0 LDIR SW_BUS LDAR2 LDAR1 CER LRW CEL 号开关K6 K5 K4 K3 K2 K1 K0状态 / 00H 0 1 0 0 0 0 1 值按一次 QD,将 00H 写入存储器 00H 地址。

(3)写地址寄存器 AR1=10信号SW7~0 LDIR SW_BUS LDAR2 LDAR1 CER LRW CEL 开关K6 K5 K4 K3 K2 K1 K0状态 / 10H 0 10 1 0 0 0 值按一次QD,将 10H写入 AR1。

计算机组成原理实验-数据通路实验

Guangzhou Colle-ge of South China University of Technology 计算机组成原理课程实验报告9.5数据通路实验姓名:曾国江______________________学号:____________________________系别:计算机工程学院班级:网络工程1班指导老师:_________________________完成时间:_________________________评语:得分:一、实验类型本实验类型为验证型+分析型+设计型二、实验目的1•进一步熟悉计算机的数据通路2.将双端口通用寄存器堆和双端口存储器模块连接,构成新的数据通路.3.掌握数字逻辑电路中的一般规律,以及排除故障的一般原则和方法.4.锻炼分析问题和解决问题的能力,在出现故障的情况下,独立分析故障现象,并排除故障•三、实验设备1、TEC-5实验系统一台2、双踪示波器一台3、逻辑测试笔一支、实验电路DBUS7DBUSO 左端口> 1JWK273) H3F2HTQCn*4Al JU <181CnN戍蜩口通用寄"器那RFCispLSI10165-一耐'12ARM —T2 —-双堵口存储器IDT7132数据通路实验电路图如图9.7 所示。

它是将双端口存储器模块和双端口通用寄存器堆模块连接在一起形成的。

存储器的指令端口(右端口)不参与本次实验。

通用寄存器堆连接运算器模块,本次实验涉及其中的DRl 。

由于双端口存储器是三态输出,因而可以直接连接到DBUS 上。

此外,DBUS 还连接着通用寄存器堆。

这样,写入存储器的数据由通用寄存器提供,从RAM 中读出的数据也可以放到通用寄存器堆中保存。

本实验的各模块在以前的实验中都已介绍,请参阅前面相关章节。

注意实验中的控制信号与模拟它们的开关K0~K15 的连接。

五、实验任务1、将实验电路与控制台的有关信号进行连接。

计算机组成原理实验(接线、实验步骤)方案

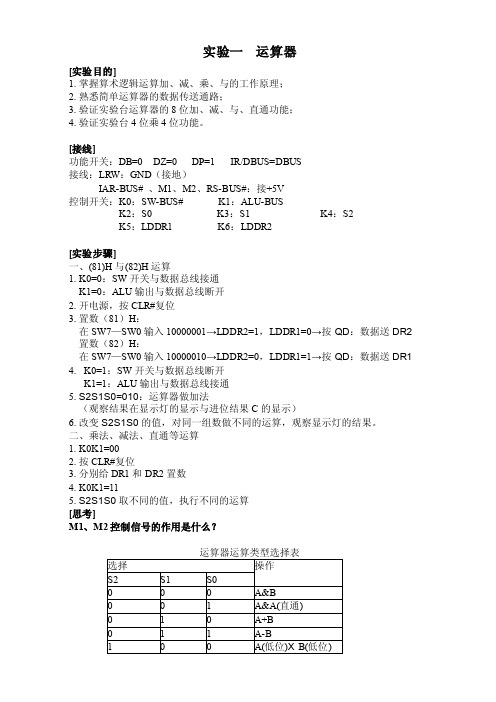

实验一运算器[实验目的]1.掌握算术逻辑运算加、减、乘、与的工作原理;2.熟悉简单运算器的数据传送通路;3.验证实验台运算器的8位加、减、与、直通功能;4.验证实验台4位乘4位功能。

[接线]功能开关:DB=0 DZ=0 DP=1 IR/DBUS=DBUS接线:LRW:GND(接地)IAR-BUS# 、M1、M2、RS-BUS#:接+5V控制开关:K0:SW-BUS# K1:ALU-BUSK2:S0 K3:S1 K4:S2K5:LDDR1 K6:LDDR2[实验步骤]一、(81)H与(82)H运算1.K0=0:SW开关与数据总线接通K1=0:ALU输出与数据总线断开2.开电源,按CLR#复位3.置数(81)H:在SW7—SW0输入10000001→LDDR2=1,LDDR1=0→按QD:数据送DR2置数(82)H:在SW7—SW0输入10000010→LDDR2=0,LDDR1=1→按QD:数据送DR1 4.K0=1:SW开关与数据总线断开K1=1:ALU输出与数据总线接通5. S2S1S0=010:运算器做加法(观察结果在显示灯的显示与进位结果C的显示)6.改变S2S1S0的值,对同一组数做不同的运算,观察显示灯的结果。

二、乘法、减法、直通等运算1.K0K1=002.按CLR#复位3.分别给DR1和DR2置数4.K0K1=115. S2S1S0取不同的值,执行不同的运算[思考]M1、M2控制信号的作用是什么?运算器运算类型选择表选择操作S2 S1 S00 0 0 A&B0 0 1 A&A(直通)0 1 0 A+B0 1 1 A-B1 0 0 A(低位)ΧB(低位)完成以下表格ALU-BUS SW-BUS# 存储器内容S2S1S0 DBUS C输入时:计算时:DR1:01100011DR2:10110100(与)DR1:10110100DR2:01100011(直通)DR1:01100011DR2:01100011(加)DR1:01001100DR2:10110011(减)DR1:11111111DR2:11111111(乘)实验二双端口存储器[实验目的]1.了解双端口存储器的读写;2.了解双端口存储器的读写并行读写及产生冲突的情况。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

华中科技大学实验报告实验名称双端口存储器原理实验成绩实验日期第 2 次试验指导老师陈国平专业计科班号组别学生姓名同组学生一、实验目的1.了解双端口静态存储器IDT7132的工作特性及其使用方法2.了解半导体存储器怎样存储和读取数据。

3.了解双端口存储器怎样并行读写,并分析冲突产生的情况。

二、实验电路图3.2 双端口存储器实验电路图图3.2示出了双端口存储器的实验电路图。

这里使用一片IDT7132(2048×8位),两个端口的地址输入A8-A10引脚接地,因此实际使用的存储容量为256字节。

左端口的数据输出接数据总线DBUS,右端口的数据输出端接指令总线IBUS。

IDT7132有六个控制引脚:CEL#、LR/W#、OEL#、CER#、RR/W#、OER#。

CEL#、LR/W#、OEL#控制左端口读、写操作;CER#、RR/W#、OER#控制右端口的读写操作。

CEL#为左端口选择引脚,低电平有效;当CEL#=1时,禁止对左端口的读、写操作。

LR/W#控制对左端口的读写。

当LR/W#=1时,左端口进行读操作;LR/W#=0时,左端口进行写操作。

OEL#的作用等同于三态门,当OEL#=0时,允许左端口读出的数据送到数据总线DBUS上;当OEL#=1时,禁止左端口的数据放到DBUS。

因此,为便于理解,在以后的实验中,我们将OEL#引脚称为RAM_BUS#。

控制右端口的三个引脚与左端口的三个完全类似,这里不再赘述。

有两点需要说明:(1)右端口读出的数据(更确切的说法是指令)放到指令总线IBUS上而不是数据总线DBUS,然后送到指令寄存器IR。

(2)所有数据/指令的写入都使用左端口,右端口作为指令端口,不需要进行数据的写入,因此我们将右端口处理成一个只读端口,已将RR/W#固定接高电平,OER#固定接地。

这两点请同学好好理解。

存储器左端口的地址寄存器AR和右端口的地址寄存器PC都使用2片74LS163,具有地址递增的功能。

同时,PC在以后的实验当中也起到程序计数器的作用。

左右端口的数据和左右端口的地址都有特定的显示灯显示。

存储器地址和写入数据都由实验台操作板上的二进制开关分时给出。

当LDAR#=0时,AR在T2时从DBUS接收来自SW7-SW0的地址;当AR+1=1时,在T2存储器地址加1。

LDAR#和AR+1不能同时有效。

在下一个时钟周期,令CEL#=0,LR/W#=0,则在T2的上升沿开始进行写操作,将SW7-SW07设置的数据经DBUS写入存储器。

三、实验任务1.按图3.2所示,将有关控制信号和二进制开关对应接好,仔细复查一遍,然后接通电源。

2.将二进制数码开关SW7-SW0(SW0为最低位)设置为00H,将其作为存储器地址置入AR;然后将二进制开关的00H作为数据写入RAM中。

用这个方法,向存储器的10H、20H、30H、40H单元依次写入10H、20H、30H和40H。

3.使用存储器的左端口,依次将第2步存入的5个数据读出,观察各单元中存入的数据是否正确。

记录数据。

注意:禁止两个或两个以上的数据源同时向数据总线上发送数据!在本实验中,当存储器进行读出操作时,务必将SW_BUS#的三态门关闭。

而当向AR送入数据时,双端口存储器也不能被选中。

4.通过存储器的右端口,将第2步存入的5个数据读出,观察结果是否与第3步结果相同。

记录数据。

5.双端口存储器的并行读写和访问冲突。

将CEL#、CER#同时置为0,使存储器的左右端口同时被选中。

当AR和PC的地址不相同时,没有访问冲突;地址相同时,由于都是读操作,也不会冲突。

如果左右端口地址相同,且一个进行读操作,一个进行写操作,就会发生冲突。

检测冲突的方法:观察两个端口的“忙”信号输出指示灯BUSYL#和BUSYR#。

BUSYL#/BUSYR#灯亮(为0)时,不一定发生冲突,但发生冲突时,BUSYL#/BUSYR#必定亮。

四、实验要求1.做好实验预习,掌握IDT7132双端口存储器的功能特性和使用方法。

2.写出实验报告,内容是:(1)实验目的。

(2)实验任务3的数据表格。

(3)实验任务4的数据表格。

(4)实验任务5的检测结果。

五、实验步骤1. 置DP=1,DB=0,编程开关拨到正常位置。

按电路图要求,将有关控制信号和二进制开关对应接好,反复检查后,接通电源。

AR+1 和PC+1 两个信号接地.3.将二进制数码开关SW7-SW0(SW0为最低位)设置为00H,将其作为存储器地址置入AR;然后将二进制开关的00H作为数据写入RAM中.用这个方法,向存储器的10H,20H,30H,40H单元依次写入10H,20H,30H,40H.任务:将00H,10H,20H,30H,40H分别写入存储器单元00H,10H,20H,30H,40H.(1)令K0(LDAR#)=0, K2(CEL#)=1, K4(RAM_BUS#)=1, K5(CER#)=1,K6(SW_BUS#)=0.置SW7-SW0=00H,按QD按钮,将00H打入地址寄存器AR.(2)令K0(LDAR#)=1, K2(CEL#)=0, K3(LR/W#)=0, K4(RAM_BUS#)=1,K5(CER#)=1, K6(SW_BUS#)=0.置SW7-SW0=00H,按QD按钮,将00H写入存储器00H单元.(3)重复1和2,只是改变SW7-SW0分别为10H,20H,30H,40H,分别将10H,20H,30H,40H写入存储器单元10H,20H,30H,40H.实验数据记录表:3.使用存储器的左端口,依次将第2步存入的5个数据读出,观察各单元中存入的数据是否正确.记录数据。

(注意:禁止两个或两个以上的数据源同时向数据总线上发送数据!在本实验中,当存储器进行读出操作时,务必将SW_BUS#的三态门关闭.而当向AR送入数据时,双端口存储器也不能被选中. )任务:从左端口读出存储器00H,10H,20H,30H,40H的内容.(1)令K0(LDAR#)=0, K2(CEL#)=1, K4(RAM_BUS#)=1, K5(CER#)=1,K6(SW_BUS#)=0.置SW7-SW0=00H,按QD按钮,将00H打入地址寄存器AR.(2)先令K6(SW_BUS#)=1,再令K2(CEL#)=0, K3(LR/W#)=1, K4(RAM_BUS#)=0,K5(CER#)=1,则在数据总线DBUS上显示出存储器单元00H的内容00H。

(3)重复1和2的方法,只是改变1中SW7-SW0的值分别为10H,20H,30H,40H,则可在数据总线DBUS上观察到存储器单元10H,20H,30H,40H的内容分别为10H,20H,30H,40H.实验结果记录表1:4.通过存储器的右端口,将第2步存入的5个数据读出,观察结果是否与第3步结果相同.记录数据。

任务:从右端口读出存储器00H,10H,20H,30H,40H的内容.(1)令K1(LDPC#)=0, K2(CEL#)=1, K4(RAM_BUS#)=1, K5(CER#)=1,K6(SW_BUS#)=0.置SW7-SW0=00H,按QD按钮,将00H打入PC.(2)令K6(SW_BUS#)=1, K2(CEL#)=1, K5(CER#)=1,则在指令总线IBUS上显示出存储器单元00H的内容00H.(3)重复1和2的方法,只是改变1中SW7-SW0的值分别为10H,20H,30H,40H,则可在指令总线IBUS上观察到存储器单元10H,20H,30H,40H的内容分别为10H,20H,30H,40H.实验结果记录表2:5.双端口存储器的并行读写和访问冲突。

(1)令K0(LDAR#)=0, K1(LDPC#)=0, K2(CEL#)=1, K4(RAM_BUS#)=1,K5(CER#)=1,K6(SW_BUS#)=0.置SW7-SW0=30H,按QD按钮,将30H打入地址寄存器AR和程序计数器PC.(2)置K6(SW_BUS#)=1, K3(LR/W#)=1, K4(RAM_BUS#)=0.先令K5(CER#)=0,K2(CEL#)=1,这时BUSYL#指令灯不亮.令K2(CEL#)=0,这时BUSYL#指令灯亮,表示左端口在右端口之后和右端口同时对同一个地址读,数据总线DBUS显示30H,指令总线IBUS也显示30H.再令K2(CEL#)=1,BUSYL#指示灯恢复不实用标准文案亮.(3)置K6(SW_BUS#)=1, K3(LR/W#)=1, K4(RAM_BUS#)=0.先令K2(CEL#)=0,K5(CER#)=1,这时BUSYR#指示灯不亮.令K5(CER#)=0,这时BUSYR#指示灯亮,表示右端口在左端口之后和左端口同时对同一个地址读,数据总线DBUS显示30H,指令总线IBUS也显示30H.再令K5(CER#)=1, BUSYR#指示灯恢复不亮.(注意:将CEL#,CER#同时置为0,使存储器的左右端口同时被选中.当AR和PC的地址不相同时,由于都是读操作,也不会冲突.如果左右端口地址相同,且一个进行读操作,一个进行写操作,就会发生冲突.检测冲突的方法:观察两个端口的"忙"信号输出指示灯BUSYL#和BUSYR#.BUSYL#/BUSYR#灯亮(为0)时,不一定发生冲突,但发生冲突时,BUSYL#/BUSYR#必定亮.)六、总结在本次实验中,我们了解了双端口静态存储器的工作特性及其使用方法,掌握了半导体存储器怎样存储和读取数据和双端口存储器怎样并行读写,在存储数据到双端口存储器之前,首先要选择好数据存放的地址,然后才能存储。

精品。