数字示波器【2007年C题一等奖】

2007年电赛C题

数字示波器(C题)【本科组】一、任务设计并制作一台具有实时采样方式和等效采样方式的数字示波器,示意图如图1所示。

图1 数字示波器示意图二、要求1.基本要求(1)被测周期信号的频率范围为10Hz~10MHz,仪器输入阻抗为1MΩ,显示屏的刻度为8 div×10div,垂直分辨率为8bits,水平显示分辨率≥20点/ div。

(2)垂直灵敏度要求含1V/div、0.1V/div两档。

电压测量误差≤5%。

(3)实时采样速率≤1MSa/s,等效采样速率≥200MSa/s;扫描速度要求含20ms/div、2μs /div、100 ns/div三档,波形周期测量误差≤5%。

(4)仪器的触发电路采用内触发方式,要求上升沿触发,触发电平可调。

(5)被测信号的显示波形应无明显失真。

2.发挥部分(1)提高仪器垂直灵敏度,要求增加2mV/div档,其电压测量误差≤5%,输入短路时的输出噪声峰-峰值小于2mV。

(2)增加存储/调出功能,即按动一次“存储”键,仪器即可存储当前波形,并能在需要时调出存储的波形予以显示。

(3)增加单次触发功能,即按动一次“单次触发”键,仪器能对满足触发条件的信号进行一次采集与存储(被测信号的频率范围限定为10Hz~50kHz)。

(4)能提供频率为100kHz的方波校准信号,要求幅度值为0.3V±5%(负载电阻≥1 MΩ时),频率误差≤5%。

(5)其他。

三、说明1.A/D转换器最高采样速率限定为1MSa/s,并要求设计独立的取样保持电路。

为了方便检测,要求在A/D转换器和取样保持电路之间设置测试端子TP。

2.显示部分可采用通用示波器,也可采用液晶显示器。

3.等效采样的概念可参考蒋焕文等编著的《电子测量》一书中取样示波器的内容,或陈尚松等编著的《电子测量与仪器》等相关资料。

4.设计报告正文中应包括系统总体框图、核心电路原理图、主要流程图、主要的测试结果。

完整的电路原理图、重要的源程序和完整的测试结果可用附件给出。

数字示波器的使用方法课件

01

02

03

04

采样率

选择合适的采样率,确保信号 的完整性。

带宽

根据测试需求选择合适的带宽 ,确保信号无失真。

幅度和偏置

调整幅度和偏置,使信号在示 波器上显示最佳。

触发模式

选择合适的触发模式,确保信 号的稳定显示。

数字示波器的信号处理与分析

滤波功能

利用低通、高通、带通等滤波 器对信号进行滤波处理,提高

详细描述

在开机之前,应确保电源线连接良好,示波器没有故障。开机时,按下电源键, 等待示波器自检并正常启动。关机时,先关闭测量菜单,再按下电源键关闭示 波器。

数字示波器的界面与菜单介绍

总结词

熟悉示波器的界面布局和菜单功能,以便快速找到所需的操作选项。

详细描述

数字示波器的界面通常包括显示屏、控制面板和菜单按钮。菜单按钮用于进入各 种测量、设置和显示选项。熟悉这些界面和菜单布局,可以更快地完成操作。

总结词

掌握示波器的测量和计算功能,以便准确获取信号的参数和性能指标。

详细描述

数字示波器具有多种测量功能,如时间、幅度、频率、相位等。通过选择相应的测量菜单,可以对信号波形进行 测量并计算出相应的参数和性能指标。此外,还可以使用自动测量功能,自动测量信号的多种参数。

03 数字示波器的使用技巧

数字示波器的参数设置

数字示波器的使用方法课件

目录

• 数字示波器简介 • 数字示波器的操作方法 • 数字示波器的使用技巧 • 数字示波器的常见问题与解决方案 • 数字示波器的维护与保养

01 数字示波器简介

数字示波器的定义与特点

定义

数字示波器是一种用于测量、观 察和记录电压波形的电子仪器。

特点

2007年全国大学生电子设计竞赛一等奖作品——数字示波器

2007年全国大学生电子设计竞赛一等奖作品——数字示波器发布时间: 2007-11-27 20:28:37作者:责任编辑:数字示波器作者:黄霖宇、陈鹍、侯碧波一等奖作品摘要本数字示波器以单片机和FPGA为核心,对采样方式的选择和等效采样技术的实现进行了重点设计,使作品不仅具有实时采样方式,而且采用随机等效采样技术实现了利用实时采样速率为1MHz的ADC进行最大200MHz的等效采样。

同时系统还具有可测2mV小信号、波形存储回放、测频、触发沿选择、校准信号输出等功能。

AbstractThis digital oscilloscope takes a MCU and FPGA as the core .We made emphases on the choice of the sampling methods and the implement of equivalent sampling, as a result, our design not only has the real-time sampling mode but also can reach the highest equivalent sample rate of 200 MHz using the real-time sample rate of 1 MHz, by way of random equivalent sampling. At the same time, this system has many other functions, such as 2mV small-signal measuring, storage andre-display of waveform, measuring frequency, selective trigger edge , output of thecorrection signal and so on.一、总体方案设计1.方案比较与选择仔细分析题目要求,以实时采样速率为1MHz的ADC实现最大200MHz的等效采样,是本题的最大难点,也是设计的重点之一。

2007年全国电子设计大赛C题

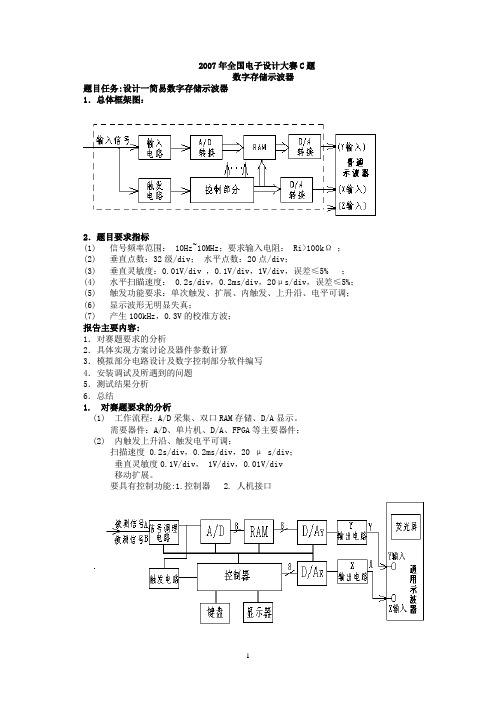

2007年全国电子设计大赛C题数字存储示波器题目任务:设计一简易数字存储示波器1.总体框架图:2.题目要求指标(1) 信号频率范围: 10Hz~10MHz;要求输入电阻: Ri>100kΩ;(2) 垂直点数:32级/div;水平点数:20点/div;(3) 垂直灵敏度:0.01V/div ,0.1V/div,1V/div,误差≤5% ;(4) 水平扫瞄速度: 0.2s/div,0.2ms/div,20μs/div,误差≤5%;(5) 触发功能要求:单次触发、扩展、内触发、上升沿、电平可调;(6) 显示波形无明显失真;(7) 产生100kHz,0.3V的校准方波;报告主要内容:1.对赛题要求的分析2.具体实现方案讨论及器件参数计算3.模拟部分电路设计及数字控制部分软件编写4.安装调试及所遇到的问题5.测试结果分析6.总结1. 对赛题要求的分析(1) 工作流程:A/D采集、双口RAM存储、D/A显示。

需要器件:A/D、单片机、D/A、FPGA等主要器件;(2) 内触发上升沿、触发电平可调;扫描速度 0.2s/div,0.2ms/div,20 μ s/div;垂直灵敏度0.1V/div, 1V/div,0.01V/div移动扩展。

要具有控制功能:1.控制器 2. 人机接口2. 具体方案讨论2.1 采样方式的选择实时采样和等效时间采样:实时采样即按照AD的采样速率对波形进行满足奈奎斯特采样速率的采样;等效采样是在周期信号频率过高,AD速率无法满足奈奎斯特采样速率时,间隔整数倍周期T+最小采样间隔时间对信号进行采样。

具体示意图见下:题中要求输入信号频率范围:10Hz~10MHz,样点直接恢复方式为至少20点/周期, A/D 转换速率应小于1Ms/s。

故对于高频信号(大于500KHz),应采用等效采样方式,低频信号采用实时采样方式。

2.2 控制器件的选择1.对控制器件的要求* AD采集速率:高达1000kHz(1 μ s),低至 20ms;(决定于扫描速度)* 样点恢复速率:DA时钟为10MHz,绝对满足输出波形要求。

2007年C题 数字存储示波器_全国大学生竞赛山东赛区组委会

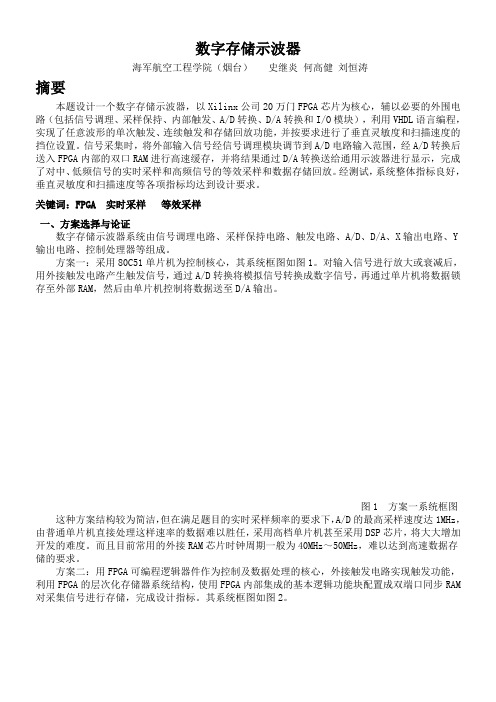

数字存储示波器海军航空工程学院(烟台)史继炎何高健刘恒涛摘要本题设计一个数字存储示波器,以Xilinx公司20万门FPGA芯片为核心,辅以必要的外围电路(包括信号调理、采样保持、内部触发、A/D转换、D/A转换和I/O模块),利用VHDL语言编程,实现了任意波形的单次触发、连续触发和存储回放功能,并按要求进行了垂直灵敏度和扫描速度的挡位设置。

信号采集时,将外部输入信号经信号调理模块调节到A/D电路输入范围,经A/D转换后送入FPGA内部的双口RAM进行高速缓存,并将结果通过D/A转换送给通用示波器进行显示,完成了对中、低频信号的实时采样和高频信号的等效采样和数据存储回放。

经测试,系统整体指标良好,垂直灵敏度和扫描速度等各项指标均达到设计要求。

关键词:FPGA 实时采样等效采样一、方案选择与论证数字存储示波器系统由信号调理电路、采样保持电路、触发电路、A/D、D/A、X输出电路、Y 输出电路、控制处理器等组成。

方案一:采用80C51单片机为控制核心,其系统框图如图1。

对输入信号进行放大或衰减后,用外接触发电路产生触发信号,通过A/D转换将模拟信号转换成数字信号,再通过单片机将数据锁存至外部RAM,然后由单片机控制将数据送至D/A输出。

图1 方案一系统框图这种方案结构较为简洁,但在满足题目的实时采样频率的要求下,A/D的最高采样速度达1MHz,由普通单片机直接处理这样速率的数据难以胜任,采用高档单片机甚至采用DSP芯片,将大大增加开发的难度。

而且目前常用的外接RAM芯片时钟周期一般为40MHz~50MHz,难以达到高速数据存储的要求。

方案二:用FPGA可编程逻辑器件作为控制及数据处理的核心,外接触发电路实现触发功能,利用FPGA的层次化存储器系统结构,使用FPGA内部集成的基本逻辑功能块配置成双端口同步RAM 对采集信号进行存储,完成设计指标。

其系统框图如图2。

图2 方案二系统框图由于FPGA可在线编程,因此大大加快了开发速度。

中国大学mooc《电子技术实验基础(一:电路分析)(电子科技大学) 》满分章节测试答案

title电子技术实验基础(一:电路分析)(电子科技大学)中国大学mooc答案100分最新版content实验1-1 常用电子测量仪器的使用——数字示波器的使用数字示波器的使用单元测试题1、如图所示示波器的面板旋钮中,标出哪个按键是垂直通道的菜单按键A:AB:BC:CD:D答案: A2、如图所示示波器的面板旋钮中,标出哪个旋钮是水平通道的位移旋钮A:AB:BC:CD:D答案: C3、若被测试的信号是交直流叠加信号,示波器的垂直耦合方式应该选择哪一挡A:AC耦合B:DC耦合C:接低耦合D:AC、DC均可答案: DC耦合4、如图所示示波器的探头,测试信号时,探头应该与测试端应如何连接A:探勾接信号端钮,黑色鳄鱼夹接地B: 探勾接地,黑色鳄鱼夹接信号端钮C: 可以任意连接D:以上均不正确答案: 探勾接信号端钮,黑色鳄鱼夹接地5、如下图所示第四个菜单栏中,如果测量时发现该菜单栏显示不是电压1X,而是电压10X,应该调节哪个按键或旋钮使其为电压1XA:旁边的按键切换选择B:VARIABLE旋钮C:AUTOSETD:关机重启答案: VARIABLE旋钮6、下图是所示是示波器探头的手柄阻抗拨动开关细节图,若手柄放在1X端,垂直菜单栏中第四栏应怎么调节?若手柄放在10X端,又该怎样调节?A:电压1X、电压10XB:电压10X、电压1XC:电压1X、电压1XD:任意选择不影响结果答案: 电压1X、电压10X7、如图所示示波器的显示屏上,哪个标示的是通道1的零基线位置A:AB:BC:CD:D答案: C实验1-2 常用电子测量仪器的使用——函数发生器和晶体管毫伏表的使用函数发生器和晶体管毫伏表单元测验1、信号源输出周期信号时频率显示如图所示,当前输出信号的频率是多少?A:1HzB:10HzC:1KHzD:10KHz答案: 1KHz2、信号源给后级网络提供正弦信号,如果信号源幅度显示窗口显示如图所示,表明现在后级网络得到的信号电压大小是?A:不确定B:电压峰值是111mVC:电压峰峰值是111mVD:电压有效值是答案: 不确定3、下列说法正确的是?A: 数字万用表可以测量函数发生器输出信号中的直流分量B: 函数发生器只用“输出幅度调节”旋钮进行幅度调节C:函数发生器可用“直流偏移”旋钮输出直流电压信号D:函数发生器输出信号电压的最大值和最小值之间相差60dB答案: 数字万用表可以测量函数发生器输出信号中的直流分量4、列说法正确的是?A:毫伏表是用来测量包括直流电压在内的电压值的仪表B:使用毫伏表测量正弦信号的有效值时需要考虑正弦信号的频率C:毫伏表和万用表作为交流电压表都可以测量正弦信号的有效值,在没有毫伏表时,可以临时用万用表替代D:三角波信号和方波信号不能送入毫伏表测量答案: 使用毫伏表测量正弦信号的有效值时需要考虑正弦信号的频率5、某个正弦交流信号的有效值是0.8V,毫伏表应选择哪一档进行测量?A:10VB:3VC:1VD:300mV答案: 1V实验2 正弦稳态时RLC元件电压电流相位关系的测试正弦稳态时RLC元件电压电流相位关系的测试1、采用课程实验方案测量电感元件的电压电流相位关系时,为了获得近似90°的电压、电流波形相位差,信号源的频率应:A:适当增大信号源的频率;B:适当减小信号源的频率;C:调节信号源的频率不会影响相位差的测试;D:以上措施都不会改善测量结果答案: 适当增大信号源的频率;2、采用课程实验方案测量电容元件的电压电流相位关系时,示波器测量波形如图所示,下面哪种说法正确:A:CH1通道为取样电阻的电压信号, CH2通道为信号源信号;B:CH1通道为信号源信号, CH2通道为取样电阻的电压信号;C:CH2通道为电容元件的电压信号, CH1通道为取样电阻的电压信号;D:无法判断答案: CH1通道为信号源信号, CH2通道为取样电阻的电压信号;3、测量示波器相位差时显示的两路波形如图所示,为了能正确测量,应适当调节面板中哪个旋钮:A:A;B:B;C:C;D:D答案: A;4、测量示波器相位差时显示的两路波形如图所示,为了减小读数误差,需要适当应适当调节面板中哪个旋钮 :A:A;B:B;C:C;D:D答案: D5、采用课程实验方案正确测量元件的电压电流相位关系时,示波器测量波形如图所示,由此可以判断当前测试的是哪种元件:A:电感;B:电容;C:电阻;D:无法判断答案: 电阻;实验3 一阶RC电路频率特性研究一阶RC电路频率特性研究1、关于一阶RC低通滤波器的截止频率fc,如下描述中哪一项是正确的?A:电阻保持不变,减小电容值, fc降低B:电阻保持不变,增大电容值, fc降低C:截止频率处的输出电压是最大输出电压的50%D:低通滤波器的带宽是fc ~∞答案: 电阻保持不变,增大电容值, fc降低2、根据一阶RC低通滤波器的相频特性公式,随着频率从低到高,相位差的正确变化规律是:A:从0°~ -90°B:从0°~90°C:从-45°~+45°D:从0°~-180°答案: 从0°~ -90°3、测试低通滤波器的幅频特性曲线时,此处假设截止频率是大于500Hz的,如下哪种说法不正确:A: 测试过程中保持电路的输入信号幅度一致B:在大于20Hz的较低频率处找到最大输出电压后,再以此为参照开始测试C: 以输入电压为参照,调节频率至输出电压下降3dB就是截止频率D:在各个频率点测试时,应当保证测试输出电压的毫伏表的指针偏转超过刻度线的⅓答案: 以输入电压为参照,调节频率至输出电压下降3dB就是截止频率。

大学生电子设计竞赛题目方向

大学生电子设计竞赛题目方向1)仪器仪表方向:音频信号分析仪:2007年A题数字取样示波器:2007年C题简易频谱分析仪:2005年C题简易逻辑分析仪:2003年D题低频相位测量仪:2003年C题数字存储示波器:2001年B题频率特性测量仪:1999年C题数字工频多用表:1999年B题简易数字频率计:1997年B题简易RLC测量仪:1995年D 题仪器仪表方向训练重点:内容:包含信号产生、采集、存储、分析、处理、显示、控制等信号处理环节中的大部分或全部。

类型:分为时域分析处理和频域分析处理两大类。

难点:强调速度、处理能力、显示性能等。

需要通过构建新技术硬件平台及运用信号处理算法来实现。

系统中的部分任务需要在训练阶段完成。

训练:DDS 任意信号产生、高速/宽带模拟电路、滤波器、高速ADC/DAC采样与回放、高速数据存储、算法、显示技术、强实时性并发多任务软件设计、FPGA/ CPLD 与单片机的接口、仪器仪表原理、各类电参数测量、等内容。

2)电路系统方向:宽带直流放大器:2009年C题简易程控滤波器:2007年D题正弦信号发生器:2005年A题宽带放大器:2003年B题压控L/C振荡器:2003年A题任意波形发生器:2001年A题简易测量放大器:1999年A题录音与回放系统:1999年E题实用信号源制作:1995年B题电路系统方向训练重点:内容:偏重概念和指标。

涉及到各类经典单元模块电路,及其基本概念、基本原理和新实现方法、性能指标测试方法等。

类型:分为功能型和指标型两大类。

难点:特别强调指标,通常经典设计、通用IC是难以完成的。

训练:放大器、滤波器、振荡器、DDS任意信号产生、基本模拟调理电路、电性能指标测试、开拓设计思路等。

3)功率电子方向:光伏发电模拟装置:2009年A题电能收集充电器:2009年E题开关型稳压电源:2007年E题数控恒流源:2005年F题三相正弦变频电源:2005年G题高效 D 类放大器:2001年D题直流稳定电源:1997年A题实用音频放大器:1995年A题功率电子方向训练重点:内容:大电流、大功率、三相电、斩波、DC-AC逆变、DC-DC开关电源、变频驱动、Class-D功放、光伏发电、并网、MPPT算法,等电力电子领域的新技术。

示波器练习题

示波器练习题一、选择题1. 示波器的核心部件是()。

A. 显示器B. 示波管C. 电源D. 探头A. 模拟示波器B. 数字示波器C. 混合信号示波器D. 数字存储示波器3. 示波器的时间基准(扫描频率)是指()。

A. 水平扫描速度B. 垂直扫描速度C. 信号频率D. 示波器屏幕刷新率4. 示波器探头上的衰减系数通常表示为()。

A. X1B. X10C. X100二、填空题1. 示波器主要由____、____、____和____等部分组成。

2. 示波器的垂直灵敏度是指____。

3. 示波器的水平灵敏度是指____。

4. 在使用示波器测量信号时,探头上的____必须与被测信号匹配。

三、判断题1. 示波器可以测量交流信号和直流信号。

()2. 示波器的探头可以直接接触被测电路,无需接地。

()3. 示波器的扫描频率越高,屏幕上显示的波形越稳定。

()4. 示波器的时间基准(扫描频率)与被测信号的频率无关。

()四、简答题1. 简述示波器的基本原理。

2. 请列举三种常见的示波器探头类型,并说明它们的特点。

3. 如何使用示波器测量交流信号的频率和幅度?4. 在使用示波器进行测量时,为什么要进行探头补偿?五、综合题1. 某模拟示波器的水平扫描速度为1ms/div,垂直灵敏度为1V/div,已知探头衰减系数为X10。

当观察到屏幕上的波形为10个周期,占据4个格子时,求被测信号的频率和峰峰值。

(1)频率:10kHz,峰峰值:5V(2)频率:1MHz,峰峰值:200mV(3)频率:100MHz,峰峰值:1V3. 使用示波器观察一个方波信号,发现波形出现顶部和底部失真,请分析可能的原因,并提出解决方法。

六、案例分析题1. 某工程师使用示波器测量一个未知频率的信号,设置水平扫描速度为5μs/div,观察到波形在屏幕上重复了4次。

请根据这些信息计算未知信号的频率。

2. 在一个电路调试过程中,工程师使用示波器观察到一个正弦波信号,垂直灵敏度为2V/div,波形峰峰值占据了3个格子。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

C题:数字示波器作者:黄霖宇、陈鹍、侯碧波一等奖作品摘要本数字示波器以单片机和FPGA为核心,对采样方式的选择和等效采样技术的实现进行了重点设计,使作品不仅具有实时采样方式,而且采用随机等效采样技术实现了利用实时采样速率为1MHz的ADC进行最大200MHz的等效采样。

同时系统还具有可测2mV小信号、波形存储回放、测频、触发沿选择、校准信号输出等功能。

AbstractThis digital oscilloscope takes a MCU and FPGA as the core .We made emphases on the choice of the sampling methods and the implement of equivalent sampling, as a result, our design not only has the real-time sampling mode but also can reach the highest equivalent sample rate of 200 MHz using the real-time sample rate of 1 MHz, by way of random equivalent sampling. At the same time, this system has many other functions, such as 2mV small-signal measuring, storage andre-display of waveform, measuring frequency, selective trigger edge , output of thecorrection signal and so on.一、总体方案设计1.方案比较与选择仔细分析题目要求,以实时采样速率为1MHz的ADC实现最大200MHz的等效采样,是本题的最大难点,也是设计的重点之一。

此外,较宽的信号带宽(10Hz~10MHz)和较大的幅度动态范围(1mV~8V)也给前级的信号调理电路提出了很高的要求。

对此,我们考虑了以下几种方案:(1)核心处理器选择:方案一:纯单片机方式。

即完全由单片机来实现前级信号程控调理、采样保持电路及A/D转换器的控制、数据的处理及存储、波形显示和控制电路等功能。

方案二:单片机与FPGA结合的方式。

即由单片机来完成信号调理和人机界面等顶层控制功能,而由FPGA来完成采集和信号处理等底层的核心计算。

方案一的最大特点是只用单片机,系统规模可以做得很小,成本较低。

但是,单片机在处理高速信号时略显吃力。

而且在时序控制方面也显得精度不足。

相比之下,方案二则更加合理和可靠。

FPGA的应用已经相当的普遍和成熟。

用其进行采样时钟控制和信号处理,是提高系统性能和指标最有效的方法。

因此,我们选择单片机与FPGA的结合来作为系统的核心处理器。

(2)前级信号调理方案设计:方案一:一路调理。

即所有信号,都通过同一路信号调理电路,经过相应的衰减或放大设计,将信号幅度控制在合适的范围内,以便后级的数据采样。

方案二:多路调理。

即将不同频率范围或不同幅度范围的信号经过各自的电路进行调理。

示波器选择不同的档位,则选择了不同的信号通路。

方案一电路简洁,但是由于信号的频率和幅度跨度都很大,给硬件电路的调试带来的较大的困难;方案二虽然可以对不同频率和幅度范围内的信号进行单独调试,降低了每一路通道对硬件电路的要求,但造成电路规模大,结构非常繁琐,同时如果每一路信号之间的隔离做得不好,也会对采集结果造成很大的影响。

综合考虑,我们选择了方案一,并精心设计了实现电路,使用了压控放大器AD603进行两级放大,前面还加了BUFFER634以提高系统的输入阻抗。

最终很好的完成了题目的要求。

2.系统总体框图(图省)本系统采用单片机和FPGA作为数据处理和控制核心,将设计任务划分为前级通道信号调理、触发信号产生、保持与采样、数据处理与存储、波形显示、控制面板等功能模块。

二、理论分析与参数计算1.等效采样分析等效采样的实现方式一般有顺序等效采样和随机等效采样两种,顺序采样要求能够精确地测出输入信号的频率,而在现今的数字示波器中,大多数采用的是随机等效采样技术。

本系统也采用随机等效采样来实现题目要求。

随机等效时间采样的基本原理是,在每一轮的采集过程中测量每次信号触发时刻后与A/D的第一个采样时钟的时间差,这个时间差表明了触发后的第一次采样时刻,因此,它确定了本轮采样的数据序列在信号波形中的位置。

由于时间差在一个采样周期内是随机分布的,当多轮采样后,采集的数据序列就能在一定的时间内遍历所有可能的取值。

通过对分布在一段时间上的随机采样数据序列的排序,就能重构信号的一个完整的采样波形。

如图2所示是随机等效采样示意波形:(图省)在随机等效采样技术中,关键是测出每次触发点与下一个采样时钟间的时间差。

但该时间极短,很难直接测量。

一般可以借助时间轴展宽方法测量,时间轴展宽是一电容充放电双斜率电路,要求充放电的时间比例很准确,本系统利用高主频FPGA计数来测量时间差。

而等效采样的频率,则与实际的采样速率和存储深度有关。

例如,用1MHz的实时采样速率实现200MHz的等效采样,即等效倍数为200,则需要进行200轮采样,每轮采样1个点。

采样结束后,根据测出的每一点的时间差,将采样的数值进行重新排列,然后将重排后的数据顺序输出,用于波形显示。

用1MHz的采样速率实现等效倍数为200倍的随机采样,需要在1us的时间内测出200个不同的随机时间差,则FPGA至少应工作在200MHz的主频上。

2.垂直灵敏度根据题目要求,垂直分辨率为8bits,显示屏的垂直刻度为8div,因此使用8位A/D即可满足题目要求。

即垂直方向共256点,显示分辨率为32点/div.因为ADC的参考电压为5V(详见硬件电路设计中关于ADC部分),则示波器幅度轴上的8div对应着峰-峰值为5V的信号,即0.625V/div,由此可以计算出每一档的垂直灵敏度所对应的信号放大倍数,如表1所示:表1 垂直灵敏度与信号放大倍数对应关系根据不同的档位选择,通过单片机内置的D/A输出不同的直流电压,来控制AD603的放大倍数,以完成信号的放大需求。

3扫描速度设计要求水平显示分辨率至少为20点/div,则存储深度M应至少为200点。

在固定的存储深度下,采样率fs与扫描速度S成反比,即10*S*fs=M,系统取M=200,则fs=20/S。

系统设定的扫描速度从100ns/div~200ms/div,总共20档,则可以计算出每一档的扫描速度所对应的采样速率,如表2所示。

表2 扫描速度与采样率的对应关系题目要求A/D转换器的最高采样速率限定为1MHz,由表2可知,扫描速度高于20us/div的档位都应该使用等效采样。

三、电路分析与设计1.输入通道调理电路系统采用两片AD603级联方式完成信号的调理。

AD603在90MHz的带宽下增益范围为-11dB~+31dB,两级级联后增益可达-20dB~+60dB,完全可以满足对小信号的放大功能。

但是,AD603的输入阻抗只有100Ω,所以在前面还加了一片BUF634,在宽带模式下BUF634的输入阻抗也高达8MΩ,满足仪器输入阻抗为1MΩ的题目要求。

此外,AD603只能承受4V峰峰值的信号输入,而且在高频时承受电压值还将下降,因此,系统在高幅档位还设计了一个由运放构成的衰减器,从而保证了高幅信号的不失真调理。

采用机械开关控制衰减器与全通电路,减小了用模拟开关或继电器控制带来的对微弱信号的影响,也就减小了系统噪声。

2.采样保持电路采样保持电路可以用运放及其必要的分立元件搭建,也可以采用专门的取样保持芯片。

我们选用了采样保持芯片AD783来实现。

AD783的采样获取时间为250ns,满足1MHz最高采样速率的要求,其小信号输入带宽可达15MHz,也满足最高输入信号频率为10MHz的题目要求。

AD783的信号输入范围为-2.5V~+2.5V,但是,在输入信号为10MHz时,峰峰值超过1V,AD783就难以对输入信号进行正确的采样。

因此,AD603最多只将输入信号放大到1V峰峰值给AD783进行采样保持,以保证采集模拟信号的带宽,然后在AD783与A/D转换器之间再加一级固定增益的放大器,使信号放大到A/D转换器的满量程范围,以保证A/D转换的精度。

(取样保持电路原理图见附录一)3.数据采集及存储电路题目要求A/D转换器的最高采样速率限定为1MHz,而且垂直分辨率为8bit,我们选用的是AD公司的8位并行输出A/D转换器芯片AD7821,其最高采样频率为1MHz,参考电压为5V,采用双电源供电,输入信号电压范围为-2.5V~+2.5V。

(A/D转换器原理图见附录二)选用XILINX公司的FPGA芯片XC3S400对采样保持电路及数据采集电路进行精准的时序控制。

同时我们还在其内部设计了存储器,作为单片机的外扩RAM,用来存储采样得到的数据,并在单片机的控制下将数据显示在液晶上。

4.触发电路(图省)触发电路的作用是产生与信号相关的脉冲信号,让采样电路与输入信号同步,以稳定显示的波形。

题目要求内触发方式,上升沿触发,触发电平可调。

它的核心是比较电路。

比较器采用高速比较器AD8564,该芯片具有7ns的传播延时,3ns的上升、下降建立时间,接成反相迟滞比较器形式,可以处理1Hz到20MHz的信号,而无明显抖动,通过改变参考电平值可以达到改变触发电平的目的。

由于接成反相比较器形式,所以触发信号在FPGA内部还通过了一个反相器,以实现上升沿触发。

四、系统程序设计1.FPGA程序设计。

FGPA主要是控制采样保持电路及A/D转换器,存储采样数据并进行数据处理。

同时还承担了测频的任务。

其程序流程图如下:(图省)2 单片机程序设计。

单片机完成放大电路的控制、波形显示及操作界面的管理。

其程序流程图如下:(图省)五、系统测试1.测试仪器:F40型数字合成函数信号发生器/计数器TDS1012B型100MHz数字存储示波器2.扫描速度测试测试条件:垂直灵敏度0.1V/div。

用信号源输出峰峰值为0.4V,不同频率的正弦波,用本系统进行测量,测试数据如表3所示:表3.扫描速度测试数据3.垂直灵敏度测试测试条件:用信号源输出1KHz,不同幅度的正弦波,用本系统进行测量,测试数据如表4所示:表4垂直灵敏度测试数据*注“?”表示信号噪声较大,无法用TDS1012B示波器精确测量误差是参考TDS1012B的测量值进行计算的4.其他功能测试经测试,波形存储功能及回放、连续触发、触发沿选择、方波校准信号等功能均能正常工作。