基于ARM和FPGA的多通道信号模拟系统设计_麻军伟

基于FPGA+ARM的智能图像门控系统

猛发展 , 得基 于 图像 识 别 的控 制 系统 成 为 现实 l 。 使 1

本文提 出了基于 F G A M 的智能图像 门控系统 , 比 P A+ R 相

于单处理器 的图像 控制 系统 , 具有 实时性好 、 图像算法 实

现简单 、 扩展性强等优 点。

1 系统设 计 方 案

I t l g ntD o r Co r lSy t m s d o FPGA +AR M n el e o nto se Ba e n i

ZHANG i ge , AN Yo g h n , UN L n y n Tn fiF n s e g S igu

(c oo ltn s n opt cn & T ho g ,ohUirto Ci ,a un 301C i , Sh lfE coi dCm u r ic o er ca eSe e e nl yNr n ei h a Ti a 05 ,h c o t vsy f n y 0 a n

b eh d aes u t eo o becnrl r( P yt a w t cu fdu l o o e F GA+AR .T ei a edt ol tdb a r hc scnrl db P A.A da tesme h r r r r t l M) h m g aai cl ce yacmeaw ihi o t l yF G s e oe n t h a

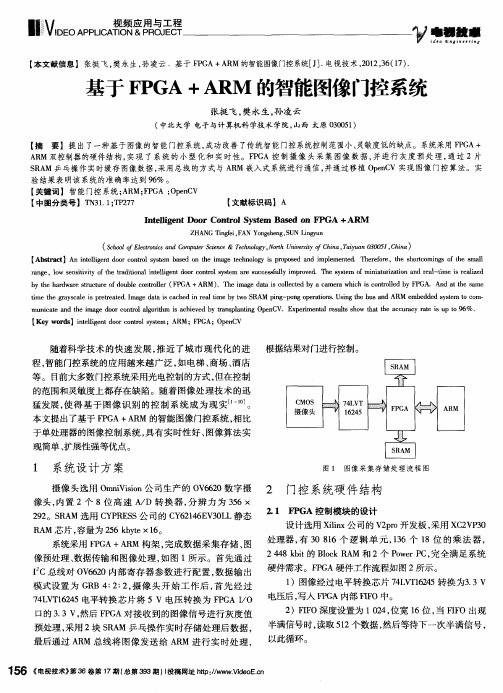

( 中北大学 电子与计算机科学技术学院 , 山西 太原 0 05 ) 3于图像 的智 能门控系统 , 成功 改善 了 统智 能 门控系统控制 范围小 、 传 灵敏度低 的 点。系统采用 FG 缺 P A+ A M 双控制器 的硬件 结构 , R 实现 了系 统 的小 型 化和 实 时性。F G P A控 制 摄像 头采 集 图像 数据 , 并进 行 灰度 预 处 理 , 过 2片 通 S A 乒 乓操 作实 时缓存 图像数据 , RM 采用 总线 的方 式与 A M嵌 入式 系统进 行通信 , R 并通过 移植 O eC 实现 图像 门控算 法。实 pn V 验 结果表 明该 系统 的准确 率达到 9 % 。 6 【 关键词 】 智能 门控 系统 ;R F G ;pnV A M;P A O eC 【 中图分类号】T 3. ;P7 N 11T 27 【 文献标识码】A

基于FPGA的多通道模拟量采集电路设计

基于FPGA的多通道模拟量采集电路设计蔡晓乐;车炯晖;吴斌;荆立雄【期刊名称】《航空计算技术》【年(卷),期】2018(048)002【摘要】针对机载系统多通道模拟量采集处理的要求,研究了基于FPGA的多通道模拟量采集电路的设计.介绍了针对模拟量采集的前端信号调理电路的设计,包括滤波电路和双向限幅电路等.同时研究了利用FPGA控制多级多路模拟开关,通过轮转和多次测量等方法实现模拟信号到数字信号的高精度转换和记录,分析了设计电路的特性,包括高精度、高可靠性和多通道数等优点.最后经过实验测试,系统能够很好地实现多通道模拟量采集的需求,同时具有很高的转换精度.%In allusion to the requirement of multi-channel analog acquisition for airborne system,this pa-per proposes a circuit of multi-channel analog acquisition.A front-end signal conditioning circuit was de-signed for the analogacquisition,including filter circuit and the bipolar diode limitercircuit.Multistage multiplex switches control method with multiple measurements and polling way using FPGA is proposed to realize the conversion and record of analog signal to digital signal.Theoretical analysis shows that the pro-posed circuit has the advantages in acquisition precision,reliability and the multi-channel ability.Experi-mental results show that the system can meet the requirement of multi-channel analog acquisition well and has high conversion accuracy.【总页数】5页(P101-104,108)【作者】蔡晓乐;车炯晖;吴斌;荆立雄【作者单位】航空工业西安航空计算技术研究所,陕西西安710068;航空工业西安航空计算技术研究所,陕西西安710068;航空工业西安航空计算技术研究所,陕西西安710068;航空工业西安航空计算技术研究所,陕西西安710068【正文语种】中文【中图分类】V247.12;TP274【相关文献】1.多通道模拟量采集电路设计探讨 [J], 江耿丰;张兴国;冯丹2.基于FPGA的多通道数据隔离采集电路设计 [J], 张伟;任勇峰;孙涛;程惠3.基于FPGA的多通道信号采集电路设计 [J], 储成君;任勇峰;刘东海;储成群4.基于FPGA的多通道模拟量采集/输出PCI板卡的研制 [J], 徐燕;毛师彬;汤永东;白煊5.基于Cortex-M4医疗设备多通道模拟量采集器的设计 [J],因版权原因,仅展示原文概要,查看原文内容请购买。

基于ARM和FPGA的多通道步进电机控制系统

基于ARM和FPGA的多通道步进电机控制系统杨永清;吴学杰【摘要】提出了一种基于ARM和FPGA的既能同步又能异步的多通道步进电机控制系统设计方案,并完成系统的软件及硬件设计.采用STM32F407和FPGA芯片为核心控制器,选用L297+L298组合作为步进电机的驱动器.以C语言和Verilog HDL语言为开发语言对设计的芯片进行实际测试,采用Delphi 7软件设计控制系统的上位机人机交互界面.【期刊名称】《装备制造技术》【年(卷),期】2017(000)003【总页数】5页(P177-180,189)【关键词】STM32;FPGA;步进电机;Delphi;控制系统【作者】杨永清;吴学杰【作者单位】西南交通大学牵引动力国家重点实验室,四川成都610031;西南交通大学牵引动力国家重点实验室,四川成都610031【正文语种】中文【中图分类】TM383.6随着微电子技术和计算机科学突飞猛进的发展,步进电机因简单和可靠性高越来越多地应用于运动控制系统。

步进电机是一种开环控制电机,在自动控制系统中扮演者重要的角色,是其主要执行元件。

在非超载的情况下,步进电机的转速、停止的位置只取决于脉冲信号的频率和脉冲数,而不受负载变化的影响[1]。

传统的步进电机控制系统多采用单片机和DSP芯片作为其核心,通常以定时器的方式产生控制脉冲[2],因此占用了较为可观的系统资源,脉冲频率更是为微控制器所限制,控制系统和驱动电路的设计复杂且昂贵,并在设计完成后很难再作修改或者灵活应用于其他场合,系统的可移植性比较差,并且难以实现人机交互,控制精度低。

本文提出的基于ARM和FPGA(现场可编程门阵列)的多通道步进电机控制系统实现了人机交互,参数可配置,具有使用灵活、修改方便、简单直观、可靠性高、可移植性强等诸多优点[3]。

多通道步进电机控制系统采用了人机操作界面管理级(PC端上位机)和实时控制级(STM32+FPGA模块),能够同时对8台两相混合式步进电机进行实时控制,使其同步或异步运行。

基于ARM+FPGA+多DSP的嵌入式实时图像处理系统

基于ARM+FPGA+多DSP的嵌入式实时图像处理系统关键字:实时图像处理FPGA FIFO实时图像处理、高速数据运算处理要求其系统具有对数据处理速度快、数据吞吐率高以及多任务处理功能。

目前大多数方案都是采用HPI数据传输方式,将ARM和DSP进行组合完成一些图像处理,DSP处理器只是完成图像采集、压缩、编码等简单的处理[1]工作,不能满足实时的智能识别或大数据量运算的视频处理要求。

在应用领域方面也会因其处理速度问题受到一定的限制。

例如,胎儿性别屏蔽项目中,要对实时视频进行性别部位的检测和屏蔽,若采用单DSP则会出现漏帧或视频不流畅;应用于高速运动物体跟踪时,单DSP无法实现实时运动物体跟踪,例如汉王科技的运动检测和海康威视运动检测,都不能实时检测,即使检测也会出现漏检现象和视频不流畅。

当处理4CIF或者更大图像时,单DSP的处理能力又会下降,虽然可以将图像缩小进行处理,但是缩小图像则会丢失一些重要的图像信息,使得智能识别准确率下降。

针对上述情况,设计一种能够实现进行快速信号处理和数据交换的实时图像处理系统很有必要。

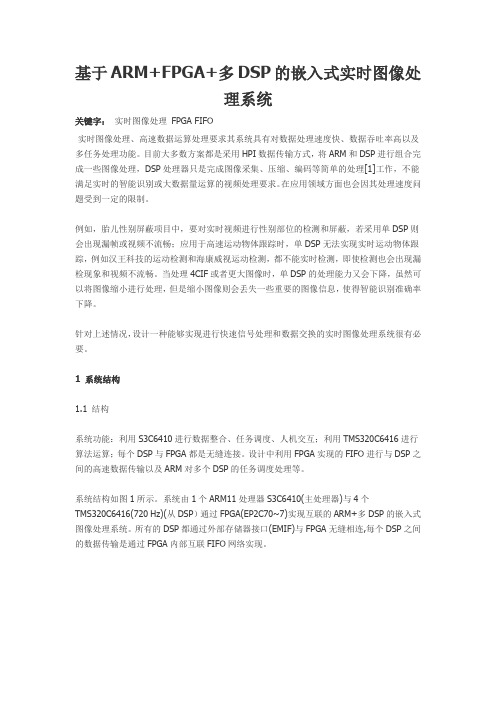

1 系统结构1.1 结构系统功能:利用S3C6410进行数据整合、任务调度、人机交互;利用TMS320C6416进行算法运算;每个DSP与FPGA都是无缝连接。

设计中利用FPGA实现的FIFO进行与DSP之间的高速数据传输以及ARM对多个DSP的任务调度处理等。

系统结构如图1所示。

系统由1个ARM11处理器S3C6410(主处理器)与4个TMS320C6416(720 Hz)(从DSP)通过FPGA(EP2C70~7)实现互联的ARM+多DSP的嵌入式图像处理系统。

所有的DSP都通过外部存储器接口(EMIF)与FPGA无缝相连,每个DSP之间的数据传输是通过FPGA内部互联FIFO网络实现。

图2所示是一种互联的FIFO网络结构和高速数据传输网络结构。

主处理器通过DMA数据访问模式与FPGA的双口FIFO连接,从而实现与FPGA通过FIFO连接的所有从DSP进行通信,所有FIFO都是双向的,FIFO及其读写控制逻辑都在FPGA内部实现。

基于FPGA的多路数字信号编解码器的设计

基于FPGA的多路数字信号编解码器的设计宋若愚;余娟;丁国宁;臧鹏【期刊名称】《计算机与数字工程》【年(卷),期】2013(041)007【摘要】Encoding and decoding technology is important measure in the modem digital communication.In the field of digital communication,coding can improve the transmission efficiency effectively,expanding the amount of data transmission.This paper describes a codec technology,multiplexing signals for voice,data and other FPGA-based implementations of the encoding/decoding method and a detailed description of the design process.%编解码技术是现代数字通信中信息处理的重要手段.在数字通信领域中,编解码技术可以有效的提高传输效率、扩大数据传输量.论文介绍一种编解码技术,基于FPGA对语音、数据等多路不同信号进行编码/解码的实现方法,对设计过程进行了详细的描述.【总页数】3页(P1199-1201)【作者】宋若愚;余娟;丁国宁;臧鹏【作者单位】空军预警学院武汉430019;空军预警学院武汉430019;空军预警学院武汉430019;空军预警学院武汉430019【正文语种】中文【中图分类】TN912.3【相关文献】1.基于FPGA的多路数字信号复分接器的设计 [J], 褚改霞;潘卫;王栋;胡文彬2.基于FPGA的多路数字信号复接系统设计与实现 [J], 赵怡;但涛3.基于多处理器结构的多路话音编解码器设计 [J], 郭巍;倪永婧4.基于FPGA的多路数字信号检测电路实验研究 [J], 高英姿;张伟明5.基于FPGA的曼彻斯特编解码器的设计 [J], 董毅;何刚强;梁汉文;倪凯诚;黄秋月因版权原因,仅展示原文概要,查看原文内容请购买。

基于ARM协调控制的多路信号采集系统

J o u r n a l of W u h a n P o l y t e c h n i c电子与计算机技术基于A R M 协调控制的多路信号采集系统马锐军,袁飞,赵先美(广东技术师范学院,广东广州510665)摘要数据采集是现代工控领域至关重要的一环,应用多处理器的主从控制模式可大大提高信号的采集与处理性能。

32位ARM 处理器进行信号的高速采集与处理,CAN 总线建立的拓扑网络负责多个处理器间数据、命令的有效对接,利用uC /OS -III 实时系统实现信号采集与 处理任务的调度,该模式可增进多个处理器间的协调控制,实现多路信号的采集和远程传输,还能增强系统的实时性和稳定性,同时可最大程度抑制线路传输干扰。

关键词:数据采集;ARM ;协调控制;uC /OS -III 操作系统中图分类号:TP 274.2文献标识码:A 文章编号:1671-931X (2017) 03-0080-04一、弓I 言在医药、化工、食品等领域生产过程中,随着生产 规模、制造过程和制造工艺的不断壮大,自动测试和 各种信息集成的要求也越来越高,为了满足不同的测 试需求,往往需要对系统一些关键信号进行采集与测 量[1]。

尤其在需要同时采集多个模拟通道的应用场合, 要求微机能自动检测多路信道,并进行信号的实时传 输和计算,以“获取和解读”有效信息[2-3]。

目前,国内外 对基于嵌人式的模拟信号采集系统做了大量的研究 工作:采用单个处理器的信号采集系统,其硬件资源 和处理能力有限,对多路模拟信号的采集与处理,效 率相对较低,且实时性能差;多处理器的信号采集系 统中,在不同的应用场合发挥着各自的优势,如基于FPG A 和D S P 的组合、基于A RM 和DSP/FPGA 的组合、基于A RM 和A R M 的组合等,该类系统处理器之 间的分工明确,可协同控制。

FPG A 和D S P 的工作速率快,为纳秒量级,可满足高速信号采样、数据处理和 存储的工作需求,尤其对矩阵处理很有优势,但是其硬件量大,很难做到小体积便携式,且设计复杂,价格高功耗大[4^。

基于FPGA+ARM的多路视频采集系统设计

化 的视 频 信 号 进 行 采 集 和 处 理 , 且 能 应 用 为 系 统 信 号发 生 设 备 。系统 采 用 F GA 为 核 心 高速 时序 逻辑 控制 、 口控 制 单 元 , 而 P 接

加 上嵌入式 AR 强大 的信号采样控 制功能 , M 能够在较低成本下对多路视频信 号进行 快速准确可靠的获取 。

引 言

视频 信号 可 以直观 地显 示 出 目标 物体 的具 体信 息。 视频 采集 在航 空航 天领域 广泛应 用 于 目标 识别 、 测 角测距 和 自动成 像制 导 。视频 采集 系统需 要 对 多

路视 频 信 号进 行严 格 地 时序 控 制 , 同时 要求 采集 生 成 的视 频 信号 与接 收 系 统有 良好 的 匹 配特 性 , 准 不 确 的视 频 采集 会带 来 目标错 误 识 别 、 量误 差 和制 测

关键词 : 路视频采集系统 ,P 多 F GA, M AR

中 图分 类 号 : TN9 5 6 文 献标 识 码 : A

De i n o u t- h nne de q s t o s g f M l ic a lVi o Ac ui ii n

S se b s d o PGA + ARM y tm a e n F

ba e s d FPGA d ARM s p e e e n t a r The v d o a qu sto s t m oton y c n a q r nd an i r s nt d i he p pe . i e c i ii n ys e n l a c uie a

Ab t a t Th e h d o e i n a d i l me t to f t e m u t- h n e i e c u sto y t m sr c : e m t o f d sg n mp e n a i n o h lic a n l v d o a q i i n s s e i

基于FPGA+ARM的多路光栅数据采集系统设计

0 引言光栅编码器作为一种重要的高精度位移测量器件,常用于运动伺服系统中,实现对运动位置的精确反馈[1]。

随着光栅编码器研制技术的发展,其测量精度、速度以及输出信号带宽也越来越高,因此,相应的对光栅信号采集及传输系统提出了更高的要求,要求采集系统具备采集速率高,传输速度快,抗干扰能力强等特点[2]。

传统的光栅数据采集系统多采用单片机或者专用的采集芯片作为处理器,存在采集速率低和灵活性较差的缺点[3]。

在信号传输上多采用RS232、RS485或CAN 等传输方式,存在传输速度低的缺点,并且目前电脑已经逐步淘汰这些接口,给测控系统设计及使用带来较大障碍[4]。

随着“工业4.0”及“互联网+”的发展,对数据的通信传输要求智能化和远程化[5]。

本文提出了一种基于FPGA+ARM 的光栅信号采集及传输系统,充分发挥了FPGA 的并行逻辑控制能力和ARM 的数据处理能力,以TCP/IP 协议完成了对数据的高速稳定传输,使得测控系统接口统一化,实现对数据的远端测控,具有采集速度快、带宽高、传输速度快和稳定等优点,可以完成对光栅数据高速的采集、处理和传输。

1 系统整体结构基于FPGA+ARM 的多路光栅数据采集系统的整体结构如图1所示。

多路光栅的输出信号经过差分转换及隔离电路后进入FPGA 中,FPGA 对多路光栅数据进行数字滤波、同步采集以及数据存储后通过FSMC 总线与ARM 端进行数据通信,ARM 端再以TCP/IP 协议以网口的形式将数据发送至上位机。

图1 系统的整体结构2 系统硬件电路设计2.1 光栅信号预处理电路光栅信号输出为RS422差分信号,输出高电平为5V,FPGA 为低电压逻辑电平,高电平为3.3V,为了便于FPGA 对信号进行采集,需要设计相应的信号调理转换电路将5V 的RS422差分信号转化为LVTTL 电平信号。

本次设计采用AM26LS32差分接收芯片,实现对测头差分信号到单端信号的转换,对信号采用了TLP2362型高速光电耦合器,降低了信号of multiplex grating data at the same time. It takes ARM microprocessor as the core to realize data processing and Ethernet transmission functions. Through the transplantation of Ethernet protocol stack, it realizes Ethernet communication with PC terminal via TCP/IP protocol. Experiments show that the system has good accuracy and stability, and can meet the requirements of raster data acquisition and transmission.Keywords:dataacquisition; FPGA; ARM; TCP /IP图2 STM32与FPGA 接口模块2.3 网络接口设计STM32F407自带以太网模块,只需外界PHY 芯片即可完成以太网通信实现10M/100Mbit/s 的数据传输速率,STM32与外部PHY 芯片使用RMII 接口进行连接,本次设计使用LAN8720A 作为PHY 芯片。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计与应用计算机测量与控制.2011.19(7) Com puter Measurement &C ontrol收稿日期:2010-12-03; 修回日期:2011-01-13。

基金项目:水下信息处理与控制国家级重点实验室基金(9140C2302061001);船舶预研基金(08J3.9.9)。

作者简介:麻军伟(1983-),男,陕西蒲城人,汉,硕士研究生,主要从事控制理论与控制工程方向的研究。

刘卫东(1962-),男,陕西西安人,博士,教授,主要从事计算机测控系统、水下航行器控制与导引系统、计算机网络多媒体方向的研究。

文章编号:1671-4598(2011)07-1767-04 中图分类号:T P302文献标识码:A基于ARM 和FPGA 的多通道信号模拟系统设计麻军伟1,刘卫东1,2,雷 娟1(11西北工业大学航海学院,陕西西安 710072;21水下信息处理与控制国家级重点实验室,陕西西安 710072)摘要:信号模拟系统在设备测试、数据处理等领域都有重要的意义;为了解决设备测试对多通道同步信号的需求,提出了一种基于ARM 和FPGA 的多通道信号模拟系统设计方法,主要介绍了以FPGA 为核心的模拟输出控制模块,其中采用ARM 进行多任务管理,用FPGA 实现时序转换和控制,FPGA 的控制逻辑采用VH DL 和原理图相结合的方法设计,使用FPGA 提高了系统性能并简化了外围电路设计,最后给出了模拟系统的实验结果,整个设计系统可模拟输出多路0101H z~40M H z 的任意信号,说明了这种设计方案的有效性。

关键词:信号模拟;多通道;FPGA;ARMDesign of Multi -channel Signal Simulator Based on ARM and FPGAMa Junw ei 1,Liu Weido ng1,2,Lei Juan1(11Co llege of M arine,No rthw ester n P olytechnica l U niver sity,Xi .an 710072,China;21N atio nal K ey L abo rato ry on U nderw ater Info rmatio n Pro cess and Contr ol,Xi .an 710072,China)Abstract:Signal Simulator is of gr eat importan ce for facility testing,signal proces sing and other field.In order to achieve the demand of m ulti-chann el s ynch ron ou s sign al for facility testing,a design m ethod of M ulti-chan nel Signal Sim ulator based on FPGA and ARM is pres -ented,and the con tr ol m odules of analog output implemented in FPGA are in tr odu ced in detail.ARM is mainly us ed for tasks managem ent and states supervision.FPGA is mainly used for timin g con version and control.C ontrol logic in the circuit design of FPGA combing VHDL w ith principle chart.T he use of FPGA improves the s ystem .s performan ce and s implifies design of the peripheral circuits.Experiment re -s ults demons trate that the n ew design approach for electrical sign al sim ulator is valid.Key words :s ignal s imulator;mu lti-channel;FPGA;ARM0 引言信号模拟系统主要用于对特定信号进行模拟仿真和外场采集数据回放,以进行设备测试或数据分析,在水声、雷达、导航、科研以及教学等领域有着广泛的应用。

目前常用的信号模拟系统大多采用DDS (直接数字合成器)专用集成芯片来实现,这种方法能够很好地模拟正弦、方波等常用简单信号,但其所能模拟的信号参数相对固定、信号形式单一、缺乏足够的灵活性。

另一种是微机程控模拟器,此方案所有信号产生电路全由硬件实现,而计算机只完成简单的指令控制,这种方法实现起来开发周期长,设备利用效率不高。

使用FP GA 作为模拟器核心控制单元,可平衡系统的性能与成本。

美国佛罗里达国际大学在其设计的通用型多通道信号模拟器中,采用单个Xilinx V irtex II P ro FP GA 开发板最为系统核心控制器[1],用其中的DCM (Digital Clock M anag er )产生同步时钟,可模拟几H z 到百M H z 的信号输出。

Ro y T aniza 等人在设计雷达系统的信号模拟器时,使用了单块Xi-linx 高密度F PG A 实现了纯数字式D DS [2],波形的所有数据存储在ROM 中,该模拟器采用外部天线转轴编码器作为内部同步时钟的参考,可模拟40~70M HZ 的中频调制信号,适用于静态或运动的雷达信号源。

目前,用户所需的信号数据量和复杂度越来越大,同时也期望有多路同步信号来联合验证设备。

将嵌入式技术与现代微电子技术结合起来,采用A RM 与F P -G A 来设计信号模拟系统,将是实现高速性、可靠性和高集成度的重要手段。

1 系统总体设计方案111 系统总体结构根据模拟系统功能和成本的要求,这里采用AR M 9和Cy -clo ne II EP 2C8F PG A 为控制核心,用通用计算机作为上位机实现数据生成和状态监控,能够快速精确地模拟16路不同形式和频率的波形信号。

系统可在外部时钟下与外部设备同步工作,也可作为独立的任意信号源,用户通过按键操作实现不同工作模式的切换。

系统的总体结构如图1所示。

图1 系统整体结构图在模拟系统用于外部设备调试验证时,一方面要能够精确模拟多路信号,另一方面还要实时采集外设信息和检测系统工#1767#计算机测量与控制 第19卷作状态,同时还要保障各子设备的顺畅通讯,为了实现多任务的实时调度和管理,设计采用A RM 9作为核心处理器,同时在上位机设计了应用软件来显示和设定状态参数。

系统中AR M 9主要完成整个信号模拟系统的控制,实现信号参数的解算、生成控制参数和部分信号的产生,ARM 9可通过以太网口或U SB 与上位计算机的通信,当脱机运行时,LCD 对主要参数进行监测显示。

在高速数据传输方面,FP GA 具有独特的优势,其片上资源丰富,时钟频率高,内部时延小,所有逻辑控制均以全硬件状态工作。

这里采用A lt era 公司的低成本、低功耗、高密度的Cyclo ne II 系列芯片作为模拟输出核心控制器。

112 系统工作原理信号模拟系统在上电自检结束后,先由A RM 采集外部设备信号和8路模式开关信号,根据工作模式选择相应的同步时钟,并设置FP A G 的控制寄存器。

当上位机连接时,AR M 接收上位机传来的波形数据,否则根据当前模式选择SD 卡中的波形数据,同时在FP GA 读写控制逻辑的配合下,依次将波形数据存储在与各通道对应的SR AM 存储器中,波形数据下载结束后,FPG A 将数据由SRA M 读出并送至高速DA C 进行同步模拟输出。

2 以FPG A 控制核心的输出模块设计211 模拟输出模块功能结构模拟输出模块是实现波形数据存储和同步输出控制的重要部分,主要由F PG A 核心控制器、大容量St atic R AM 、高速DAC 模组、波形调理输出单元和其他外围电路组成,其功能结构如图2所示。

设计中采用了Cypress 公司的256k @16SR AM 作为数据存储器,它具有读写速度快、存储容量大等优点,可很好地配合高速FP GA 的操作。

数模转换器采用LI NER 公司LT C1668芯片,这是一种16位75M SPS 的差分电流输出DA 转换器,其输出可直接连接到高速运算放大器上,最后经信号调理后输出。

根据系统的设计要求,选择了A ltera 公司的Cy clo ne II EP2C8Q F PG A 作为信号模拟输出的核心控制器。

该器件内部有2个锁相环(P L L)和8个全局时钟网络,8256个逻辑单元(L E)个,36个M 4K RA M ,18个乘法器模块,可用I/O 数138个,EP2C8Q 具有低成本、高性能、低功耗和对IP -P BX 系统的可扩展性(足够多的I/O 接口)的优点,非常适合多IO 口的逻辑控制。

FP GA 作为输出核心控制器,主要用来接收A RM 下载的波形数据并存储在外部SRA M 中,在进行波形模拟输出时,实现数据读取和DA C 的转换控制。

F PG A 逻辑设计采用VH DL 和原理图混编的方式,先通过VH DL 实现各个模块功能,在由编辑器生成Symbol 模块,再用顶层原理图方式完成各个Symbol 模块的对接设计。

采用这种方法实现设计,其结构清晰、高效方便。

FPG A 内部功能结构如图2虚线框所示,主要由片选译码器、同步时钟单元、读写控制器、配置寄存器组等模块组成。

212 FPGA 控制模块工作流程FP GA 控制模块的操作时序如图3所示。

在控制寄存器中设置了S _R (SRA M _REA DY)、S _B (SRA M _BU SY)两图2 FPGA 控制模块功能结构个信号,主要用于FPG A 和A RM 的通信握手。

当S _R 为低电平时,F PG A 根据A RM 的读写信号产生对SRA M 的操作时钟,配合AR M 完成波形数据的下载;下载完成后,S _R 置高,F PG A 在IN T 有效沿信号的触发下,开始延时并进行波形的模拟输出。

当FPG A 对波形数据帧进行操作时,设置S _B 为高以禁止A RM 的操作,从而保证了信号的完整性和系统的安全性。

图3 FPGA 控制模块操作时序213 同步时钟模块为保证各通道信号输出的同步性,这里采用了Cyclo ne II 的全局时钟驱动网络。