8.13多进制数字频率调制(MFSK)系统

多进制数字相位调制(MPSK)系统

AbstractMultiple Phase Shift Keying (MPSK - multiple phase shift keying) is also called multi-phase system, which is the promotion of the two-phase system. It is the modulation to characterize digital information using the different carrier’s phase state. Similar with the Binary Digital Phase Modulation, it has the absolute phase modulation (MPSK) and phase modulation (MDPSK) as the two kinds of modulation methods.This article is mainly about the Multiple Phase Shift Keying system (MPSK) based on Xilinx ISE simulation software design, setting 4PSK as an example. The modulation method is the simple phase-selection method. It only concentrates on the design of digital system, neglecting the analog circuit system.Keywords: Multiple Phase Shift Keying MPSK Xilinx ISEphase-selection method摘要多进制数字相位调制(MPSK - multiple phase shift keying)又称多相制,是二相制的推广。

多进制数字振幅调制(MASK)系统

--计数器 --计数器 --并行数据寄存器 --8位DAC数据寄存器

process(clk) --此进程完成基带信号的串并转换, --完成4位并行数据到8位DAC数据的译码 begin if clk'event and clk='1' then if start='0' then q<=0; elsif q=0 then q<=1;xx(3)<=x; if xx(3)='1' then yy<=xx&"1111"; --if语句完成4位并行数据到8位DAC数据转换 elsif xx(2)='1' then yy<=xx&"1011"; elsif xx(1)='1' then yy<=xx&"0111"; elsif xx(0)='1' then yy<=xx&"0011"; else yy<=xx&"0000"; end if; elsif q=2 then q<=3;xx(2)<=x; elsif q=4 then q<=5;xx(1)<=x; elsif q=6 then q<=7;xx(0)<=x; else q<=q+1; end if; end if; end process;

MASK调制程序仿真图及注释

(MASK调制VHDL程序仿真仿真全图)

(MASK调制VHDL程序仿真局部放大图)

MASK调制电路VHDL程序与仿真

MASK调制方框图

通信原理期末考试重要知识点2

多进制数字调制系统多进制数字调制具有以下两个特点:(1)在相同的码元传输速率下,多进制数字调制系统的信息传输速率比二进制高。

Rb=RB2 bit/sRb=logN bit/s(2) 在相同的信息传输速率下,多进制数字调制系统的码元传输速率比二进制低,, BN<B2可增加码元的能量,减小干扰的影响。

1. 多进制数字振幅调制(MASK)(1)多进制数字振幅调制的原理。

——多进制数字振幅调制又称多电平调制。

*MASK表示式: (波形)eASK=bn=P1+P2+……..PM=1(2) 系统的带宽: BASK =(3)单位频带内有超过2bit/s.Hz的信息传输速率。

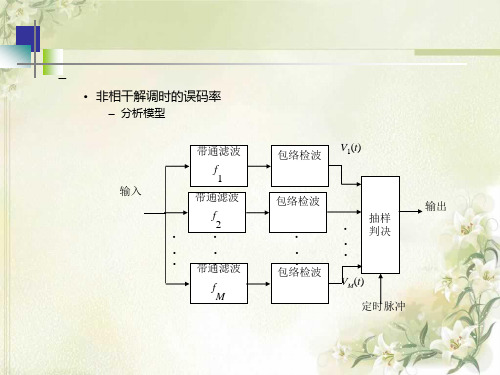

2. 进制数字频率调制(MFSK)(1)多进制数字频率调制的原理——MFSK调制简称多频制,是二进制数字频率键控方式的直接推广。

(2) 一个多频制系统的组成方框如图:●带通滤波器的中心频率就是多个载频的频率。

●抽样判决器-----在给定时刻上比较各包络。

(3) MFSK系统带宽:BFSK=|fM-fl|+ΔfΔf单个码元宽度。

3. 多进制数字相位调制(MPSK)(1) 多进制数字相位调制的原理——多进制数字相位调制又称多相制。

*利用载波的多种不同相位(或相位差)表征数字信息的调制方式。

也可分为绝对移相(MPSK)和相对(差分)移相(MDPSK)两种。

*多进制相位调制: M=2k K位码元。

一个相位表示K位二进码元.*以四相制为例(2) QPSK(QDPSK)信号调制的原理(A)QPSK:定义:用载波的四种不同相位来表征数列中的信息。

两个信息比特与载波相位关系如下,分为A方式, B方式。

(B) QDSK:定义:利用前后码元之间的相对相位变化来表示数字信息。

以前一码元相位作为参考,并令Δ为本码元与前一码元的初相差。

信息比特与载波相位变化Δ的关系如上所示,分为A方式, B方式。

(C) 波形:(D) 表达式:ePSK ==式中:——受调相位。

M进制用M种不同相位来表征。

多进制数字频率调制MFSK

• 非相干解调时的误码率

– 分析模型 带通滤波 f 输入 1 包络检波 输出 V1(t)

包络检波

带通滤波 f

. .

. . 带通滤波

f M

2

包络检波

. .

. .

VM(t)

抽样 判决

定时脉冲

有信号码元输出的带通滤波器的输出电压包络服从广义瑞利分布 :

p(x) x

2 n

Ax I0 2 n

exp( kr b / 2 )

在上式中若用M代替(M-1)/2,不等式右端的值将增大,但是此不 等式仍然成立,所以有

P e M exp( kr b / 2 )

这是一个比较弱的上界,但是它可以用来说明下面的问题。

A 2

2 2 n

M 1

Pe e

M 1

n 1

( 1)

n 1

Pb 2 2

k k 1

1

Pe

Pe 2 [1 (1 / 2 )]

k

当k很大时,

Pb P e / 2

– 误码率曲线

Pe

(a) 非相干解调

rb

• 相干解调时的误码率 –计算结果给出如下:

Pe 1 1 2

e

A

2

/2

1 2

A

2r

e

u

2

/2

du

上式是一个正负项交替的多项式,在计算求和时,随着项数增加 ,其值起伏振荡,但是可以证明它的第1项是它的上界,即有 上式可以改写为

M 1 2

A

2

Pe

e

/ 4

2363《通信原理》自学考试大纲1

《通信原理》(2363)自学考试大纲一、课程性质与设置目的(一)课程性质、地位与任务通信原理是高等教育自学考试通信工程专业的一门重要的专业课程。

本课程的任务是学生通过学习现代通信系统所涉及的基本原理、基本技术,掌握数字数据通信的系统构成、工作原理和主要性能指标。

(二)本课程的基本要求1. 理解通信系统的基本模型、基本指标、信息、信道、传输介质、通信方式、差错控制、信号及噪声等基本概念和基本原理。

2. 理解模拟调制的基本原理。

3. 掌握数字数据传输的基本原理和技术。

4. 掌握不同传输方式通信系统的噪声性质,并进行分析和比较。

5. 掌握复用技术和多址技术的基本原理。

6. 掌握通信网的基本理论。

7. 掌握通信系统中不同同步方式的原理和作用。

8. 学生在自学过程中应按大纲要求,仔细阅读教材,切实掌握有关内容的基本概念、基本原理和基本方法。

(三)本课程与相关课程的联系与分工本课程是自学考试计划中通信工程专业一门重要专业课程。

要学好本课程,必须具有“电路与电子技术”“工程数字”等课程的基本知识。

二、课程内容与考核目标第一章绪论(一)学习目的与要求要求学生能理解通信系统模型的基本原理,理解信息及其度量、信道与信道容量的基本概念,掌握不同类型传输介质的特性,掌握不同通信方式及差错控制的基本原理,掌握通信系统主要性能指标。

(二)课程内容第一节通信系统模型:通信系统模型及各组成部分模拟通信系统模型数字通信系统模型第二节信息及其度量:信息信息量第三节信道与信道容量:信道信道容量传输介质传输介质的分类通信系统中常用的传输介质第四节通信方式:串行传输和并行传输同步传输和异步传输单工、半双工和全双工传输第五节差错控制:差错产生的原因差错的类型差错控制第六节通信系统的主要性能指标:模拟通信系统的有效性和可靠性的衡量数字通信系统的有效性和可靠性的衡量–1–(三)考核知识点1. 通信系统模型的组成2. 信息及信息量的概念3. 信道及信道容量的概念、传输介质的分类4. 串行传输与并行传输、单工传输、半双工传输和全双工传输、同步传输和异步传输的基本原理5. 差错产生的原因及差错类型、差错控制的基本原理6. 通信系统的性能指标:可靠性和有效性(四)考核要求1. 通信系统模型的组成:通信系统模型、模拟通信系统原理、数字通信系统模型,达到“领会”层次。

现代通信技术-多进制数字调相(MPSK)

03. 4PSK信号的产生与解调

4PSK利用载波的四种不同相位来表征数字信息。

由于每一种载波相位代表两个比特信息,故每个四进制码元又被称为双比特码元,

习惯上把双比特的前一位用代表,后一位用代表。

双比特码元 载波相位(φn )

a

0 1

0 3150

1

0

1

1

x

带通 滤波 低通 滤波 抽样 判决 码反 变换 抽样 判决 并/串 变换

cos c t sin c t

位定时

输出

输入

x

载波 恢复

低通 滤波

04. 4DPSK信号的产生与解调

4DPSK信号的差分相干解调方式原理如图所示。

低通 滤波 抽样 判决 并/串 变换 抽样 判决

x

带通 滤波

延迟Ts

双比特码元 a 0 1 1 0 b 0 0 1 1 载波相位变化 (Δφn ) 00 900 1800 2700

04. 4DPSK信号的产生与解调

与2DPSK信号的产生相类似,在直接调相的基础上加码变换器,就可形成4DPSK信号。

4DPSK信号(A方式)产生方框如图的所示。

x c 输入

串/并 变换

多进制数字调相

目录

01

多进制调相的概念

02

03

MPSK信号的频谱及带宽

4PSK信号的产生与解调

04 4DPSK信号的产生与解调

01.多进制调相的概念

多进制数字相位调制又称多相制,是二相制的推广。

它是利用载波的多种不同相位状态来表征数字信息的调制方式。

与二进制数字相位调制相同,多进制数字相位调制也有绝对相 位调制(MPSK)和相对相位调制(MDPSK)两种。

mfsk的误码率 -回复

mfsk的误码率-回复MFSK (Multiple Frequency Shift Keying)是一种数字调制技术,广泛应用于无线通信中。

作为无线通信的关键参数之一,误码率(Bit Error Rate,BER)在评估通信系统的性能时起着至关重要的作用。

本文将一步一步回答关于MFSK的误码率的问题,旨在帮助读者深入了解MFSK系统的性能评估。

第一步:了解MFSK调制技术MFSK是一种基于频率偏移的调制技术,它将不同数量的频率划分为不同的数字符号,用于表示数字信息。

MFSK系统中,发送端通过对不同数字符号(也称为音调)施加频率偏移,将数字信息编码为频率序列。

接收端通过解调过程,将接收到的信号转换回数字信息。

MFSK调制技术广泛应用于许多应用领域,包括无线电通信、调频广播和数据传输等。

第二步:理解误码率(BER)的定义误码率是衡量数字通信系统性能的重要参数之一,它表示在传输过程中每一位(bit)上出现错误的概率。

误码率通常用一个小数表示,例如,1e-3 表示每1000个bit中平均有一个bit出错。

低误码率意味着通信质量好,传输可靠性高。

第三步:了解误码率的计算方法误码率的计算涉及到多个因素,如信噪比(SNR)、调制技术以及信道状态等。

对于MFSK系统,误码率通常可以使用理论分析方法或仿真方法来计算。

理论分析方法是基于概率论和统计学原理,通过计算每个符号的误码率,并根据信号传输过程中的错误积累确定整个系统的误码率。

误码率的计算通常需要考虑噪声的影响以及调制技术的特性。

仿真方法是通过模拟信道传输过程,随机生成符号序列,并将其经过实际信道传输和接收处理。

利用误码率的统计平均值可以得到系统的误码率。

仿真方法可以更准确地估计实际系统的性能,但计算复杂度较高。

第四步:MFSK的误码率计算MFSK的误码率计算与调制技术和信道条件有关。

MFSK中最常用的是二进制频移键控(Binary Frequency Shift Keying,BFSK)和多进制频移键控(Multi-ary Frequency Shift Keying,MFSK)。

多进制数字调制系统

多进制数字调制系统摘要: 一、多进制幅度调制原理及抗噪声性能M 电平调制信号的时间表达式为: 式中且有4ASK 信号的波形图1 4ASK 信号的波形图(b)所示的4ASK 信号波形可以等效成图(c)中四种波形之和,其中三种波形都分...一、多进制幅度调制原理及抗噪声性能M 电平调制信号的时间表达式为: 式中且有4ASK 信号的波形图1 4ASK 信号的波形图(b)所示的4ASK 信号波形可以等效成图(c)中四种波形之和,其中三种波形都分别是一个2ASK 信号。

这就是说,MASK 信号可以看成是由振幅互不相等、时间上互不相容的个2ASK 信号相加而成。

其中是多进制码元速率。

频带利用率若以信息速率来考虑频带利用率,则有它是2ASK 系统的倍。

这说明在信息速率相等的情况下,MASK 系统的频带利用率高于2ASK 系统的频带利用率。

MASK 信号的解调与2ASK 相同,可以使用相干解调和非相干解调的方法来恢复基带信号。

采用相干解调时,MASK 信号的误码率与电平基带信号的误码率相同,即其中为信噪比,,为信号功率,为噪声功率。

MASK 信号有以下几个特点:(1)传输效率高。

与二进制相比,当码元速率相同时,多进制调制的信息速率比二进制的高,是二进制的倍。

在相同信息速率的情况下,MASK 系统的频带利用率也是2ASK 系统的倍。

(2)在接收机输入平均信噪比相等的情况下,MASK 系统的误码率比2ASK系统要高。

(3)抗衰减能力差。

只适宜在恒参信道中使用。

(4)进制数越大,设备越复杂。

二、多进制频率调制原理及抗噪声性能多进制数字频率调制(MFSK)基本上是2FSK 方式的推广。

它是用多个频率的载波分别代表不同的数字信息。

MFSK 通信系统原理方框图如图2 所示。

图2 MFSK 系统的原理方框图与2ASK 信号相同,可将MFSK 信号等效为个2ASK 信号相加,它的相邻载波频率间隔应大于进制码元速率的二倍,否则接收端的带通滤波器无法将各个2ASK 信号分离开。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

这种方式产生的MFSK信号的相位是不连续的,可 看作是M个振幅相同、载波不同、时间上互不相容 的二进制ASK信号的叠加。 因此其带宽

其中fH为最高载频;fL为最低载频;fS为码元速率。

MFSK调制电路VHDL程序及仿真

MFSK调制方框图

FPGA

clk start

f3

串/并转换

分频

f2 f1 f0 调制信号

因此,当一组组二进制码输入时,加法器的输出便 是一个MFSK波形。接收部分由多个中心频率为f1、 f2、….fM的带通滤波器、包络检波器及一个抽样判 决器、逻辑电路、并/串变换电路组成。 当某一载频来到时,只有相应频率的带通滤波器能 收到信号,其它带通滤波器输出都是噪声。 抽样判决器的任务就是在某一时刻比较所有包络检 波器的输出电压,判断哪一路的输出最大,以达到 判决频率的目的。 将最大者输出,就得到一个多进制码元,经逻辑电 路转变成k位二进制并行码,再经并/串变换电路转 换成串行二进制码,从而完成解调任务。

process(clk,yy) --此进程完成对输入基带信号x的MFSK调制 begin if clk'event and clk='1' then if start='0' then y<='0'; -- if语句完成2位并行码到4种载波的选通 elsif yy="00" then y<=not f(3); elsif yy="01" then y<=not f(2); elsif yy="10" then y<=not f(1); else y<=not f(0); end if; end if; end process; end behav;

process(clk) --对输入的基带信号x进行串/并转换,得到2位并行信号的yy begin if clk'event and clk='1' then if start='0' then q<=0; elsif q=0 then q<=1;xx(1)<=x;yy<=xx; elsif q=8 then q<=9;xx(0)<=x; else q<=q+1; end if; end if; end process;

signal q :integer range 0 to 15; --计数器 signal f :std_logic_vector(3 downto 0); --分频器 signal xx:std_logic_vector(1 downto 0); --寄存输入信号x的2位寄存器 signal yy:std_logic_vector(1 downto 0); --寄存xx信号的寄存器 begin process(clk)--此进程对clk进行分频,得到4种载波信号f3、f2、 f1和f0 begin if clk'event and clk='1' then if start='0' then f<="0000"; elsif f="1111" then f<="0000"; else f<=f+1; end if; end if; end process;

MFSK信号除了上述解调方法之外,还可采用分路 滤波相干解调方式。 此时,只需将上张图中的包络检波器用乘法器和 低通滤波器代替即可。 但各路乘法器需分别送入不同频率的相干本地载 波。 MFSK系统提高了信息速率,误码率与二进制相比 却增加不多,但占据较宽的频带,因而频带利用 率低,多用于调制速率不高的传输系统中。

MFSK调制VHDL程序仿真图及注释

(MFSK调制VHDL程序仿真全图)

注:中间信号yy与输出调制信号y的对应关系: “00”=f3;“01”=f2;“10”=f1;“11”=f0。 (MFSK调制VHDL程序仿真局部放大图1)

(MFSK调制VHDL程序仿真局部放大图2)

(MFSK调制VHDL程序仿真局部放大图3)

图中串/并变换电路和逻辑电路将输入的二进制 码转换成M进制的码,将输入的二进制码每k位分 为一组,然后由逻辑电路转换成具有多种状态的 多进制码。 控制相应的M种不同频率振荡器后面所接的门电路, 当某组二进制码来到时,逻辑电路的输出一方面 打开相应的门电路,使该门电路对应的载波发送 出去,同时关闭其它门电路,不让其它载波发送 出去。 每一组二元制码(log2M位)对应一个门打开,因 此信道上只有 M种频率中的一种被送出。

基带信号

四选一开关

注:电路符号图中没有包含模拟电路部分,输出信号为数字信号。 基带信号x通过串/并转换得到2位的并行信号。 四选一开关根据2位并行信号选择相应的载波输出。

MFSK调制电路符号

MFSK调制VHDL程序及仿真

--文件名:MFSK --功能:基于VHDL硬件描述语言,完成对基带信号的MFSK调制 --说明:这里MFSK的M为4 --最后修改日期:2004.2.13 library ieee; use ieee.std_logic_arith.all; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity MFSK is port(clk :in std_logic; --系统时钟 start :in std_logic; --开始调制信号 x :in std_logic; --基带信号 y :out std_logic); --调制信号 end MFSK; architecture behav of MFSK is

8.13多进制数字频率调制(MFSK)系统

多进制数字频率调制(MFSK)

多进制数字频率调制也称多元调频或多频 制。 M频制有M个不同的载波频率与M种数字信 息对应,即用多个频率不同的正弦波分别 代表不同的数字信号,在某一码元时间内 只发送其中一个频率。

(多频制系统(MFSK)原理框图)