四位二进制除法器

计算机组成原理4位二进制计数器实验报告

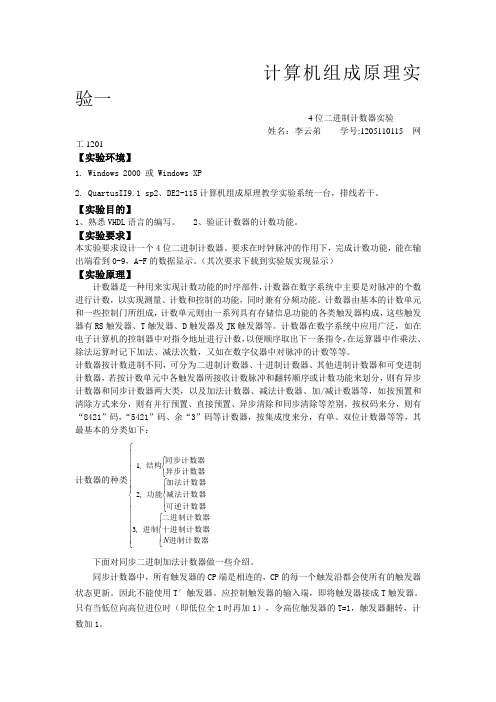

计算机组成原理实验一4位二进制计数器实验姓名:李云弟 学号:1205110115 网工1201【实验环境】1. Windows 2000 或 Windows XP2. QuartusII9.1 sp2、DE2-115计算机组成原理教学实验系统一台,排线若干。

【实验目的】1、熟悉VHDL 语言的编写。

2、验证计数器的计数功能。

【实验要求】本实验要求设计一个4位二进制计数器。

要求在时钟脉冲的作用下,完成计数功能,能在输出端看到0-9,A-F 的数据显示。

(其次要求下载到实验版实现显示)【实验原理】计数器是一种用来实现计数功能的时序部件,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。

计数器由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS 触发器、T 触发器、D 触发器及JK 触发器等。

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

计数器按计数进制不同,可分为二进制计数器、十进制计数器、其他进制计数器和可变进制计数器,若按计数单元中各触发器所接收计数脉冲和翻转顺序或计数功能来划分,则有异步计数器和同步计数器两大类,以及加法计数器、减法计数器、加/减计数器等,如按预置和清除方式来分,则有并行预置、直接预置、异步清除和同步清除等差别,按权码来分,则有“8421”码,“5421”码、余“3”码等计数器,按集成度来分,有单、双位计数器等等,其最基本的分类如下:计数器的种类⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎨⎧⎪⎩⎪⎨⎧⎪⎩⎪⎨⎧⎩⎨⎧进制计数器十进制计数器二进制计数器进制可逆计数器减法计数器加法计数器功能异步计数器同步计数器结构N 、、、321 下面对同步二进制加法计数器做一些介绍。

同步计数器中,所有触发器的CP 端是相连的,CP 的每一个触发沿都会使所有的触发器状态更新。

基于FPGA的4位二进制数除法器设计

基于FPGA的4位⼆进制数除法器设计1. 设计要求: 设计⼀个4位⼆进制数除法器,如下图所⽰。

其中,a[3:0]为被除数,b[3:0]为除数,s[3:0]为商,r[3:0]为余数。

2. 设计原理: 和⼗进制除法类似,以计算 27 除以 5 的过程为例:除法运算过程如下:(1) 取被除数的⾼⼏位数据,位宽和除数相同(实例中是 3bit 数据)。

(2) 将被除数⾼位数据与除数作⽐较,如果前者不⼩于后者,则可得到对应位的商为 1,两者做差得到第⼀步的余数;否则得到对应的商为0,将前者直接作为余数。

(3) 将上⼀步中的余数与被除数剩余最⾼位 1bit 数据拼接成新的数据,然后再和除数做⽐较。

可以得到新的商和余数。

(4) 重复过程 (3),直到被除数最低位数据也参与计算。

需要说明的是,商的位宽应该与被除数保持⼀致,因为除数有可能为1。

所以上述⼿动计算除法的实例中,第⼀步做⽐较时,应该取数字 27最⾼位 1 (3’b001) 与 3’b101 做⽐较。

根据此计算过程,设计位宽可配置的流⽔线式除法器,流⽔延迟周期个数与被除数位宽⼀致。

3. 设计实现module divider_4bit(input wire [3:0] a,input wire [3:0] boutput wire [3:0] s,output wire [3:0] y);wire [3:0] part_0;wire [3:0] part_1;wire [3:0] part_2;wire [3:0] part_3;assign s[3] = a[3] >= b; //最⾼位的商s[3]assign part_3 = (s[3] == 1'b1 )? a[3] - b : a[3];assign s[2] = {part_3, a[2]} >= b;assign part_2 = (s[2] == 1'b1) ? {part_3, a[2]} - b : {part_3, a[2]};assign s[1] = {part_2, a[1]} >= b;assign part_1 = (s[1] == 1'b1) ? {part_2, a[1]} - b : {part_2, a[1]};assign s[0] = {part_1, a[0]} >= b;assign part_0 = (s[0] == 1'b1) ? {part_1, a[0]} - b : {part_1, a[0]};assign y = part_0;endmodule4. 仿真验证`timescale 1ns/1psmodule divider_4bit_tb();reg [3:0] a;reg [3:0] b;wire [3:0] s;wire [3:0] y;wire [3:0] tb_s;wire [3:0] tb_y;assign tb_s = a / b;assign tb_y = a % b;divider_4bit divider_4bit_inst (.a (a),.b (b),.s (s),.y (y));initial beginrepeat(20)begina = {$random} % 16;b = {$random} % 16;# 20;endendendmodule注:0/0=⽆穷⼤,任何数除以零(⽆穷⼩)得⽆穷⼤,⽽在Veriog中,默认0/0=错误结果,s[3:0]最⼤值为15。

计算机组成原理四位无符号除法

计算机组成原理四位无符号除法无符号整数是一种没有正负符号的整数表示方式,可以表示从0到2的n次方减1的整数范围。

对于四位无符号整数,其范围是0到2的4次方减1,即0到15在计算机中进行四位无符号除法运算时,首先需要对被除数和除数进行二进制表示。

四位无符号整数可以用四位二进制数表示,例如被除数可以表示为D3D2D1D0,除数可以表示为d3d2d1d0。

其中,D3表示最高位(最高权重)的二进制位,D0表示最低位(最低权重)的二进制位。

四位无符号除法的过程可以用以下步骤来描述:1.将被除数D3D2D1D0和除数d3d2d1d0对齐,即将它们的最高位对齐。

2.初始化商Q和余数R为全0,将被除数D3D2D1D0赋值给余数R。

3.从左到右进行除法运算,即从最高位开始。

a)将余数R的最高位与除数的最高位进行比较:-如果余数的最高位小于除数的最高位,那么将商的最高位置为0。

-如果余数的最高位大于或等于除数的最高位,那么将商的最高位置为1,并将余数的最高位与除数的最高位进行减法运算。

b)将商的最高位与余数的次高位进行比较:-如果商的最高位小于余数的次高位,那么将商的次高位置为0。

-如果商的最高位大于或等于余数的次高位,那么将商的次高位置为1,并将商的次高位与余数的次高位进行减法运算。

c)重复上述比较和减法运算,直到处理完所有的二进制位。

4.最终得到的商就是四位无符号除法的结果。

以上描述的是四位无符号除法的基本过程,其中涉及到的比较和减法运算可以用计算机中的逻辑运算和算术运算来实现。

总结起来,四位无符号除法是通过对齐被除数和除数,从最高位开始逐位进行比较和减法运算,得到商的过程。

这个过程是计算机运算中的基本操作,对于理解和设计计算机系统具有重要意义。

4bitalu加法器工作原理

4bitalu加法器工作原理

4位二进制加法器(4-bit binary adder)是一种电子电路,用于将两个4位二进制数相加。

最常见的4位二进制加法器是基于全加器(Full Adder)的设计。

以下是4位二进制加法器的工作原理:

输入:

4位二进制加法器有两个4位的输入,通常表示为A和B。

每一位都可以是0或1。

全加器:

4位二进制加法器由4个全加器组成,每个全加器都用于处理对应位的加法。

全加器的结构:

每个全加器包括三个输入:A的对应位(Ai)、B的对应位(Bi)和前一位的进位(Ci-1)。

输出包括两个部分:当前位的和(Si)和传递到下一位的进位(Ci)。

第一位的处理:

第一位的全加器只有两个输入,即A0和B0,因为没有前一位的进位。

输出为第一位的和(S0)和传递到第二位的进位(C1)。

中间位的处理:

对于中间的三位,每个全加器都有三个输入(Ai、Bi、Ci-1)和两个输出(Si、Ci)。

输出的和(Si)作为当前位的二进制和。

输出的进位(Ci)传递到下一位的进位输入(Ci-1)。

最后一位的处理:

最后一位的全加器输出的和(S3)和进位(C4)即为4位二进制数相加的结果。

进位检测:

如果最后一位的全加器输出的进位(C4)为1,则表示溢出。

输出:

4位二进制加法器的输出为一个4位的二进制数,其中每一位都是相应位的和。

总体而言,4位二进制加法器通过级联多个全加器,逐位相加并处理进位,实现对两个4位二进制数的加法运算。

这种结构也可以扩

展到更多位数的二进制加法器。

二进制运算器

二进制运算器二进制运算是在计算机科学中非常重要的一部分,尤其在逻辑电路设计、编程、计算机网络等领域都有广泛的应用。

因此掌握二进制运算器的使用方法,对于学习这些领域的人来说是至关重要的。

二进制是一种仅使用0和1两个数字的计数系统。

在二进制系统中,每一位数字都表示一个2的幂次方。

例如,二进制中的第0位表示2的0次方,即1,第1位表示2的1次方,即2,第2位表示2的2次方,即4,以此类推。

因此一个二进制数的每一位都可以用以下公式计算:数字*2的指数。

二进制运算器可以执行四个基本运算:加、减、乘、除。

以下将详细介绍每种运算方法。

加法:二进制加法与十进制加法类似,只不过需要考虑进位的问题。

当两个位都是1时,需要进位1。

由于进位可能会一直传递到最高位,因此在二进制加法中需要多增加一位来处理进位。

例如,2+3=5,而二进制中的10+11=101。

减法:二进制减法同样需要考虑借位的问题。

当从一个数字中减去另一个比其更大的数字时,需要从高位到低位依次向下借位。

例如,7-3=4,而二进制中的1110-101=101。

乘法:二进制乘法如同十进制乘法一样,需要用到竖式计算。

并且在逐位相乘的同时需要考虑进位的问题。

例如,3*5=15,而二进制中的11*10=110。

除法:二进制除法同样需要用到除法的竖式计算。

而且在进行二进制除法的时候,需要对被除数进行左移或者右移来保证能够与除数相匹配。

例如,10/2=5,而二进制中的1010/10=101。

总结来说,掌握二进制运算器的使用方法对于学习计算机科学、电路设计以及编程来说是必不可少的。

尤其在处理二进制和十六进制数据时,二进制运算器能够节约大量的时间和精力。

因此,我们需要不断地学习、练习,掌握二进制运算的技巧,提高自己的计算能力。

EDA四位二进制除法器设计报告

沈阳航空航天大学课程设计(说明书)4位二进制除法器的设计班级 / 学号学生姓名指导教师常丽东沈阳航空航天大学课程名称数字逻辑课程设计院(系)计算机学院专业计算机科学与技术班级学号姓名课程设计题目4位二进制除法器的设计课程设计时间: 2011 年07 月11 日至2011 年07 月24 日课程设计的内容及要求:一、设计说明设计一个4位二进制除法器,可以存贮其商和余数。

电路原理框图如图1所示。

除法器可以利用减法器和寄存器实现。

图1 乘法器原理框图寄存器A、B、C及R分别存放被除数、除数、商及余数。

比较器用来判断“余数”和除数的大小,即比较R寄存器和B寄存器的内容来确定商,用S2表示判断的结果,R≥B,S2=1;R<B,S2=0。

计数器P用来累计运行次数,当P=4时,除法结束。

二、技术指标1.设计4位二进制除法器。

输入数据:被除数X(0000~1111);除数Y(0001~1111)。

输入命令:启动信号S1,高有效。

输出数据:商数C(0000~1111),余数R(R<Y)2.存贮其商和余数。

三、设计要求1.在选择器件时,应考虑成本。

2.根据技术指标通过分析计算确定电路形式和元器件参数。

3.主要器件:(1)74LS74双D触发器;(2)74LS194双向移位的寄存器;(3)74LS283加法器;(4)74LS163计数器;(5)74LS00、74LS04等门电路。

四、实验要求1.根据技术指标制定实验方案;验证所设计的电路。

2.进行实验数据处理和分析。

五、推荐参考资料1.谢自美. 电子线路设计·实验·测试. [M]武汉:华中理工大学出版社,2000年2.阎石. 数字电子技术基础. [M]北京:高等教育出版社,2006年3.付家才. 电子实验与实践. [M]北京:高等教育出版社,2004年六、按照要求撰写课程设计报告指导教师年月日负责教师年月日学生签字年月日成绩评定表一、设计概述要求设计一个四位二进制除法器,要求被除数的最大值位1111,最小值为0000。

4位同步二进制加法计数器计数最大值

4位同步二进制加法计数器是一种常见的数字电路,用于实现二进制计数。

它可以将二进制数字表示为电信号,并且在每次输入脉冲时进行递增。

下面将详细介绍4位同步二进制加法计数器及其计数的最大值。

一、4位同步二进制加法计数器的原理1. 4位同步二进制加法计数器由4个触发器组成,每个触发器对应一个二进制位。

当输入一个脉冲时,每个触发器根据前一位的状态以及输入脉冲的信号进行状态转换。

这样就实现了二进制数的递增。

2. 触发器之间通过门电路连接,用于控制触发器状态的变化。

这些门电路可以根据具体的设计选择不同的逻辑门,常见的有AND门、OR 门、NOT门等。

3. 4位同步二进制加法计数器是同步计数器,即所有触发器同时接收输入脉冲,确保计数的同步性。

二、4位同步二进制加法计数器的计数最大值1. 4位二进制数的表示范围是0~15,因此4位同步二进制加法计数器的计数最大值为15。

2. 在计数到15后,再输入一个脉冲,计数器将重新从0开始计数,即实现了循环计数。

三、4位同步二进制加法计数器的应用1. 4位同步二进制加法计数器常用于数字电子钟、信号发生器等数字电路中,用于实现计数和定时功能。

2. 它还可以作为其他数字电路的组成部分,用于构建更复杂的逻辑功能。

3. 在数字系统中,计数器是十分重要的组件,它能够实现数字信号的计数和控制,广泛应用于各种数字系统中。

4位同步二进制加法计数器是一种重要的数字电路,通过它可以实现对二进制数的递增计数。

其计数的最大值为15,应用领域广泛。

希望本文内容能够对读者有所启发。

四、4位同步二进制加法计数器的工作原理4位同步二进制加法计数器是一种晶体管数字集成电路,它利用触发器和逻辑门等基本元件构成,能够实现二进制数字的加法计数。

在4位同步二进制加法计数器中,每个触发器代表一个二进制位,通过输入脉冲的控制,能够实现对二进制数的递增计数。

具体来说,当输入一个脉冲信号时,4位同步二进制加法计数器会根据触发器之间的连线和逻辑门的作用,根据之前的状态和输入脉冲的信号进行状态转换,从而实现二进制数的递增。

四位二进制除法器说明书

目录一、设计目的 (1)二、设计要求 (1)三、设计内容 (1)3.1、除法的实现 (1)3.2、设计框图 (1)3.3、功能说明 (1)3.4、VHDL程序源代码 (2)3.5、VHDL程序说明 (3)四、原理图和印刷板图 (4)PCB板图 (4)Protel 原理图 (5)五、设计结论 (6)六、设计心得体会 (6)七、主要参考文献 (7)一、设计目的1.掌握电子电路的一般设计方法和设计流程;2.学习使用PROTEL软件绘制电路原理图及印刷板图。

二、设计要求设计一个四位二进制除法器,具体要求如下:1. 用键盘输入两个四位二进制数,并用数码管显示输入数。

2.按除法键即显示相除结果。

3. 除数为零时,数码管黑屏,不显示任何内容。

三、设计内容1、设计过程要想实现四位二进制除法器,必须首先实现除法的功能。

除法实现的方案可以用VHDL语言实现。

整个四位二进制除法器包括:输入电路,判断电路,除法电路,译码电路和显示电路。

这些电路可以分别进行设计。

2、设计框图3.各个模块的功能说明●整个四位二进制除法器的实现可以分为以下5个部分:●输入电路:输入两个4位2进制数A和B。

它是通过连着高电平的8个开关来实现的。

●判断电路:判断B是否为0。

它是通过1个5输入同或门实现的。

如果B为0,输出端输出高电平,使能端除法器不工作,显示器黑屏。

●除法电路:由VHDL语言实现的。

它实现两个4位2进制数相除,并输出商y和余数r.●译码电路:由VHDL语言实现的。

它实现两个4位2进制数相除,并输出商y和余数r.●显示电路:将译码器译成的数用数码管显示出来。

4.VHDL程序源代码除法源代码1.Library ieee;2.Use ieee.std_logic_1164.all;3.Entity divider is4.Generic (n: integer :=3);5.Port( a, b : in integer range 0 to 15;6.y:out std_logic_vector ( 3 downto 0);7.rest:out integer range 0 to 15;8.err:out std_logic);9.End divider ;10.Architecture rtl of divider is11.Begin12.Process (a,b)13.Variable temp1:integer range 0 to 15;14.Variable temp2:integer range 0 to 15;15.Begin16.temp1:=a;17.temp2:=b;18.if(b=0)then err <=’1’;19.Else err<=’0’;20.End if;21.For I in n downto 0 loop22.If (temp1>=temp2*2**i) then23.y(i) <=‘1’;24.temp1:=temp1-temp2*2**i;25.Else y(i)<= ‘0’;26.End if;27.End loop;28.Rest <=temp1;29.End process;30.End rtl;5.VHDL程序说明假设要计算Y=A/B,其中 A 和 B 有相同的位数4位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

四位二进制除法器设计

李道通58

1、设计方法

采用移位相减法设计二进制除法器:被除数和除数都是二进制数,采用将除数移位的方法。

1)判断除数是否零:如果除数为零,返回等待;2)除数不为零时,C左移一位,将被除数A的最高位赋值给C的最低位,A左移一位,将最低位赋值为零;3)判断C和除数B的大小,若C>=B,这C=C-B,且A的最低位赋值为1。

4)如此循环四次,得到的A即为商,得到的C为余数。

该算法的好处在于被除数和商公用一个寄存器A,节省资源。

2、算法流程图

图中:被除数和除数分别放在A、B中,商余数分别放在A和C,N为计数器

3、VHDL程序代码:

LIBRARY IEEE;

USE ldt_chufaqi IS

PORT(A,B:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

C,D:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END ENTITY ldt_chufaqi;

ARCHITECTURE BEHAV OF ldt_chufaqi IS

BEGIN

S1:PROCESS(A,B)

VARIABLE N:INTEGER;

VARIABLE TEMP_A,TEMP_B,TEMP_C:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

TEMP_A:=A;

TEMP_B:=B;

TEMP_C:="0000";

N:=0;

IF(B>"0000")THEN

WHILE(N<4) LOOP

TEMP_C:=TEMP_C(2 DOWNTO 0)& TEMP_A(3);

TEMP_A:=TEMP_A(2 DOWNTO 0)&'0';

IF TEMP_C>=TEMP_B THEN

TEMP_C:=TEMP_C-TEMP_B;

TEMP_A(0):='1';

END IF;

N:=N+1;

END LOOP;

ELSE

TEMP_A:="ZZZZ";

TEMP_C:="ZZZZ";

END IF;

D<=TEMP_A(3 DOWNTO 0);C<=TEMP_C(3 DOWNTO 0);

END PROCESS;

END ARCHITECTURE BEHAV;

4、仿真结果:

图中:A、B、C、D分别是被除数、除数、余数和商,因本人对软件和语言的运用理解不足,无法做到A的同时输入和输出,故将A的结果赋值给D,但基本思路运算方法已经得到实现。

除数为零时,商和余数都为高阻态;

除数为3时,求的商和余数,仿真结果正确。

除数为5时,商和余数的仿真结果正确。