加减法运算电路设计

加法运算和减法运算电路

=8V

12

例:由三运放放大器组成的温度测量电路。

E=+5V

R

R

R

Rt

+ A1 +

ui

_

+ A2 +

R R1 RW R R1

R2

+ A3 +

uo

R2

Rt :热敏电阻

集成化:仪表放大器

13

E=+5V

R

R

R

Rt

+ A1 +

ui _

+ A2 +

R R1 RW R R1

R2

+ A3 +

uo

R2

Rt f (TC)

( RP2 // R RP1 RP 2 //

R ui1

RP

RP1 // R 2 RP1 //

R

ui

2

)

(R1 Rf )Rf R1 R f

( RP1

//

RP 2

//

R)(

ui1 RP1

ui 2 ) RP 2

将RP= RN的条件代入可得:

uo

Rf

( ui1 RP1

ui 2 RP 2

)

在RP1=

RP2

ui1

可以变为:

uo ui2 ui1

反相输入结构的减法电路,由于出现虚地,放大电路没

有共模信号,故允许 ui1 、ui2 的共模电压范围较大,且输

入阻抗较低。在电路中,为减小温漂提高运算精度,同相端

须加接平衡电阻。

4

6.2.2 减法运算电路

1、差动减法器

由Ui1产生的输出电压为:

uo

Rf R1

模电课程设计加减法电路

1 设计任务描述1.1 设计题目:加法运算电路1.2 设计要求1.2.1 设计目的(1)学习基本理论在实践中综合运用的初步经验,掌握模拟电路设计的基本方法、设计步聚,培养综合设计与调试能力; (2)学会利用运算放大器实现加减法电路;(3)学会直流稳压电源的设计方法和性能指标测试方法; (4)培养实践技能,提高分析和解决实际问题的能力。

1.2.2 基本要求(1)利用两级运算放大器实现321o 42i i i u u u u ++=(2)设计电路所需的直流稳压电源,要求包括整流、滤波、稳压。

1.2.3 发挥部分(1)由于同相加法电路存在共模电压,将造成几个输入信号之间的互相影响,所以本次设计我选用两级运放反相输入,在第一级运用反相输入的求和电路,在第二级采用双端输入式,从而实现课设要求的输出与输入的线性关系。

(2)在线性直流电源中,将普通的电容滤波更改为两个电容与一个电阻的π型滤波电路,增加对交流分量的滤除。

(3)在线性直流电源中,将一般的稳压电路改为固定式三端集成稳压器工作。

2 设计思路本次设计的课题是加法运算电路,其“加法”的含义是实现输出与输入的线性关系。

本次设计还要求设计为运算电路提供电源的线性直流稳压电源。

首先这次设计的重点是加法运算电路,我需要设计一个电路使得其输出电压与输入电压满足表达式。

为满足这一线性关系,我选用两级放大来实现。

经过一个学期的学习,我大致了解关于集成运算放大器的工作原理,而这次设计主要是关于运放的线性应用。

首先第一级放大电路中,由于同相输入存在共模电压,会造成几个输入信号之间的互相影响。

而反相输入式放大电路中,根据虚断的概念,同相位输入端的电位为零,相当于与地等电位,即“虚地”。

这样可保证运放输入端无共模信号。

在第一级运算放大器的反相端输入施加两个电压信号,从而达到两个输入电压与第一级运放的输出电压之间的线性关系。

然后将这一输出加到第二级运放的反相端,同时在第二级运放的同相端加入第三个信号源,实现双端输入式放大电路,这种电路的的特点是输入电阻大、输出电阻小。

加减法运算电路设计

加减法运算电路设计1.设计内容及要求1.设计一个4位并行加减法运算电路,输入数为一位十进制数,且作减法运算时被减数要大于或等于减数。

2.led灯组成的七段式数码管显示置入的待运算的两个数,按键控制运算模式,运算完毕,所得结果亦用数码管显示。

3.提出至少两种设计实现方案,并优选方案进行设计2.结构设计与方案选择2.1电路原理方框图电路原理方框图如下→→图1-1二进制加减运算原理框图如图1-1所示,第一步置入两个四位二进制数(要求置入的数小于1010),如(1001)2和(0111)2,同时在两个七段译码显示器上显示出对应的十进制数9和7;第二步通过开关选择运算方式加或者减;第三步,若选择加运算方式,所置数送入加法运算电路进行运算,同理若选择减运算方式,则所置数送入减法运算电路运算;第四步,前面所得结果通过另外两个七段译码器显示。

即:若选择加法运算方式,则(1001)2+(0111)2=(10000)2十进制9+7=16 并在七段译码显示器上显示16.若选择减法运算方式,则(1001)2-(0111)2=(00010)2十进制9-7=2并在七段译码显示器上显示02.2.2加减运算电路方案设计2.2.1加减运算方案一如图2-2-1所示:通过开关S2——S9接不同的高低电平来控制输入端所置的两个一位十进制数,译码显示器U13和U15分别显示所置入的两个数。

数A 直接置入四位超前进位加法器74LS283的A4——A1端,74LS283的B4——B1端接四个2输入异或门。

四个2输入异或门的一输入端同时接到开关S1上,另一输入端分别接开关S6——S9,通过开关S6——S9控制数B的输入。

当开关S1接低电平时,B与0异或的结果为B,通过加法器74LS283完成两个数A和B的相加。

当开关S1接高电平时,B与1异或的结果为B非,置入的数B在74LS283的输入端为B的反码,且74LS283的进位信号C0为1,其完成S=A+B (反码)+1,实际上其计算的结果为S=A-B完成减法运算。

加法和减法运算电路---知识点

加法和减法运算电路

1、加法运算电路

加法运算电路能实现多个模拟量的求和运算。

分为反相加法运算电路和同相加法运算电路两种。

可以利用“虚短”、“虚短”的概念或者叠加原理进行分析。

1)反相加法运算电路的常见电路如图1所示。

电路为并联电压负反馈。

平衡电阻R 2=R i1//R i2//R F。

图1

F F o i1i 2i1i 2

()R R u u u R R =-+2)同相加法运算电路的常见电路如图2所示。

电路为串联电压负反馈。

平衡电阻满足关系R 1//R F =R i1//R i2。

图2

F i 2i1o i1i 21i1i 2i1i 2

(1)()R R R u u u R R R R R =++++2、减法运算电路

减法运算电路的常见电路如图3所示。

可以将电路看做反相比例

运算电路和同相比例运算电路的叠加进行分析。

R F 相对于u i1是并联电压负反馈,对于u i2

是串联电压负反馈。

图3

3F F

o i 2i1

1231(1)R

R R u u u

R R R R =+-+。

减法运算电路

积件 4-1-3-2:加减运算放大的仿真研究

2) 同相加法运算电路

图4-11 同相加法运算电路

积件 4-1-3-2:加减运算放大的仿真研究

(2)减法运算电路

图 412 减 法 运 算 电 路

积件 4-1-3-2:加减运算放大的仿真研究

二、其它方面的应用

1.电压比较器 (1)基本电路

图4-13 电压比较器

积件 4-1-3-2:加减运算放大的仿真研究

作业: 1、画出集成运放电路组成的加法器、 减法器电路图。并证明输入电压与输出 电压的关系式。 2、画出输出电压Uo与输入电压Ui符合 下列关系的运放电路图;(1) Uo/Ui=-1;(2)Uo/Ui=15;(3) Uo/(Ui1+Ui2+Ui3)=-20。

加减运算放大的仿真研究一集成运放的线性应用二运算电路1加法运算电路反相加法运算电路图410反相加法运算电路电路输出电压

积件 4-1-3-2:加减运算放大的仿真研究

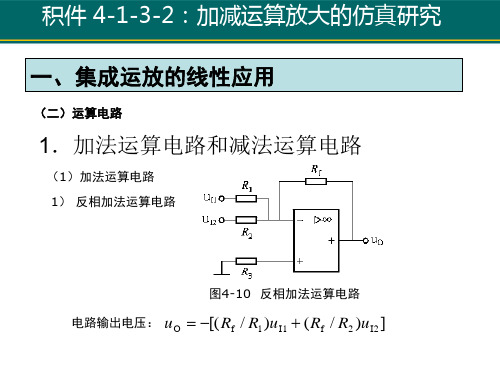

一、集成运放的线性应用

(二)运算电路

1.加法运算电路和减法运算电路

(1)加法运算电路 1) 反相加法运算电路

图4-10 反相加法运算电路

电路输出电压: uO [( Rf / R1 )uI1 (Rf / R2 )uI2 ]

积件 4-1-3-2:加减运算放大的仿真研究

可见,输出电压与输入电压反相,且uo是两输入信号加权后的负值相加,故称反相

加法器。

若取, R1 R2 则

uO (Rf / R1 )(uI1 uI2 )

若取,Rf R1 R2 则, uO (uI1 uI2 )

电路成为反相加法器。

积件 4-1-3-2:加减运算放大的仿真研究

简单加减计算电路

简单加/减运算电路1 设计主要内容及要求1.1 设计目的:(1)掌握1位十进制数加法运算电路的构成、原理与设计方法;(2)熟悉QuartusII的仿真方法。

1.2 基本要求:(1)实现二进制数的加/减法;(2)设计加数寄存器A和被加数寄存器B单元;(3)实现4bit二进制码加法的BCD调整;(4)根据输入的4bitBCD编码自动判断是加数还是被加数。

1.3 发挥部分:(1)拓展2位十进制数(2)MC存储运算中间值;(3)结果存储队列;(4)其他。

2 设计过程及论文的基本要求2.1 设计过程的基本要求(1)基本部分必须完成,发挥部分可任选2个方向:(2)符合设计要求的报告一份,其中包括逻辑电路图、实际接线图各一份;(3)设计过程的资料、草稿要求保留并随设计报告一起上交;报告的电子档需全班统一存盘上交。

2.2 课程设计论文的基本要求(1)参照毕业设计论文规范打印,文字中的小图需打印。

项目齐全、不许涂改,不少于3000字。

图纸为A3,附录中的大图可以手绘,所有插图不允许复印。

(2)装订顺序:封面、任务书、成绩评审意见表、中文摘要、关键词、目录、正文(设计题目、设计任务、设计思路、设计框图、各部分电路及参数计算(重要)、工作过程分析、元器件清单、主要器件介绍)、小结、参考文献、附录(逻辑电路图与实际接线图)。

摘要当今的社会是信息化的社会,也是数字化的社会,各种数字化的电器与设备越来越普及,人们的大部分生活都依赖于这些数字化的设备。

而随着科技的发达,这些数字设备的功能越来越强大,程序越来越复杂。

但是我们都知道各种复杂的运算都是从简单的加减运算衍生出来的。

经过半学期的数字电子技术基础的学习,我们对数字电子技术的理论知识有了一定的了解。

在这个时刻,将理论结合实际的欲望,便显得更加迫切,而此时的课设安排正好可以帮助我们将理论结合实际,将梦想变成现实。

本次的简单运算电路是基于QuartusⅡ仿真软件而设计的,而每一个仿真软件都有它自己的特色与优缺点。

4.加减法运算电路

1.反向加法电路:仿真电路图:仿真结果:(输入信号):(输出结果)注释:从输入和输出的波形可以知道,OUT=--(IN1+IN2); 其实电路的表达式为:RfR In R In out *)]22()11[(+-=因为电路中的Rf=R1=R2;所以电路的输入、输出仅仅表现出简单的反向加法的关系;调节Rf 和R1,R2的比例关系,便可以得到具有放大作用的反向减法电路;2.同向加法电路:仿真电路:输入、输出关系:(输入):(输出波形):注释:从输入和输出的波形可以看出,输出(out=In1+In2); 其实电路的输出、输入之前的数学表达式为:3*)2*421*41(R RfIn R R In R R Out +=由于上面的仿真电路中取,13*41=R RfR R 和13*42=R Rf R R ,所以电路的输入输出特性仅仅表现为简单的同向加法电路,调节Rf 和R3以及R4的阻值大小可以得到放大倍数不同的同向加法放大电路。

由于此电路数学表达式比较复杂,且输入电阻不大,一般不直接采用。

3.减法电路: 简单减法电路: 仿真电路:注释:从仿真电路的输入输出关系可以知道,out=Vi-V2; 其实,电路的输入输出关系为:13*2)131(*424*1R R In R R R R R In Out -++=由于上面电路中的R2=R4,R3=2R2;所以out=Vi-V2;使用两个运放的减法电路:注释说明:电路的输入输出关系式为:)]2211(2[21R In R In Rf R Rf Uo -=上面的仿真电路中Rf1=R2,Rf2=R1=R2,所以输入输出关系仅仅表现出简单的减法关系 这一点路的特点是两个运放的反相输入端都是虚地,共模输入电压Uc=U-=U+约等于0;因此对运放电路的共模抑制比要求较低。

4.高输入阻抗减法电路: 仿真电路:输入波形:输出波形:注释:电路的输入输出关系是为:2)341(1)34)(121(Ui R R Ui R R R R Uo ++-+=但是为了抑制共模,必须选择合适的电阻阻值; 为了抑制共模,必须使)341()34)(121(=++-+R R R R R R取R2=R3,R1=R4,满足上面的式子,所以最终得到输入输出关系为:)12)(341(Ui Ui R R Uo -+=该电路具有很高的输入阻抗,所以适合用于小信号的处理。

基于multisim的加减法运算电路设计

基于multisim的加减法运算电路设计随着科技的不断发展,电子技术在我们的日常生活中扮演着越来越重要的角色。

而在电子技术中,加减法运算电路是最基础也是最常见的一种电路。

本文将介绍基于Multisim的加减法运算电路设计。

Multisim是一款功能强大的电子电路仿真软件,它可以帮助我们在计算机上进行电路设计和仿真。

在设计加减法运算电路之前,我们首先需要了解加减法运算的原理。

加法运算是指将两个或多个数相加得到一个和的过程。

在电路中,我们可以使用全加器来实现加法运算。

全加器是一种能够将两个二进制数相加并输出和与进位的电路。

在Multisim中,我们可以使用逻辑门和触发器来构建全加器电路。

减法运算是指将一个数减去另一个数得到差的过程。

在电路中,我们可以使用加法器和补码来实现减法运算。

补码是一种用来表示负数的编码方式,它可以将减法运算转化为加法运算。

在Multisim中,我们可以使用加法器和逻辑门来构建减法器电路。

在Multisim中设计加减法运算电路的步骤如下:1. 打开Multisim软件,并创建一个新的电路设计文件。

2. 选择所需的元件,包括逻辑门、触发器和加法器等,并将它们拖放到电路设计界面上。

3. 连接各个元件,确保电路的连接正确无误。

4. 设置输入端口和输出端口,以便输入和输出数据。

5. 对电路进行仿真,检查电路的运行情况和输出结果是否符合预期。

设计加减法运算电路时,我们需要考虑以下几个方面:1. 选择适当的元件:根据加减法运算的原理,选择适当的逻辑门、触发器和加法器等元件。

2. 连接正确:确保电路中的元件连接正确无误,以保证电路的正常运行。

3. 输入输出设置:设置输入端口和输出端口,以便输入和输出数据。

4. 仿真调试:在进行仿真之前,可以先进行一些简单的调试,确保电路的运行情况和输出结果符合预期。

通过Multisim软件,我们可以方便地进行加减法运算电路的设计和仿真。

这不仅提高了电路设计的效率,还可以减少实际电路搭建的成本和风险。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子课程设——加减法运算电路设计¥学院:电信息工程学院;专业:电气工程及其自动化班级:姓名:学号:指导老师:闫晓梅2014年12月 19日加减法运算电路设计一、设计任务与要求#1.设计一个4位并行加减法运算电路,输入数为一位十进制数,2.作减法运算时被减数要大于或等于减数。

灯组成的七段式数码管显示置入的待运算的两个数,按键控制运算模式,运算完毕,所得结果亦用数码管显示。

4.系统所用5V电源自行设计。

二、总体框图1.电路原理方框图:%图2-1二进制加减运算原理框图2.分析:如图1-1所示,第一步置入两个四位二进制数(要求置入的数小于1010),如(1001)2和(0111)2,同时在两个七段译码显示器上显示出对应的十进制数9和7;第二步通过开关选择运算方式加或者减;第三步,若选择加运算方式,所置数送入加法运算电路进行运算,同理若选择减运算方式,则所置数送入减法运算电路运算;第四步,前面所得结果通过另外两个七段译码器显示。

例如:若选择加法运算方式,则(1001)2+(0111)2=(10000)2十进制9+7=16,并在七段译码显示器上显示16;若选择减法运算方式,则(1001)2-(0111)2=(00010)2十进制9-7=2,并在七段译码显示器上显示02。

三、选择器件~1.器件种类:}^表3-12.重要器件简介:(1)[(2). 4位二进制超前进位加法器74LS283:完成加法运算使用该器件。

1).74LS283 基本特性:供电电压:输出高电平电流:输出低电平电流: 8mA。

2).引脚图:图3-1引出端符号:A1–A4 运算输入端B1–B4 运算输入端《C0 进位输入端∑1–∑4 和输出端C4 进位输出端3).逻辑符号:图3-2 4).内部原理图:-图3-3 5).功能表:表3-2(3)异或门:74LS861).引脚图: 2).逻辑符号:、图3-4 图3-53). 逻辑图:图3-6·4).真值表:表3-3分析:异或:当AB不相同时, 结果才会发生。

函数式:(3).三输入或非门:74LS271).引脚图:\图3-7 2).逻辑符号:B ABABAY⋅+⋅=⊕=图3-83). 逻辑图:图3-9.4).真值表:表3-4函数式:分析逻辑功能:A 、B 、C 中只要出现“1”,则输出为“1”;只有A 、B 、C 都为“0”时,输出才为“0”。

(4).非门:74LS04当输入为高电平时输出等于低电平,而输入为低电平时输出等于高电平。

因此输出与输入的电平之间是反向关系,也叫非门或反向器。

`C++=B A Y<图3-101)结构TTL反相器由三部分构成:输入级、中间级和输出级。

2)原理A为低电平时,T1饱和,V B1≈,V B2≈,T2和T5截止,T4和D2导通,Y为高电平;A为高电平时,V B1≈,T1倒置,V B2≈,T2和T5饱和,T4和D2截止,Y为低电平。

74LS04为六反相器,输入是A,输出是Y,6个相互独立倒相。

供电电压5V,电压范围在~内可以正常工作。

门数6,每门输入输出均为TTL电平(<低电平>2v高电平),低电平输出电流,高电平输出电流8mA。

其逻辑符号、逻辑功能表、内部结构、管脚图分别如下:?图3-11 74LS04的逻辑图表3-5 74LS04功能表图3-12 74LS04的逻辑符号图3-13 74LS04的管脚图YA函数式:》(5).与门74LS081).引脚图: 2).逻辑符号:图3-14 74LS08管脚图图3-15<3).逻辑图:图3-164).真值表:表3-6函数式:]B AY⋅=(6).七段数码管:图3-17是七段数码管的符号,数码管用七个发光二极管做成a、b、c、…、g七段,通过七段亮灭的不同组合,来显示信息。

并分为共阴极与共阳极两种。

共阴极是将七个发光二极管的阴极接在一起并接在地上,阳极接到译码器的各输出端,当发光二极管对应的阳极为高电平时,发光二极管就亮,共阳极则与之相反。

只要按规律控制各发光段的亮、灭,就可以显示各种字形或符号,共阴极七段数码管原理图如图3-18所示。

图3-17 图3-18七段显示译码器是驱动七段显示器件的专用译码器,它可以把输入的二―十进制代码换成七段显示管所需要的输入信息,以使七段显示管显示正确的数码,应用原理如图所示。

BCD七段译码器的输入是一位BCD码(以D、C、B、A表示),输出是数码管各段的驱动信号(以F a~F g表示)。

若用它驱动共阴LED数码管,则输出应为高有效,即输出为高(1)时,相应显示段发光。

例如,当输入8421码DCBA=0100时,应显示 4,即要求同时点亮b、c、f、g段,熄灭a、d、e段,故译码器的输出应为F a~F g=0110011,这也是一组代码,常称为段码。

图3-19 共阳极数码管应用原理图图3-20 七段数码显示|其真值表如下表所示:表3-7(7)74LS147:10线-4线8421 BCD码优先编码器74LS147的真值表见表。

74LS147的引脚图如图所示,其中第9脚NC为空。

74LS147优先编码器有9个输入端和4个输出端。

某个输入端为0,代表输入某一个十进制数。

当9个输入端全为1时,代表输入的是十进制数0。

4个输出端反映输入十进制数的BCD码编码输出。

74LS147优先编码器的输入端和输出端都是低电平有效,即当某一个输入端低电平0时,4个输出端就以低电平0的输出其对应的8421 BCD编码。

当9个输入全为1时,4个输入出也全为1,代表输入十进制数0的8421 BCD编码输1).管脚图如下:<图3-21功能表如下:`表3-8内部原理图如下:图3-22(7)LM7812LM7812是指三段稳压集成电路IC芯片元器件,适用于各种电源稳压电路,输出稳定性好、使用方便、输出过流、过热自动保护。

本设计使用的电路为:/图3-23内部原理图如下:图3-24(注:在此设计中,如电阻,电容二极管等器件均无特别要求,按电路中所标参数选取即可。

)|四.功能模块1:减法电路的实现:(1):原理:如图1所示(如下),该电路功能为计算A-B。

若n位二进制原码为N原,则与它相对应的补码为N补=2n-N原,补码与反码的关系式为N补=N反+1,A-B=A+B补-2n=A+B反+1-2n(2):因为B○+1= B非,B○+0=B,所以通过异或门74LS86对输入的数B求其反码,并将进位输入端接逻辑1以实现加1,由此求得B的补码。

加法器相加的结果为:A+B反+1,(3):由于2n=24=(10000)2,要求相加结果与相2n减只能由加法器进位输出信号完成。

当进位输出信号为1时,即相当于2n,可实现减2n,因为设计要求被减数大于或等于减数,所以所得的差值就是A-B差的原码。

减法仿真图:下页图为4-1;分析结果:数A为9,数B为7,(1001)2-(0111)2=(00010)2十进制9-7=2并在七段译码显示器上显示02。

(]/]2:加法电路的实现如下:;(1)加法原理:A.通过开关S1——S9接编码器74LS147U12输入端,通过开关节高低电平使译码显示器U5显示所置入的数A,同理,通过开关S10——S18接编码器74LS147U23输入端,通过开关节高低电平使译码显示器U22显示可置入数B。

数A直接置入四位超前进位加法器74LS283的A1——A4端,74LS283的B1——B4端接四个2输入异或门。

四个2输入异或门的一输入端同时接到开关S19上。

B.当开关S19接低电平时,B与0异或的结果为B,通过加法器74LS283完成两个数A和B的相加。

C.由于译码显示器只能显示0——9,所以当A+B>9时不能显示,我们在此用另一片芯片74LS283完成二进制码与8421BCD码的转换,即S>9(1001)时加上6(0110),产生的进位信号送入译码器U10来显示结果的十位,U11显示结果的个位(2)加法电路的实现:用两片4位全加器74LS83和门电路设计一位8421BCD码加法器A.由于一位8421BCD数A加一位数B有0到18这十九种结果。

a)两个 8421 码相加,其和仍应为8421 码,如不是 8421 码则结果错误。

如:b)!c)产生错误的原因是 8421BCD码为十进制,逢十进一,而四位二进制是逢十六进一,二者进位关系不同,当和数大于 9 时,8421BCD应产生进位,而十六进制还不可能产生进位。

为此,应对结果进行修正。

当运算结果小于等于 9 时,不需修正或加“0”,但当结果大于 9 时,应修正让其产生一个进位,加0110即可。

如上述后两种情况:故修正电路应含一个判 9 电路,当和数大于 9 时对结果加0110,小于等于 9 时加0000。

除了上述大于 9 时的情况外,如相加结果产生了进位位,其结果必定大于 9,所以大于 9 的条件为;图4-2图4-3B. 另一种设计:当大于9的时候要加六转换才能正常显示,所以设计的时候有如下的真值表:表4-1由表4-1我们可以算出Y 的表达式:,(1)由前16项有: Y= S 4S 3+ S 4S 2 (2)由后10项有: Y= C 4=1由(1)(2)有: 得到了如下的加法仿真图(下页图为4-4): 分析结果:数A 为9,数B 为7,(1001)2+(0111)2=(10000)2 十进制9+7=16 并在七段译码显示器上显示16。

&—^S 2.S 4S 3.S 4C 4S 2.S 4S 3.S 4C 4Y ++=++=` | ! - #!3:译码显示电路的实现一个七段LED译码驱动器74HC4511和一个七段LED数码显示器组成。

七段LED 译码驱动器74HC4511的功能表如下.在74HC4511中,经前面运算电路运算所得的结果输入74HC4511的D3D2D1D,再译码输出,最后在七段LED显示器中显示出来.表4-2:七段LED译码驱动器74HC4511功能表{表4-3:七段LED译码驱动器74HC4511功能表续;—图4-5译码显示电路4.电源部分图4-6电路图如上,系统输出为5v,可以为电路提供合适电压。

五.总体设计电路图Nultisim仿真电路图:(注:下面两图分别为4-7,4-8)($ ]结果分析:(1) 加法运算:选择开关接低电平,S9选择低电平,S10也选择高电平,则编码器74LS147输出0110,1110,再通过输出端的非门后变为1001,0001,则(1001)2+(0001)2=(01010)2 十进制9+1=10,并在七段译码显示器上显示10. (2)减法运算开关接高电平,S9选择低电平,S10也选择高电平,则编码器74LS147输出0110,1110,再通过输出端的非门后变为1001,0001,则为(1001)2-(0001)2=(01000)2十进制9-1=8,并在七段译码显示器上显示08.六、心得体会通过这次课程设计,加强了我动手、思考和解决问题的能力。