广东工业大学数字电子技术试卷1

数电(内容系建雄嗰啲相)

广东工业大学考试试卷课程名称: 数字电子技术A一、 填空題(20分)1. ( 731 )8 = ( )10= ( )8421BCD2. 半導體數碼管的每個顯示段是由 構成的。

3. JK 觸發器的次態方程為,則驅動方程J= , K= 。

4. 觸發器的輸出脈衝寬度與輸入信號無關。

5. 在A/D 電路中輸入信號的最大頻率是15kHz,則取樣脈衝的頻率至少要大於 kHz 。

6. 若把輸入的正弦波轉換成同頻的矩形波,則採用 電路。

7.一個8位D/A 轉換器的每個量化階梯為0.025V 電壓,則它最大能表示 V 電壓 。

8. 圖1所示電路的最簡與或式為 。

二、判斷題(5分) 1. 由譯碼器和邏輯門構成的電路能同時實現多個函數輸出。

( ) 2. 函數 與互為反函數。

( ) 3. 將4個三態門的輸出接到同一條數據線上,則在任何時刻應至少有一個三態門處於高阻態 ( )4. 石英晶體多謝振盪器的主要優點是振盪頻率高。

( )5. 連續“同或”100個0的結果是1。

( )三、單項選擇題 (15分)1. 函數F(a,b,c,d)=Σm(2,3,6,8,9,10,11,12,12,14)的最簡 與-或 式是F= 。

A. B. C. D. 2. 十進制計數器74160不能實現( )分頻。

A. 4B. 10C. 2D. 163. 在8位D/A 轉換器中,其分辨率是 。

A. 1/8B. 1/256C. 1/255D. 1/24. 右圖中CMOS 邏輯門構成的電路 輸出不為高電平的是( )。

A. Y 1和Y 2B. Y 2和Y 3C. Y 3和Y 4,且Y 2為高阻態D. Y 2和Y 4+=+++=++=++++++++5. 圖3所示邏輯電路的邏輯功能是()。

A. 譯碼器B. 數據比較器C. 數據選擇器D. 全加器四. 寫出如圖所示各門電路的輸出最簡表達式。

圖中是74系列TTL電路。

Y1= Y2= Y3= 五、寫出下圖所示電路的次態方程,並畫出觸發器輸出端波形圖。

广工数电试卷

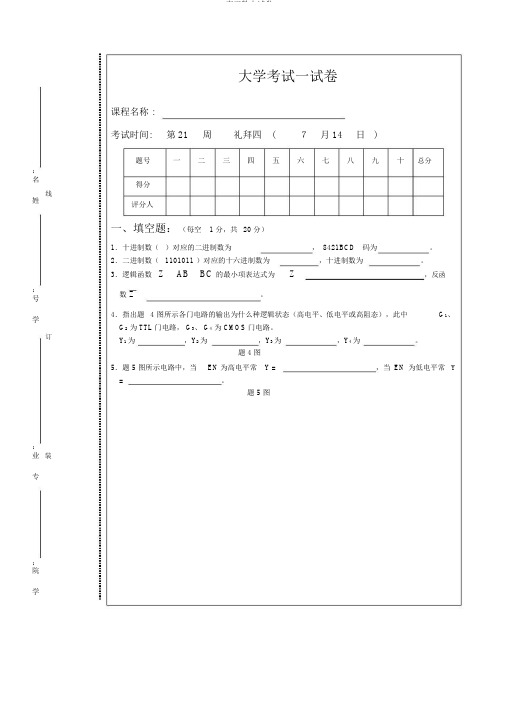

:名线姓:号学订:业装专:院大学考试一试卷课程名称 :考试时间:第21周礼拜四(7月14日)题号一二三四五六七八九十总分得分评分人一、填空题:(每空 1 分,共20 分)1.十进制数()对应的二进制数为,8421BCD码为。

2.二进制数(1101011 )对应的十六进制数为,十进制数为。

3.逻辑函数Z AB BC 的最小项表达式为Z,反函数 Z。

4.指出题 4 图所示各门电路的输出为什么种逻辑状态(高电平、低电平或高阻态),此中G1、G2为 TTL 门电路, G3、 G4为 CMOS 门电路。

Y1为,Y2为,Y3为,Y4为。

题 4 图5.题 5 图所示电路中,当EN 为高电平常Y =,当EN为低电平常Y =。

题 5 图学6 .依据电路构造形式的不一样,能够将触发器分为基本RS 触发器、、和边缘触发器等几种种类。

7 .题 7 图所示电路中,若输入时钟脉冲CP 的频次为 80kHz ,则输出 Z 的频次为。

1CP 1 J Q 1 J Q ZC1 C11K Q 1K Q题 7 图8.常用的两类经过整形产生矩形脉冲的电路为和。

9. 用 2114 芯片( 1024× 4 位的 ROM )构成 8k× 8 位的 ROM 时,需用片2114芯片,其字线和位线分别是。

10. 一个 8 位 D/A 变换器的最小输出电压增量为0.02V ,则当输入代码为01001011 时,输出电压v o为__________ 。

二、剖析设计题(8题共80分)11. 将以下逻辑函数化简为最简与或式(方法不限,但要写出化简过程。

8 分)(1) F1 AB AC BC(2) F2 ABC A CD C D( A B) ,拘束条件为AB CD 012.试用 8 选 1 数据选择器及适合的门电路设计一个四变量奇偶检测器,要求当四个输入变量中有偶数个 1 时输出为 1,不然输出为 0。

(要有设计过程, 12 分)13. 由 4 位加法器 74LS283 构成的电题13图路如题13 图所示,输入为8421BCD 码。

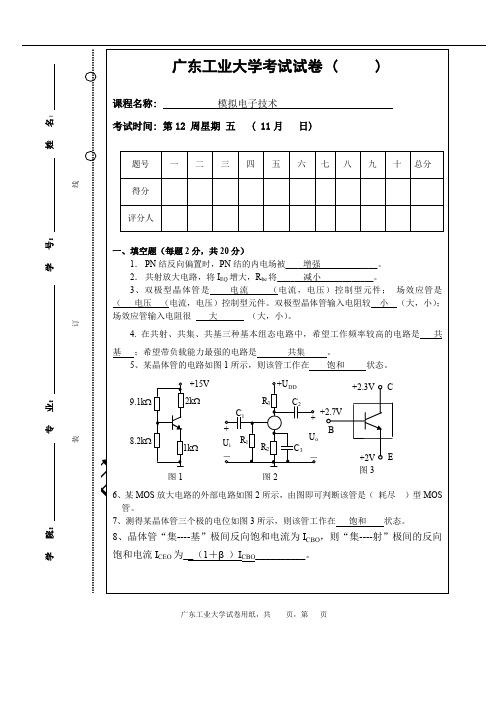

(完整word版)广工模拟电子技术基础试卷1

RE

U CC

1

2 uo1 uo2

图5

广东工业大学试卷用纸,共 页,第 页

3.已知 RB11=30k,RB12=20k,RB2=130k,,RC1=4k,,RE1=4k,RE2=3k, RL=3k , 1=2=50,UCC=12V。求静态工作点及电压放大倍数。(12 分)

4. 已知 RG=10M,RG1=2M,RG2=47k,RD=30k, RS=2k ,

入电阻最小的是___共基极____.

10、晶体管阻容耦合放大器电路中,高频时放大倍数下降的主要原因是_极间电容__

的影响;低频时放大倍数下降的主要原因是_耦合电容旁路电容_的影响。

二.. .项选择题(每小题 2 分,共 12 分)在每小题列出的四个选项中只有一个选项是符合题目要求 的,请将正确选项前的字母填在题后的括号内。

6.某共射电路如题图,已知三极管的 rbb’=300Ω ,rb’e=700Ω ,gm=0.04s 不考虑 Cb’c, Cb’e=400pF,图中 C1=2μ F,C2=4μ F,Rb=20kΩ ,Rs=800Ω ,Rc=RL=2kΩ ;(12 分) (1) 计算上、下限截止频率ƒH,ƒL ;

(2) 简要画出幅频、相频特性波特图;

A.35

B.37

C.40

D.43

16.输入信号 vi 的频率范围为 50Hz~20kHz,应选择下限频率 fL 和上限频率 fH 分别为( C 放大电路,才能对信号进行不失真放大。

A.≤50Hz、≥15kHz

B. ≤100Hz、≥15kHz

C. ≤50Hz、≥20kHz

D. ≤100Hz、≥20kHz

UDD=18V, UGS=-0.2V,gm=1.2.mA/V 。 求 (1)静 态工 作 点 ;(2) 电压 放 大倍 数;(3)输入电阻和输出电阻。(12 分)

数字电子技术试题及答案(题库)

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

数字电子技术测试试卷与答案精选全文完整版

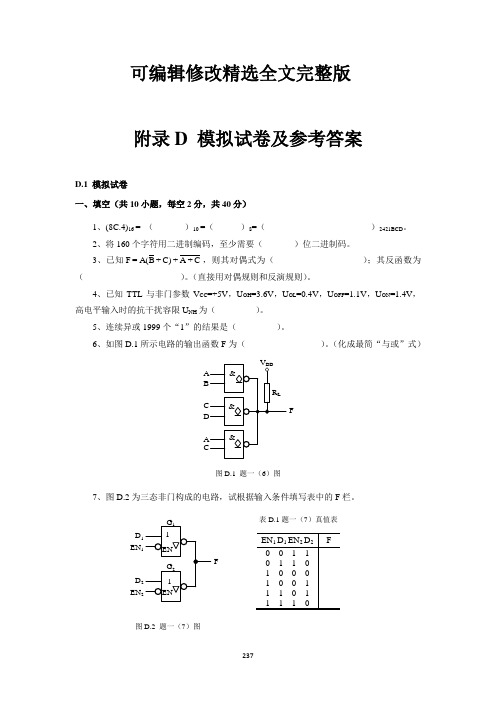

可编辑修改精选全文完整版附录D 模拟试卷及参考答案D.1 模拟试卷一、填空(共10小题,每空2分,共40分)1、(8C.4)16 = ( )10 =( )8=( )2421BCD 。

2、将160个字符用二进制编码,至少需要( )位二进制码。

3、已知F =A(B +C)+A +C ,则其对偶式为( );其反函数为( )。

(直接用对偶规则和反演规则)。

4、已知TTL 与非门参数V CC =+5V ,U OH =3.6V ,U OL =0.4V ,U OFF =1.1V ,U ON =1.4V ,高电平输入时的抗干扰容限U NH 为( )。

5、连续异或1999个“1”的结果是( )。

6、如图D.1所示电路的输出函数F 为( )。

(化成最简“与或”式)F图D.1 题一(6)图7、图D.2为三态非门构成的电路,试根据输入条件填写表中的F 栏。

图D.2 题一(7)图表D.1题一(7)真值表D 1EN 1D 2EN 2F8、设计模值为61的自然二进制码计数器、十进制计数器和余3 BCD码计数器分别需要()级、()级和()级触发器。

一个五位二进制加法计数器,由00000状态开始,问经过109个输入脉冲后,此计数器的状态为()。

9、用()片1024×4位的RAM可组成8K×8位的RAM,需要增加()条地址线、()条数据线。

10、在10位的倒T型电阻网络D/A转换器中,若U REF = ─10V,该D/A转换器能分辨的最小输出电压U LSB=()mV。

二、选择题(共10小题,每小题2分,共20分)1、有符号位二进制数的补码为(10011),则对应的十进制数为()。

A、-29B、+13C、-13D、-32、下列说法正确的是()。

A、n个变量所构成的全部最小项之和恒等于0B、n个变量所构成的全部最大项之和恒等于0C、n个变量所构成的全部最小项之积恒等于1D、n个变量所构成的全部最大项之积恒等于03、下列说法正确的是()。

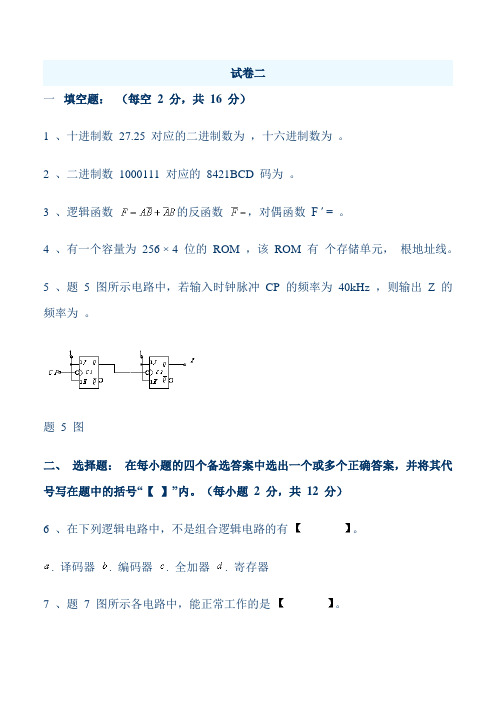

广东工业大学数字电子技术试卷2

试卷二一填空题:(每空 2 分,共16 分)1 、十进制数27.25 对应的二进制数为,十六进制数为。

2 、二进制数1000111 对应的8421BCD 码为。

3 、逻辑函数的反函数,对偶函数F ′ = 。

4 、有一个容量为256 × 4 位的ROM ,该ROM 有个存储单元,根地址线。

5 、题5 图所示电路中,若输入时钟脉冲CP 的频率为40kHz ,则输出Z 的频率为。

题5 图二、选择题:在每小题的四个备选答案中选出一个或多个正确答案,并将其代号写在题中的括号“【】”内。

(每小题 2 分,共12 分)6 、在下列逻辑电路中,不是组合逻辑电路的有。

. 译码器. 编码器. 全加器. 寄存器7 、题7 图所示各电路中,能正常工作的是。

题 7 图《数字电子技术》试题A( 共5 页) 第1 页8 、题8 图所示TTL 电路中,若开门电阻,关门电阻,能实现逻辑功能的电路是。

题 8 图9 、题9 图所示电路中,能完成逻辑功能的电路是。

题 9 图10 、用ROM 实现逻辑设计时,要求ROM 的与阵列必须产生。

变量的个最小项变量的个或项变量的个与项变量的个或项11 、构造一个十进制加法计数器,至少要用JK 触发器。

. 3 个. 4 个. 5 个. 10 个三、分析与设计题(共72 分)12 、将下列逻辑函数化简为最简与或式(方法不限,但要写出化简过程。

共6 分)••,约束条件为。

《数字电子技术》试题 A( 共 5 页 ) 第 2 页13 、某双 4 选 1 数据选择器的功能如下表,接成如题 13 图 所示的电路。

分析电路功能,写出输出逻辑函数的表达式,用最小项之和的形式表示。

(共 8 分) 4 选 1 选择器功能表题 13 图选通 地 址 输出1 × × 0 0 00 0 0 1 0 10 0 1 1试卷二14 、写出题 14 图( )所示电路的次态函数(即),并画出在题 14 图()给定信号作用下的电压波形。

数字电子技术试卷和答案

数字电子技术试卷和答案(总59页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--数字电子技术试卷(1)一.填空(16)1.十进制数123的二进制数是 1111011 ;十六进制数是 7B 。

2.是8421BCD码,其十进制为861 。

3.逻辑代数的三种基本运算是与,或和非。

4.三态门的工作状态是0 , 1 ,高阻。

5.描述触发器逻辑功能的方法有真值表,逻辑图,逻辑表达式,卡诺图,波形图。

6.施密特触发器的主要应用是波形的整形。

7.设4位D/A转换器的满度输出电压位30伏,则输入数字量为1010时的输出模拟电压为。

8.实现A/D转换的主要方法有,,。

二.判断题(10)1.BCD码即8421码(错)2.八位二进制数可以表示256种不同状态。

(对)3.TTL与非门与CMOS与非门的逻辑功能不一样。

()4.多个三态门的输出端相连于一总线上,使用时须只让一个三态门传送信号,其他门处于高阻状态。

(对)5.计数器可作分频器。

(对)三.化简逻辑函数(14)1.用公式法化简--+++=ADDCEBDBAY,化为最简与或表达式。

解;D B A Y +=-2.用卡诺图化简∑∑=m d D C B A Y ),,,,()+,,,,(84210107653),,,(,化为最简与或表达式。

四.电路如图1所示,要求写出输出函数表达式,并说出其逻辑功能。

(15) 解;C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。

五.触发器电路如图2(a ),(b )所示,⑴写出触发器的次态方程; ⑵对应给定波形画出Q 端波形(设初态Q =0)(15) 解;(1)AQ Q Qn +=-+1,(2)、A Q n =+1六.试用触发器和门电路设计一个同步的五进制计数器。

(15)七.用集成电路定时器555所构成的自激多谐振荡器电路如图3所示,试画出V O ,V C 的工作波形,并求出振荡频率。

数字电子技术期末考试试题及答案(试卷一)

、 代入规则 对偶规则 反

演规则

、

。

5、为 了 实 现 高 的 频 率 稳 定 度 , 常 采 用 石英晶体

振荡

器 ; 单 稳 态 触 发 器 受 到 外 触 发 时 进 入 暂稳态 态

6、同步 RS 触发器中 R、S 为 高 电平有效,基本 R、S 触发器中 R、S

为低

电平有效

7、在进行 A/D 转换时,常按下面四个步骤进行, 采样 保持 量化 编

码、

、

、。Βιβλιοθήκη 二、选择题(每题 1 分,共 10 分)

1、有八个触发器的二进制计数器,它们最多有(

)种计数状态。

A、8; B、16; C、256; D、64

2、下列触发器中上升沿触发的是( )。

A、主从 RS 触发器;B、JK 触发器;C、T 触发器;D、D 触发器

3、下式中与非门表达式为( d ),或门表达式为(a )。

数字电子技术期末考试试题及答案(试卷一)

目录

数字电子技术期末考试试题及答案(试卷一) ........................................................................... 1 一、填空题(每空 1 分,共 20 分).............................................................................................2 二、选择题(每题 1 分,共 10 分).............................................................................................2 三、判断(每题 1 分,共 10 分):...............................................................................................3 四、数制转化(每题 2 分,共 10 分):.......................................................................................3 五、逻辑函数化简(每题 5 分,共 10 分):...............................................................................3 六、分析电路:(每题 10 分,共 20 分).....................................................................................4 七、设计电路(共 10 分).............................................................................................................4 试题答案(一)...............................................................................................................................5

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

试卷一

一填空题(每题2 分,共14 分)

•=( ) 16 。

•函数的反函数__________ 。

•一个10 位地址码、8 位输出的ROM ,其存储矩阵的容量为__________ 。

•单稳态触发器的主要用途为__________ 、__________ 和延时。

•一个8 位D/A 转换器的最小输出电压增量为0.02V ,当输入代码为

11011001 时,输出电压为__________ 。

•若一个8 位D/A 转换器的分辨率用百分数表示,则应是__________ 。

•已知TTL 与非门的特性如下: 输入电流mA ,40 m A 。

输出低电平时,输出电流最大为10mA ,输出高电平时,输出电流最大为1mA ,则其扇出系数N 0 =__________ 。

二、判断下图所示各电路接法的对错,对的打“ ? ”,错的打“ × ”。

(除特殊说明

外,均为TTL 电路)(8 小题,共16 分)

(1 )(2 )CMOS 电路

(3 )(4 )

(5 )(6 )

(7) (8)CMOS 电路

三用卡诺图化简逻辑函数,约束条件为。

将结果写成与非—与非形式。

(6 分)

四已知逻辑函数,(1 )用公式法化简为最简与- 或式。

(2 )用3 线-8 线译码器(逻辑符号如右图)和最少的门电路实现该逻

辑函数。

译码器输出低电平有效,使能端。

(10 分)

五在双积分式A/D 转换器中,计数器的最大计数容量为N 1 =(3000) 10 ,若参考电压V REF =+15V ,第二次计数值N 2 =(2000) 10 ,此时的输入模拟电压

为多少?输出数字量是多少?(4 分)

•

六用RAM2114 芯片构成和3 线-8 线译码器组成4K × 8 的RAM ,画出逻辑图。

(6 分)

七试用两片如图所示的四位二进制加法计数器74LS161 (Q 3 为高位端)构

成85 进制计数器。

要求两片之间采用同步级连及整体置数法置0 实现。

(8 分)

74LS161 功能表

CP

R

D LD EP ET

工作状

态

′ 0 ′ ′ ′ 清0

1 0 ′ ′ 预置数

′ 1 1 0 ′ 保持

′ 1 1 ′ 0 保持

1 1 1 1 计数

八设TTL 主从JK 触发器的初态Q n =0 ,试画出下图所示的输入信号作用下触发器的工作波形。

( 5 分)

•

九 D 触发器组成的电路如右下图所示,已知触发器的输入波形,画出输出波形Q 。

触发器的初态Q n =0 。

(5 分)

•

十如图所示电路( 1 )说明555(1) 和555(2) 分别接成什么电路;( 2 )试

分别画出当开关S 断开和闭合情况下V O 的波形。

(管脚说明:2- ,

3-OUT ,4- ,6-TH ,7-DISC ,8-Vcc )(8 分)

十一试分析如图所示电路,列出该时序电路的状态转换表。

(10 分)

十二已知输入为8421BCD 码,要求当输入小于 5 时,输出为输入数加 2 ,当输入大于、等于5 时,输出为输入数加6 。

试用一片如图所示的四位二进制加法器及与非门实现此电路。

要求写出必要的设计过程,并出画逻辑图。

(说明 A 0 ~A 3 为被加数,B 0 ~B 3 为加数,S 0 ~S 3 为和,C I 为低位进位,C O 为进位)(8 分)加法器。