modelsim仿真小结

ModelSim使用的一点心得- -

ModelSim使用的一点心得- -1、至今还没有弄明白为什么要用ModelSim,因为看波形Quartus II自带的工具就可以了啊。

2、我刚刚接触modelsim,我想大多数菜鸟跟我一样,看过如何使用ModelSim的介绍,说句实话,那些介绍写的都太过简单,仿佛大家都不屑写上一些比较“弱智”的步骤,恰恰就是这些看似累赘的步走,难为我好久。

教程上都写道,modelsim的简单使用方法如下:建立库- 影射库到物理目录- 编译代码- 启动仿真。

首先建立库就叫我头晕。

库的概念用在这儿实在不合适,把我吓坏了,也就没心思看下一步了。

在我看来,教程应该这么写:<1> 建立一个目录modelsimStudy。

用任何文本编辑器编辑一个简单的例子程序,比如计数器counter.vhd。

有clk、ena、reset输入,cnt作为输出。

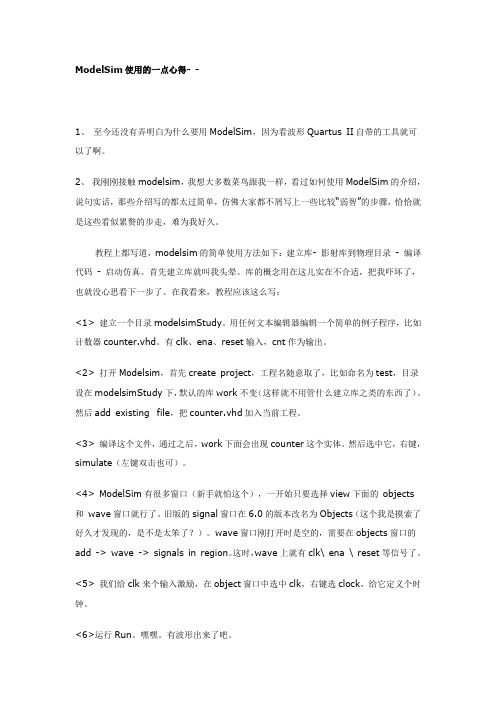

<2> 打开Modelsim,首先create project,工程名随意取了,比如命名为test,目录设在modelsimStudy下,默认的库work不变(这样就不用管什么建立库之类的东西了)。

然后add existing file,把counter.vhd加入当前工程。

<3> 编译这个文件,通过之后,work下面会出现counter这个实体。

然后选中它,右键,simulate(左键双击也可)。

<4> ModelSim有很多窗口(新手就怕这个),一开始只要选择view下面的objects 和wave窗口就行了。

旧版的signal窗口在6.0的版本改名为Objects(这个我是摸索了好久才发现的,是不是太笨了?)。

wave窗口刚打开时是空的,需要在objects窗口的add -> wave -> signals in region。

这时,wave上就有clk\ ena \ reset等信号了。

<5> 我们给clk来个输入激励,在object窗口中选中clk,右键选clock,给它定义个时钟。

ModelSim实验报告5

CPLD/FPGA 设计实验报告实验名称: 时序电路设计基础 实验目的: 掌握ModelSim 软件的基本使用方法,完成基本时序电路设计 实验内容:实验一 八位全加器一、 创建工程工程名称:t_add8二、编写一个测试文件,完成对8位全加器的仿真。

`timescale 1ns/1ns module t_add8; reg cin; reg[7:0] ina,inb; wire [7:0] sum;wire cout;parameter delay=100;add_8 u1(cout,sum,ina,inb,cin); initial begin ina=8'd0;inb=8'd0;cin=1'd0;#delay ina=8'd0;inb=8'd0;cin=8'd0; #delay ina=8'd50;inb=8'd200;cin=1'b1; #delay ina=8'd150;inb=8'd230;cin=1'b0; #delay ina=8'd200;inb=80;cin=1'b0; #delay ina=8'd220;inb=60;cin=1'b1; #delay ina=8'd100;inb=8'd80; #delay ina=8'd240;inb=8'd20;#delay ina=8'd255;inb=8'd255;cin=1'b1;#delay $stop;endinitial $monitor($time,,,"%d+%d+%d={%b,%d}",ina,inb,cin,cout,sum); endmodule三、源码。

module add_8(cout,sum,ina,inb,cin); input cin;装订线input[7:0] ina,inb;output[7:0] sum;output cout;assign{cout,sum}=ina+inb+cin;endmodule四、仿真结果。

关于simulink,modelsim仿真的小结

MODELSIM学习笔记(二)Dsp Builder设计初步的小结杨森Sept 2015现在使用的软件版本分别是 quartusii 11.0 ,modelsim 10.0c, matlab 2010b ,关于软件的安装以及相互之间的关联,做一个简要的说明。

主要需要注意的是,1.必须在安装dsp builder之前安装matlab;2.dsp破解后(若不破解,simulink中的dsp的库文件不能使用),设置环境变量;3.dsp builder破解过程会生成一个license,这个和之后安装的modelsim生成的license需要共用一个环境变量,所以,可以把两个license合并(把其中一个拷到另外一个最后面);软件相互之间能够关联非常重要,否则后面会出现很多意想不到的问题。

我一开始是按照“EDA技术与VHDL(第三版潘松著)”一书中第九章dsp builder设计初步来做的,课本里说使用tcl脚本文件,不知道是不是由于软件版本的原因,根本无法产生想要的结果,故花了一周左右的时间研究modelsim的使用方法。

在这过程中,出现了各种各样的bug,在崩溃的边缘,最后还是依靠各种网络上的资源片段,一个一个warning和error的调试,最终把所有的仿真给做出来了。

我之所以这么执着于仿真,是因为我后期需要做一个FIR的滤波,在simulink中来做,非常的方便,但是,若不进行rtl级仿真和时序仿真,根本不知道转换过来的vhdl代码能不能使用,这是闲话哈,好了,开始我们的操作过程中遇到的问题的详述吧。

本文主要是关于modelsim的RTL级仿真,后面还会陆续有关于时序仿真的教程,如果有童鞋遇到的难题,可以相互讨论一下,我的联系方式:邮箱:senyangah@主要的过程1.完成一个例程其实很多软件都一个共性,那就是,看再多的例程都不如亲手完成一个设计.网上关于各种初级教程有很多,但是,大多数情况是,你跟着教程一步一笔的去做,根本出现不了你想要的结果,我选择了2个稍微比较好一点的教程,并且里面出现的一些小的bug都已经通过注释给讲明了怎么改.本来我也是打算自己写一个教程,一步一步的把操作步骤写下来,但是我发现,首先就是完全没必要啊,网上给的教程的大致过程都是对的,其次就是这个太耗时间了,所以原谅我的偷懒哈,附件中的教程2和教程3,都是可以仿真成功的,大家跟着做就行啦~其中教程2是使用的自动编译,从quartus中直接启动modelsim,教程3是手动编译,第一个例子是使用vism的命令进行操作的,虽然很繁琐,但是对于初学者来说,了解各个参数的设置是很好的,后面的例程通过编写testbench来进行仿真,这种方式是我们以后进行仿真的主要模式.2.Testbench的编写因为本文主要是围绕着simulink生成的vhdl的modelsim仿真来编写的,所以,我们主要介绍的是怎样使用vhdl来编写testbench,附件中教程4,就是用vhdl来编写testbench,以后我们每次需要编写testbench的时候,就先通过quartus来生成一个testbench模板,然后按照教程4中的模板进行各个参数的设置.关于怎么生成testbench的模板,教程2中有说明.3.关于library的添加如果代码是我们编出来的,那么在用modelsim进行仿真的时候,无需添加任何的library,但是若使用到IP核(比方说product模块吧),则需要添加library,原因可以问度娘哈.关于怎么添加library,教程5非常的好用,这里面有几个主要的关键点需要注意:1.教程5的前几个库添加的时候,一定要注意每个VHD文件添加的顺序,比方说:先添加altera_mf_components.vhd后ALTERA_MF.vhd,一个一个的添加,如果一下子全部的话,会有报错。

ModelsimNC-Verilog仿真理解

ModelsimNC-Verilog仿真理解Modelsim/NC-Verilog仿真理解仿真(Simulation),也称为模拟,是对所有集成电路或系统的一种检测方法。

用户可以在设计过程中对整个系统和部分模块进行仿真,即在计算机上用仿真软件验证功能是否正确、各部分的时序配合是否正确。

如果有问题可以随时进行修改,从而避免逻辑错误。

高级的仿真软件还可以整个系统设计性能进行评估。

设计规模越大就越需要进行仿真。

仿真包括功能仿真和时序仿真。

在设计输入阶段按进行仿真,不考虑信号延时等因素成为功能仿真,又称前仿真;时序仿真又称为后仿真,他在选择了具体器件并完成了布局布线以后进行的含定时关系的仿真。

由于不同器件的内部延时不同,不同的布局、布局方案也给延时造成了很大的影响,因此在设计实现后,对网络和逻辑块进行延时仿真,分析定时关系,估计设计性能非常有必要。

要进行电路仿真必须有仿真器的支持。

常用的Verilog仿真器有:ModelSim、Verilog-XL、NC-Verilog和VCS等。

下面我们简单介绍下我们常用到的ModelSim、NC-Verilog两款仿真软件特点、区别。

一、ModelSimModelSim是Mentor Graphics子公司ModelSim Technology 的产品,是业界优秀的HDL 语言仿真软件之一,它是编译型的VerilogHDL/VHDL混合仿真器。

MoselSim可以在同一设计中单独或混合使用Verilog HDL和VHDL,允许Verilog HDL模块调用VHDL 的实体,或用VHDL模块调用Verilog HDL的实体。

由于ModelSim 是编译型仿真器,使用编译后的HDL 库进行仿真,因此在进行仿真前,必须所有待仿真的HDL文件编译成为HDL仿真库,在编译时使源文件获得优化,提高了仿真速度。

Model Sim只完成逻辑功能的仿真,并不考虑具体使用什么器件,学习HDL或者设计逻辑的时候compile一次所用的时间很短,便于调试找出逻辑的错误。

altera_modelsim6.1g仿真总结

软件环境说明:quartusII 7.2 sp3+altera_modelsim6.1g(作者:刘国华)1,软件的安装详细请看《如何破解ModelSim-Altera 6.1g.pdf》。

(一个注意的地方就是环境变量设置完后一定要重新启动)2,软件的设置《如何解決在Quartus II无法使用ModelSim-Altera模拟的問題.pdf》。

3,用altera_modelsim6.1g做功能仿真,设置地方有3处如下:接着就是运行仿真软件,进行仿真:方法有两种:①编译完后,通过自动运行②编译完后,手动运行,一般运行Gate Level Simulation仿真图如下,由于是功能仿真,所以没有延时信息出现:4,关于do文件的使用技巧问题:执行的默认脚本在:工程所在目录\simulation\modelsim下,例如我的工程:该do文件的内容为:transcript onif {[file exists gate_work]} { #判断库是否存在,存在的话就先删除vdel -lib gate_work -all}vlib gate_work #建立一个库vmap work gate_work #映射库vlog -vlog01compat -work work +incdir+. {counter.vo} #编译文件vlog -vlog01compat -work work +incdir+E:/pratice/verilog/my_counter {E:/pratice/verilog/my_counter/testbench.v} #编译文件vsim -t 1ps -L cyclone_ver -L gate_work -L work top_tb #启动仿真add wave * #把testbench.v的顶层信号加入到波形窗口中view structureview signals #打开信号窗口run –all #执行仿真、modelsim窗口指示的就是这个脚本:如把以下的选项勾起,并指定一个do文件:这个时候上面那个counter_run_msim_gate_verilog.do文件的脚本就会发生以下变化:transcript onif {[file exists gate_work]} {vdel -lib gate_work -all}vlib gate_workvmap work gate_workvlog -vlog01compat -work work +incdir+. {counter.vo}vlog -vlog01compat -work work +incdir+E:/pratice/verilog/my_counter {E:/pratice/verilog/my_counter/testbench.v}vsim -t 1ps -L cyclone_ver -L gate_work -L work top_tb#执行自己写的do文件,这样的话,就可以很好的控制自己想看的信号do E:/pratice/verilog/my_counter/simulation/modelsim/my.domy.do文件如下:view signalview waveadd wave *#将设计文件的内部信号cnt以无符号十进制的形式加入到波形图add wave -radix unsigned /top_tb/tb_counter/cntrun –all5,用altera_modelsim6.1g做布局布线后的仿真(后仿真),设置地方有2处如下:仿真图如下,可以看到下图明显存在延时信息:。

quartus与modelsim联合仿真步骤总结自己

1.首先安装好quartus和modelsim2.复制altera quartus eda sim_lib 中对应芯片的.v文件到modelsim文件夹内3.打开quartus新建工程在第四步eda tool setting 中simulation选项中选择modelsim 语言默认为veillog 后面不打勾4.assignments settings eda stimulation工具选择modelsim 路径选择modelsim安装的路径写到win32这一步点击确定至此准备工作全部完成5.写veillog 程序然后保存编译编译后会在我们的工程目录下生成simulation文件夹,里面又有一个modelsim文件夹。

6.创建或者是编写testbench引导文件简单的可以创建复杂的需要自己编写quartus自己创建不了这是一个端口引导文件目的是建立modelsim和quartus之间的桥梁能够让modelsim创建出我们需要的与quartus中相匹配的端口并且执行相同的功能这些功能执行信息都存放在了testbench引导文件当中7.创建testbench文件过程:Processing->Start->Start Test Bench Template Write这时创建的testbench文件存放在4中所说的modelsim文件夹中以.vt为后缀名以工程名命名8.添加该文件:Assignments->EDA Tool Settings选择Simulation设置仿真环境在NativeLink settings中选择Compile test bench并点击后面的Test Benches 在Test Benches中点击New设置Test Bench属性在Test bench entity栏一定要填写刚刚我们创建的testbench文件的实体名即module top_vlg_tst();中的top_vlg_tst。

基于脚本的modelsim自动化仿真笔记

基于脚本的modelsim⾃动化仿真笔记 这⾥记录⼀下基于脚本的modelsim⾃动化仿真的⼀些知识和模板,以后忘记了可以到这⾥查找。

转载请标明出处:。

⼀、基本介绍 这⾥介绍⼀下如何利⽤脚本调⽤modelsim进⾏⾃动化仿真,随笔前⾯先介绍⼀下前仿真,随笔结尾处介绍后仿真。

前仿真的基本介绍如下所⽰,由于我的笔记是写在.do⽂件中,因此我这⾥也给代码的格式,如下所⽰:# #表⽰注释,modelsim不⽀持中⽂,因此可能不能识别注释#①退出当前仿真功能,退出当前的⼯程,跟在modelsim界⾯的命令⾏敲⼊命令的效果⼀样,之后就可以创建其他的⼯程quit -sim#②清除命令⾏显⽰信息;在命令⾏‘敲⼊这个命令,回车’的效果⼀样.main clear#③创建库:vlib:创建库到⼀个物理⽬录中,也就是创建⽂件夹⽬录了。

#可以理解库为某⼀个路径的⽂件夹,⽤来存储modelsim的⼀些数据⽂件;#创建库的格式vlib <library name>,默认库的名字为work#下⾯的代码意思是:1-在当前路径(.do⽂件的路径)下,创建lib⽂件夹;相当于在命令⾏敲‘vlib lib 回车’#2-在当前路径的lib⽂件夹下,创建work⽂件夹库;相当于在命令⾏敲‘vlib ./lib/work’vlib ./libvlib ./lib/work#④映射逻辑库到物理⽬录;也就是说,在modelsimGUI界⾯的Library选项卡⾥⾯创建⼦选项,这个⼦选项就叫做逻辑库,#编译⼯程之后,得到⼀堆编译⽂件,这些⽂件名就放在这个逻辑库选项卡⾥⾯。

但是编译得到的是实体⽂件,这些⽂件必须#有⼀个⽬录存储,因此就需要把逻辑库映射到物理(⽂件夹)⽬录,也就是把那些得到的实体⽂件放在某⼀个⽂件夹⽬录(路径当中)#这样,就可以在实际⽂件夹⾥⾯查看编译得到的⽂件内容,⽽不是单单从选项卡⾥⾯看到名字⽽已#注意,在映射之前,⼀定要先创建好对应的物理路径#语法为 vmap work(逻辑库名称) <library name>(库的路径)#下⾯的代码意思是:在modelsim界⾯的library选项卡创建⼀个叫work的选项卡(逻辑库),编译之后得到的⽂件名称就在,#相应的⽂件就放在./lib/work这个⽂件夹⾥⾯。

想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀

想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀。

为了这个问题,我在网上找了很多的资料,但发现这些资料往往说的不明白。

一些步骤被作者有意无意地省略掉,这常常给读者造成不必要的麻烦,所以我决定写下这一篇文章,把这3天我努力的结果拿出来,与大家分享。

首先,我把我用到的软件说明一下。

如果你发现根据我的操作,你还是解决不了ModelSim后仿真的问题,那就可能是软件版本的问题。

1, ModelSim Se 6.1b2, Synplify Pro 7.5.13, ISE 5.2i (这个是老了点)4, WindowsXP(这个应该没有多大的关系)还有就是我使用的是verilog,我想VHDL的方法与verilog是差不多的,最多也就是在建库方面有点差别而已。

下面的这些方法,是我这3天搞出来的。

当然也参考了一些文章。

如果谁有更方便的方法,欢迎指出来。

我的邮箱是****************。

有空大家多交流。

一、为modelsim生成3个库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

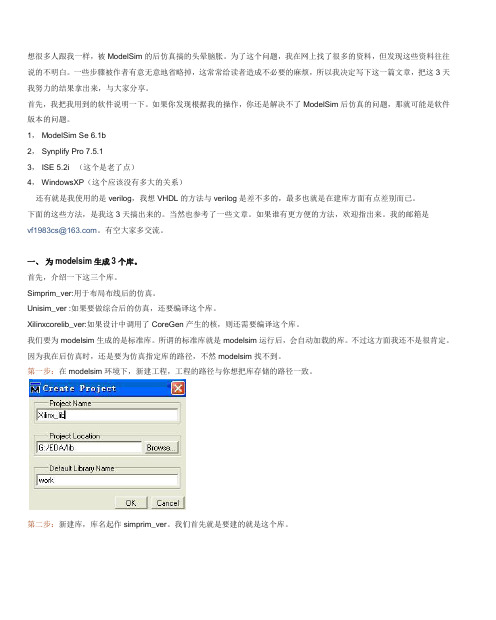

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver d:/Xilinx/verilog/src/simprims/*.v其中的d:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Modelsim仿真小结Modelsim的基本仿真流程大致分以下几个步骤:建库、编译工程、前后仿真、调试等。

Modelsim仿真既可以在modelsim界面操作,也可以用do文件实现,这里结合学习的教程、网上看到的资料,和实际遇到的一些问题,分别做一整理小结。

1.建库建库包括Altera库和Xilinx库,同时都包括Verilog和VHDL。

这里只建了Verilog库,VHDL和Verilog步骤相同。

对于Altera库主要包括lpm元件库、Mega_Function库atera_mf、altera原语库altera_primitive和各器件系列模型库。

前三种是调用altera模块的必备库,第四种是进行综合后功能仿真和布线后时序仿真需要的库,和器件系列有关,只选对应系列即可。

Altera库创建和编译步骤如下:a)在Modelsim安装目录下新建文件夹,命名altera_lib,以存放编译后的库文件,可以在altera_lib下新建Verilog和VHDL两个子文件夹,分别存放Verilog和VHDL库。

b)打开Modelsim,新建Library,file ->new->library ..c)如下图,创建lpm库,路径E:\modeltech_10.1a\altera_lib\Verilog\lpmd)添加库文件,并编译,compile -> compile …,出现compile source files窗口,library 指定到lpm下,查找范围,选quartus安装目录下… eda\sim_lib目录里的仿真原型文件:220model.v ,点c ompile ,点done。

到此,lpm库建立完毕。

e)同理,建立altera_mf库添加altera_mf.v ,建立primitive库添加altera_primitive.v建立各系列的模型库,命名可用系列名加_ver“xxx_ver”,也可随意吧,添加各系列的xxx_atoms.v。

这里,也可以把以上库放在一个文件夹,这样做简单,一次就搞定,分开也就是条理清楚,没人去看,所以没必要。

f)修改modelsim.ini文件,为的是让modelsim能自动map到已经编译的这些库上。

先去掉只读属性,在[Library]和[vcom]之间加上:库名=库路径[绝对路径或者相对路径],相对路径是相对于modelsim安装路径,modelsim安装路径用$MODEL_TECH 表示。

这里所有库都放在E:\modeltech_10.1a\altera_lib下,库名是altera_lib,这里只添加一句:altera_lib = E:\modeltech_10.1a\altera_libg)保存退出,改回modelsim.ini只读属性,防止乱改。

至此altera库建立完毕。

Xlinx库创建和编译步骤如下:相比altera,xilinx建库很方便。

xilinx有批处理命令,直接在console命令窗口,输入compxlib命令,调出编译库的窗口,先改掉modelsim安装目录下modelsim.ini只读属性。

设置如下图:Next,选择语言:Next,选择需要编译的器件:Netx -> next,选择输出路径,launch compile process,等待编译完成。

完成后改回modelsim.ini只读属性。

至此xilinx库建立完毕。

2.编译工程编译工程主要包括:code、testbench、建立工程、建立工程库、映射、编译等。

Code 主要有code思想和风格,在Verilog部分涉及。

Testbench,下边给出一个公用模板,基于这个方便修改,可以根据自己的习惯建一个temp_tb.v。

Modelsim界面编译工程:a)新建工程:打开modelsim,file -> new -> project .. ,指定工程名、路径、工程库。

b)Add existing filec)Add testbench file ….d)编译,compile –> complie alle)编译语法查错,直到编译通过。

至此编译完毕。

3.功能和时序仿真仿真是在编译的基础上,进行的功能调试,包括综合前功能仿真、综合后功能仿真和布局布线后时序仿真。

Modelsim界面综合前仿真:a)指定顶层,开始仿真;simulation -> start simulation …,在work 库中,指定testbench,ok,开始仿真。

b)查看仿真结果,打开wave,信号,加入wavec)运行,查看波形。

Run -> run all ….至此,简单的modelsim界面综合前仿真介绍完毕。

Modelsim界面综合后仿真:综合后仿真需要quartus综合后的网表文件(以altera为例),a)综合后的网表的生成: quartus工程名右键-> setting –> EDA Tool Setting, 双击Simulation ,选择EDA软件modelsim,选择输出网表路径,如图b)More settings ….将Generate netlist for functional simulation only设置为ONc)保存,全编译。

d)检查一下…/modelsim/Psyth/source 里面,可以发现,已经生成了一个*.vo 文件。

这个就是需要的网表文件。

(VHDL 的输出网表是*.vho 后缀名的)e) 将vo文件添加到工程,指定TestBench 文件top_tb.v,同前边一样进行仿真。

e)得到的仿真结果Modelsim界面布局布线后仿真:布局布线后仿真需要综合网表文件和添延时文件*.sdo(Verilog)或*_vhd.sdo(VHDL);a)QuartusII 里面设置重新把Generate netlist for functional simulation only 设置成OFF。

b)指定延时文件c)运行,查看波形,波形带有延时4.用tcl文件.do 进行modelsim仿真在modelsim中使用do文件是非常方便的进行仿真的一种方法,的项目比较大,特别是几个人分开做的时候,前后模块的联合仿真比较重要,查看的信号比较多,使用了do文件可以自动仿真,省去很多体力活。

下面是编写do文件的一般步骤:a). quit -sim : 首先退出原来仿真的工程。

b). cd: 设置工作目录的路径,就是你所要建立的工作目录work要放在哪里。

c). vlib work: 在工作目录下建立一个work目录,请注意不要用操作系统直接新建一个work的文件夹,因为用操作系统建立的work文件夹并没有modelsim SE自动生成的_info文件。

还有个问题是,当你的软件工程里需要用到软核时,可能会需要一些库,但这些库ISE软件中是没有的,此时就需要我们自己新建库了,并映射到当前目录下。

我们只自己新建的库一般放在work库前面建立。

d). vmap work :将新建的work库映射到当前工作目录下(当前目录就是第一步中的目录了)。

其他新建的库也要这样的方法映射。

e). vlog +acc –work work “file_path/*.v”: 编译“file_path”目录下所有.v文件,并将其添加进工作库(work)中,包括IP生成的V文件也要编译的。

或者:vlog -f top_tb.f,top_tb.f是.v的列表文件。

编译时可以分开单独编译,但是一定要注意顺序,先编译被调用的文件。

在综合后仿真和布局布线后仿真的时候,这里添加综合后网表和tb即可。

VHDL 用vcom编译。

对于xilinx工程在仿真的时候还需要用到一个文件,那就是glbl.v这个库文件。

它是存放在xilinx安装目录下,我们直接编译它并添加时工作库(work)就可以了。

特别需要说明的是,在仿真软核的时候,在XPS软件里点击simulation -> generate simulation hdl files会在工程目录中生成一个simulaton文件夹,这个文件夹里的东西就是软核仿真时所需要的仿真文件了。

所以我们需把simulaton里所以的v文件都编译一次,这样才能仿真软核。

f). vsim -L altera_lib -novopt work.top_tb:这是没有调用IP Core时的仿真命令,注意后面的参数top_tb必须为Testbench中的模块名。

布局布线后仿真是这里要指定延时文件,vsim -L altera_lib -novopt -sdfmax /top_tb/top=top_v.sdo work.top_tbg). do vawe.do运行添加wave tcl,这里可以给信号分组,添加颜色,设置波形属性等。

h). run –all 设定运行时间,run 1000ms等。

i). 在do里可以用file copy/file delete 来对临时文件进行操作。

至此,modelsim仿真总结完毕。

这里仅为了简单记录仿真方法和流程,旨在简单明了,对更深入的和更详细的有待进一步补充。

附件一、testbench 模板////////////////////////////////////////////////////////////////////////////////// Company: <Company Name>// Engineer: <Iyoyoo>//// Create Date: <date>// Design Name: <name_of_top_level_design>// Module Name: <top_tb>// Target Device: <target device>// Tool versions: <tool_versions>// Description:// <top_tb for top.v simulation in modelsim>// Dependencies:// <sub module....>// Revision:// <v1.0>// Additional Comments:// <This is a testbench temp file for verilog>////////////////////////////////////////////////////////////////////////////////`timescale 1ns / 1psmodule top_tb;//*************************Parameter Declarations******************************parameter CLK_PERIOD = 20 ; //clk = 50Mhz//************************Internal Declarations***********************//************************** Register Declarations ****************************reg clk ;reg reset;//********************************Wire Declarations**************************//******************************Main Body of Code***************************//--------------------------------- initial reg data ---------------------------------initialbeginend//---------- Generate Reference Clock input to tb ----------------initialbeginclk = 1'b1;endalways#(CLK_PERIOD/2) clk = !clk;//--------------------------------- Resets ---------------------------------initialbeginrst_n = 1'b1;#(10*CLK_PERIOD) rst_n = 1'b0;#(100*CLK_PERIOD) rst_n = 1'b1;end//----------------------------- Data Transfer---------------------------------initialbegin#(10*CLK_PERIOD);@(negedge data)beginendend//----------------------------- simulation end ---------------------------------initialbegin#(10*CLK_PERIOD);if ( ) //end signbegin$display("------- TEST PASSED -------");endelsebegin$display("####### ERROR: TEST FAILED ! #######");end$stop;end//------------------------ Instantiate TOP module ------------------------top #(.parameter1 (1), //.parameter2 (0) //)top_inst(.a (a),);Endmodule////////////////////////////////////////////////////////////////////////////////附件二、do 模板////////////////////////////////////////////////////////////////////////////////#!/bin/bash#this bash shell document is used to verilog project simulation#author:iyoyooecho "***************** end pre-project ********************************"quit -simecho "***************** go to work dir ********************************"#cd /#cd D:/quartus/EP4CE15F/lcd/simulationecho "***************** start to setup work lib************************" vlib workecho "***************** start to compile ******************************" vlog -f top_tb.fecho "***************** set up reference library ***********************" vmap altera_lib E:/modeltech_10.1a/altera_libecho "***************** delet pre-temp files *************************" #file delete ../simulation/pika_ani.mif#file delete ../simulation/modelsim/top_v.sdoecho "***************** copy temp file *********************************" #file copy ../source/pika_ani.mif ../simulation/#file copy ../simulation/modelsim/top_v.sdo ../simulation/echo "***************** start to simulation **************************" #-pli novas.dll --- for debussy#-sdfmax /top_tb/top=top_v.sdo -----for post synthesis simvsim -L altera_lib -novopt work.top_tbecho "***************** add signal to vawe **************************" do vawe.doecho "***************** start to run ******************************" run -allecho "***************** delete temp files ***************************"#file delete ../simulation/pika_ani.mif#file delete ../simulation/modelsim/top_v.sdo//////////////////////////////////////////////////////////////////////////////// 附件三、file.f模板//////////////////////////////////////////////////////////////////////////////// +licq_all++access+r//../simulation/modelsim/top.vo -for post synthesis simulation../source/top.v../simulation/top_tb.v+libext+vmd+.v-y $QUARTUS_ROOTDIR/eda/sim_lib////////////////////////////////////////////////////////////////////////////////附件三、file.f模板////////////////////////////////////////////////////////////////////////////////view signals stucture waveonerror {resume}quietly WaveActivateNextPane {} 0#-color Green for all signal is green#-color Green Blue Yellow Pink Orchid Red Salmon Orange# top_tb groupadd wave -itemcolor Blue -noupdate -expand -group top_tb -format Logic -radix hexadecimal /top_tb/*# sub groupadd wave -itemcolor Green -noupdate -expand -group sub -format Logic -radix hexadecimal /top_tb/sub/*TreeUpdate [SetDefaultTree]WaveRestoreCursors {{Cursor 1} {10000 ns} 0}configure wave -namecolwidth 364configure wave -valuecolwidth 100configure wave -justifyvalue leftconfigure wave -signalnamewidth 0configure wave -snapdistance 10configure wave -datasetprefix 0configure wave -rowmargin 4configure wave -childrowmargin 2configure wave -gridoffset 0configure wave -gridperiod 1configure wave -griddelta 40configure wave -timeline 0configure wave -timelineunits psupdateWaveRestoreZoom {10000 ns} {10000 ns}////////////////////////////////////////////////////////////////////////////////。