基于可编程计数器的时序逻辑电路设计

时序逻辑电路的设计方法

时序逻辑电路的设计方法时序逻辑电路是一类通过内部的记忆元件来实现存储功能的数字电路,它能够根据输入信号的时序变化来决定输出信号的状态。

常见的时序逻辑电路包括时钟发生器、时钟分配器、触发器、计数器等。

在设计时序逻辑电路时,需要考虑到电路的功能要求、时序要求、稳定性和可靠性。

本文将介绍时序逻辑电路的设计方法。

1.确定功能要求:首先需要明确时序逻辑电路的功能要求,即输入信号和输出信号之间的逻辑关系。

可以通过真值表、状态转换图、状态方程等方式进行描述。

根据功能要求,可以确定电路中需要使用到的逻辑门、触发器等元件。

2.确定时序要求:在时序逻辑电路中,输入信号的变化必须满足一定的时序要求,通常需要使用时钟信号来进行同步控制。

时钟信号是一个周期性的信号,控制电路在时钟的上升沿或下降沿进行状态的改变。

时序要求还包括时序逻辑电路在不同输入组合下的稳态和状态转换时的时间要求。

3.设计电路结构:根据功能要求和时序要求,可以确定时序逻辑电路的整体结构。

电路结构的设计包括将逻辑元件(例如逻辑门、触发器)按照特定的方式连接起来,以实现所需的功能。

常见的电路结构包括级联结构、并行结构、环形结构等。

4.选择逻辑元件:根据电路的功能和时序要求,选择合适的逻辑元件来实现电路的功能。

常见的逻辑元件包括与门、或门、非门、异或门等。

触发器是时序逻辑电路的核心元件,常用的触发器包括D触发器、JK触发器、T触发器等。

5.进行逻辑功能实现:将所选择的逻辑元件按照电路结构进行连接,并完成时序逻辑电路的逻辑功能实现。

这一步可以使用绘图工具进行电路图的绘制,也可以通过硬件描述语言(HDL)进行电路的逻辑设计。

6.时序优化:对设计的时序逻辑电路进行时序优化。

时序优化可以通过调整逻辑元件的连接方式、引入时序优化电路等方式来提高电路的性能和可靠性。

时序优化的目标是尽可能满足时序要求,减少信号传输延迟和功耗。

7.进行电路仿真和验证:对设计的时序逻辑电路进行仿真和验证。

可编程逻辑电路设计实验

可编程逻辑电路设计实验一、实验目的1.理解可编程逻辑器件(如FPGA)的原理和工作方式;2.掌握VHDL语言的基本语法和编程方法;3.学习使用开发工具进行电路设计和仿真;4.熟悉设计流程,培养实践操作能力。

二、实验原理1.可编程逻辑器件原理可编程逻辑器件(FPGA)是一种可重构的数字电路,可以通过编程方式配置其内部电路,实现各种逻辑功能。

FPGA由可编程逻辑单元(PLU)、输入输出模块和配置存储器组成,其中PLU是FPGA的核心部分,由一系列可编程查找表(LUT)组成,LUT可以存储逻辑功能和状态信息。

2.VHDL语言简介VHDL(VHSIC Hardware Description Language)是一种用于描述数字电路的硬件描述语言,它允许工程师用一种类似于C语言的描述方法来开发和测试电路。

VHDL可以描述电路的结构、行为和时序特性,具有很强的可移植性和灵活性。

三、实验环境和工具1. 实验环境:Windows操作系统;2. 开发工具:Xilinx ISE Design Suite。

四、实验内容本次实验中,我们要设计一个简单的计数器电路,并通过FPGA进行仿真验证。

计数器电路的原理如下:1.通过按键输入信号,控制计数器的工作方式:上升沿触发或下降沿触发;2.计数器可以进行增计或减计,最大计数值为7;3.计数器的输出结果通过LED灯显示出来。

五、实验步骤1. 在Xilinx ISE Design Suite中创建新工程,并设置工程的基本参数,如工程名称和目标设备;2.在ISE中创建新的源文件,并编写VHDL代码来描述计数器电路的结构、行为和时序;3. 对VHDL代码进行综合、布局和路由,生成对应的bit文件;5.在FPGA板上调试和测试设计的电路。

六、实验结果与分析经过实验,我们成功设计了一个简单的计数器电路,并通过FPGA进行了仿真验证。

通过按键控制,我们可以观察LED灯随着计数器的计数进行增亮或减弱的变化。

基于可编程逻辑器件的数字电路设计

基于可编程逻辑器件的数字电路设计作者:刘彩虹,陈秀萍来源:《现代电子技术》2009年第19期摘要:可编程逻辑器件的出现,使得传统的数字系统设计方法发生了根本的改变,所以有必要介绍一下基于可编程逻辑器件的数字电路设计方法。

以计数器的实现方法作为实例,介绍了采用原理图和硬件描述语言两种方法作为输入,实现计数器的方法,并描述了编译仿真的方法,给出了对应的仿真结果。

采用熟悉的器件为例,使基于可编程逻辑器件的数字电路设计方法更容易理解掌握。

关键词:可编程器件;计数器;数字电路;VHDL中图分类号:TN47文献标识码:A文章编号:1004-373X(2009)19-189-02Design of Digital Circuit Based on Programmable Logic DevicesLIU Caihong,CHEN Xiuping(Northwest Minorities University,Lanzhou,730030,China)Abstract:The traditional design method of digital systems has fundamentally changed because of the emergence of programmable logic devices,it is necessary to introduce the design of digital circuit based on the programmable logic device.The realization methods of counter as examples,described two ways to achieve counter by schematic and hardware description language as input methods.The method of compiled simulation was described,and given the simulation results.The design of digital circuit based on the programmable logic device easier to understand and grasp by the use of familiar device.Keywords:programmable logic devices;counter;digital circuit;VHDL0 引言可编程逻辑器件PLD(Programmable Logic Device)是一种数字电路,它可以由用户来进行编程和进行配置,利用它可以解决不同的逻辑设计问题。

时序逻辑电路的设计与实现

时序逻辑电路的设计与实现时序逻辑电路是数字电路中的一种重要类型,它可以根据输入信号的变化和先后顺序,产生相应的输出信号。

本文将介绍时序逻辑电路的设计与实现,并探讨其中的关键步骤和技术。

一、概述时序逻辑电路是根据时钟信号的变化产生输出信号的电路,它可以存储信息并根据特定的时序条件进行信号转换。

常见的时序逻辑电路包括触发器、计数器、移位寄存器等。

二、时序逻辑电路的设计步骤1. 确定需求:首先需要明确所要设计的时序逻辑电路的功能和性能需求,例如输入信号的种类和范围、输出信号的逻辑关系等。

2. 逻辑设计:根据需求,进行逻辑设计,确定逻辑门电路的组合方式、逻辑关系等。

可以使用真值表、状态转换图、状态表等方法进行设计。

3. 时序设计:根据逻辑设计的结果,设计时序电路,确定触发器的类型和触发方式,确定时钟信号的频率和相位,以及信号的启动和停止条件等。

4. 电路设计:将逻辑电路和时序电路整合,并进行布线设计。

通过选择合适的器件和元器件,设计稳定可靠的电路。

5. 功能验证:对设计的时序逻辑电路进行仿真验证,确保电路的功能和性能符合设计要求。

三、时序逻辑电路的实现技术1. 触发器:触发器是时序逻辑电路的基本组成部分,常见的触发器有RS触发器、D触发器、T触发器等。

通过组合和串联不同类型的触发器,可以实现不同的功能。

2. 计数器:计数器是一种特殊的时序逻辑电路,用于计数和记录输入脉冲信号的次数。

常见的计数器有二进制计数器、十进制计数器等。

3. 移位寄存器:移位寄存器是一种能够将数据向左或向右移位的时序逻辑电路。

它可以在输入端输入一个位串,随着时钟信号的变化,将位串逐位地向左或向右移位,并将移出的位存储起来。

四、时序逻辑电路的应用领域时序逻辑电路广泛应用于数字系统中,例如计算机中的控制单元、存储器等。

它们在数据处理、信息传输、控制信号处理等方面发挥着重要作用。

总结:时序逻辑电路的设计与实现是一项复杂而重要的任务。

在设计过程中,需明确需求、进行逻辑设计和时序设计,并通过合适的触发器、计数器和移位寄存器等元件来实现功能。

时序逻辑电路设计

时序逻辑电路设计1.以一个计数器74161为核心器件和少量门电路,设计一个带同步清0功能的5421BCD码计数器:电路有清0输入控制端R,当R=0时,同步清0;当R=1时,按5421BCD码规则同步计数,注意不能有过渡态。

5421BCD码编码规则:0~9分别为:0000、0001、0010、0011、0100、1000、1001、1010、1011、1100。

请写出设计过程。

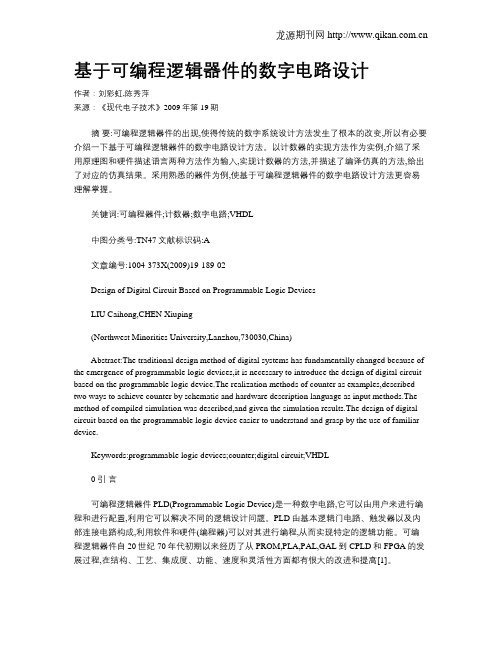

2 试用JK触发器及与非门设计一个具有异步清零功能的2421BCD码十进制同步计数器,不要求自启动分析。

2421BCD码如下表所示:3.分析由移位计数器74194组成的时序,画出电路状态图?(排列次序:Q0 Q1 Q2 Q3功另外S1 S0=00,保持;S1 S0=01,右移;S1 S0=10,左移;S1 S0=11,置数。

)5 分析如图所示的电路功能,假设Q2Q1初态为00。

6.分析图中所示的时序电路,其中74283为四位加法器、74175为4D寄存器、14585为四位比较器,Y为输出。

画出状态转换图并说明电路功能。

7. 用JK触发器和门电路设计三位格雷码同步加法计数器,具有进位Y输出,要求:1、画出状态转换图;2、写出驱动(激励)方程、输出方程;3、画出逻辑电路图。

8. 试用两块十进制同步加法计数器74LS160及必要的其它器件实现可变模计数器,要求:①当A=0时,实现24进制计数器;当A=1时,实现60进制计数器;②不能有过渡状态;③写出设计过程,画出逻辑电路。

9. 试分析图5所示电路的功能(D IL 为左移数据输入), 按照(3210Q Q Q Q )画出状态图,并检查自启动。

10. 用D 触发器和必要的门电路设计一个序列信号发生器,使其输出信号Y 的周期为时钟CLK 周期的7倍,其输出波形如下图所示. 要求:1、画出状态转换图;2、写出驱动(激励)方程、输出方程;3、画出逻辑电路图.11. 图中为某时序的状态转换图,试用JK 触发器设计此同步时序电路,要求:(1)写出次态卡诺图、求出驱动方程; (2)画出逻辑电路图; (3)检查电路能否自启动。

fpga现代数字系统设计教程——基于xilinx可编程逻辑

fpga现代数字系统设计教程——基于xilinx可编程逻辑1. 引言1.1 概述:在当今数字系统设计领域,快速、高效的设计流程和可靠的硬件实现是至关重要的。

而可编程逻辑器件(FPGA)作为一种灵活且可重构的芯片,正逐渐成为数字系统设计中的主流选择。

本教程将介绍如何利用Xilinx可编程逻辑来进行现代化数字系统设计。

1.2 文章结构:本文将按照以下方式组织内容:第二部分将对FPGA进行概述,包括可编程逻辑器件简介以及Xilinx FPGA的介绍。

此外,我们还将探讨FPGA在数字系统设计中的各种应用。

第三部分将回顾一些基本原理,并提供如何搭建开发环境的指南。

其中包括对数字电路基础知识的回顾、VHDL语言简介和基础语法,以及Xilinx Vivado工具的安装与配置方法。

第四部分将详细介绍FPGA设计流程与实践技巧。

我们会讲解项目创建与工程管理方法,并探讨如何实现模块化设计和代码重用性提高的技巧。

另外,还会介绍仿真与验证技术在FPGA设计过程中的应用。

第五部分则涵盖了一些高级主题与应用案例分析。

我们将重点讨论并行计算与加速器设计、数据通信与嵌入式系统设计以及高精度数据处理系统设计等领域的案例分析,并提供相应的实践指导。

1.3 目的:本教程通过详细讲解FPGA现代数字系统设计的流程和技巧,旨在帮助读者全面了解FPGA在数字系统设计中的应用,并提供实用的指导和建议。

通过学习本教程,读者能够掌握从开发环境搭建到高级应用案例分析所需的知识和技能,为他们日后在数字系统设计领域取得成功打下坚实基础。

无论是初学者还是有经验的工程师,都能从本教程中获益,并将其应用于自己的项目中。

2. FPGA概述:2.1 可编程逻辑器件简介:可编程逻辑器件(FPGA)是一种基于可重新配置数字电路的集成电路芯片,它可以实现用户定义的数字逻辑功能。

与传统的定制集成电路(ASIC)相比,FPGA 具有灵活性强、开发周期短和可重构性等优势。

时序逻辑电路的基本设计步骤

时序逻辑电路的基本设计步骤时序逻辑电路是数字电路的重要组成部分,它根据时钟信号的变化控制不同的输出状态。

时序逻辑电路的设计需要遵循一定的步骤,下面将介绍时序逻辑电路的基本设计步骤。

一、确定电路功能首先需要明确电路的功能,即输入和输出之间的关系。

这一步需要明确输入信号的种类和电路对输入信号的处理方式,以及输出信号的种类和电路对输出信号的生成方式。

二、建立状态转移图状态转移图是描述电路状态变化的图形化表示,它包括状态和状态之间的转移关系。

在建立状态转移图时,需要明确每个状态的含义和状态之间的转移关系,以便后续的电路设计。

三、建立状态表状态表是状态转移图的一种表格形式,它列出了所有可能的输入和输出组合以及对应的状态转移关系。

在建立状态表时,需要根据输入信号和状态转移图确定每个状态的输入、输出和转移条件。

四、设计电路逻辑方程在确定了状态表后,需要根据状态表设计电路的逻辑方程。

逻辑方程是根据输入信号、状态和输出信号之间的关系描述电路行为的数学表达式。

可以使用布尔代数等数学工具来设计电路的逻辑方程。

五、选择适当的电路元件根据电路的逻辑方程和输入输出的特性,需要选择适当的电路元件来实现电路功能。

常用的电路元件包括门电路、触发器、计数器等。

六、进行电路实现在选择了适当的电路元件后,需要进行电路实现。

电路实现可以使用数字集成电路或可编程逻辑器件等。

需要根据电路的逻辑方程和输入输出特性来进行电路的布线和连接。

七、进行电路测试在完成电路实现后,需要进行电路测试。

电路测试可以通过模拟测试或实际测试来进行。

在测试过程中需要检查输入输出是否符合电路设计要求,并对可能存在的故障进行排除。

八、进行电路优化在进行电路测试后,需要对电路进行优化。

电路优化可以通过简化逻辑方程、减少电路元件数量等方式来实现。

优化后的电路可以提高电路的性能和可靠性。

以上是时序逻辑电路的基本设计步骤。

在进行时序逻辑电路的设计时,需要按照以上步骤进行,以确保电路的正确性和可靠性。

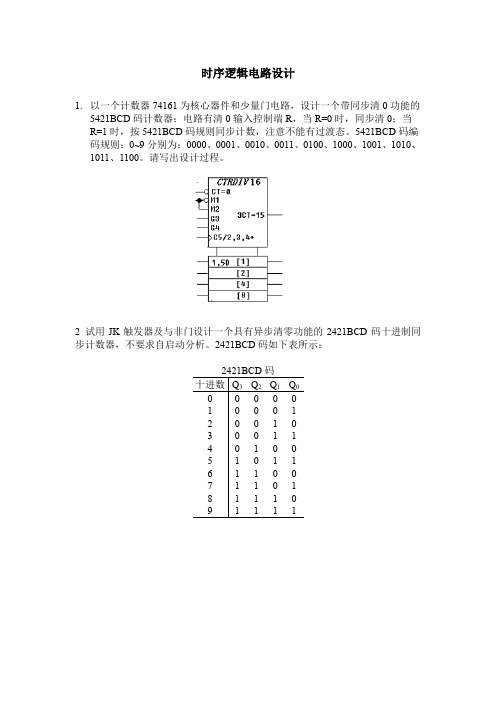

实验八计数器设计(可编程实验)

实验八计数器设计一、实验目的1、掌握计数器电路设计的方法。

2、能够通过CPLD开发实现时序逻辑电路的功能。

二、实验内容(1)设计一个同步带有进位输出端的十进制显示,模为24的计数器,且能够自启动。

要求如下:○1用原理图输入法,元件采用74160设计上述计数器,并硬件下实现,结果用数码管显示。

○2用文本输入法设计编程,并硬件下实现,结果用数码管显示。

(2)用综合方法设计一个计数器,要求:○1用原理图输入法,元件采用74160设计上述计数器,并硬件下实现,结果用数码管显示。

○2用文本输入法设计编程,并硬件下实现,结果用数码管显示三、实验逻辑功能分析及预习情况(2)模24计数器真值表四、实验过程模为24的计数器(一)采用原理图设计模为24的计数器(1)启动MAX+plusII软件;(2)创建一个新工程;(3)原理图编辑;编辑原理图,如下(4)保存、编译原理图;(5)启动波形图编译器;设计End time为1.0us,Grid Size为50.0ns。

结果如下:(6)时间分析图(7)利用真值表验证所设电路的逻辑功能;(8)经过验证保存仿真原理图。

(二)采用文本文档设计模为24的计数器(1)启动MAX+plusII软件;(2)创建一个新工程;○1启动文本编译器;○2编译VHDL语言程序为Library ieee;Use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;Entity mo24cx isPort(CLK:in std_logic;ohigh,olow:out std_logic_vector(6 downto 0);CO :out std_logic);End;Architecture rtl of mo24cx issignal h_temp,l_temp:std_logic_vector(3 downto 0):="0000";signal CO_temp : std_logic;beginprocess(CLK)beginCO_temp <= h_temp(1) and l_temp(1) and l_temp(0);if(CLK'event and CLK = '1')thenif(h_temp = "0010" and l_temp = "0011" )thenh_temp <= "0000";l_temp <= "0000";elsif(l_temp = "1001")thenh_temp <= h_temp+1;l_temp <= "0000";elsel_temp <= l_temp+1;end if;end if;end process;process(l_temp)begincase l_temp iswhen "0000" => olow <= "1111110";when "0001" => olow <= "0110000";when "0010" => olow <= "1101101";when "0011" => olow <= "1111001";when "0100" => olow <= "0110011";when "0101" => olow <= "1011011";when "0110" => olow <= "1011111";when "0111" => olow <= "1110000";when "1000" => olow <= "1111111";when "1001" => olow <= "1111011";when others => olow <= "ZZZZZZZ";end case;end process;process(h_temp)begincase h_temp iswhen "0000" => ohigh <= "1111110";when "0001" => ohigh <= "0110000";when "0010" => ohigh <= "1101101";when "0011" => ohigh <= "1111001";when "0100" => ohigh <= "0110011";when "0101" => ohigh <= "1011011";when "0110" => ohigh <= "1011111";when "0111" => ohigh <= "1110000";when "1000" => ohigh <= "1111111";when "1001" => ohigh <= "1111011";when others => ohigh <= "ZZZZZZZ";end case;end process;CO <= CO_temp;end;○3启动波形图编译器;○4时间分析图○5利用真值表验证所设电路的逻辑功能;○6经过验证保存仿真原理图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于可编程计数器的时序逻辑电路设计作者:任骏原来源:《现代电子技术》2010年第11期摘要:介绍了基于MSI可编程计数器74LS161的时序逻辑电路设计技术,目的是探索MSI可编程计数器实现一般时序逻辑电路的扩展应用方法,即以计数器端的代码组合表示时序逻辑电路的各个状态,由输入变量控制计数器的EP,ET及LD端,综合利用计数、置数、保持功能,使计数器的状态变化满足所要求的时序,用计数功能实现“次态=现态+1”的二进制时序关系,用置数功能实现“次态=预置数”的非二进制时序关系,用保持功能实现“次态=现态”的自循环时序关系。

所述方法的创新点是提出了MSI可编程计数器改变应用方向的逻辑修改方法。

关键词:可编程计数器; 二进制时序; 非二进制时序; 逻辑设计中图分类号:TN79 文献标识码:A文章编号:1004-373X(2010)11-0167-04Design of Sequential Logic Circuits Based on Programmable CounterREN Jun-yuan(Department of Physics, Bohai University, Jinzhou 121000, China)Abstract: The design technique of the sequential logic circuits based on MSI programmable counter 74LS161 is presented. The purpose is to investegate a common method to realize theto denote the states of the sequential logic circuit, the input variables are adopted to control the EP, ET andports of LD, and the data-setting, counting and keeping functions are used to allow the change of the counter state to meet the requirement of the sequence, which means that the counting function is used to realize the binary sequential relation(″next state=present state+1″), the data-setting function is used to achieve the non-binary sequential relation(″next state=setting data″), and the keeping function is used to carry out the self-looping sequential relation(″next state=present state″). This is a new method for MSI programmable counter to change its application direction.Keywords: programmable counter; binary sequence; non-binary sequence; logic design0 引言各种MSI中规模数字集成电路都有自己的主要特性和应用目标,如果进行非常规使用,则改变它的使用方向,就可进一步发挥其功能和作用。

扩展专用集成电路的应用领域是一项有实际意义的研究。

本文研究了MSI可编程计数器改变应用方向的逻辑修改方法及时序逻辑电路的设计技术。

1 基本原理74LS161是可编程中规模同步4位二进制加法计数器,图1为其图形符号[1-10]。

其中为计数状态输出端;C为进位输出端;EP,ET为计数控制端;LD为预置数控制端为预置数输入端;RD为异步置零控制端;CP为计数脉冲输入端。

图1 74LS161可编程计数器图形符号表1为可编程计数器74LS161的功能表[1-10] 。

表1 74LS161可编程计数器的功能表输入RD输出逻辑功能0××××××××0000置零预置数1111↑××××二进制加法计数计数110××××××保持保持11×0×××××保持(C=0)保持由表1可知,在RD=1条件下,74LS161可编程计数器由EP,ET及LD控制具有计数、预置数和保持三种功能。

用74LS161可编程计数器端的代码组合表示时序逻辑电路的各个状态,由输入变量控制EP,ET及LD端,综合利用计数、置数、保持功能,使计数器的状态变化满足所要求的时序,即用计数功能实现“次态=现态+1”的二进制时序关系,用预置数功能实现“次态=预置数”的非二进制时序关系,用保持功能实现“次态=现态”的自循环时序关系,可实现一般时序逻辑电路[1]。

1.1 可编程计数器状态转换对控制函数的要求由表1所示的功能表,可确定74LS161可编程计数器各种状态转换时对控制函数的要求,如表2所示。

表2 74LS161可编程计数器不同状态转换对控制函数的设置要求现态次态控制函数设置说明无输入变量作用按二进制时序进行状态转换。

EP=ET=×LD=0无输入变量作用,按非二进制时序转换到预置状态。

龙源期刊网 EP=ET=MLD=1输入变量M=1有效时按二进制时序进行状态转换;M=0无效时状态不变。

EP=ET=0LD=M输入变量M=1有效时按非二进制时序转换到预置状态M=0无效时状态不变。

L输入变量有效时按二进制时序进行状态转换有效时按非二进制时序转换到预置状态均无效时状态不变。

1.2 基于可编程计数器时序逻辑电路的基本形式用1个74LS161可编程计数器和2个16选1数据选择器可构成多输入时序逻辑电路的基本形式[1],如图2所示。

图2 74LS161可编程计数器和16选1数据选择器构成多输入时序电路的基本形式图2中,74LS161计数器的现态输出作为数据选择器的选择控制变量,数据选择器的Y输出作为74LS161可编程计数器的EP,ET计数控制信号及LD预置数控制信号,数据选择器的输入端作为所构成时序网络的外部信号输入端。

74LS161可编程计数器处于不同现态时通过数据选择器选择不同的外部输入信号作用于EP,ET及LD端,对74LS161可编程计数器的基本工作时序进行修改,在时钟脉冲CP的作用下,使计数器的输出状态按所要求的时序关系进行改变,即可实现状态个数不超过16个的一般时序逻辑电路。

74LS161可编程计数器的EP,ET及LD控制函数可写成如下矩阵形式:(1)(2)如果所实现的时序逻辑电路其状态个数不超过8个,可使用74LS161可编程计数器的低3位和2个8选1数据选择器进行组合。

如果所实现的时序逻辑电路其状态个数不超过4个,可使用74LS161可编程计数器的低2位和2个4选1数据选择器进行组合。

由状态转换关系,依表2确定式(1),式(2)中输入矩阵的参数。

1.3 时序逻辑电路的输出函数所设计的时序逻辑电路为Mealy型时,输出是现态及输入变量的函数,可写成式(3)所示的矩阵形式并用数据选择器实现,由各状态的输出要求确定式(3)中输入矩阵的参数。

(3)所设计的时序逻辑电路为Moore型时,输出仅是现态的函数:(4)用卡诺图化简求出最简输出逻辑表达式,用逻辑门实现。

当每态对应一个不同的输出函数时,可用二进制译码器实现输出函数。

1.4 基于可编程计数器时序逻辑电路的设计一般设计步骤:(1) 作出状态图使用MSI可编程计数器及数据选择器设计时序逻辑电路时,状态的简化通常不会简化电路结构,一般不进行状态简化,直接使用原始状态图进行设计,可使各个状态所表示的含义清楚,电路与所实现的逻辑功能之间的对应关系较为明确。

(2) 状态分配进行状态分配时,尽量使用不需进行预置数的二进制时序,尽量对非二进制时序作相邻分配,以利于预置数的简化。

(3) 求出EP,ET及LD的矩阵式,用卡诺图化简求出预置数最简逻辑表达式,求出输出函数逻辑表达式。

(4) 画出逻辑图。

2 设计举例一个同步时序逻辑电路,输入信号为。

当连续输入4个或4个以上的1时,然后输入1个1时,输出Z为不同时输入1。

由设计要求作出原始状态图如图3所示。

其中状态表示起始状态表示输入了1个状态表示输入了2个状态表示输入了3个状态表示输入了4个或4个以上的1。

图3 设计举例的原始状态图图3中有S0 ~ S4 共5个状态,使用74LS161可编程计数器的低3位代码进行状态分配,按尽量使用二进制时序的分配原则,状态分配关系为:S0: 000;S1: 001;S2: 010;S3: 011;S4: 100。

状态分配后的状态图如图4所示。

由图4及表2,写出74LS161计数器的EP,ET及LD矩阵方程式:0](5)(6)其中,不使用的101,110和111状态,将EP,ET及LD均设置为1,使计数器处于二进制时序状态工作,能自启动。

图4 状态分配后的状态图作出74LS161计数器预置输入变量的卡诺图及画包围圈化简如图5所示,各预置输入变量的最简逻辑表达式为:(7)图5 预置输入变量的卡诺图及化简由图4所示的状态图,写出输出函数Z的矩阵方程式:(8)其中,不使用的101,110和111状态的输出设置为0,亦可设置为1。

用1个74LS161可编程计数器,3个8选数据选择器74LS151按式(5)~(8)画出逻辑图如图6所示。

图6 设计举例的逻辑图3 结语基于可编程计数器的时序逻辑电路设计技术,提出了设计一般时序逻辑电路的状态分配原则及设计步骤,具有实际应用意义。

需要指出,当用单片74LS161可编程计数器控制EP,ET及LD构成模数N无输入变量,所用状态仅最后一个是非二进制时序,其余均为二进制时序。

由功能表可知,需将EP,ET设置为常数1且不需选择,可将图2所示的一般结构中控制EP,ET的数据选择器简化掉,而LD 控制函数仅在最后状态为0,可用门简单控制。

参考文献[1]任骏原,张凤云.电子线路专题研究[M].成都:西南交通大学出版社,1995.[2]任骏原.电子线路与数字逻辑解题方法指导[M].沈阳:东北大学出版社,1996.[3]华成英,童诗白.模拟电子技术基础[M].4版.北京:高等教育出版社,2006.[4]杨素行.模拟电子技术基础简明教程[M].3版.北京:高等教育出版社,2006.[5]胡晏如.模拟电子技术[M].2版.北京:高等教育出版社,2004.[6]王佩珠.电路与模拟电子技术[M].南京:南京大学出版社,2001.[7]付植桐.电子技术[M].北京:高等教育出版社,2000.[8]康华光,陈大钦.电子技术基础(模拟部分)[M].4版.北京:高等教育出版社,1999.[9]杨素行.模拟电子电路[M].北京:中央广播电视大学出版社,1994.[10]余雄南.数字电路与系统[M].西安:西安电子科技大学出版社,1988.。