创新中心FPGA开发板技术要求

fpga技术要求

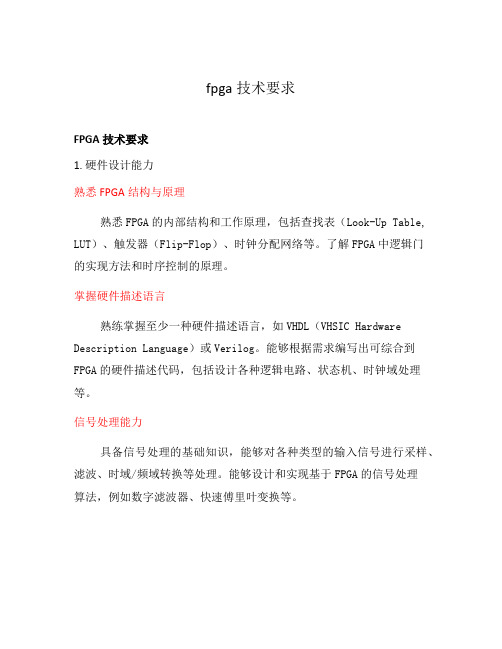

fpga技术要求FPGA技术要求1. 硬件设计能力熟悉FPGA结构与原理熟悉FPGA的内部结构和工作原理,包括查找表(Look-Up Table, LUT)、触发器(Flip-Flop)、时钟分配网络等。

了解FPGA中逻辑门的实现方法和时序控制的原理。

掌握硬件描述语言熟练掌握至少一种硬件描述语言,如VHDL(VHSIC Hardware Description Language)或Verilog。

能够根据需求编写出可综合到FPGA的硬件描述代码,包括设计各种逻辑电路、状态机、时钟域处理等。

信号处理能力具备信号处理的基础知识,能够对各种类型的输入信号进行采样、滤波、时域/频域转换等处理。

能够设计和实现基于FPGA的信号处理算法,例如数字滤波器、快速傅里叶变换等。

2. 软件工具熟悉FPGA开发平台具备对FPGA开发平台的熟悉程度,如Xilinx的Vivado或Altera的Quartus。

能够使用开发平台进行FPGA的开发、综合、仿真和下载。

能力应用软件工具进行仿真与调试具备使用软件工具进行FPGA设计的仿真和调试能力,例如ModelSim等仿真工具,能够准确验证设计的正确性,并对可能存在的问题进行调试和优化。

熟悉高级综合工具熟悉高级综合工具,如Xilinx的Vivado HLS或Altera的HLS工具。

能够通过高级综合工具,将C/C++等高级语言代码转换为FPGA硬件描述代码,提高设计效率和可移植性。

3. 项目经验具备项目管理经验具备项目管理经验,能够在有限的时间和资源下,组织和管理FPGA项目的开发和验证工作。

能够根据项目要求,合理规划开发进度和资源分配,保证项目高质量地完成。

有FPGA设计实践经验具备一定的FPGA设计实践经验,能够独立完成FPGA设计任务。

能够根据需求,完成FPGA硬件设计、仿真验证、性能优化等工作。

参与过复杂FPGA项目参与过复杂FPGA项目的开发,有从0到1完成复杂功能模块的经历。

FPGA开发板使用说明书(二版)

目 录第一章综述 (1)核心板介绍EP1C12核心板资源介绍 (1)EP2C35核心板资源介绍 (2)FPGA开发板介绍FPGA开发板资源介绍 (4)第二章 系统模块功能介绍 (7)EP1C12核心板模块说明EP1C12F324C8芯片说明 (9)NOR FLASH模块说明 (10)SRAM模块说明 (11)FPGA接口I/O说明 (12)EP2C35核心板模块说明EP2C35F484C8芯片说明 (19)NOR FLASH模块说明 (20)SRAM模块说明 (21)S D R A M模块说明 (22)NAND FLASH模块说明 (23)FPGA接口I/O说明 (24)核心板使用注意事项 (29)FPGA开发平台模块说明液晶显示模块 (31)RTC实时时钟模块 (33)USB接口模块 (33)音频CODEC接口模块 (34)EEPROM存储模块 (35)数字温度传感器模块 (36)其它功能模块 (37)FPGA开发平台使用注意事项 (38)第三章 软件的安装 (39)QUARTUSII的安装 (39)QUARTUSII的授权 (46)NIOSII IDE的安装 (51)附表一核心板载资源与FPGAEP1C12I/O接口对照表 (55)附表二核心板载资源与FPGAEP2C35I/O接口对照表 (60)附表三EP1C12/ EP2C35与开发板硬件资源I/O接口对照表 (66)第一章综述FPGA开发平台是根据现代电子发展的方向,集EDA和SOPC系统开发为一体的综合性实验开发系统,除了满足高校专、本科生和研究生的SOPC教学实验开发之外,也是电子设计和电子项目开发的理想工具。

整个开发系统由核心板、SOPC开发平台和扩展板构成,根据用户不同的需求配置成不同的开发系统。

系统根据用户不同的设计需求来更换其它不同系列的核心板,如: EP1C12、EP2C20、EP3C25等。

所以,不管从性能上而言,还是从系统灵活性上而言,无论您是初学者,还是资深硬件工程师,它都会成为您的好帮手。

FPGA课程设计——要求_题目_安排

FPGA课程设计——要求_题目_安排FPGA课程设计要求1、FPAG课设所选题目要求采用自顶向下的全正向设计方法,并选用Verilog_HDL语言为设计输入工具。

2、要求电路的功能仿真和FPGA后仿真验证全部正确通过,且功能仿真和后仿真建议采用第三方验证工具(Modelsim),综合与布局布线工具为:Quartus II。

3、课程设计的具体评定标准:(1)完成功能和引脚定义,提交《技术规范》;(10分)(2)完成总体方案及详细方案设计,提交《设计方案》;(10分)(3)完成验证方案设计,提交《功能验证方案》;(10分)(4)完成电路设计和功能仿真,提交电路设计源代码,功能仿真激励源代码及功能仿真结果报告;(15分)(5)完成设计电路的FPGA综合及布局布线,提交综合及布局布线报告和引脚分布报告;(10分)(6)采用第三方工具完成后仿真,提交后仿真结果报告;(10分)(7)基于FPGA开发板完成设计电路的功能测试验证,提交硬件测试结果报告;(30分)(8)积极与教师和同学进行技术交流沟通,撰写课设的心得体会;(5分)4、题目要求独立完成,设计和报告如有雷同,将一个成绩平均分配雷同的同学。

说明1:课程设计时间段内任意时间点名未到(吃饭时间12:00 ~ 12:40除外)、迟到扣3分/次,玩游戏扣20分/次。

说明2:迟到、点名未到6次及6次以上者课程设计成绩直接记:不及格。

FPGA课程设计题目序号题目说明1简易数据流检测器设计及FPGA功能验证设计一个有限状态机检测5位二进制序列“10010”,要求数据采用串行输入,检测结果用一个高脉冲来指示。

用FPGA开发板上的按键作为数据流输入,led或数码管作为输出指示。

2可逆加减计数器及FPGA功能验证可预置16位可逆加减计数器。

要求计数器有16位计数输出同时有进位和借位输出,预置输入采用同步方式。

用FPGA开发板上的按键作为加减计数控制输入,数码管(或led)作为计数值输出。

fpga使用注意!!

------------------------------------------------------------------------------------ 本板子由哈尔滨工程大学青年创业电子设计小组(简称青创电子设计小组)开发,对板子及其相关的实例、教程具有完全的自主设计权。

请勿将例程、电路图、教程用作其它商用,否则将追究其法律责任!!!。

若要在网络上以学习的目的发布相关内容,请注明出处!

-----------------------------------------------------------------------------------

注意:为了方便查找,我们在每个文件夹的名字中都带了中文注释,但在运行这些文件夹中的工程时,最好把文件夹名字里的这些中文注释去掉,防止产生不必要的错误,耽误大家的学习。

关于如何利用好这些实例,以帮助你更快速的学好VHDL的一点建议:

(1)将配套实例先在开发板上运行一遍,观察实验结果;(2)仔细分析实验代码,经自己最大的努力看懂它们:

(3)自己将实验代码重新写一遍(一个字一个字的敲入计算机,请一定不要复制我们提供的现成代码),然后在Quartus下进行调试;

(4)看看是否可以用另外的方法实现实验所要达到的效果,假如可以,可自己编写代码进行调试。

经过以上四步的练习,相信初学者可以很好的掌握

VHDL的编程,熟练的操作Quartus软件,对CPLD 开发流程也有了比较深刻的体会。

我们提供了视频教程,喜欢视频教学的读者可结合视频学习。

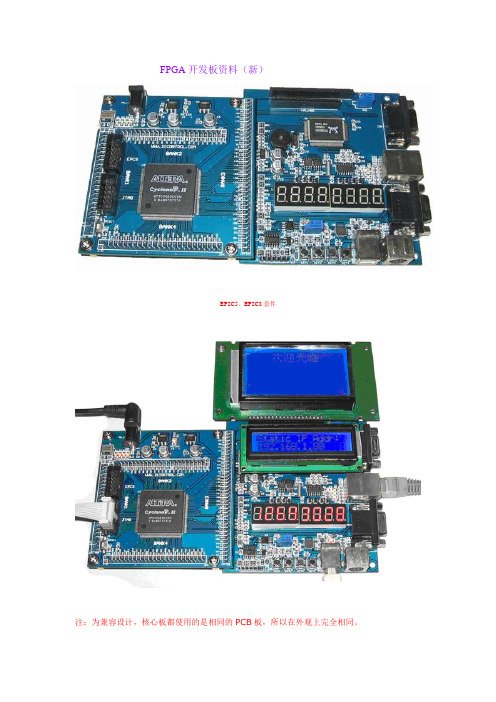

FPGA开发板资料

FPGA开发板资料(新)EP2C5、EP2C8套件注:为兼容设计,核心板都使用的是相同的PCB板,所以在外观上完全相同。

我们秉承一贯以来实用的理念,处处用心为用户着想,重新精心打造,每个功能都精心设计实用的例子程序,并重新编写详细的教程,无论用于学习或是研制产品原型,都非常具有实际意义。

另外我们设计了包含Cyclone、CycloneII 等多款核心板供用户选择,不断开发和供应各种实用的功能扩展板,扩展性能卓越。

无论学习、开发,该套件都是您合适的首选。

质量保证:(1)我们竭诚为顾客提供超值的产品。

任何产品邮发之前都经过严格的检验和测试,保证每个功能都工作良好。

如果有质量问题,7天内免费更换,一年保修,对于人为造成的损坏(如使用不当烧毁芯片等),我们仍给以免费维修,但需以成本价收取芯片费用。

(2)于外地客户,我们采用信誉良好的航空快递公司进行配送,保证产品快速完好地送到客户手上,如果在配送过程中有损坏,我们负责给予更换。

(3)我们严格控制产品出厂的质量,做到每块板卡邮出之前经过再三测试,如遇特殊情况,请及时联系我们,我们会给予精诚的解决方案。

我们视质量和服务是我们获得顾客长期信赖和合作的根本,更是我们赖之成长的源泉。

技术支持:采用电话、BBS、QQ、QQ客户群等方式。

套件包括:一、FPGA核心板:多种核心板供选择,所采用的FPGA分别有:(1)Cyclone核心:EP1C12Q240C8、EP1C6Q240C8;(2)CycloneII核心:EP2C8Q208C8、EP2C5Q208C8、EP2C20Q208C8;CycloneIII核心:EP3C16Q240C8、EP3C25Q240C8;(3)SDRAM:8MByte;(4)Flash:8MByte;(5)EPCS1、EPCS4、EPCS16配置芯片:EP1C6和EP2C5核心板配备EPCS1;EP1C12和EP2C8以及EP2C20核心板配备EPCS4;EP3C16和EP3C25配备EPCS16(即容量为16Mb);(6)提供配置模式:JTAG和AS;(7)两个或一个50Mhz有源时钟;(8)所有IO、Avalon总线、配置管脚等都通过4排插针引出,用户可以充分自由发挥,扩展更灵活;(9)4个LED;(10)一个复位按键。

FPGA 开发板用户手册

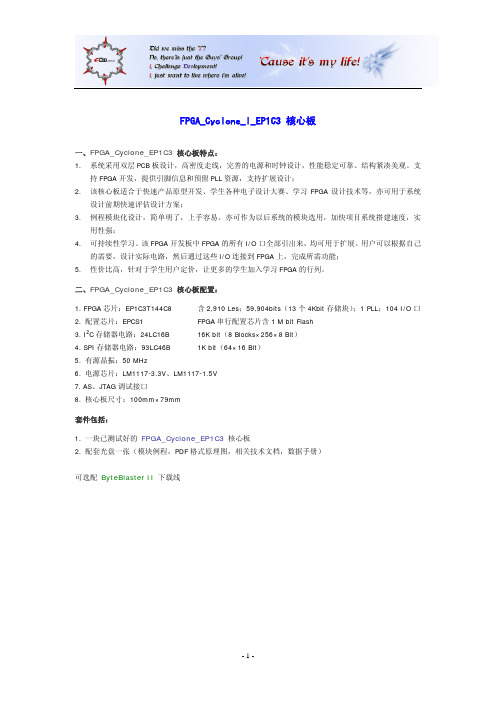

FPGA_Cyclone_I_EP1C3 核心板一、FPGA_Cyclone_EP1C3 核心板特点:1.系统采用双层PCB板设计,高密度走线,完善的电源和时钟设计,性能稳定可靠、结构紧凑美观。

支持FPGA开发,提供引脚信息和预留PLL资源,支持扩展设计;2.该核心板适合于快速产品原型开发、学生各种电子设计大赛、学习FPGA设计技术等,亦可用于系统设计前期快速评估设计方案;3.例程模块化设计,简单明了,上手容易。

亦可作为以后系统的模块选用,加快项目系统搭建速度,实用性强;4.可持续性学习。

该FPGA开发板中FPGA的所有I/O口全部引出来,均可用于扩展。

用户可以根据自己的需要,设计实际电路,然后通过这些I/O连接到FPGA上,完成所需功能;5.性价比高,针对于学生用户定价,让更多的学生加入学习FPGA的行列。

二、FPGA_Cyclone_EP1C3 核心板配置:1. FPGA芯片:EP1C3T144C8 含2,910 Les;59,904bits(13个4Kbit存储块);1 PLL;104 I/O口2. 配置芯片:EPCS1 FPGA串行配置芯片含1 M bit Flash3. I2C存储器电路:24LC16B 16K bit(8 Blocks×256×8 Bit)4. SPI存储器电路:93LC46B 1K bit(64×16 Bit)5. 有源晶振:50 MHz6. 电源芯片:LM1117-3.3V、LM1117-1.5V7. AS、JTAG调试接口8. 核心板尺寸:100mm×79mm套件包括:1. 一块已测试好的FPGA_Cyclone_EP1C3 核心板2. 配套光盘一张(模块例程,PDF格式原理图,相关技术文档,数据手册)可选配 ByteBlaster II 下载线Periphery_For_FPGA外设板Periphery_For_FPGA外设板特点:1. 该外设板是基于FPGA的硬件描述语言和软内核嵌入式系统的SOPC开发平台。

fpga技术要求

fpga技术要求

(原创版)

目录

1.FPGA 技术的定义和基本原理

2.FPGA 技术的主要要求

3.FPGA 技术的应用领域

正文

FPGA(现场可编程门阵列)技术是一种集成电路设计技术,它的基本原理是通过将多个逻辑门和其他电子元件组合在一起,形成一个可重新配置硬件架构的数字电路。

FPGA 技术具有灵活性高、开发速度快、可重构性强等优点,因此在现代电子技术中有着广泛的应用。

FPGA 技术的主要要求包括以下几个方面:

首先,FPGA 技术要求具有较高的灵活性。

FPGA 器件可以根据需要实时地改变其硬件结构,从而实现不同的逻辑功能。

这种灵活性使得 FPGA 技术非常适用于需要频繁更改设计方案的电子系统,如人工智能、图像处理等领域。

其次,FPGA 技术要求具有较快的开发速度。

FPGA 设计可以通过编程实现,而不需要进行复杂的硬件设计。

这使得 FPGA 技术的开发速度相比传统的硬件设计方法要快得多,可以大大缩短产品的研发周期。

最后,FPGA 技术要求具有较强的可重构性。

FPGA 器件可以根据需要实时地改变其硬件结构,从而实现不同的逻辑功能。

这种可重构性使得FPGA 技术非常适用于需要频繁更改设计方案的电子系统。

FPGA 技术的应用领域非常广泛,包括但不限于人工智能、图像处理、通信、汽车电子等领域。

例如,FPGA 技术可以用于实现深度学习算法,实现高效的图像识别和处理;FPGA 技术也可以用于设计高速的通信芯片,

实现高速、稳定的数据传输。

FPGA实验核心开发板简介

一、主要器件及特性

1、FPGA:EP1C12Q240C8,配置芯片EP1C12

2、一片256K X 16Bit的异步SRAM 3、一片4M X 32Bit d SDRAM支持166M byte 4、一片2M X 8Bit或者1M X 16Bit的Flash读写速度为 90ns 5、9针RS-232串口 6、PS/2鼠标,键盘接口 7、USB2.0高速数据接口:采用Cypress公司CY7C68013 芯片实现了USB接口的扩展 8、LCD1602带背光字符型液晶模块

开发板说明

一、开发板电源

1、USB供电:J8跳到USB_VCC 2、外部电源供电: 外部1A/5V直流开关电源,J8 跳到EX_VCC

3、EDA底板供电:将开关电源插到EDA底板上, J8跳到EX_VCC

二、LCD接口

J11插入LCD1602

三、配置端口

板上两个配置端口:AS和JTAG

四、与EDA底板进行连接时的注意事项

七、主板上外设LED

Байду номын сангаас

八、主板上系统时钟

九、主板上4 x 4矩阵键盘和按键

十、主板上蜂鸣器

十一、主板上温度测试

主要电路及管脚

二、LED和按键

1、4个发光二极管

2、4个按键

3、两位动态扫描数码管

一、主板PS2

二、主板RS232

三、主板VGA接口

四、主板步进电机接口(J11短接5V)

五、主板液晶接口(J27) 标准字符液晶LCD1602,汉字图像液晶LCD12864

六、主板上外设数码管

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

创新中心FPGA开发板技术要求

通信与信息工程学院创新中心因大学生创新训练及实践教学需要,拟采购FPGA口袋实验平台32套、电子系统设计FPGA开发板7套、基于ZYNQ的开源量测FPGA开发板4套,要求该批设备为同一生产厂家产品,具体技术要求如下:

一、FPGA口袋实验平台32套

1.主芯片:Xilinx Artix FPGA,逻辑单元不低于33,280、Slices不低于5,200、分布式RAM不低于

400Kb、DSP单元不低于90个、BlockRAM不低于1,800Kb;

2.板上时钟不低于100MHz;

3.板卡配置方式:支持USB-JTAG编程接口和SPI闪存配置方式;

4.板上需要有不少于2Mbit的SRAM;

5.需要有SPI闪存;

6.需要提供不少于16个LED、不少于8个的拨码开关、不少于8个DIP开关、不少于5个按键;

7.提供通用扩展IO不少于32pin;

8.板上7段数码管不少于8个;

9.板上需要提供VGA视频输出接口与Audio音频接口;

10.提供用于系统调试的USB-UART接口;

11.板卡需要具有板载蓝牙模块;

12.板卡需要具有板载DAC模块;

13.板卡需要具有可调节的电位器,为XADC提供模拟输入;

14.板卡需要具有XADC;

15.要求提供Xilinx Vivado完全正式版开发工具以及license;

16.提供Xilinx Vivado相关培训资料;

17.提供Xilinx Vivado开发流程培训;

18.提供板卡开发流程上手视频;

19.提供不少于12个参考实验案例,包括蓝牙远程控制实验,嵌入式Microblaze实验。

二、电子系统设计FPGA开发板7套

1.主芯片:Xilinx Artix FPGA,逻辑单元不低于33,280、Slices不低于5,200、分布式RAM不低于

400Kb、DSP单元不低于90个、BlockRAM不低于1,800Kb;

2.板上时钟不低于100MHz;

3.板卡配置方式:支持JTAG编程接口和SPI闪存配置方式;

4.板上需要有不少于8Mbit的SRAM;

5.需要具有板载SMA接口、80MSPS采样率、10bit分辨率ADC;

6.需要具有板载SMA接口、165MSPS采样率、10bit分辨率DAC;

7.需要具有独立时钟/FPGA输出/外部SMA输入可选的ADC时钟;

8.需要具有板FPGA提供DAC时钟;

9.需要提供不少于4个LED、不少于4个的拨码开关、不少于2个按键;

10.需要提供不少于20个GPIO;

11.需要具有底板连接器支持5V单电源供电;

12.需要支持USB供电;

13.需要具有128-64液晶;

14.需要具有4×4小键盘;

15.需要具有RS-232接口;

16.需要具有VGA接口;

17.需要具有PWM信号接口;

18.需要具有高速PMOD接口;

19.需要具有可插拔的TM4C1294XL Launchpad。

三、基于ZYNQ的开源量测FPGA开发板4套

1.要求主控芯片使用ZYNQ-7000系列芯片,集成两颗ARM Cortex-A9硬核,提供

2.8万FPGA逻辑

单元、2Mb片上block RAM以及80个DSP计算单元;

2.板上需要提供4个12-bit、100k/s采样的模拟输入;

3.板上需要提供4个12-bit、100k/s采样的模拟输出;

4.需要具有板载125MSPS采样率、14bit分辨率、双通道ADC,带宽50MHz;

5.需要具有板载125MSPS采样率、14bit分辨率、双通道DAC,带宽50MHz;

6.板上需要提供4Gb DDR3内存以及MicroSD卡;

7.板上需要提供千兆以太网连接器、USB2.0接口、USB-UART接口;

8.板上需要提供至少16个扩展IO;

9.需要具有提供扩展子板用于连接外部功能模块,并支持IIC、SPI等总线接口;

10.需要支持网络远程访问,并且支持Python、Matlab、Labview、Scilab远程控制。