基于DE2-115开发板的FPGA入门设计实验

FPGA入门实验教程 适合初学者

艾米电子工作室—让开发变得更简单FPGA 入门系列实验教程——点亮LED1. 实验任务点亮发光二极管。

通过这个实验,熟悉并掌握CPLD/FPGA 开发软件QuartusII 的使用方法和开发流程以及Verilog HDL的编程方法。

2. 实验环境硬件实验环境为艾米电子工作室型号EP2C5T144 开发套件。

软件实验环境为Quartus II 8.1 开发软件。

3. 实验原理FPGA 器件同单片机一样,为用户提供了许多灵活的独立的输入/输出I/O 口(单元)。

FPGA 每个I/O 口可以配置为输入、输出、双向、集电极开路和三态门等各种组态。

作为输出口时,FPGA 的I/O 口可以吸收最大为24mA 的电流,可以直接驱动发光二极管LED 等器件。

图1. 1 为8 个发光二极管硬件原理图,本原理图对应艾米电子工作室型号为EP2C5T144 FPGA 开发板及接口板。

通过原理图可知如果要点亮这八个LED,所以只要正确分配并锁定引脚后,在相应的引脚上输出相应高电平“1”,就可实现点亮该发光二极管的功能。

本工作室开发板均采用输出“1”点亮LED 的模式,以后就不再另作说明。

图1. 1 发光二极管LED 硬件原理图艾米电子工作室—让开发变得更简单FPGA 入门系列实验教程——LED 闪烁灯1. 实验任务让实验板上的8 个LED 周期性的闪烁。

通过这个实验,熟悉并掌握采用计数与判断的方式来实现分频的Verilog HDL 的编程方法以及Quartus II 软件的使用方法和开发流程。

2. 实验环境硬件实验环境为艾米电子工作室型号EP2C8Q208 增强版开发套件。

软件实验环境为Quartus II 8.1 开发软件。

3. 实验原理艾米电子工作室开发套件板载50MHz 的时钟源,假如我们直接把它输入到发光二极管LED,由于人眼的延迟性,我们将无法看到LED 闪烁,认为它一直亮着。

如果我们期望看到闪烁灯,就需要将时钟源的频率降低后再输出。

DE2-115以太网通信之一88E1111网卡接收PC数据

DE2-115以太⽹通信之⼀88E1111⽹卡接收PC数据想利⽤⼿头上的DE2-115 写⼀个关于以太⽹通信的驱动,经过了这么多天的实验调试终于有了⼀些认识。

1、我在观察⽹卡发送数据与接收数据的过程中发现,我从fpga上的⼀个⽹卡发送数据,然后另⼀个⽹卡接收数据,接收到的数据前⾯会有55h这8bit的数据。

我从PC上发送数据,⽤fpga上的⽹卡接收数据,那么在接收到的数据前⾯会有55h,55h,55h,55h,55h,55h,55h,5dh这64bit的数据。

那么如果55h这8bit数据是PHY发送时⾃动添加那么从PC上接收到的最后应该是55⽽不应该是5d。

那么只能是⽹卡在接收的时候⾃动添加的55h这8bit位。

那剩下的56bit应该是⾃⼰添加在数据中发送的。

2、我⽤signaltap ii设置的采样频率是50Mh,⽽数据的带宽是100Mhz。

当我⽤⼩兵以太⽹测试仪设置的发送频率为1000000/次时,发现siganltap ii 中rx_data的数据很久才会变化,其余时刻都是零,但是⽤led通过对接收数据进⾏观察时就符合发送的频率,那么signal tap ii 很长时间观察不到数据的情景应该和时钟的设置有关。

3、有⼀段时间我从PC上发送数据,然后fpga上接收的数据,⼀段数据的个别位发⽣错误。

等我把板⼦上两个phy的配置都设置正确时。

就能正确的接收数据了。

4、signaltap 接收到的PC数据⾼四位与第四位颠倒,⽐如说如果发送的数据是56h 75h 83h 那么接收到的数据就是65h 57h 38h。

说明数据在发送的过程中⾼先发送低四位后发送⾼四位。

5、88E1111 采⽤100M ,全双⼯能从Pc接收数据的寄存器设置。

a、PHY的物理地址为10000,板⼦连接JP1的23.b、读寄存器以及写寄存器。

读寄存器主要是为了观察PHY配置是否正确。

在调试的过程中正确的读寄存器⾮常重要。

代码如下1if(flag) begin2case(mdc_num)30:begin RST_N<=0;mdio_reg<=mdio_reg+1;if(mdio_reg&32'hffffffff==32'hffffffff) begin RST_N<=1; mdc_num<=1;end else mdc_num<=0;end41:begin mdio_reg<=96'hffff_ffff__585a__0000_ffff_ffff;mdc_num<=2;end //选择page0 copper52:begin mdc_count<=mdc_count+1;6if(mdc_count<96)begin mdio<=mdio_reg[95]; wr_rd<=1;mdio_reg<=mdio_reg<<1;mdc_num<=2;end7else begin mdc_num<=5;mdc_count<=0;end end115:begin mdio_reg<=96'hffff_ffff__5812_0101_ffff_ffff;mdc_num<=6;end //4 100full duplex,802.3126:begin mdc_count<=mdc_count+1; if(mdc_count<96)begin mdio<=mdio_reg[95]; wr_rd<=1;mdio_reg<=mdio_reg<<1;mdc_num<=6;end14else begin mdc_num<=9;mdc_count<=0;end end9:begin mdio_reg<=96'hffff_ffff__5826__0400_ffff_ffff;mdc_num<=10;end //9⾃动主从,multi port device1910:begin mdc_count<=mdc_count+1; if(mdc_count<96)begin mdio<=mdio_reg[95]; wr_rd<=1;mdio_reg<=mdio_reg<<1;mdc_num<=10;end else begin mdc_num<=13;mdc_count<=0;end end 2213:begin mdio_reg<=96'hffff_ffff__5842__0068_ffff_ffff;mdc_num<=14;end //16 power up2514:begin mdc_count<=mdc_count+1; if(mdc_count<96)begin mdio<=mdio_reg[95]; wr_rd<=1;mdio_reg<=mdio_reg<<1;mdc_num<=14;end else begin mdc_num<=17;mdc_count<=0;end 2 17:begin mdio_reg<=96'hffff_ffff__5852_9051_ffff_ffff;mdc_num<=18;end //90513118:begin mdc_count<=mdc_count+1;if(mdc_count<96)begin mdio<=mdio_reg[95]; wr_rd<=1;mdio_reg<=mdio_reg<<1;mdc_num<=18;end else begin mdc_num<=19;mdc_count<= 3419:begin mdio_reg<=96'hffff_ffff__5802_a100_ffff_ffff;mdc_num<=20;end3520:begin mdc_count<=mdc_count+1; if(mdc_count<96)begin mdio<=mdio_reg[95]; wr_rd<=1;mdio_reg<=mdio_reg<<1;mdc_num<=20;end else begin mdc_num<=21;mdc_count<= 3821:begin mdc_count<=mdc_count+1;if(mdc_count<32)begin mdio<=1'b1; wr_rd<=1;mdc_num<=21;end46else begin flag<=0;wr_rd<=0;end end47endcase end48else49begin5051case(timenum)520:begin mdio_reg<=96'b11111111111111111111111111111111_01101000010001z1_zzzzzzzzzzzzzzzz_11111111111111111111111111111111;timenum<=1;wr_rd<=1;mdc_count<=0;end531:begin mdc_count<=mdc_count+1; if(mdc_count<48)begin mdio<=mdio_reg[95]; mdio_reg<=mdio_reg<<1;timenum<=1;end else begin wr_rd<=0;timenum<=2;end end542:begin data1[15]<=mdio_in;timenum<=3;end553:begin data1[14]<=mdio_in;timenum<=4;end564:begin data1[13]<=mdio_in;timenum<=5;end575:begin data1[12]<=mdio_in;timenum<=6;end586:begin data1[11]<=mdio_in;timenum<=7;end597:begin data1[10]<=mdio_in;timenum<=8;end608:begin data1[9]<=mdio_in;timenum<=9;end619:begin data1[8]<=mdio_in;timenum<=10;end6210:begin data1[7]<=mdio_in;timenum<=11;end6311:begin data1[6]<=mdio_in;timenum<=12;end6412:begin data1[5]<=mdio_in;timenum<=13;end6513:begin data1[4]<=mdio_in;timenum<=14;end6614:begin data1[3]<=mdio_in;timenum<=15;end6715:begin data1[2]<=mdio_in;timenum<=16;end6816:begin data1[1]<=mdio_in;timenum<=17;end69 17:begin data1[0]<=mdio_in;mdc_count<=1;timenum<=18;end7018:begin mdc_count<=mdc_count+1;wr_rd<=1;mdio<=1;if(mdc_count==7'h3f)mdc_count<=0;timenum<=0; end71endcase7275end。

附录DE2-115引脚表

SW[11]PIN_AB24Slide Switch[11]Depending on JP7 SW[12]PIN_AB23Slide Switch[12]Depending on JP7 SW[13]PIN_AA24Slide Switch[13]Depending on JP7 SW[14]PIN_AA23Slide Switch[14]Depending on JP7 SW[15]PIN_AA22Slide Switch[15]Depending on JP7 SW[16]PIN_Y24Slide Switch[16]Depending on JP7 SW[17]PIN_Y23Slide Switch[17]Depending on JP7表 2 按钮开关引脚配置Signal Name FPGA Pin No.Description I/O Standard KEY[0]PIN_M23Push-button[0]Depending on JP7KEY[1]PIN_M21Push-button[1]Depending on JP7KEY[2]PIN_N21Push-button[2]Depending on JP7KEY[3]PIN_R24Push-button[3]Depending on JP7表 3 LED引脚配置Signal Name FPGA Pin No.Description I/OS tandard LEDR[0]PIN_G19LED Red[0] 2.5VLEDR[1]PIN_F19LED Red[1] 2.5VLEDR[2]PIN_E19LED Red[2] 2.5VLEDR[3]PIN_F21LED Red[3] 2.5VLEDR[4]PIN_F18LED Red[4] 2.5VLEDR[5]PIN_E18LED Red[5] 2.5VLEDR[6]PIN_J19LED Red[6] 2.5VLEDR[7]PIN_H19LED Red[7] 2.5V LEDR[8]PIN_J17LED Red[8] 2.5V LEDR[9]PIN_G17LED Red[9] 2.5V LEDR[10]PIN_J15LED Red[10] 2.5V LEDR[11]PIN_H16LED Red[11] 2.5V LEDR[12]PIN_J16LED Red[12] 2.5V LEDR[13]PIN_H17LED Red[13] 2.5V LEDR[14]PIN_F15LED Red[14] 2.5V LEDR[15]PIN_G15LED Red[15] 2.5V LEDR[16]PIN_G16LED Red[16] 2.5V LEDR[17]PIN_H15LED Red[17] 2.5V LEDG[0]PIN_E21LED Green[0] 2.5V LEDG[1]PIN_E22LED Green[1] 2.5V LEDG[2]PIN_E25LED Green[2] 2.5V LEDG[3]PIN_E24LED Green[3] 2.5V LEDG[4]PIN_H21LED Green[4] 2.5V LEDG[5]PIN_G20LED Green[5] 2.5V LEDG[6]PIN_G22LED Green[6] 2.5V LEDG[7]PIN_G21LED Green[7] 2.5V LEDG[8]PIN_F17LED Green[8] 2.5V 表 4 七段数码管引脚配置Signal Na me FPGA Pin No.Description I/O StandardHEX0[0]PIN_G18Seven Segment Digit 0[0]2.5VHEX0[1]PIN_F22Seven Segment Digit 0[1] 2.5VHEX0[2]PIN_E17Seven Segment Digit 0[2] 2.5VHEX0[3]PIN_L26Seven Segment Digit 0[3]Depending onJP7HEX0[4]PIN_L25Seven Segment Digit 0[4]Depending on JP7HEX0[5]PIN_J22Seven Segment Digit 0[5]Depending on JP7HEX0[6]PIN_H22Seven Segment Digit 0[6]Depending on JP7HEX1[0]PIN_M24Seven Segment Digit 1[0]Depending on JP7HEX1[1]PIN_Y22Seven Segment Digit 1[1]Depending on JP7HEX1[2]PIN_W21Seven Segment Digit 1[2]Depending on JP7HEX1[3]PIN_W22Seven Segment Digit 1[3]Depending onJP7HEX1[4]PIN_W25Seven Segment Digit 1[4]Depending onJP7HEX1[5]PIN_U23Seven Segment Digit 1[5]Depending onJP7HEX1[6]PIN_U24Seven Segment Digit 1[6]Depending onJP7HEX2[0]PIN_AA25Seven Segment Digit 2[0]Depending onJP7HEX2[1]PIN_AA26Seven Segment Digit 2[1]Depending onJP7HEX2[2]PIN_Y25Seven Segment Digit 2[2]Depending on JP7HEX2[3]PIN_W26Seven Segment Digit 2[3]Depending on JP7HEX2[4]PIN_Y26Seven Segment Digit 2[4]Depending on JP7HEX2[5]PIN_W27Seven Segment Digit 2[5]Depending on JP7HEX2[6]PIN_W28Seven Segment Digit 2[6]Depending on JP7HEX3[0]PIN_V21Seven Segment Digit 3[0]Depending on JP7HEX3[1]PIN_U21Seven Segment Digit 3[1]Depending on JP7HEX3[2]PIN_AB20Seven Segment Digit 3[2]Depending onJP6HEX3[3]PIN_AA21Seven Segment Digit 3[3]Depending onJP6HEX3[4]PIN_AD24Seven Segment Digit 3[4]Depending onJP6HEX3[5]PIN_AF23Seven Segment Digit 3[5]Depending onJP6HEX3[6]PIN_Y19Seven Segment Digit 3[6]Depending onJP6HEX4[0]PIN_AB19Seven Segment Digit 4[0]Depending onJP6HEX4[1]PIN_AA19Seven Segment Digit 4[1]Depending on JP6HEX4[2]PIN_AG21Seven Segment Digit 4[2]Depending on JP6HEX4[3]PIN_AH21Seven Segment Digit 4[3]Depending on JP6HEX4[4]PIN_AE19Seven Segment Digit 4[4]Depending on JP6HEX4[5]PIN_AF19Seven Segment Digit 4[5]Depending on JP6HEX4[6]PIN_AE18Seven Segment Digit 4[6]Depending on JP6HEX5[0]PIN_AD18Seven Segment Digit 5[0]Depending on JP6HEX5[1]PIN_AC18Seven Segment Digit 5[1]Depending onJP6HEX5[2]PIN_AB18Seven Segment Digit 5[2]Depending onJP6HEX5[3]PIN_AH19Seven Segment Digit 5[3]Depending onJP6HEX5[4]PIN_AG19Seven Segment Digit 5[4]Depending onJP6HEX5[5]PIN_AF18Seven Segment Digit 5[5]Depending onJP6HEX5[6]PIN_AH18Seven Segment Digit 5[6]Depending onJP6HEX6[0]PIN_AA17Seven Segment Digit 6[0]Depending on JP6HEX6[1]PIN_AB16Seven Segment Digit 6[1]Depending on JP6HEX6[2]PIN_AA16Seven Segment Digit 6[2]Depending on JP6HEX6[3]PIN_AB17Seven Segment Digit 6[3]Depending on JP6HEX6[4]PIN_AB15Seven Segment Digit 6[4]Depending on JP6HEX6[5]PIN_AA15Seven Segment Digit 6[5]Depending on JP6HEX6[6]PIN_AC17Seven Segment Digit 6[6]Depending on JP6HEX7[0]PIN_AD17Seven Segment Digit 7[0]Depending onJP6HEX7[1]PIN_AE17Seven Segment Digit 7[1]Depending onJP6HEX7[2]PIN_AG17Seven Segment Digit 7[2]Depending onJP6HEX7[3]PIN_AH17Seven Segment Digit 7[3]Depending onJP6HEX7[4]PIN_AF17Seven Segment Digit 7[4]Depending on JP6HEX7[5]PIN_AG18Seven Segment Digit 7[5]Depending on JP6HEX7[6]PIN_AA14Seven Segment Digit 7[6] 3.3V表 5 时钟信号引脚配置信息Signal NameFPGA Pin N o.DescriptionI/O StandardCLOCK_50PIN_Y250 MHz clock input3.3V CLOCK2_50PIN_AG1450 MHz clock input 3.3V CLOCK3_50PIN_AG1550 MHz clock input Depending onJP6SMA_CLKOUT PIN_AE23External (SMA) clock o utputDepending onJP6SMA_CLKINPIN_AH14External (SMA) clock in put3.3V表 6 LCD 模块引脚配置Signal NameFPGAPinNo.DescriptionI/OLCD_DATA[7]PIN_M5LCD Data[7]StandardLCD_DATA[6]PIN_M3LCD Data[6]3.3VLCD_DATA[5]PIN_K2LCD Data[5]3.3VLCD_DATA[4]PIN_K1LCD Data[4]3.3VLCD_DATA[3]PIN_K7LCD Data[3]3.3VLCD_DATA[2]PIN_L2LCD Data[2]3.3VLCD_DATA[1]PIN_L1LCD Data[1]3.3VLCD_DATA[0]PIN_L3LCD Data[0]3.3VLCD_ENPIN_L4LCD Enable3.3VLCD_RWPIN_M1LCD Read/Write Select, 0 = Write, 1 = Read3.3VLCD_RSPIN_M2LCD Command/Data S elect, 0 = Command, 1= Data3.3VLCD_ONPIN_L5LCD Power ON/OFF3.3V LCD_BLONPIN_L6LCD Back Light ON/OF F 3.3V表 7 HSMC 接口引脚配置Signal NameFPGA Pin No.DescriptionI/O StandardHSMC_CLKIN0PIN_AH15Dedicated clock inputDepending on JP6HSMC_CLKIN_N1PIN_J28LVDS RX or C MOS I/O or diff erential clock inputDepending on JP7HSMC_CLKIN_N2PIN_Y28LVDS RX or C MOS I/O or diff erential clock inDepending on JP7putHSMC_CLKIN_P1PIN_J27LVDS RX or C MOS I/O or diff erential clock inputDepending on JP7HSMC_CLKIN_P2PIN_Y27LVDS RX or C MOS I/O or diff erential clock in put Depending on JP7HSMC_CLKOUT0PIN_AD28Dedicated clock output Depending on JP7HSMC_CLKOUT_N1PIN_G24LVDS TX or C MOS I/O or diff erential clock in put/output Depending on J P7HSMC_CLKOUT_N2PIN_V24LVDS TX or C MOS I/O or diff erential clock in put/output Depending on J P7HSMC_CLKOUT_P1PIN_G23LVDS TX or C MOS I/O or diff erential clock input/outputDepending on J P7HSMC_CLKOUT_P2PIN_V23LVDS TX or C MOS I/O or diff erential clock input/outputDepending on JP7HSMC_D[0]PIN_AE26LVDS TX or CDepending on JMOS I/O P7HSMC_D[1]PIN_AE28LVDS TX or CMOS I/O Depending on J P7HSMC_D[2]PIN_AE27LVDS TX or CMOS I/O Depending on J P7HSMC_D[3]PIN_AF27LVDS TX or CMOS I/O Depending on J P7HSMC_RX_D_N[0]PIN_F25LVDS RX bit 0n or CMOS I/O Depending on J P7HSMC_RX_D_N[1]PIN_C27LVDS RX bit 1n or CMOS I/O Depending on J P7HSMC_RX_D_N[2]PIN_E26LVDS RX bit 2n or CMOS I/O Depending on J P7HSMC_RX_D_N[3]PIN_G26LVDS RX bit 3n or CMOS I/O Depending on J P7HSMC_RX_D_N[4]PIN_H26LVDS RX bit 4n or CMOS I/O Depending on J P7HSMC_RX_D_N[5]PIN_K26LVDS RX bit 5n or CMOS I/O Depending on J P7HSMC_RX_D_N[6]PIN_L24LVDS RX bit 6n or CMOS I/O Depending on J P7HSMC_RX_D_N[7]PIN_M26LVDS RX bit 7n or CMOS I/O Depending on J P7HSMC_RX_D_N[8]PIN_R26LVDS RX bit 8n or CMOS I/O Depending on J P7HSMC_RX_D_N[9]PIN_T26LVDS RX bit 9n or CMOS I/O Depending on J P7HSMC_RX_D_N[10]PIN_U26LVDS RX bit 10n or CMOS I/O Depending on J P7HSMC_RX_D_N[11]PIN_L22LVDS RX bit 11n or CMOS I/O Depending on J P7HSMC_RX_D_N[12]PIN_N26LVDS RX bit 12n or CMOS I/O Depending on J P7HSMC_RX_D_N[13]PIN_P26LVDS RX bit 13n or CMOS I/O Depending on J P7HSMC_RX_D_N[14]PIN_R21LVDS RX bit 14n or CMOS I/O Depending on J P7HSMC_RX_D_N[15]PIN_R23LVDS RX bit 15n or CMOS I/O Depending on J P7HSMC_RX_D_N[16]PIN_T22LVDS RX bit 16n or CMOS I/O Depending on J P7HSMC_RX_D_P[0]PIN_F24LVDS RX bit 0or CMOS I/O Depending on J P7HSMC_RX_D_P[1]PIN_D26LVDS RX bit 1or CMOS I/O Depending on J P7HSMC_RX_D_P[2]PIN_F26LVDS RX bit 2or CMOS I/O Depending on J P7HSMC_RX_D_P[3]PIN_G25LVDS RX bit 3or CMOS I/O Depending on J P7HSMC_RX_D_P[4]PIN_H25LVDS RX bit 4or CMOS I/O Depending on J P7HSMC_RX_D_P[5]PIN_K25LVDS RX bit 5or CMOS I/O Depending on J P7HSMC_RX_D_P[6]PIN_L23LVDS RX bit 6or CMOS I/O Depending on J P7HSMC_RX_D_P[7]PIN_M25LVDS RX bit 7or CMOS I/O Depending on J P7HSMC_RX_D_P[8]PIN_R25LVDS RX bit 8or CMOS I/O Depending on J P7HSMC_RX_D_P[9]PIN_T25LVDS RX bit 9or CMOS I/O Depending on J P7HSMC_RX_D_P[10]PIN_U25LVDS RX bit 10 or CMOS I/O Depending on J P7HSMC_RX_D_P[11]PIN_L21LVDS RX bit 11 or CMOS I/O Depending on J P7HSMC_RX_D_P[12]PIN_N25LVDS RX bit 12 or CMOS I/O Depending on J P7HSMC_RX_D_P[13]PIN_P25LVDS RX bit 13 or CMOS I/O Depending on J P7HSMC_RX_D_P[14]PIN_P21LVDS RX bit 14 or CMOS I/O Depending on J P7HSMC_RX_D_P[15]PIN_R22LVDS RX bit 15 or CMOS I/O Depending on J P7HSMC_RX_D_P[16]PIN_T21LVDS RX bit 16 or CMOS I/O Depending on J P7HSMC_TX_D_N[0]PIN_D28LVDS TX bit 0n or CMOS I/O Depending on J P7HSMC_TX_D_N[1]PIN_E28LVDS TX bit 1n or CMOS I/O Depending on J P7HSMC_TX_D_N[2]PIN_F28LVDS TX bit 2n or CMOS I/O Depending on J P7HSMC_TX_D_N[3]PIN_G28LVDS TX bit 3n or CMOS I/O Depending on J P7HSMC_TX_D_N[4]PIN_K28LVDS TX bit 4n or CMOS I/O Depending on J P7HSMC_TX_D_N[5]PIN_M28LVDS TX bit 5n or CMOS I/O Depending on J P7HSMC_TX_D_N[6]PIN_K22LVDS TX bit 6n or CMOS I/O Depending on J P7HSMC_TX_D_N[7]PIN_H24LVDS TX bit 7n or CMOS I/O Depending on J P7HSMC_TX_D_N[8]PIN_J24LVDS TX bit 8n or CMOS I/O Depending on J P7HSMC_TX_D_N[9]PIN_P28LVDS TX bit 9n or CMOS I/O Depending on J P7HSMC_TX_D_N[10]PIN_J26LVDS TX bit 10n or CMOS I/O Depending on J P7HSMC_TX_D_N[11]PIN_L28LVDS TX bit 11n or CMOS I/Depending on J P7OHSMC_TX_D_N[12]PIN_V26LVDS TX bit 12n or CMOS I/O Depending on J P7HSMC_TX_D_N[13]PIN_R28LVDS TX bit 13n or CMOS I/O Depending on J P7HSMC_TX_D_N[14]PIN_U28LVDS TX bit 14n or CMOS I/O Depending on J P7HSMC_TX_D_N[15]PIN_V28LVDS TX bit 15n or CMOS I/O Depending on J P7HSMC_TX_D_N[16]PIN_V22LVDS TX bit 16n or CMOS I/O Depending on J P7HSMC_TX_D_P[0]PIN_D27LVDS TX bit 0or CMOS I/O Depending on J P7HSMC_TX_D_P[1]PIN_E27LVDS TX bit 1or CMOS I/O Depending on J P7HSMC_TX_D_P[2]PIN_F27LVDS TX bit 2or CMOS I/O Depending on J P7HSMC_TX_D_P[3]PIN_G27LVDS TX bit 3or CMOS I/O Depending on J P7HSMC_TX_D_P[4]PIN_K27LVDS TX bit 4or CMOS I/O Depending on J P7HSMC_TX_D_P[5]PIN_M27LVDS TX bit 5 Depending on Jor CMOS I/O P7HSMC_TX_D_P[6]PIN_K21LVDS TX bit 6or CMOS I/O Depending on J P7HSMC_TX_D_P[7]PIN_H23LVDS TX bit 7or CMOS I/O Depending on J P7HSMC_TX_D_P[8]PIN_J23LVDS TX bit 8or CMOS I/O Depending on J P7HSMC_TX_D_P[9]PIN_P27LVDS TX bit 9or CMOS I/O Depending on J P7HSMC_TX_D_P[10]PIN_J25LVDS TX bit 10 or CMOS I/O Depending on J P7HSMC_TX_D_P[11]PIN_L27LVDS TX bit 11 or CMOS I/O Depending on J P7HSMC_TX_D_P[12]PIN_V25LVDS TX bit 12 or CMOS I/O Depending on J P7HSMC_TX_D_P[13]PIN_R27LVDS TX bit 13 or CMOS I/O Depending on J P7HSMC_TX_D_P[14]PIN_U27LVDS TX bit 14 or CMOS I/O Depending on J P7HSMC_TX_D_P[15]PIN_V27LVDS TX bit 15 or CMOS I/O Depending on J P7HSMC_TX_D_P[16]PIN_U22LVDS TX bit 16 or CMOS I/O Depending on J P7表8 GPIO 引脚配置信息Signal Nam e FPGA Pin No.Description I/O StandardGPIO[0]PIN_AB22GPIO Connection DATA[0]Depending on JP 6GPIO[1]PIN_AC15GPIO Connection DATA[1]Depending on JP 6GPIO[2]PIN_AB21GPIO Connection DATA[2]Depending on JP 6GPIO[3]PIN_Y17GPIO Connection DATA[3]Depending on JP 6GPIO[4]PIN_AC21GPIO Connection DATA[4]Depending on JP 6GPIO[5]PIN_Y16GPIO Connection DATA[5]Depending on JP 6GPIO[6]PIN_AD21GPIO Connection DATA[6]Depending on JP 6GPIO[7]PIN_AE16GPIO Connection DATA[7]Depending on JP 6GPIO[8]PIN_AD15GPIO Connection DATA[8]Depending on JP 6GPIO[9]PIN_AE15GPIO Connection DATA[9]Depending on JP 6GPIO[10]PIN_AC19GPIO Connection DATA[10]Depending on JP 6GPIO[11]PIN_AF16GPIO Connection DATA[11]Depending on JP 6GPIO[12]PIN_AD19GPIO Connection DATA[12]Depending on JP 6GPIO[13]PIN_AF15GPIO Connection DATA[13]Depending on JP 6GPIO[14]PIN_AF24GPIO Connection DATA[14]Depending on JP 6GPIO[15]PIN_AE21GPIO Connection DATA[15]Depending on JP 6GPIO[16]PIN_AF25GPIO Connection DATA[16]Depending on JP 6GPIO[17]PIN_AC22GPIO Connection DATA[17]Depending on JP 6GPIO[18]PIN_AE22GPIO Connection DATA[18]Depending on JP 6GPIO[19]PIN_AF21GPIO Connection DATA[19]Depending on JP 6GPIO[20]PIN_AF22GPIO Connection DATA[20]Depending on JP 6GPIO[21]PIN_AD22GPIO Connection DATA[21]Depending on JP 6GPIO[22]PIN_AG25GPIO Connection DATA[22]Depending on JP 6GPIO[23]PIN_AD25GPIO Connection DATA[23]Depending on JP 6GPIO[24]PIN_AH25GPIO Connection DATA[24]Depending on JP 6GPIO[25]PIN_AE25GPIO Connection DATA[25]Depending on JP 6GPIO[26]PIN_AG22GPIO Connection DATA[26]Depending on JP 6GPIO[27]PIN_AE24GPIO Connection DATA[27]Depending on JP 6GPIO[28]PIN_AH22GPIO Connection DATA[28]Depending on JP 6GPIO[29]PIN_AF26GPIO Connection DATA[29]Depending on JP 6GPIO[30]PIN_AE20GPIO Connection DATA[30]Depending on JP 6GPIO[31]PIN_AG23GPIO Connection DATA[31]Depending on JP 6GPIO[32]PIN_AF20GPIO Connection DATA[32]Depending on JP 6GPIO[33]PIN_AH26GPIO Connection DATA[33]Depending on JP 6GPIO[34]PIN_AH23GPIO Connection DATA[34]Depending on JP 6GPIO[35]PIN_AG26GPIO Connection DATA[35]Depending on JP 6表9 扩展接口引脚配置信息Signal Name FPGA Pin No.Description I/O Standard EX_IO[0]PIN_J10Extended IO[0] 3.3VEX_IO[1]PIN_J14Extended IO[1] 3.3VEX_IO[2]PIN_H13Extended IO[2] 3.3VEX_IO[3]PIN_H14Extended IO[3] 3.3VEX_IO[4]PIN_F14Extended IO[4] 3.3VEX_IO[5]PIN_E10Extended IO[5] 3.3VEX_IO[6]PIN_D9Extended IO[6] 3.3V表10 ADV7123 引脚配置Signal Name FPGA Pin No.Description I/O Standard VGA_R[0]PIN_E12VGA Red[0] 3.3VVGA_R[1]PIN_E11VGA Red[1] 3.3VVGA_R[2]PIN_D10VGA Red[2] 3.3VVGA_R[3]PIN_F12VGA Red[3] 3.3VVGA_R[4]PIN_G10VGA Red[4] 3.3VVGA_R[5]PIN_J12VGA Red[5] 3.3VVGA_R[6]PIN_H8VGA Red[6] 3.3VVGA_R[7]PIN_H10VGA Red[7] 3.3VVGA_G[0]PIN_G8VGA Green[0] 3.3VVGA_G[1]PIN_G11VGA Green[1] 3.3VVGA_G[2]PIN_F8VGA Green[2] 3.3VVGA_G[3]PIN_H12VGA Green[3] 3.3VVGA_G[4]PIN_C8VGA Green[4] 3.3VVGA_G[5]PIN_B8VGA Green[5] 3.3VVGA_G[6]PIN_F10VGA Green[6] 3.3VVGA_G[7]PIN_C9VGA Green[7] 3.3VVGA_B[0]PIN_B10VGA Blue[0] 3.3VVGA_B[1]PIN_A10VGA Blue[1] 3.3VVGA_B[2]PIN_C11VGA Blue[2] 3.3VVGA_B[3]PIN_B11VGA Blue[3] 3.3VVGA_B[4]PIN_A11VGA Blue[4] 3.3VVGA_B[5]PIN_C12VGA Blue[5] 3.3VVGA_B[6]PIN_D11VGA Blue[6] 3.3VVGA_B[7]PIN_D12VGA Blue[7] 3.3VVGA_CLK PIN_A12VGA Clock 3.3VVGA_BLANK_N PIN_F11VGA BLANK 3.3VVGA_HS PIN_G13VGA H_SYNC 3.3VVGA_VS PIN_C13VGA V_SYNC 3.3VVGA_SYNC_N PIN_C10VGA SYNC 3.3V表11 音频编解码芯片引脚配置Signal Name FPGA Pin No.Description I/O Standard3.3VAUD_ADCLRCK PIN_C2Audio CODEC ADC LR ClockAUD_ADCDAT PIN_D2Audio CODEC ADC Data 3.3V3.3VAUD_DACLRCK PIN_E3Audio CODEC DAC LR ClockAUD_DACDAT PIN_D1Audio CODEC DAC Data 3.3VAUD_XCK PIN_E1Audio CODEC Chip Clock 3.3V3.3VAUD_BCLK PIN_F2Audio CODEC Bit-StreamClockI2C_SCLK PIN_B7I2C Clock 3.3VI2C_SDAT PIN_A8I2C Data 3.3V表12 RS-232 引脚配置Signal Name FPGA Pin No.Description I/O Standard UART_RXD PIN_G12UART Receiver 3.3VUART_TXD PIN_G9UART Transmitter 3.3VUART_CTS PIN_G14UART Clear to Send 3.3VUART_RTS PIN_J13UART Request to Send3.3V表13 PS/2 引脚配置Signal Name FPGA Pin No.Description I/O StandardPS2_CLK PIN_G6PS/2 Clock 3.3VPS2_DAT PIN_H5PS/2 Data 3.3VPS2_CLK2PIN_G5PS/2 Clock (reserved for second PS/2 device)3.3VPS2_DAT2PIN_F5PS/2 Data (reserved for second PS/2 device)3.3V表14 千兆以太网芯片引脚配置Signal Name FPGA Pin No.Description I/O StandardE NET0_GTX_CLK PIN_A17GMII Transmit Clock 12.5VENET0_INT_N PIN_A21Interrupt open drain2.5Voutput 13.3V ENET0_LINK100PIN_C14Parallel LED outputof 100BASE-TX link12.5V ENET0_MDC PIN_C20Management data clock reference 1ENET0_MDIO PIN_B21Management data 12.5V2.5V ENET0_RST_N PIN_C19Hardware reset signal 1ENET0_RX_CLK PIN_A15GMII and MII receiv2.5Ve clock 12.5V ENET0_RX_COL PIN_E15GMII and MII collision 1ENET0_RX_CRS PIN_D15GMII and MII carrie2.5Vr sense 12.5V ENET0_RX_DATA[0]PIN_C16GMII and MII receive data[0] 12.5V ENET0_RX_DATA[1]PIN_D16GMII and MII receive data[1] 12.5V ENET0_RX_DATA[2]PIN_D17GMII and MII receive data[2] 12.5V ENET0_RX_DATA[3]PIN_C15GMII and MII receive data[3] 12.5V ENET0_RX_DV PIN_C17GMII and MII receive data valid 1ENET0_RX_ER PIN_D18GMII and MII receiv2.5Ve error 1ENET0_TX_CLK PIN_B17MII transmit clock 12.5V ENET0_TX_DATA[0]PIN_C18MII transmit data[0]2.5V12.5V ENET0_TX_DATA[1]PIN_D19MII transmit data[1]12.5V ENET0_TX_DATA[2]PIN_A19MII transmit data[2]12.5V ENET0_TX_DATA[3]PIN_B19MII transmit data[3]12.5V ENET0_TX_EN PIN_A18GMII and MII transmit enable 12.5V ENET0_TX_ER PIN_B18GMII and MII transmit error 1ENET1_GTX_CLK PIN_C23GMII Transmit Cloc2.5Vk 22.5V ENET1_INT_N PIN_D24Interrupt open drainoutput 22.5V ENET1_LINK100PIN_D13Parallel LED outputof 100BASE-TX link22.5V ENET1_MDC PIN_D23Management data clock reference 2ENET1_MDIO PIN_D25Management data 22.5V ENET1_RST_N PIN_D22Hardware reset sig2.5Vnal 22.5V ENET1_RX_CLK PIN_B15GMII and MII receive clock 22.5V ENET1_RX_COL PIN_B22GMII and MII collision 22.5V ENET1_RX_CRS PIN_D20GMII and MII carrier sense 22.5V ENET1_RX_DATA[0]PIN_B23GMII and MII receive data[0] 22.5V ENET1_RX_DATA[1]PIN_C21GMII and MII receive data[1] 22.5V ENET1_RX_DATA[2]PIN_A23GMII and MII receive data[2] 2ENET1_RX_DATA[3]PIN_D21GMII and MII receiv2.5Ve data[3] 2ENET1_RX_DV PIN_A22GMII and MII receiv2.5Ve data valid 22.5V ENET1_RX_ER PIN_C24GMII and MII receive error 2ENET1_TX_CLK PIN_C22MII transmit clock 22.5V2.5V ENET1_TX_DATA[0]PIN_C25MII transmit data[0]2ENET1_TX_DATA[1]PIN_A26MII transmit data[1]2.5V2ENET1_TX_DATA[2]PIN_B26MII transmit data[2]2.5V2ENET1_TX_DATA[3]PIN_C26MII transmit data[3]2.5V22.5V ENET1_TX_EN PIN_B25GMII and MII transmit enable 22.5V ENET1_TX_ER PIN_A25GMII and MII transmit error 2ENETCLK_25PIN_A14Ethernet clock sour3.3Vce表15 TV 解码芯片引脚配置Signal Name FPGA Pin No.Description I/O Standard TD_ DATA [0]PIN_E8TV Decoder Data[0] 3.3VTD_ DATA [1]PIN_A7TV Decoder Data[1] 3.3VTD_ DATA [2]PIN_D8TV Decoder Data[2] 3.3VTD_ DATA [3]PIN_C7TV Decoder Data[3] 3.3VTD_ DATA [4]PIN_D7TV Decoder Data[4] 3.3VTD_ DATA [5]PIN_D6TV Decoder Data[5] 3.3VTD_ DATA [6]PIN_E7TV Decoder Data[6] 3.3VTD_ DATA [7]PIN_F7TV Decoder Data[7] 3.3VTD_HS PIN_E5TV Decoder H_SYNC 3.3VTD_VS PIN_E4TV Decoder V_SYNC 3.3V3.3VTD_CLK27PIN_B14TV Decoder Clock Input.TD_RESET_N PIN_G7TV Decoder Reset 3.3VI2C_SCLK PIN_B7I2C Clock 3.3VI2C_SDAT PIN_A8I2C Data 3.3V 表16 USB (ISP1362)引脚配置Signal Name FPGA Pin No.Description I/O StandardOTG_ADDR[0]PIN_H7ISP1362 Address[0] 3.3V OTG_ADDR[1]PIN_C3ISP1362 Address[1] 3.3V OTG_DATA[0]PIN_J6ISP1362 Data[0] 3.3V OTG_DATA[1]PIN_K4ISP1362 Data[1] 3.3V OTG_DATA[2]PIN_J5ISP1362 Data[2] 3.3V OTG_DATA[3]PIN_K3ISP1362 Data[3] 3.3V OTG_DATA[4]PIN_J4ISP1362 Data[4] 3.3V OTG_DATA[5]PIN_J3ISP1362 Data[5] 3.3V OTG_DATA[6]PIN_J7ISP1362 Data[6] 3.3V OTG_DATA[7]PIN_H6ISP1362 Data[7] 3.3V OTG_DATA[8]PIN_H3ISP1362 Data[8] 3.3V OTG_DATA[9]PIN_H4ISP1362 Data[9] 3.3V OTG_DATA[10]PIN_G1ISP1362 Data[10] 3.3V OTG_DATA[11]PIN_G2ISP1362 Data[11] 3.3V OTG_DATA[12]PIN_G3ISP1362 Data[12] 3.3V OTG_DATA[13]PIN_F1ISP1362 Data[13] 3.3V OTG_DATA[14]PIN_F3ISP1362 Data[14] 3.3V OTG_DATA[15]PIN_G4ISP1362 Data[15] 3.3V OTG_CS_N PIN_A3ISP1362 Chip Select 3.3VOTG_RD_N PIN_B3ISP1362 Read 3.3V OTG_WR_N PIN_A4ISP1362 Write 3.3V OTG_RST_N PIN_C5ISP1362 Reset 3.3V OTG_INT[0]PIN_A6ISP1362 Interrupt 0 3.3V OTG_INT[1]PIN_D5ISP1362 Interrupt 1 3.3V OTG_DACK_N[0]PIN_C4ISP1362 DMA Acknowledge 0 3.3V OTG_DACK_N[1]PIN_D4ISP1362 DMA Acknowledge 1 3.3V OTG_DREQ[0]PIN_J1ISP1362 DMA Request 0 3.3V OTG_DREQ[1]PIN_B4ISP1362 DMA Request 1 3.3V3.3V OTG_FSPEED PIN_C6USB Full Speed, 0 = Enable, Z= Disable3.3V OTG_LSPEED PIN_B6USB Low Speed, 0 = Enable, Z= Disable表17 IR 引脚配置Description I/O StandardSignal Name FPGA Pin No.IRDA_RXD PIN_Y15IR Receiver 3.3V表18 SRAM 引脚配置Signal Name FPGA Pin No.Description I/O Standard SRAM_ADDR[0]PIN_AB7SRAM Address[0] 3.3VSRAM_ADDR[1]PIN_AD7SRAM Address[1] 3.3VSRAM_ADDR[2]PIN_AE7SRAM Address[2] 3.3VSRAM_ADDR[3]PIN_AC7SRAM Address[3] 3.3VSRAM_ADDR[4]PIN_AB6SRAM Address[4] 3.3V SRAM_ADDR[5]PIN_AE6SRAM Address[5] 3.3V SRAM_ADDR[6]PIN_AB5SRAM Address[6] 3.3V SRAM_ADDR[7]PIN_AC5SRAM Address[7] 3.3V SRAM_ADDR[8]PIN_AF5SRAM Address[8] 3.3V SRAM_ADDR[9]PIN_T7SRAM Address[9] 3.3V SRAM_ADDR[10]PIN_AF2SRAM Address[10] 3.3V SRAM_ADDR[11]PIN_AD3SRAM Address[11] 3.3V SRAM_ADDR[12]PIN_AB4SRAM Address[12] 3.3V SRAM_ADDR[13]PIN_AC3SRAM Address[13] 3.3V SRAM_ADDR[14]PIN_AA4SRAM Address[14] 3.3V SRAM_ADDR[15]PIN_AB11SRAM Address[15] 3.3V SRAM_ADDR[16]PIN_AC11SRAM Address[16] 3.3V SRAM_ADDR[17]PIN_AB9SRAM Address[17] 3.3V SRAM_ADDR[18]PIN_AB8SRAM Address[18] 3.3V SRAM_ADDR[19]PIN_T8SRAM Address[19] 3.3V SRAM_DQ[0]PIN_AH3SRAM Data[0] 3.3V SRAM_DQ[1]PIN_AF4SRAM Data[1] 3.3V SRAM_DQ[2]PIN_AG4SRAM Data[2] 3.3V SRAM_DQ[3]PIN_AH4SRAM Data[3] 3.3V SRAM_DQ[4]PIN_AF6SRAM Data[4] 3.3V SRAM_DQ[5]PIN_AG6SRAM Data[5] 3.3V SRAM_DQ[6]PIN_AH6SRAM Data[6] 3.3VSRAM_DQ[7]PIN_AF7SRAM Data[7] 3.3VSRAM_DQ[8]PIN_AD1SRAM Data[8] 3.3VSRAM_DQ[9]PIN_AD2SRAM Data[9] 3.3VSRAM_DQ[10]PIN_AE2SRAM Data[10] 3.3VSRAM_DQ[11]PIN_AE1SRAM Data[11] 3.3VSRAM_DQ[12]PIN_AE3SRAM Data[12] 3.3VSRAM_DQ[13]PIN_AE4SRAM Data[13] 3.3VSRAM_DQ[14]PIN_AF3SRAM Data[14] 3.3VSRAM_DQ[15]PIN_AG3SRAM Data[15] 3.3VSRAM_OE_N PIN_AD5SRAM Output EnableSRAM_WE_N PIN_AE8SRAM Write EnableSRAM_CE_N PIN_AF8SRAM Chip SelectSRAM_LB_N PIN_AD4SRAM Lower Byte StrobeSRAM_UB_N PIN_AC4SRAM Higher Byte Strobe表19 SDRAM 引脚配置Signal Name FPGA Pin No.Description I/O Standard DRAM_ADDR[0]PIN_R6SDRAM Address[0] 3.3VDRAM_ADDR[1]PIN_V8SDRAM Address[1] 3.3VDRAM_ADDR[2]PIN_U8SDRAM Address[2] 3.3VDRAM_ADDR[3]PIN_P1SDRAM Address[3] 3.3VDRAM_ADDR[4]PIN_V5SDRAM Address[4] 3.3VDRAM_ADDR[5]PIN_W8SDRAM Address[5] 3.3V DRAM_ADDR[6]PIN_W7SDRAM Address[6] 3.3V DRAM_ADDR[7]PIN_AA7SDRAM Address[7] 3.3V DRAM_ADDR[8]PIN_Y5SDRAM Address[8] 3.3V DRAM_ADDR[9]PIN_Y6SDRAM Address[9] 3.3V DRAM_ADDR[10]PIN_R5SDRAM Address[10] 3.3V DRAM_ADDR[11]PIN_AA5SDRAM Address[11] 3.3V DRAM_ADDR[12]PIN_Y7SDRAM Address[12] 3.3V DRAM_DQ[0]PIN_W3SDRAM Data[0] 3.3V DRAM_DQ[1]PIN_W2SDRAM Data[1] 3.3V DRAM_DQ[2]PIN_V4SDRAM Data[2] 3.3V DRAM_DQ[3]PIN_W1SDRAM Data[3] 3.3V DRAM_DQ[4]PIN_V3SDRAM Data[4] 3.3V DRAM_DQ[5]PIN_V2SDRAM Data[5] 3.3V DRAM_DQ[6]PIN_V1SDRAM Data[6] 3.3V DRAM_DQ[7]PIN_U3SDRAM Data[7] 3.3V DRAM_DQ[8]PIN_Y3SDRAM Data[8] 3.3V DRAM_DQ[9]PIN_Y4SDRAM Data[9] 3.3V DRAM_DQ[10]PIN_AB1SDRAM Data[10] 3.3V DRAM_DQ[11]PIN_AA3SDRAM Data[11] 3.3V DRAM_DQ[12]PIN_AB2SDRAM Data[12] 3.3V DRAM_DQ[13]PIN_AC1SDRAM Data[13] 3.3V DRAM_DQ[14]PIN_AB3SDRAM Data[14] 3.3VDRAM_DQ[15]PIN_AC2SDRAM Data[15] 3.3V SRAM_OE_N PIN_AD5SRAM Output Enable 3.3V SRAM_WE_N PIN_AE8SRAM Write Enable 3.3V SRAM_CE_N PIN_AF8SRAM Chip Select 3.3V SRAM_LB_N PIN_AD4SRAM Lower Byte Strobe3.3VSRAM_UB_N PIN_AC4SRAM Higher Byte Strobe3.3V 表20 SDRAM 引脚配置Signal Name FPGA Pin No.Description I/O StandardDRAM_ADDR[0]PIN_R6SDRAM Address[0] 3.3V DRAM_ADDR[1]PIN_V8SDRAM Address[1] 3.3V DRAM_ADDR[2]PIN_U8SDRAM Address[2] 3.3V DRAM_ADDR[3]PIN_P1SDRAM Address[3] 3.3V DRAM_ADDR[4]PIN_V5SDRAM Address[4] 3.3V DRAM_ADDR[5]PIN_W8SDRAM Address[5] 3.3V DRAM_ADDR[6]PIN_W7SDRAM Address[6] 3.3V DRAM_ADDR[7]PIN_AA7SDRAM Address[7] 3.3V DRAM_ADDR[8]PIN_Y5SDRAM Address[8] 3.3V DRAM_ADDR[9]PIN_Y6SDRAM Address[9] 3.3V DRAM_ADDR[10]PIN_R5SDRAM Address[10] 3.3V DRAM_ADDR[11]PIN_AA5SDRAM Address[11] 3.3V DRAM_ADDR[12]PIN_Y7SDRAM Address[12] 3.3VDRAM_DQ[0]PIN_W3SDRAM Data[0] 3.3V DRAM_DQ[1]PIN_W2SDRAM Data[1] 3.3V DRAM_DQ[2]PIN_V4SDRAM Data[2] 3.3V DRAM_DQ[3]PIN_W1SDRAM Data[3] 3.3V DRAM_DQ[4]PIN_V3SDRAM Data[4] 3.3V DRAM_DQ[5]PIN_V2SDRAM Data[5] 3.3V DRAM_DQ[6]PIN_V1SDRAM Data[6] 3.3V DRAM_DQ[7]PIN_U3SDRAM Data[7] 3.3V DRAM_DQ[8]PIN_Y3SDRAM Data[8] 3.3V DRAM_DQ[9]PIN_Y4SDRAM Data[9] 3.3V DRAM_DQ[10]PIN_AB1SDRAM Data[10] 3.3V DRAM_DQ[11]PIN_AA3SDRAM Data[11] 3.3V DRAM_DQ[12]PIN_AB2SDRAM Data[12] 3.3V DRAM_DQ[13]PIN_AC1SDRAM Data[13] 3.3V DRAM_DQ[14]PIN_AB3SDRAM Data[14] 3.3V DRAM_DQ[15]PIN_AC2SDRAM Data[15] 3.3V DRAM_DQ[16]PIN_M8SDRAM Data[16] 3.3V DRAM_DQ[17]PIN_L8SDRAM Data[17] 3.3V DRAM_DQ[18]PIN_P2SDRAM Data[18] 3.3V DRAM_DQ[19] PIN_N3SDRAM Data[19] 3.3V DRAM_DQ[20]PIN_N4SDRAM Data[20] 3.3V DRAM_DQ[21]PIN_M4SDRAM Data[21] 3.3V DRAM_DQ[22]PIN_M7SDRAM Data[22] 3.3VDRAM_DQ[23]PIN_L7SDRAM Data[23] 3.3V DRAM_DQ[24]PIN_U5SDRAM Data[24] 3.3V DRAM_DQ[25]PIN_R7SDRAM Data[25] 3.3V DRAM_DQ[26]PIN_R1SDRAM Data[26] 3.3V DRAM_DQ[27]PIN_R2SDRAM Data[27] 3.3V DRAM_DQ[28]PIN_R3SDRAM Data[28] 3.3V DRAM_DQ[29]PIN_T3SDRAM Data[29] 3.3V DRAM_DQ[30]PIN_U4SDRAM Data[30] 3.3V DRAM_DQ[31]PIN_U1SDRAM Data[31] 3.3V DRAM_BA[0]PIN_U7SDRAM Bank Address[0] 3.3V DRAM_BA[1]PIN_R4SDRAM Bank Address[1] 3.3V DRAM_DQM[0]PIN_U2SDRAM byte Data Mask[0] 3.3V DRAM_DQM[1]PIN_W4SDRAM byte Data Mask[1] 3.3V DRAM_DQM[2]PIN_K8SDRAM byte Data Mask[2] 3.3V DRAM_DQM[3]PIN_N8SDRAM byte Data Mask[3] 3.3V DRAM_RAS_N PIN_U6SDRAM Row Address Strobe 3.3V3.3V DRAM_CAS_N PIN_V7SDRAM Column Address StrobeDRAM_CKE PIN_AA6SDRAM Clock Enable 3.3V DRAM_CLK PIN_AE5SDRAM Clock 3.3V DRAM_WE_N PIN_V6SDRAM Write Enable 3.3V DRAM_CS_N PIN_T4SDRAM Chip Select 3.3V 表21 Flash 引脚配置Signal Name FPGA Pin No.Description I/O StandardFL_ADDR[0]PIN_AG12FLASH Address[0] 3.3V FL_ADDR[1]PIN_AH7FLASH Address[1] 3.3V FL_ADDR[2]PIN_Y13FLASH Address[2] 3.3V FL_ADDR[3]PIN_Y14FLASH Address[3] 3.3V FL_ADDR[4]PIN_Y12FLASH Address[4] 3.3V FL_ADDR[5]PIN_AA13FLASH Address[5] 3.3V FL_ADDR[6]PIN_AA12FLASH Address[6] 3.3V FL_ADDR[7]PIN_AB13FLASH Address[7] 3.3V FL_ADDR[8]PIN_AB12FLASH Address[8] 3.3V FL_ADDR[9]PIN_AB10FLASH Address[9] 3.3V FL_ADDR[10]PIN_AE9FLASH Address[10] 3.3V FL_ADDR[11]PIN_AF9FLASH Address[11] 3.3V FL_ADDR[12]PIN_AA10FLASH Address[12] 3.3V FL_ADDR[13]PIN_AD8FLASH Address[13] 3.3V FL_ADDR[14]PIN_AC8FLASH Address[14] 3.3V FL_ADDR[15]PIN_Y10FLASH Address[15] 3.3V FL_ADDR[16]PIN_AA8FLASH Address[16] 3.3V FL_ADDR[17]PIN_AH12FLASH Address[17] 3.3V FL_ADDR[18]PIN_AC12FLASH Address[18] 3.3V FL_ADDR[19]PIN_AD12FLASH Address[19] 3.3V FL_ADDR[20]PIN_AE10FLASH Address[20] 3.3V FL_ADDR[21]PIN_AD10FLASH Address[21] 3.3V。

DE2-115中文使用手册

早上1目录第1章.关于DE2-115 工具包 (4)1.1包装内容 (4)1.2 DE2-115 的组装 (5)1.3获得帮助 (5)第2章.DE2-115 开发板简介 (7)2.1开发板布局和组件 (7)2.2 DE2-115 系统框图 (9)2.3 DE2-115上电 (11)第3章.DE2-115控制面板 (13)3.1 控制面板初始化 (13)3.2控制LED灯, 7段数码显示管和 LCD显示器 (15)3.3开关与按钮 (17)3.4 SDRAM/SRAM/EEPROM/Flash控制器和编程器 (18)3.5 USB 监测 (20)3.6 PS/2设备 (20)3.7 SD卡 (21)3.8 RS-232 通信 (22)3.9 VGA (23)3.10 HSMC (24)3.11红外接收器 (25)3.12 DE2-115 控制面板的整体结构 (26)第4章.使用DE2-115 (28)4.1 配置Cyclone IV E FPGA芯片 (28)4.2 使用按钮开关和拨动开关 (31)4.3 使用LED (32)14.5 时钟电路 (36)4.6 使用LCD模块 (37)4.7 HSMC接口 (39)4.8 使用通用扩展接头 (44)4.9 使用14脚扩展口 (49)4.10 使用VGA (49)4.11 使用24比特音频编解码芯片 (52)4.12 RS-232串口 (53)4.13 PS/2接口 (54)4.14 千兆以太网接口 (55)4.15 TV解码器 (58)4.16 TV编码器实现 (59)4.17 使用USB界面 (59)4.18 使用IR模块 (61)4.19 使用SRAM/SDRAM/Flash/EEPROM/SD 卡 (61)第5章.DE2-115 系统生成器 (68)5.1简介 (68)5.2一般设计流程 (68)第6章.高阶设计范例 (75)6.1 DE2-115默认配置 (75)6.2 TV 电视盒设计范例 (76)6.3 USB画笔 (78)6.4 USB设备 (80)6.5 卡拉OK机 (82)6.6 SD卡设计范例 (84)6.7 SD卡音乐播放器 (86)6.8 PS/2鼠标控制器设计范例 (89)6.9 IR接收器设计范例 (92)6.10 音乐合成器设计范例 (95)26.12 网页服务器设计范例 (101)第7章.附录1097.1 修改历史 (109)7.2 版权声明 (109)3第1章.关于DE2-115 工具包DE2-115 套装包含了所有使用开发板会用到的器件资源,您额外需要的仅是一台装有微软视窗操作系统的个人电脑。

FPGA设计与应用实验指导书-v2

FPGA设计与应用实验指导书实验一Quartus II开发软件入门一、实验目的1. 熟悉Quartus II 开发软件的基本使用方法2. 掌握用VHDL语言设计组合逻辑电路的方法二、实验内容1. 运用Quartus II 开发软件,完成工程创建、代码编写、程序调试、编译仿真等基本操作。

2. 用VHDL语言设计实现一个3-8译码器,并进行功能仿真验证。

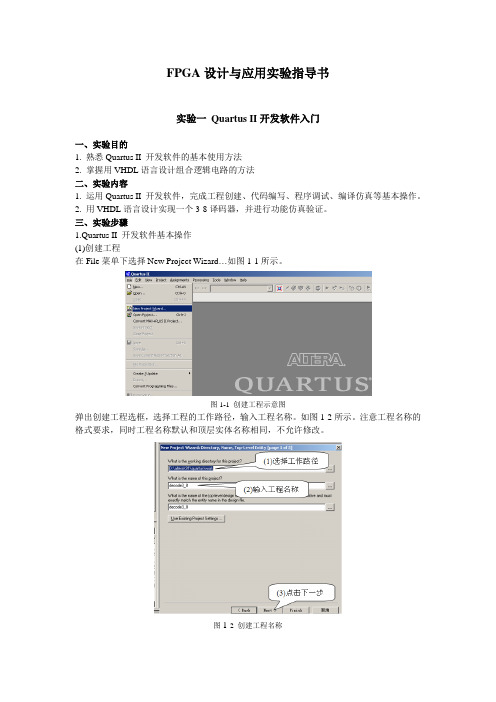

三、实验步骤1.Quartus II 开发软件基本操作(1)创建工程在File菜单下选择New Project Wizard…如图1-1所示。

图1-1 创建工程示意图弹出创建工程选框,选择工程的工作路径,输入工程名称。

如图1-2所示。

注意工程名称的格式要求,同时工程名称默认和顶层实体名称相同,不允许修改。

图1-2 创建工程名称可选择添加已有的程序文件,如图1-3所示。

这里不添加,直接下一步。

图1-3 添加文件选框选择芯片系列和芯片型号,如图1-4所示。

实验中使用的是Altera公司的Cyclone II系列FPGA 芯片,型号为EP2C35F672C6。

如果不进行硬件下载,可直接下一步。

图1-4 芯片参数选框EDA外部工具选框如图1-5所示。

一般选择默认值,直接下一步。

图1-5 EDA外部工具选框完成工程设置后的工程信息如图1-6所示。

图1-6 工程信息选框至此完成工程的创建。

(2)新建VHDL文件在File菜单下选择New选项,如图7所示。

图1-7新建文件示意图点击新建菜单后给出新建文件选框如图1-8所示。

选择VHDL File项创建VHDL文件。

图1-8 新建VHDL文件选框确定后弹出新建VHDL文件编辑窗口如图1-9所示。

可在窗口中编写程序内容并保存,注意文件名称与工程实体名称必须一致。

图1-9 VHDL文件编辑窗口至此完成VHDL文件的创建和VHDL程序的编写。

(3) 程序编译程序编写完成后,选择Processing菜单下的编译工具(Compiler Tool)菜单,如图1-10所示,调出编译工具。

《FPGA技术基础》实验一

实验一DE2的顶层默认程序这个实验为用户提供连接分配和顶层Verilog模块,这个模块也是这本手册所有其他实验的基础性模块。

这个实验产生的编程文件是DE2开发板在出货时作为默认载入开发板的编程文件。

本实验将介绍如何编译工程并把生成的编程文件下载到DE2开发板中。

启动开发板(1)将USB线和电源连接到DE2板上。

(2)按下电源开关,这时电源指示灯会被点亮。

(3)你将看到以下现象:●所有的LED灯都闪烁。

●所有七段数码管从0到F循环显示。

●液晶屏显示“Welcome to the Altera DE2 Board”。

●在VGA显示器上显示欢迎信息。

●将开关SW17置OFF,从LINEOUT插座输出1khz正弦波的声音;将开关SW17置ON并将一个MP3播放器的输出接到DE2板的LINE—IN端口,可从耳机里听到MP3播放的音乐。

●若将麦克风接到DE2板的MIC端口上,这样用户的声音可与MP3播放器混合。

Cyclone II中的顶层verilog模块这部分将介绍一个Quartus II工程中所需要的所有组件。

它将让你了解如何使用Quartus II将代码转换成数据流下载的整个设计流程。

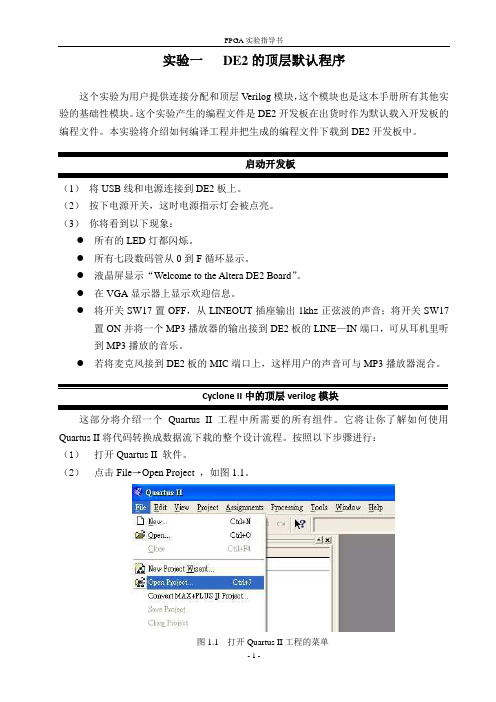

按照以下步骤进行:(1)打开Quartus II 软件。

(2)点击File→Open Project ,如图1.1。

图1.1 打开Quartus II工程的菜单(3)在D:\DE2_Default目录下选中DE2_Default.qpf工程文件打开。

(4)在“Project Navigator”工程导航区可查看该工程的层次、包含的所有文件、设计单元等信息。

其中“File”下列出了整个工程包含的所有文件。

双击顶层设计文件DE2_Default.v,可以看到文件的内容和I/O口的声明。

在对每个引脚声明时加上了详细的注释,以便用户更好的明白每个引脚的功能。

如图1.2所示。

编译设计(1)使用Processing→Start Compilation菜单或者单击快捷工具条中的工具按钮运行编译器。

南理工电类综合实验报告FM调制解调的数字实现汇总

《电类综合实验》仿真报告实验课题:FM调制解调的数字实现指导教师:刘光祖学生姓名:院系:电光学院专业:通信与信息系统实验时间:2016.05.09至2016.05.13一、实验背景1.FPGA简介FPGA(Field-Programmable Gate Array,现场可编程逻辑门阵列)是在PAL、GAL、CPLD等可编程逻辑器件的基础上进一步发展的产物,是专用集成电路领域一种半定制的集成数字芯片,其最大特点是现场可编程,既解决了全定制电路的不足,又克服了原有可编程逻辑器件门电路数有限的缺点。

FPGA的内部结构由CLB、RAM、DCM、IOB、Interconnect 等构成。

如下给出了FPGA的最典型的结构:FPGA开发的一般流程:1(a) 1(b)2.DE2-115开发板简介本实验中所用开发板为Altera公司的DE2-115。

如下为开发板的配置列表:•Altera Cyclone® IV 4CE115 FPGA 器件•Altera 串行配置芯片:EPCS64•USB Blaster 在线编程;也支持JTAG和AS可编程方式•2MB SRAM•两片64MB SDRAM•8MB Flash memory•SD卡插槽•4个按钮•18个滑动开关•18个红色LED•9个绿色LED•50M时钟源•24位音频编解码器,麦克风插孔•电视解码•RJ45 2G以太网接口•VGA连接器•含有USB_A和USB_B连接器的主从控制器•RS232收发器和9针连接器•PS/2鼠标和键盘连接器•红外接收器ControlPanel是开发板自带的一个工具软件,可以通过该软件提供的图形界面直接对FPGA上的各个外设进行操作。

通过该操作可以确认PC机与开发板的连接是否正确,开发板的硬件工作是否正常。

ControlPanel的安装过程如下:确保QUARTUS II 10.0 或以上版本能被成功安装;将开关RUN/PROG切换到RUN位置;将USB接线连接至USB驱动端口,供12V电源并打开开关;打开主机上的可执行文件DE2_115_ControlPanel.exe,controlPanel的用户界面如下:DE2_115_ControlPanel.exe一旦被启动,DE2_115_ControlPanel.sof程序流文件将会被自动加载;如果未连接,点击CONNECT,点sof文件将会重新加载到板子上;注意,控制面板将会占用一直到你关闭那个端口,除非你关闭USB端口,否则你不能使用QUARTUS II 来下载文件;控制面板现在可以使用了,通过设置一些LED灯ON/OFF的状态来观察DE2-115上的状态。

DE2开发板指导手册

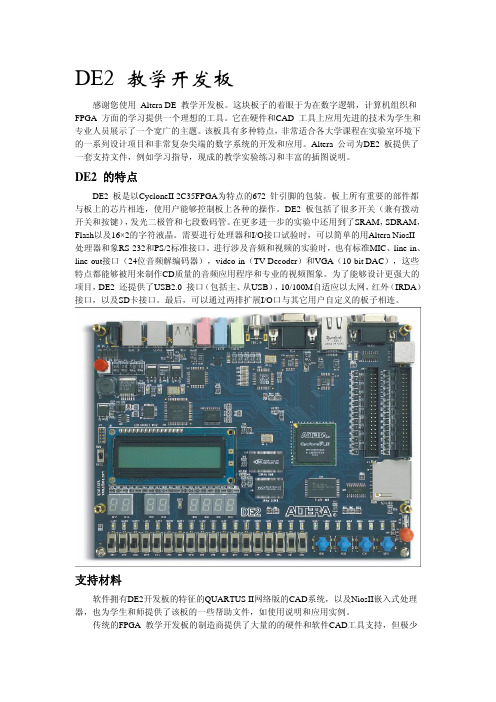

DE2 教学开发板感谢您使用 Altera DE 教学开发板。

这块板子的着眼于为在数字逻辑,计算机组织和FPGA 方面的学习提供一个理想的工具。

它在硬件和CAD 工具上应用先进的技术为学生和专业人员展示了一个宽广的主题。

该板具有多种特点,非常适合各大学课程在实验室环境下的一系列设计项目和非常复杂尖端的数字系统的开发和应用。

Altera 公司为DE2 板提供了一套支持文件,例如学习指导,现成的教学实验练习和丰富的插图说明。

DE2 的特点DE2 板是以CycloneII 2C35FPGA为特点的672 针引脚的包装。

板上所有重要的部件都与板上的芯片相连,使用户能够控制板上各种的操作。

DE2 板包括了很多开关(兼有拨动开关和按键),发光二极管和七段数码管。

在更多进一步的实验中还用到了SRAM,SDRAM,Flash以及16×2的字符液晶。

需要进行处理器和I/O接口试验时,可以简单的用Altera NiosII处理器和象RS-232和PS/2标准接口。

进行涉及音频和视频的实验时,也有标准MIC、line-in、line-out接口(24位音频解编码器),video-in(TV Decoder)和VGA(10-bit DAC),这些特点都能够被用来制作CD质量的音频应用程序和专业的视频图象。

为了能够设计更强大的项目,DE2 还提供了USB2.0 接口(包括主、从USB),10/100M自适应以太网,红外(IRDA)接口,以及SD卡接口。

最后,可以通过两排扩展I/O口与其它用户自定义的板子相连。

支持材料软件拥有DE2开发板的特征的QUARTUS II网络版的CAD系统,以及NiosII嵌入式处理器,也为学生和师提供了该板的一些帮助文件,如使用说明和应用实例。

传统的FPGA 教学开发板的制造商提供了大量的的硬件和软件CAD工具支持,但极少提供直接面向教学目的的帮助文件。

但Altera 公司的DE2 板别树一帜,除了DE2 板的硬件和软件外,Aletra 公司也为一些典型的逻辑设计课程和计算机组织提供了全套的能够在实验室条件下实现的实验练习。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

. ;. 基于DE2-115开发板的FPGA入门设计实验

1、Lab1: 4位加法器、减法器的设计 1.1 摘要 在文件add_sub里面的工程文件operation_4.v为顶层文件,该顶层文件包含了三个子模块,分别为数码管显示模块,4位带进位的二进制加法器模块和4位带借位的二进制减法器模块,最后通过DE2-115开发板显示实验结果。 1.2 程序 1)add_4bits.v 加法器 module adder_4bits ( input clk, input rst_n, input [3:0] x, input [3:0] y, output reg [3:0] sum, output reg carry_out //溢出位 ); always@(posedge clk or negedge rst_n) begin if(!rst_n) . ;. {carry_out, sum} <= 0; else {carry_out, sum} = x + y; end endmodule 2)substractor_4bits.v减法器 module subtractor_4bits ( input clk, input rst_n,

input [3:0] x, input [3:0] y, output reg [3:0] sub, output reg borrow_out ); always@(posedge clk or negedge rst_n) begin if(!rst_n) {borrow_out, sub} <= 0; else begin . ;. if(x >= y) {borrow_out, sub} = {1'b0, x - y}; else {borrow_out, sub} = {1'b1, x - y}; end end endmodule 3)seg7_lut.v 数码管显示译码模块 module Seg7_lut ( input [3:0] iDIG, output reg [6:0] oSEG ); always @(iDIG) begin case(iDIG) 4'h1: oSEG = 7'b1111001; // ---t---- 4'h2: oSEG = 7'b0100100; // | | 4'h3: oSEG = 7'b0110000; // lt rt 4'h4: oSEG = 7'b0011001; // | | 4'h5: oSEG = 7'b0010010; // ---m---- 4'h6: oSEG = 7'b0000010; // | | . ;. 4'h7: oSEG = 7'b1111000; // lb rb 4'h8: oSEG = 7'b0000000; // | | 4'h9: oSEG = 7'b0011000; // ---b---- 4'ha: oSEG = 7'b0001000; 4'hb: oSEG = 7'b0000011; 4'hc: oSEG = 7'b1000110; 4'hd: oSEG = 7'b0100001; 4'he: oSEG = 7'b0000110; 4'hf: oSEG = 7'b0001110; 4'h0: oSEG = 7'b1000000; endcase end endmodule 1.3 结果 本设计通过Verilog HDL硬件描述语言。描述加法、减法算法,包括了进位以及借位,最终可以在实验板上观察结果,验证了算法的正确性。拨码开关SW[7:0]输入两位计算值,SW[17]为复位按键,如下图所示:

该实验结果显示的是7+b=02,进位位在LEDG[0]显示,.

;. 7-b=12,借位位在LEDR[0]显示。计算过程如下: .

;. 2、Lab2: 三位二进制乘法器的设计 2.1 摘要 在文件mult_3bits里面的工程文件operation_4.v为顶层文件,该顶层文件包含了两个子模块,分别为数码管显示模块和三位二进制乘法器模块,最后通过DE2-115开发板显示实验结果。 2.2 程序 1)mult_3bits.v 乘法器 module mult_3bits ( input [2:0] x, input [2:0] y, output [5:0] mult_out ); wire [2:0] temp0 = y[0] ? x : 3'd0; wire [2:0] temp1 = y[1] ? x : 3'd0; wire [2:0] temp2 = y[2] ? x : 3'd0; assign mult_out = temp0 + (temp1 << 1) + (temp2 << 2); endmodule 2)seg7_lut.v文件与Lab1中的相同 2.3 结果 本设计通过Verilog HDL硬件描述语言,通过移位以及. ;. 加法,实现三位二进制乘法功能,最终可以在实验板上观察结果,验证了算法的正确性。拨码开关SW[6:0]输入两位计算值,SW[17]为复位按键,如下图所示: .

;. 3、Lab3: 序列检测器的设计 3.1 摘要 通过Verilog HDL硬件描述语言,按照要求,设计一个序列检测器,在检测到4’b1111序列后输出高电平标志位,反之输出低电平。电路在Quartus II中设计,最后通过波形图仿真和开发板得出实验结果。 3.2 程序 sequence_detect.v 序列检测器 module sequence_detect ( input clk, input rst_n, input din_en, //H vaild input din, output reg dout ); //capture the posedge of din_en for data receive reg din_en_r0,din_en_r1; always@(posedge clk or negedge rst_n) begin if(!rst_n) begin . ;. din_en_r0 <= 0; din_en_r1 <= 0; end else begin din_en_r0 <= din_en; din_en_r1 <= din_en_r0; end end wire din_flag = (~din_en_r1 & din_en_r0) ? 1'b1 : 1'b0; //din_en的值由0变1时,din_flag的值变为高电平维持一个时钟周期(脉冲边沿检测) //din_en作为数据输入的标志 //-------------------------------------------- reg [3:0] sequence_data;//序列数据寄存器 always@(posedge clk or negedge rst_n) begin if(!rst_n) begin sequence_data <= 0;//初始化时寄存器状态 dout <= 0; //寄存器输出为0 end . ;. else if(din_flag)//din_en上升沿,din_flag=1 begin sequence_data <= {sequence_data[2:0], din}; //串行输入 dout <= (sequence_data == 4'b1111) ? 1'b1 : 1'b0; end end endmodule 3.3 结果 该程序中定义可串行输入接口:din,串行输出接口dout,同时添加了数据输入标志信号din_en,以指示数据的输入。 串行数据输入序列通过移位操作,存入与sequence_data中,同时检测sequence_data,当出现4’b1111时,dout输出1表示检测到了要求的序列。其中仿真结果如下: .

;. 4、Lab4: 变模计数器的设计 4.1 摘要 在设计一个计数器的前提下,要求模值可变,即计算器最大值可变。因此,这要求能动态改变计数器的模值,同时在数码管上实时显示输出结果。在文件variable_counter里面的工程文件variable_counter.v为顶层文件,该顶层文件包含了一个数码管显示子模块,最后通过DE2-115开发板显示实验结果。 4.2 内容 1)变模的实现 模值可以通过选择,也可以通过输入,来动态改变。在该实验中,通过一个拨码开关SW[0]来选择模值“16”或者“64”,实现选择通过一个选择语句即可实现。如下语句: wire [7:0] max_vaule = SW[0] ? 8'd64 : 8'd16; 2) 输出显示 本实验通过2个7段数码管来显示数据。同时为了肉眼能看到数据的变化,通过计数,实现0.25S的使能标志定点时间,以此标志位来作为计数器的计数周期,保证肉眼可以看得到数据的变化。 4.3 程序 1) variable_counter.v 变模计数器顶层模块 module variable_counter