fpga课程设计总结报告模版

fpga课程设计心得体会

fpga课程设计心得体会在参与FPGA(Field-Programmable Gate Array)课程设计的过程中,我深刻体会到了以下几点心得与体会。

通过对所学内容的实践与探索,我收获了宝贵的经验和知识,不仅提升了自己的技能,也对FPGA这一领域有了更深刻的理解。

1. 硬件描述语言的重要性在课程设计中,我学习并运用了硬件描述语言(HDL),如VHDL或Verilog。

这种语言使得设计者能够通过描述硬件电路的结构和行为来实现某一功能。

通过学习HDL,我了解到了硬件设计与软件开发之间的差异,理解了硬件设计的并行性和高效性。

熟练运用HDL能够简化设计过程,提高开发效率。

2. 设计流程的重要性一个良好的设计流程是FPGA课程设计的基础。

在进行实际设计之前,我学习了系统设计的基本步骤,包括需求分析、架构设计、模块分解、仿真验证等。

通过遵循设计流程,我能够更好地规划和组织我的设计工作,避免了混乱和错误。

同时,设计流程也能帮助我更好地掌握项目进展,并及时调整和改进设计方案。

3. 仿真与验证的重要性在设计过程中,仿真与验证是不可或缺的环节。

通过仿真工具,我们可以在实际硬件开发之前对设计进行全面的测试和验证。

通过仿真,我们可以发现和解决潜在的问题,优化和改进设计。

当设计与预期结果一致时,我们可以认为设计是正确的。

通过验证,我们可以杜绝设计中的错误和漏洞,提高设计的可靠性和稳定性。

4. 协同合作的意义在FPGA课程设计中,我有幸与其他同学一起合作完成了一些小组项目。

通过协同合作,我们能够充分利用每个人的优势,共同完成一个更复杂和高效的设计。

团队合作不仅能够提高设计的质量和效率,也能够培养我们的沟通与合作能力。

通过与团队成员相互交流和学习,我们可以共同解决问题,取得更好的成果。

5. 不断学习的态度FPGA技术在不断发展和演进,因此不断学习的态度对于掌握这一领域至关重要。

通过参与FPGA课程设计,我认识到自己的知识还有很多不足之处,需要不断扩充和加强。

FPGA学习总结

FPGA学习总结FPGA(现场可编程门阵列)是一种数字电路开发和实现的工具,它提供了一种灵活的方式来设计和实现各种数字电路。

在我的FPGA学习过程中,我经历了以下几个方面的学习和实践:1.FPGA基础知识:在学习FPGA之前,我首先了解了FPGA的基本概念和原理。

我学习了FPGA的架构、时序和时钟设计、数字电路设计和综合等方面的知识。

这些基础知识为我深入学习和实践FPGA打下了坚实的基础。

2. FPGA开发工具的使用:我使用了常见的FPGA开发工具,如Vivado和Quartus。

这些工具提供了一种直观而强大的方式来设计和实现FPGA。

我学习了如何创建项目、添加模块、定义信号、综合和布局布线等操作。

通过不断的实践和尝试,我逐渐掌握了这些工具的使用。

3. Verilog和VHDL的学习:Verilog和VHDL是FPGA开发中常用的硬件描述语言。

通过学习这两种语言,我能够使用它们来描述和设计各种数字电路。

我掌握了如何使用这些语言来描述寄存器、组合逻辑、状态机等部件,并能够将它们综合成FPGA可实现的电路。

4.FPGA的应用实践:在学习了FPGA的基础知识和工具使用之后,我开始进行一些实际的应用实践。

我使用FPGA设计和实现了一些简单的电路,如计数器、加法器、乘法器等。

通过实践,我加深了对FPGA的理解,并增强了自己的设计和调试能力。

5.FPGA高级特性的学习:除了基础知识和工具使用外,我还学习了一些FPGA的高级特性,如时序分析、时钟域划分、并行数据传输和高速串行数据传输等。

这些特性在设计和实现一些高性能和复杂的电路时非常重要,我通过学习和实践,学会了如何正确地使用这些特性。

总结起来,FPGA学习是一个既有理论基础又注重实践和应用的过程。

通过学习FPGA,我更好地理解了数字电路的原理和设计,增强了自己的工程能力。

我学会了使用FPGA开发工具,掌握了Verilog和VHDL等硬件描述语言,实践了FPGA的设计和实现,并学习了一些高级特性。

fpga实训报告

fpga实训报告本报告旨在总结和分享我在FPGA实训课程中的学习和实践经验。

我将介绍我在实训过程中所遇到的挑战、学到的知识以及对未来发展的展望。

1. 概述FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有灵活性和可重构性,广泛应用于嵌入式系统、数字电路设计和计算机硬件加速等领域。

在本次实训中,我们团队学习了FPGA的基本原理和使用方法,并基于Verilog语言开发了几个具体的项目。

2. 实训内容2.1 FPGA基础知识我们首先学习了FPGA的基础知识,包括FPGA的结构和工作原理、FPGA开发流程、Verilog语言基础等。

通过理论学习和实际操作,我们对FPGA的内部结构和原理有了更深入的了解。

2.2 FPGA开发工具在实训中,我们使用了主流的FPGA开发工具。

通过熟练掌握这些工具的使用,我们能够进行FPGA的设计、仿真和下载等操作,为后续的实验项目做好准备。

2.3 FPGA实验项目在实训过程中,我们完成了多个FPGA实验项目,包括数字逻辑电路设计、时序电路设计、数码管显示、LED闪烁、有限状态机设计等。

通过这些项目,我们将理论知识应用到实际场景中,提高了自己的设计能力和实践能力。

3. 实训经验和收获3.1 团队合作在实训中,我们组成了小组合作完成各项实验项目。

通过合作,我们不仅学会了协作和沟通,还互相帮助解决问题,提高了团队凝聚力和协作能力。

3.2 动手实践FPGA实训的一个重要特点是强调实践操作。

通过大量的实验练习,我们不仅掌握了基本的FPGA开发技能,还了解了FPGA在各个领域中的广泛应用,并在实践中提高了自己的问题解决能力。

3.3 创新思维在一些项目中,我们需要设计和实现独特的功能,这要求我们发挥创新思维,灵活运用所学知识。

通过这个过程,我们培养了创新意识和解决实际问题的能力。

4. 未来展望通过FPGA实训的学习和实践,我对FPGA的应用和发展前景有了更深入的认识和理解。

fpga课程设计总结

fpga课程设计总结一、教学目标本课程的教学目标是使学生掌握FPGA的基本原理、设计和应用。

具体来说,知识目标包括:了解FPGA的基本结构和工作原理;掌握FPGA的编程语言和设计方法;熟悉FPGA在数字信号处理、嵌入式系统等方面的应用。

技能目标包括:能够使用FPGA设计简单的数字系统;能够使用FPGA进行嵌入式系统设计;能够进行FPGA的编程和调试。

情感态度价值观目标包括:培养学生的创新意识和团队合作精神;使学生认识到FPGA技术在现代科技中的重要地位和应用价值。

二、教学内容根据课程目标,教学内容主要包括FPGA的基本原理、设计和应用。

具体包括以下几个方面:1. FPGA的基本结构和工作原理;2. FPGA的编程语言和设计方法;3. FPGA在数字信号处理、嵌入式系统等方面的应用;4. FPGA的设计工具和实验方法。

三、教学方法为了达到课程目标,我们将采用多种教学方法,包括讲授法、讨论法、案例分析法和实验法等。

通过这些方法,我们将引导学生从不同角度理解和掌握FPGA技术和应用。

具体来说:1. 讲授法:通过讲解FPGA的基本原理、设计和应用,使学生掌握相关知识;2. 讨论法:通过分组讨论和课堂讨论,引导学生深入思考和理解FPGA技术;3. 案例分析法:通过分析实际案例,使学生了解FPGA在实际应用中的优势和局限;4. 实验法:通过FPGA实验,使学生掌握FPGA的设计和编程方法,提高实际操作能力。

四、教学资源为了支持教学内容和教学方法的实施,我们将选择和准备以下教学资源:1. 教材:选用权威、实用的教材,为学生提供系统、全面的学习材料;2. 参考书:推荐一些与FPGA相关的参考书,拓展学生的知识视野;3. 多媒体资料:制作课件、视频等多媒体资料,提高课堂教学效果;4. 实验设备:准备FPGA实验设备,为学生提供实践操作的机会。

五、教学评估本课程的评估方式包括平时表现、作业和考试等。

平时表现主要评估学生的课堂参与、提问和讨论等情况,占总评的20%。

FPGA课程设计实验报告

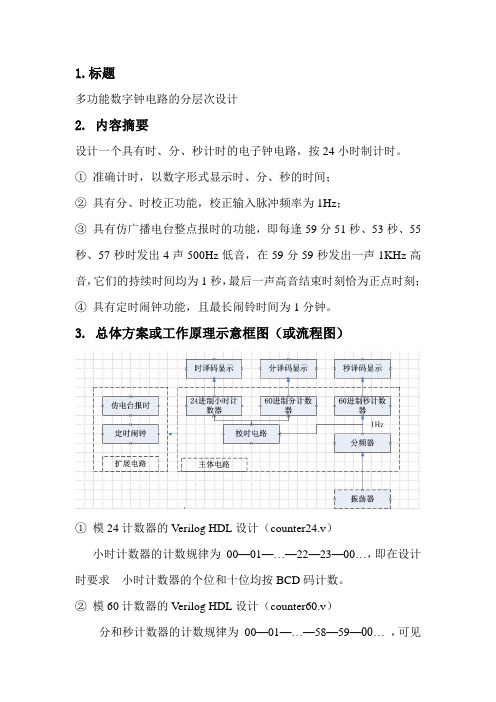

1.标题多功能数字钟电路的分层次设计2. 内容摘要设计一个具有时、分、秒计时的电子钟电路,按24小时制计时。

①准确计时,以数字形式显示时、分、秒的时间;②具有分、时校正功能,校正输入脉冲频率为1Hz;③具有仿广播电台整点报时的功能,即每逢59分51秒、53秒、55秒、57秒时发出4声500Hz低音,在59分59秒发出一声1KHz高音,它们的持续时间均为1秒,最后一声高音结束时刻恰为正点时刻;④具有定时闹钟功能,且最长闹铃时间为1分钟。

3. 总体方案或工作原理示意框图(或流程图)①模24计数器的Verilog HDL设计(counter24.v)小时计数器的计数规律为00—01—…—22—23—00…,即在设计时要求小时计数器的个位和十位均按BCD码计数。

②模60计数器的Verilog HDL设计(counter60.v)分和秒计数器的计数规律为00—01—…—58—59—00… ,可见个位计数器从0~9计数,是一个10进制计数器;十位计数器从0~5计数,是一个六进制计数器。

可以先分别设计一个十进制计数器模块(counter10.v)和一个六进制计数器模块(counter6.v),然后将这两个模块组合起来,构成六十进制计数器。

4. 顶层逻辑电路图组成及原理简单叙述仿真波形如下:分析结论:经仿真波形分析①走时正常;②能〝校时〞〝校分〞;③整点报时;④时段控制到位。

功能完全符合设计要求,可以下载。

5. 对应各模块功能仿真波形(数据分析)分析及结论1、小时计时模块:仿真波形:当小时的高四位为0、1时,小时的低四位为九时,在下一个时钟的上跳延来了之后,高四位加一;当小时的高四位为2,同时低四位为3时,小时的高低四位都清零。

实现从00到23的循环计数。

2、分钟计时模块:仿真波形:当分钟的高四位为0、1、2、3、4时,小时的低四位为九时,在下一个时钟的上跳延来了之后,高四位加一;当分钟的高四位为5时,同时低四位为9时,分钟的高低四位都清零,实现从00到59的循环计数。

FPGA课程设计报告

课程设计开课学期: 2014年—2015年下学期课程名称:FPGA课程设计学院:信息科学与工程学院专业:集成电路设计与集成系统班级:集成1201班学号:20121221077姓名:蔚任课教师:涛2015 年 7 月 21 日基于FPGA的数字钟设计摘要本文介绍一种利用现场可编程逻辑器件FPGA产生多功能数字钟的设计方案。

数字钟是采用数字电路实现对时、分、秒数字显示的计时装置,是人们日常生活中不可少的必需品。

本设计采用EDA技术,以硬件描述语言Verilog为系统逻辑描述手段设计文件,在Quartus II工具软件环境下,由各个基本模块共同构建了一个基于FPGA的数字钟。

系统由时钟模块、控制模块、计时模块、数据译码模块、显示以及报时模块组成。

经编译和仿真所设计的程序,在可编程逻辑器件上下载验证。

开发板采用5CSEMA5F31C6N。

本次设计的多功能数字钟,具有时、分、秒的数码管显示功能,以24小时循环计数,具有整点报时功能,并有由按键输入进行数字钟的校时、清零、启停功能。

关键词:可编程逻辑器件 FPGA Verilog 数字钟 EDA技术AbstractThis paper introduces a kind of based on field programmable logic device FPGA design of multi-function digital clock, the digital clock is used in digital circuits, and seconds digital display timing device is in people's daily life necessities.This design using EDA technology, hardware description language Verilog logic system description method of design documents, in the Quartus II software environment, by all the basic modules together to build a a FPGA based digital clock.System consists of the clock module, control module, time module, data decoding module, display and broadcast module composition. Program after compilation and simulation design, programmable logic device to download verification. Development board using the multi-function digital clock 5CSEMA5F31C6N. this design, with time, points, the second digital tube display, to a 24-hour cycle count, with the whole point timekeeping function and input by the key of the school of digital clock, clear, open and stop function.Key words: programmable logic device FPGA Verilog Digital cloc EDA Technology目录前言 (1)第一章多功能数字钟概述 (2)1.1 数字钟的构成 (2)1.3 计时电路 (3)1.4 异步清零电路 (4)1.5 校时、校分功能电路 (4)第二章 FPGA简介 (5)2.1 现场可编程逻辑门阵列FPGA (5)2.2 FPGA简介 (6)2.3 Quartus II软件简介 (6)第三章设计方案 (7)第四章设计实现 (9)4.1 顶层模块 (9)4.2 新建工程项目 (9)4.3 选择芯片 (10)4.4 子模块 (12)4.4.1 分频器 (12)4.4.2 控制器和计数器 (13)4.4.3 显示器 (16)4.5 元件封装 (21)4.6 引脚的绑定和设置 (21)4.7 之后再进行一次编译运行。

FPGA课程设计报告

FPGA课程设计设计任务1.基于Quartus II软件完成十进制加法计数器、分频器、数码管动态扫描显示设计;2.采用Modelsim仿真软件对上述设计进行仿真验证;3.将上述各模块按照一定的连接关系连接,使其实现功能。

一、总体设计方案设计一个led秒钟系统,8位数码管同时显示秒数,秒数一秒一动,可通过开关控制开始,暂停,置零。

二、各功能模块设计1.十进制加法计数器的设计1.1代码module adder (clk,rst_n,EN,clr,data_out);input clk,rst_n,EN,clr;output data_out;wire[3:0] data_out;reg[3:0] data_out_r;always @ (posedge clk or negedge rst_n) beginif(!rst_n) data_out_r <= 4'd0;else if(EN) beginif(clr) data_out_r <= 4'd0;else begindata_out_r = data_out_r + 1'b1;if(data_out_r == 4'd10) data_out_r = 4'd0;endendendassign data_out = data_out_r;endmodule1.2测试文件(Test Bench)`timescale 1 ns/ 1 psmodule adder_vlg_tst();reg EN;reg clk;reg clr;reg rst_n;wire [3:0] data_out;adder i1 (.EN(EN),.clk(clk),.clr(clr),.data_out(data_out),.rst_n(rst_n));initialbeginclk = 0;forever #10 clk = ~clk;endinitialbeginrst_n = 0;EN = 0;clr = 0;#20 rst_n = 1;#10 EN = 1;#20 clr = 1;#20 clr = 0;#200 $stop;endendmodule1.3 仿真波形2.分频器的设计2.1源代码module clkdiv#(parameter M = 100) //参数定义,默认为100 (input wire clk,output wire clk_div_M);localparam N = log2(M/2);//M/2值所需位数reg clk_div_r = 0;assign clk_div_M = clk_div_r;reg[N-1:0] cnt = 0; //分频计数器always @ (posedge clk)beginif(cnt == (M/2-1) )begincnt <= 0;clk_div_r = ~clk_div_r;endelse cnt <= cnt + 1'b1;end//log2 constant functionfunction integer log2(input integer n);integer i;beginlog2 = 1;for(i=0; 2**i<n; i=i+1)log2 = i+1;endendfunctionendmodule2.1测试文件(Test Bench)`timescale 1 ns/ 1 nsmodule clkdiv_vlg_tst();reg clk;wire clk_div_M;clkdiv i1 (.clk(clk),.clk_div_M(clk_div_M));Initial beginclk = 0;forever clk = ~clk;endinitial begin#100000;$stop;endendmodule2.3仿真波形3.数码管动态扫描显示设计3.2 源代码module SMG (clk,data_in,wei,duan);input wire clk;input wire[3:0] data_in;output wire[7:0] wei;output wire[7:0] duan;reg[7:0] wei_r = 8'hff;reg[7:0] duan_r = 8'hff;assign wei = wei_r;assign duan=duan_r;reg[2:0] count = 3'd0; //位选扫描信号reg[7:0] temp = 8'hff; //显示编码always @ (posedge clk) begin //位选扫描信号自加if(count == 3'b111) count <= 3'b000;else count <= count + 1'b1;endalways @ (posedge clk) begincase(count)3'd1: begin wei_r <= 8'h01; duan_r <= temp;end3'd2: begin wei_r <= 8'h02; duan_r <= temp;end3'd3: begin wei_r <= 8'h04; duan_r <= temp;end3'd4: begin wei_r <= 8'h08; duan_r <= temp;end3'd5: begin wei_r <= 8'h10; duan_r <= temp;end3'd6: begin wei_r <= 8'h20; duan_r <= temp;end3'd7: begin wei_r <= 8'h40; duan_r <= temp;end3'd8: begin wei_r <= 8'h80; duan_r <= temp;enddefault:begin wei_r <= 8'bx;duan_r <= 8'bx;endendcaseendalways @ (posedge clk) begincase(data_in)4'b0000: temp=8'b11000000; //共阳数码管显示0的段码4'b0001: temp=8'b11111001; //共阳数码管显示1的段码4'b0010: temp=8'b10100100; //4'b0011: temp=8'b10110000; //4'b0100: temp=8'b10011001; //4'b0101: temp=8'b10010010; //4'b0110: temp=8'b10000010; //4'b0111: temp=8'b11111000; //4'b1000: temp=8'b10000000; //4'b1001: temp=8'b10010000; //共阳数码管显示9的段码4'b1010: temp=8'b10001000; //共阳数码管显示A的段码4'b1011: temp=8'b10000011; //共阳数码管显示B的段码4'b1100: temp=8'b11000110; //共阳数码管显示C的段码4'b1101: temp=8'b10100001; //共阳数码管显示D的段码4'b1110: temp=8'b10000110; //共阳数码管显示E的段码4'b1111: temp=8'b10001110; //共阳数码管显示F的段码default: temp=8'hFF;endcaseendendmodule3.2测试文件(Test Bench)`timescale 1 ns/ 1 psmodule SMG_vlg_tst();reg clk;reg [3:0] data_in;wire [7:0] duan;wire [7:0] wei;SMG i1 (.clk(clk),.data_in(data_in),.duan(duan),.wei(wei));initial beginclk = 0;forever #10 clk = ~clk;endinitial begindata_in = 0;forever #40 data_in = data_in + 1'b1;#1000 $stop;endendmodule3.3 仿真波形三、设计实现1.1顶层代码module add_ten(clk_50M,rst_n,EN,clr,wei,duan);input wire clk_50M;input wire rst_n;input wire EN;input wire clr;output wire[7:0] wei;output wire[7:0] duan;wire[3:0] data_r; // data为中间变量,用于加法器-->数码管传递/***** 分频器设计例化*********/wire clk_1M,clk_1K,clk_1HZ;clkdiv #(.M(50)) //50分频--->1MHZclkdiv_1M (.clk(clk_50M),.clk_div_M(clk_1M));clkdiv #(.M(1000)) //1000分频--->1KHZ,给数码管扫描clkdiv_1000 (.clk(clk_1M),.clk_div_M(clk_1K));clkdiv #(.M(1000)) //1000分频--->1HZ,给加法计数器clkdiv_1HZ (.clk(clk_1K),.clk_div_M(clk_1HZ));/***** 加法计数器设计例化*********/adder inst(.clk(clk_1HZ),.rst_n(rst_n),.EN(EN),.clr(clr),.data_out(data_r));/***** 数码管设计例化*********/SMG SMG_1 (.clk(clk_1K), .data_in(data_r),.wei(wei),.duan(duan));endmodule1.2 RTL视图四、心得体会为期一周的FPGA课程设计结束了,自己感觉不是很顺利的完成课设。

fpga课程设计心得体会

fpga课程设计心得体会近年来,随着科技的不断进步和发展,FPGA(Field-Programmable Gate Array)技术在各个领域中得到了广泛的应用。

作为一门专业课程,FPGA课程设计向我们展示了FPGA技术的基本原理、应用场景以及设计方法。

在这门课程的学习中,我获得了许多宝贵的知识和经验,下面将结合个人心得体会进行总结。

1. 了解基本原理在FPGA课程设计中,我们首先需要了解FPGA的基本原理。

FPGA是一种可编程逻辑器件,通过可编程的门电路和可编程的内部连线,可以实现不同的逻辑功能。

通过学习FPGA的内部结构、编程语言以及设计流程,我对FPGA的工作机制有了更深入的理解。

这对于后续的设计工作非常重要,因为只有了解了基本原理,才能够更好地应用和设计。

2. 掌握设计工具FPGA课程设计中,我们使用了一些重要的设计工具,如Vivado、Quartus等。

这些工具提供了一个集成的设计环境,可以帮助我们完成设计、仿真以及综合等工作。

通过学习和使用这些工具,我能够更加高效地进行FPGA设计。

同时,在实际的操作中,我也发现不同的工具有其特点和适用场景,因此正确选择和掌握设计工具对于设计工作的顺利进行至关重要。

3. 实践项目经验FPGA课程设计充分注重实践,为我们提供了多个设计项目的机会。

通过这些项目,我能够将理论知识应用到实际中,加深对FPGA设计过程的理解。

例如,在一个数字电路的设计项目中,我需要将一个简单的逻辑电路转化为FPGA可编程的电路。

在这个过程中,我不仅学会了如何进行电路设计和仿真,还学会了如何调试和优化电路性能。

4. 学会团队合作在FPGA课程设计中,我们通常需要与同学一起完成设计项目。

这让我学会了团队合作的重要性。

团队合作不仅能够充分发挥每个成员的优势,提高工作效率,还可以相互学习和交流经验。

通过与团队成员的密切合作,我不仅学到了其他同学的设计思路和方法,也发现了自己在某些方面的不足和提升空间。

FPGA课程设计报告

F PG A课程设计报告(实现多功能数字钟)专业班级: 07通信2班******学号:************时间:2009.12.30一、标题:设计多功能数字钟控制电路二、任务书:用MAX+PLU SⅡ软件及Verilog HDL语言设计一个多功能的数字钟,包括有时、分、秒的计时,以及校时(对小时、分钟和秒能手动调整以校准时间)、正点报时(每逢整点,产生“嘀嘀嘀嘀-嘟”,4短一长的报时音)等附加功能。

三、关键词:24进制、60进制、正点报时、校时、数字钟四、总体方案:多功能数字钟控制电路框图是由三部分组成的,即秒分时控制电路、整点报时控制电路、时段控制电路。

用Verilog HDL硬件描述语言完成编译和仿真。

五、原理框图如下:↓↓↓六、Verilog HDL硬件描述语言编写的功能模块:/*秒计数器m60*/module m60(M,CP60M,CPM,RD);output [7:0]M;output CP60M;input CPM;input RD;reg [7:0]M;wire CP60M;always@(negedge RD or posedge CPM)beginif(!RD)begin M[7:0]<=0;endelsebeginif((M[7:4]==5)&&(M[3:0]==9))beginM[7:0]<=0;endelsebeginif(M[3:0]==9)beginM[3:0]<=0;if(M[7:4]==5)begin M[7:4]<=0;endelse M[7:4]<=M[7:4]+1;endelse M[3:0]<=M[3:0]+1;endendendassign CP60M=~(M[6]&M[4]&M[3]&M[0]); endmodule/*分计数器m60*/module m60(M,CP60M,CPM,RD);output [7:0]M;output CP60M;input CPM;input RD;reg [7:0]M;wire CP60M;always@(negedge RD or posedge CPM) beginif(!RD)begin M[7:0]<=0;endelsebeginif((M[7:4]==5)&&(M[3:0]==9))beginM[7:0]<=0;endelsebeginif(M[3:0]==9)beginM[3:0]<=0;if(M[7:4]==5)begin M[7:4]<=0;endelse M[7:4]<=M[7:4]+1;endelse M[3:0]<=M[3:0]+1;endendendassign CP60M=~(M[6]&M[4]&M[3]&M[0]); endmodule/*小时计数器m24*/module m24(H,CPH,RD);output [7:0]H;input CPH,RD;reg [7:0]H;always@(negedge RD or posedge CPH) beginif(!RD) H[7:0]<=0;elsebeginif((H[7:4]==2)&&(H[3:0]==3))beginH[7:0]<=0;endelsebeginif(H[3:0]==9)begin H[3:0]<=0;H[7:4]<=H[7:4]+1;endelse H[3:0]<=H[3:0]+1;endendendendmodule/*秒分时控制计数器xiaoshi2*/module xiaoshi2(CPM,CPH,CPS,CP60M,CP60S,SWM,SWH);output CPM,CPH;input SWM,SWH;input CPS,CP60S,CP60M;reg CPM,CPH;always@(SWM or SWH or CPS or CP60S or CP60M)begincase({SWM,SWH})2'b01: begin CPM<=CPS;CPH<=CP60M;end2'b10: begin CPM<=CP60S;CPH<=CPS;enddefault: begin CPM<=CP60S;CPH<=CP60M;end endcaseendendmodule/*时段控制器sdkz*/module sdkz(h,sk);input [7:0]h;output sk;reg sk;always@(h)beginif((h<=5)||(h>=19))sk<=1;elsesk<=0;endendmodule/*报时计数器baoshi*/module baoshi(m6,m4,m3,m0,s6,s4,s3,s0,dy,gy,bshi); input m6,m4,m3,m0,s6,s4,s3,s0,dy,gy;output bshi;wire bm;reg bshi;assign bm=m6&m4&m3&m3&m0&s6&s4&s0; always@(bm or s3 or dy or gy)beginif(bm&s3)bshi<=gy;else if(bm)bshi<=dy;elsebshi<=0;endendmodule七:各模块原理图及仿真波形:24进制原理图:60进制原理图:电路原理图:时段控制:报时:1、秒计数器仿真波形2、分计数器的仿真波形3、小时计数器的仿真波形4、秒分时控制电路的仿真波形5、时段控制的仿真波形6、报时器的仿真波形八、顶层文件及仿真波形顶层文件的仿真波形:九:选用ACEX1K芯片中的EP1K30TC144-3型号,对芯片管脚号的分配如下:十:课程设计结论:此次课程设计通过最终下载及编译可实现以上功能,在七段显示器上可实现秒、分计数器60进制,时计数器24进制显示,以及调节CLK1、CLK2的频率可使计数器上数字延时显示。

fpga实训报告

fpga实训报告一、引言FPGA(Field-Programmable Gate Array)是一种可编程逻辑集成电路,通过在硬件设计中使用现场可编程的逻辑门阵列,实现了对硬件电路的灵活配置和重构。

FPGA广泛应用于数字信号处理、通信系统、嵌入式系统等领域。

本篇报告将介绍我在FPGA实训过程中的学习和实践成果。

二、实训目标本次FPGA实训的主要目标是通过学习和实践,掌握FPGA的基本原理和设计流程。

具体的实训内容包括FPGA的基本结构、开发环境的搭建、逻辑电路的设计与实现等。

三、FPGA基本原理1. FPGA的结构FPGA由可编程逻辑单元(CLB)、输入/输出块(IOB)、全局时钟网络(GCLK)、可编程互连网络等构成。

可编程逻辑单元是FPGA的核心,用于实现逻辑功能;输入/输出块用于与外部系统进行数据交互;全局时钟网络用于传播时钟信号;可编程互连网络用于连接逻辑单元和输入/输出块。

2. FPGA的编程语言FPGA的设计可以使用硬件描述语言(HDL)进行开发。

常用的HDL语言有VHDL和Verilog,开发者可以根据需求选择适合的语言进行设计。

四、实训步骤1. 搭建开发环境在开始实训之前,需要搭建好FPGA的开发环境。

首先,安装相应的开发软件,并配置开发板的驱动程序。

接着,将开发板与计算机连接,并确认连接成功。

2. 设计逻辑电路在FPGA实训中,我首先根据实际需求设计了一组逻辑电路。

通过使用VHDL语言,我实现了数字信号的采样和滤波功能。

为了验证设计的正确性,我使用仿真工具进行了逻辑电路的模拟。

3. 烧写程序设计完成后,我将设计好的逻辑电路通过编译器生成可烧写文件。

然后,将可烧写文件烧写到FPGA芯片中,使其能够正确运行设计好的逻辑电路。

五、实训成果通过本次FPGA实训,我深入了解了FPGA的基本原理和设计流程,掌握了VHDL语言的使用,熟悉了FPGA开发环境的搭建和操作。

最终,我成功实现了一组逻辑电路的功能,并通过烧写程序在FPGA上进行了验证。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

成都理工大学工程技术学院

FPGA数字系统课程设计

总结报告

项目名称:基于指纹识别的考勤系统的设计

专业:2013级电子科学与技术

班级:电子科学与技术1班

成员:夏雨

吴杰帅

指导教师:何勇

评分:

年月日

目

录

1 项目计划 .............................................................................................................................................. .. (1)

1.1 方案可行性分析 (1)

1.2 项目执行计划 (2)

2 设计说明 (3)

2.1各单元模块设计原理4

2.2各单元模块设计流程5

2.3部分源程序及注解6

3 调试说明

3.1 调试方法及步骤.8

3.2 调试数据.9

4 总结 (10)

5 参考文献 (11)

6 附录 (12)

1

1.1 方案可行性分析

1.1.1 市场分析

自动温度控制器是一款适应现代生活发展的科技产品。

面对现今中央空调的

使用和普及,自动温度控制器能够有效可行的节约能源和提高生活质量,适用于各种酒店、学校、商场等大型公共场所。

其环保卫生和节约能源消耗费用的作用对各大场所都有很强吸引力。

表1-1 测试数据

(单位:V )。