计算机的并行接口大全

计算机系统接口技术-并行接口

第3讲 并行端口

Centronics打印机接口 Centronics打印机接口

硬件简单 工业标准 速度较快(相对于RS-232) 速度较快(相对于RS-232)

标准并行接口

I/O地址:0x0378,0x0278 I/O地址:0x0378, 数据(基地址+0):传送8位数据到PC和 数据(基地址+0):传送8位数据到PC和 从PC传回8位数据 PC传回8 控制(基地址+2):传送控制信号给外设 控制(基地址+2):传送控制信号给外设 状态(基地址+1):返回打印机状态 状态(基地址+1):返回打印机状态

ECP模式 ECP模式

双向高速字节传送 地址和数据 FIFO保存接收到字节或待发送字节 FIFO保存接收到字节或待发送字节

数据寄存器

D0-D7 D0PC-设备或设备-PC PC-设备或设备-

状态寄存器

bit3: nError(0-错误) nError( bit4: Select(1-在线) Select( bit5: PaperEnd(1-无纸) PaperEnd( bit6: nAck(0-回应) nAck( bit7: Busy(1-忙) Busy( bit0: 1=超时(EPP模式) 1=超时(EPP模式)

兼容模式

主机向外设送一个字节,主机与外设之间 通过Busy和nAck实现握手联络 通过Busy和nAck实现握手联络

四位组模式

4个状态端口传送一字节中的4个位,剩下 个状态端口传送一字节中的4 的状态位和数据位提供握手联络服务

字节模式

双向数据线,数据端口输入

EPP模式 EPP模式

双向高速字节传输,传送数据和地址信息 时使用不同联络信号

计算机的并行接口大全

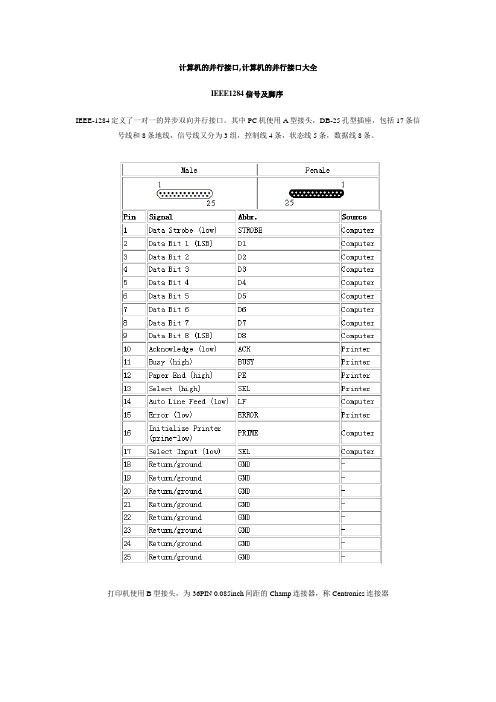

计算机的并行接口,计算机的并行接口大全IEEE1284信号及脚序IEEE-1284定义了一对一的异步双向并行接口。

其中PC机使用A型接头,DB-25孔型插座,包括17条信号线和8条地线,信号线又分为3组,控制线4条,状态线5条,数据线8条。

打印机使用B型接头,为36PIN 0.085inch间距的Champ连接器,称Centronics连接器36PIN Centronics连接器的各脚信号的含义C型:新的Mini-Centronics 36PIN连接器,0.050inch间距,既可用于主机,也可用于外设D型25针和36针Centronics的针脚定义对照:A型、B型、C型连接器的针脚定义对照:4. IEEE1284接口的对接:PC机DB-25与打印机Centronics 36PIN连接器的信号对应关系:PC机边A型(DB-25)与打印机边B 型(Centronics 36PIN)连接器的对接:PC机边A型(DB-25)与打印机边C 型(Mini-Centronics 36PIN)连接器的对接:PC机边C型(Mini-Centronics 36PIN)与打印机边B 型(Centronics 36PIN)连接器的对接:5. IEEE1284硬件接口IEEE-1284定义了2种级别的接口兼容性,Level I 用于产品不需要高速模式,但需要利用反向通道能力的场合;Level II用于长电缆和高速传输率场合。

并行接口输出的是TTL标准的逻辑电平,输入信号也要符合TTL标准。

这种特性可以使接口容易应用在电子设计中。

大部分的PC并行接口能吸收和输出12mA左右的电流,如应用时小于或大于这个值,应使用缓冲电路。

为了保持与早期的Centronics 接口兼容,使用OC(open collector)驱动器,使用上拉电阻(pull-up resisto r)标准电阻值为2.2k欧或4.7k欧。

控制线与状态线仅要求上拉电阻Rp,数据线和Strobe线还要求串联电阻Rs来匹配线路阻抗,调整串联电阻值使其与驱动器的输出阻抗之和等于45欧到55欧的线路阻抗。

第2.6并行接口

并行接口P0~P3 2.6 并行接口P0~P3

⑵ 读引脚操作和读锁存器操作 口的位结构图中可以看出, 从 P1口的位结构图中可以看出, 有两种读口的操作: 一种 口的位结构图中可以看出 有两种读口的操作: 是读引脚操作,一种是读锁存器操作。 是读引脚操作,一种是读锁存器操作。 读引脚信号时 在响应读引脚信号 在响应读引脚信号时,端口本身引脚的电平值通过缓冲器 BUF1进入内部总线。这种类型的指令,执行之前必须先将端 进入内部总线。 进入内部总线 这种类型的指令, 口锁存器置1, 点处于高电平, 口锁存器置 ,使 A点处于高电平,否则会损坏引脚,而且也 点处于高电平 否则会损坏引脚, 使信号无法读出。 使信号无法读出。 这种类型的指令有: 这种类型的指令有: MOV A,P1 , MOV direct,P1 , ;A←P1 ;direct←P1

⒈ 位结构

P0口位结构原理图见图4-1。 口位结构原理图见图 - 。 口位结构原理图见 口中一个多路开关: ⑴ P0口中一个多路开关:多路开关的输入有两个,地址/数 口中一个多路开关 多路开关的输入有两个,地址/ 据输出;输出锁存器的输出/Q。 据输出;输出锁存器的输出 。多路开关的输出用于控制输出 FET Q0的导通和截止。 多路开关的切换由内部控制信号控制。 的导通和截止。 多路开关的切换由内部控制信号控制。 的导通和截止 口的输出上拉电路(Q1)导通和截止受内部控制信号和地 ⑵ P0口的输出上拉电路 口的输出上拉电路 导通和截止受内部控制信号和地 址/数据信号共同(相“与”)来控制。 数据信号共同( 来控制。

并行接口P0~P3 2.6 并行接口P0~P3

P1.i 位作输入口用时:先向 位作输入口用时:先向P1.i 位输出高电平,使A点提升为 位输出高电平, 点提升为 高电平,此操作称为设置P1.i 为输入线。若外设输入为 时A点 为输入线。若外设输入为1时 点 高电平,此操作称为设置 为高电平, 读入总线后B点也为高电平 为高电平,由BUF1读入总线后 点也为高电平;若外设输入为 读入总线后 点也为高电平; 0时A点为低电平,由BUF1读入总线后 点也为低电平 点为低电平, 读入总线后B点也为低电平 时 点为低电平 读入总线后 点也为低电平。 ⒉ P1口的特点 口的特点 输出锁存器,输出时没有条件; 输出锁存器,输出时没有条件; 输入缓冲,输入时有条件 先置 先置1) 输入缓冲,输入时有条件(先置 ),即需要先将该口设为输 入状态; 入状态; 工作过程中无高阻悬浮状态, 工作过程中无高阻悬浮状态,也就是该口不是输入态就是 输出态。具有这种特性的口不属于“真正”的双向口, 输出态。具有这种特性的口不属于“真正”的双向口,而被称 双向口。 为“准”双向口。

并行接口

并行接口并行接口并行接口,指采用并行传输方式来传输数据的接口标准。

从最简单的一个并行数据寄存器或专用接口集成电路芯片如8255、6820等,一直至较复杂的SCSI或IDE并行接口,种类有数十种。

一个并行接口的接口特性可以从两个方面加以描述:1. 以并行方式传输的数据通道的宽度,也称接口传输的位数;2. 用于协调并行数据传输的额外接口控制线或称交互信号的特性。

数据的宽度可以从1~128位或者更宽,最常用的是8位,可通过接口一次传送8个数据位。

在计算机领域最常用的并行接口是通常所说的LPT接口。

目录概述通信原理主要特点串口与并口的区别分类IEEE1284接口连接器1.A型2.B型3.C型IEEE1284接口电缆1.性能要求2.典型电缆链式连接发展困境展开概述通信原理主要特点串口与并口的区别分类IEEE1284接口连接器1.A型2.B型3.C型IEEE1284接口电缆1.性能要求2.典型电缆链式连接发展困境展开概述通常所说的并行接口一般称为Centronics接口,也称IEEE1284,最早由Centronics Data Computer Corporation公司在20世纪60年代中期制定。

Centronics公司当初是为点阵行式打印机设计的并行接口,1981年被IBM公司采用,后来成为IBM PC计算机的标准配置。

它采用了当时已成为主流的TTL电平,每次单向并行传输1字节(8-bit)数据,速度高于当时的串行接口(每次只能传输1bit),获得广泛应用,成为打印机的接口标准。

1991年,Lexmark、 IBM、Texas instruments等公司为扩大其应用范围而与其他接口竞争,改进了Centronics接口,使它实现更高速的双向通信,以便能连接磁盘机、磁带机、光盘机、网络设备等计算机外部设备(简称外设),最终形成了IEEE1284-1994标准,全称为"Standard Signaling Method for a Bi-directional Parallel Peripheral Interface for Personal Computers",数据率从10KB/s提高到可达2MB/s(16Mbit/s)。

计算机并口

计算机并口介绍计算机并行接口,简称并口。

并口采用的是25针D形接头。

所谓“并行”,是指8位数据同时通过并行线进行传送,这样数据传送速度大大提高,但并行传送的线路长度受到限制,因为长度增加,干扰就会增加,数据也就容易出错。

目前,并行接口主要作为打印机端口等。

并口的引脚定义如下:并口中有3个可访问的寄存器:数据端口、状态端口和控制端口口偏移地址分别为:00h、01h和02h,基地址由FDC37C935的配置寄存器选定,ISA兼容的I/O地址为:378h(278h) ,379h(279h),37Ah(27Ah)。

数据端口寄存器CPU通过这个寄存器与外部设备传送并行数据。

寄存器数据在系统初始化过程中被清除。

当CPU对该寄存器进行写访问时,该寄存器在IOW#信号的上升沿处锁存CPU的写数据,然后把锁存的写数据输出到D[0:7]数据线上。

当CPU对该寄存器进行读访问时,D[O:7]数据线上的内容经并行接口缓冲(不被锁存)后送入CPU。

状态端口寄存器CPU通过这个只读寄存器输入外部设备的状态信息,当CPU对该寄存器进行读访问时,各对应状态信号线上的现行状态信息锁存于这个寄存器中并送至CPU。

状态寄存器各位如下所示。

位7锁存的是Busy输入引脚电平的反码,该位为0表示打印机为忙状态不能接受新的字符数据:为1,表示打印机已准备好接受下一字符数据。

位6锁存的是ACK#输入引脚的状态,该位为0意思是打印机已经收到个字符数据并且可以接受下一个数据了;为1意思是打印机还正在处理上一个字符数据或尚未收到数据。

位5锁存的是PE输入引脚的状态,该位为1表示打印纸已用完:为0表示还有打印纸。

位4锁存的是SLCT输入引脚的状态,该位为1表示打印机巳经联机;为0表示打印机末被主机选择。

位3锁存的是ERROR#输入引脚的状态,该位为0表示一个打印机错误巳被检测到:为0表示没有检测到错误。

控制端口寄存器并行接口对打印机输出的各控制信号是通过CPU写该寄存器来形成的,即由软件实现控制。

并行接口

外

片选 译码

RD WR CS A1 A0

读写 控制

端口B

设

片内 译码

控制口 D

可编程并行接口芯片8255A

9.2.2 8255A的引脚信号 1. D7-D0:数据总线,双向,三态。与系统 5.PA7-PA0:端口A的8个数据输入/出引脚,双 3. CS数据总线相连,用于与系统交换数据。 :片选信号引脚,输入。常与译码器输 向,三态。一个8 位数据输入或 8位 出线相连,用于使能 8255A 。 输出锁存 /缓冲器。 RD :读信号引脚,低电平有效,输入。与 RESET: 复位引脚,高电平有效,输入。与 8284 8086/8088 的RD相连。 4.Vcc: 电源引脚,输入。接 +5V电压。 相连,有效时, 8255A复位。复位时,所有 WR : 写信号引脚,低电平有效, GND :接地引脚。 寄存器清 0,端口设置为方式 0的输入状态, 5.PB 7 - 0:端口 B的8个输入/出引脚, 双向, 2. A1-A0PB :地址线,输入。与系统的低位地 输入。与 8086/8088 的 WR 即高阻态。 三态。一个数据 I/O 锁存 /相连。 缓冲器或一 址线相连,用于选择三个数据端口和控 个数据输入缓冲器。 制端口。

D0 D1 D2 D3 D4 D5 D6 D7

目 的

可编程并行接口芯片8255A

总线

可编程并行接口芯片8255A 8255A

RESET

端口A

reset

D7 ~ D0 IOR IOW A9 ~ A2 A1 A0

D7

~

D0

数据 缓冲器

端口C

PA7 ~ PA0 PC7 ~ PC0 PB7 ~ PB0 +5V GND

计算机接口大全范文

计算机接口大全范文1.串口接口(Serial Port)串口接口是一种通过串行通信传输数据的接口,它可用于连接串口设备,如调制解调器、鼠标、键盘等。

常见的串口接口有RS-232C和RS-4852.并口接口(Parallel Port)并口接口是一种通过并行通信传输数据的接口,它可用于连接打印机、扫描仪等设备。

常见的并口接口有IEEE1284B接口(Universal Serial Bus)USB接口是一种高速串行总线接口,它可以连接多种外部设备,如打印机、摄像头、移动存储设备等。

USB接口已经成为目前最为常用的接口标准。

4.PS/2接口PS/2接口是用于连接鼠标和键盘的接口,它有两种类型,分别是PS/2键盘接口和PS/2鼠标接口。

5.扩展卡接口(Expansion Card Slot)扩展卡接口是一种用于连接扩展卡的接口,扩展卡可以增加计算机的功能,如显卡、声卡等。

常见的扩展卡接口有PCI、PCI Express等。

6.显卡接口(Display Interface)显卡接口是用于连接显示器的接口,它可以传输图像信号和控制信号。

常见的显卡接口有VGA、DVI、HDMI、DisplayPort等。

7.音频接口(Audio Interface)音频接口是用于连接音频设备的接口,它可以传输音频信号。

常见的音频接口有耳机插孔、麦克风插孔、音频线接口等。

8.网卡接口(Network Interface)网卡接口是用于连接计算机与局域网或广域网的接口,它可以传输网络数据。

常见的网卡接口有以太网接口和无线网络接口。

9.存储设备接口存储设备接口是用于连接硬盘、光驱等存储设备的接口,它可以传输数据和控制信号。

常见的存储设备接口有SATA、IDE、SCSI等。

10.蓝牙接口(Bluetooth Interface)蓝牙接口是一种用于无线通信的接口,它可以连接蓝牙设备,如手机、耳机等。

蓝牙接口可以传输数据和音频信号。

以上是计算机接口的大部分种类,每一种接口都有自己的特点和应用场景。

并行接口有哪些

并行接口有哪些并行接口是计算机领域中常用的一种数据传输方式,它允许多个数据位同时传输,提高数据传输的速率和效率。

在计算机硬件中存在多种不同类型的并行接口,本文将介绍并行接口的几种常见类型。

1. 并口接口(Parallel Port)并口接口是最早出现的一种并行接口,也被称为打印机接口。

它是计算机与外部设备之间进行并行数据传输的接口,通常用于连接打印机。

并口接口一般采用DB-25接插口,支持传输8位数据,同时提供了一些控制和状态引脚。

2. SCSI接口(Small Computer System Interface)SCSI接口是一种用于连接计算机与外部设备之间的并行接口标准。

它支持多种设备类型的连接,包括磁盘驱动器、光盘驱动器、扫描仪等。

SCSI接口速度较快,同时支持多个设备的连接,并且可通过链路控制器进行设备的管理。

3. 并行ATA接口(Parallel ATA)并行ATA接口,又称为IDE(Integrated Drive Electronics)接口,是一种用于连接计算机与硬盘驱动器之间的标准接口。

该接口采用了IDE线缆进行数据传输,支持传输16位数据,并提供了控制和状态引脚。

并行ATA接口的速度较慢,并且在连接的设备数量上有限制。

4. 并行SCSI接口(Parallel SCSI)并行SCSI接口是一种用于连接计算机与外部设备之间的高性能并行接口。

它是SCSI接口的一种变体,采用了高性能并行电缆进行数据传输,支持高速数据传输和多设备连接。

并行SCSI接口通常用于连接需要较高数据传输速率的设备,如磁带机、光盘库等。

5. 并行通用串行总线(Parallel Universal Serial Bus)并行通用串行总线是一种用于连接计算机与外部设备之间的接口标准。

它是通用串行总线(USB)的一种变体,采用了并行数据传输的方式,提供了更高的数据传输速率。

并行通用串行总线可以同时传输多个数据位,支持高速数据传输和多设备连接。

第9章(并行接口)

8255A可编程并行接口

并行接口的应用范围—— 各种外部设备(显示器、键盘、打印机、 硬盘、CD-ROM、扫描仪等)的接口电路都配有 并行接口电路,各种驱动控制(电机、数据采 集、数字和模拟开关等)也都用到并行接口。

8255A简介—— 是Intel系列的可编程通用并行接口电路,具 有2个8位输入/输出端口(A口、B口)和2个4位(C口 高/低4位)输入/输出端口;芯片为40脚双列直插 式大规模集成电路,使用+5V电源,专为Intel系 列微处理器设计,不需要附加外部电路,即可与 Intel系列微处理器及外部设备直接连接。

MOV DX, 2A8H OUT DX, AL MOV AL, 00001110B ;使PC7=0,即 ;设置STROBE=0 MOV DX,2ABH OUT DX, AL INC SI LOOP AGAIN JMP $ CODE ENDS END START

例4 8255A方式1中断应用: 8255A做打印机接口。处理器以中断方式控制输出数据到打印机: 8255A将数据输出后,自动产生OBF(低有效)至打印机的STROBE脚, 启动打印机,打印机用此信号将数据锁存,同时发出BUSY信号取反后 给8255A的ACK,表示正在打印,当打印完成,则将BUSY信号变低, ACK变高,此时若8255内部的INTE=1,则产生中断请求信号INTR。 硬件电路:

PC3

中断允许触发器中断请求信源自 请求CPU接收数据端口B方式1作输入:

PB7~PB0

INTEB

数据选通信号 表示外设已经准备好数据 STBB

PC2 PC1

IBFB

输入缓冲器满信号 表示A口已经接收数据 INTRB

PC0

中断允许触发器

中断请求信号 请求CPU接收数据

最全的计算机串口和并口介绍

计算机中的串口和并口COM是串口的意思而LPT(不是LTP)是并口的意思,串口是计算机总线提供的用于数据传输的一个端口,在串口中数据是按位成流传输的,而LPT是传输的另一种端口,在这里一般是按字节成流传输,也就是说串口好比每位排队排一排传输,并口是8位并排排一起传输,虽然感觉LPT这样是串口的8倍,但是由于波特率的原因,所以串口不一定比并口慢,波特率是指每秒传输多少位数据,这里的波特是bit,而不是BYTE(1BYTE=7bit+1bit校验),如果存在这样一个串口它的波特率是100bit/s而1个并口它的珀特率是80bit/s这说明这个串口1秒传100bit,每次传1个,并口传80bit每秒,传10次就可以了但是10次的时间是1秒.为什么会慢,是因为串口实现简单,相同设备下串口可以达到更高的理论传输平率串行接口串行接口,简称串口,也就是COM接口,是采用串行通信协议的扩展接口。

串口的出现是在1980年前后,数据传输率是115kbps~230kbps,串口一般用来连接鼠标和外置Modem以及老式摄像头和写字板等设备,目前部分新主板已开始取消该接口。

并行接口并行接口,简称并口,也就是LPT接口,是采用并行通信协议的扩展接口。

并口的数据传输率比串口快8倍,标准并口的数据传输率为1Mbps,一般用来连接打印机、扫描仪等。

所以并口又被称为打印口。

另外,串口和并口都能通过直接电缆连接的方式实现双机互连,在此方式下数据只能低速传输。

多年来PC的串口与并口的功能和结构并没有什么变化。

在使用串并口时,原则上每一个外设必须插在一个接口上,如果所有的接口均被用上了就只能通过添加插卡来追加接口。

串、并口不仅速度有限,而且在使用上很不方便,例如不支持热插拔等。

随着USB接口的普及,目前都已经很少使用了,而且随着BTX规范的推广,是必然会被淘汰的。

计算机上有串口和并口的地方应该有:硬盘、主板、还有打印机等。

串口一般用于接一些特殊的外接设备。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机的并行接口,计算机的并行接口大全IEEE1284信号及脚序IEEE-1284定义了一对一的异步双向并行接口。

其中PC机使用A型接头,DB-25孔型插座,包括17条信号线和8条地线,信号线又分为3组,控制线4条,状态线5条,数据线8条。

打印机使用B型接头,为36PIN 0.085inch间距的Champ连接器,称Centronics连接器36PIN Centronics连接器的各脚信号的含义C型:新的Mini-Centronics 36PIN连接器,0.050inch间距,既可用于主机,也可用于外设D型25针和36针Centronics的针脚定义对照:A型、B型、C型连接器的针脚定义对照:4. IEEE1284接口的对接:PC机DB-25与打印机Centronics 36PIN连接器的信号对应关系:PC机边A型(DB-25)与打印机边B 型(Centronics 36PIN)连接器的对接:PC机边A型(DB-25)与打印机边C 型(Mini-Centronics 36PIN)连接器的对接:PC机边C型(Mini-Centronics 36PIN)与打印机边B 型(Centronics 36PIN)连接器的对接:5. IEEE1284硬件接口IEEE-1284定义了2种级别的接口兼容性,Level I 用于产品不需要高速模式,但需要利用反向通道能力的场合;Level II用于长电缆和高速传输率场合。

并行接口输出的是TTL标准的逻辑电平,输入信号也要符合TTL标准。

这种特性可以使接口容易应用在电子设计中。

大部分的PC并行接口能吸收和输出12mA左右的电流,如应用时小于或大于这个值,应使用缓冲电路。

为了保持与早期的Centronics 接口兼容,使用OC(open collector)驱动器,使用上拉电阻(pull-up resist or)标准电阻值为2.2k欧或4.7k欧。

控制线与状态线仅要求上拉电阻Rp,数据线和Strobe线还要求串联电阻Rs来匹配线路阻抗,调整串联电阻值使其与驱动器的输出阻抗之和等于45欧到55欧的线路阻抗。

比如驱动IC输出阻抗为15欧,则需要33欧的串联电阻。

IEEE-1284接口芯片:因为最小输出驱动电压为2.4V, 标准TTL的+5V或低压TTL 的+3.3V的芯片都可以使用。

Fairchild、ST、TI公司都有类似芯片,如74ACT1284、74LVC161284、74LV161284等,还有专用的ESD芯片74F1071等。

6. IEEE1284信号规格表本文参考了以下资料,表示感谢:温正伟原载电子报的资料/Design_Connector_1284.html /ieee1284.html/1284int.htm/devzone/cda/tut/p/id/3466/系统分类:接口电路|用户分类:信号接口|标签:并行接口IEEE-1284 打印机Centronics D25 |来源:整理|点击查看原文发表评论阅读全文(2165) | 回复(0)发表于2007/12/30 1:45:502计算机的并行接口(2)2. IEEE1284定义的5种工作模式为了提高Centronics接口的性能,也要兼容过去的标准,IEEE1284定义了5种工作模式:SPP模式:Standard Parallel Port标准并行接口,也称为Compatibility mode兼容模式,Nibble模式:从PC机到外设8-bit数据线,反向4-bit数据线Byte模式:8-bit双向传输,速率在50KB/s 到150KB/s之间EPP模式:Enhanced Parallel Port增强并行接口,允许任一方向的高速字节传输ECP模式:Extended Capabilities Port扩展功能并行接口,允许PC机发送数据块符合IEEE 1284标准的并口,使用设备ID(Device identification sequence)来实现即插即用(Plug and Pl ay)配置,使并口更易于使用。

各种模式都可以使用相同的连接器和电缆连接方式,因硬件和编程方式的不同,传输速度可以从50K Bits/秒到2MB/秒不等。

2.1)SPP模式:即传统的Centronics并行接口,所以也称Centronics mode提供基本的信号,包括8-bit数据线,4条控制线(Strobe、Initialize Printer、Select Printer、Auto Feed lin e)和5条状态线(Busy、Acknowledge、Select、Paper Empty、Fault),需要三个不同的寄存器来进行数据的读写操作。

SPP模式是最基本的工作模式,异步、字节单向传输,数据率在50KB/s 到150KB/s之间。

使用AB-cable 电缆可传6米,而使用新的CC-cable 电缆可达10米。

基本的SPP 模式的时序如图:当打印机准备好接收数据,设BUSY为低,主机发出有效的数据到数据线,等待至少500ns然后发出STR OBE负脉冲持续至少500ns,有效的数据在STROBE上升沿后至少要维持500 ns 。

打印机接收数据并设BUSY有效以指示处理数据,当打印机完成数据接收,发出ACK脉冲至少500ns,然后清除BUSY以指示准备好接收下一个字节数据。

Centronics标准的握手信号略有不同,nStrobe为最小宽度大于1us的负脉冲,nAck为宽度大于5us的响应负脉冲,由于nAck信号的负脉冲较短,一般不会查询它,而是查询Busy。

主机软件通过4步来完成1字节数据通过并口的传输:1. 把有效数据写入数据寄存器2. 检查BUSY状态线,等待其无效(0)3. 写控制寄存器,使STROBE有效(0)4. 写控制寄存器,使STROBE失效(1)SPP模式要求的最小的建立时间、保持时间和脉冲宽度限制了其性能,考虑到软件的等待时间,IEEE1284最大的数据传输率为150 kbytes/s,而Centronics典型为10 kbytes/s,这对于点阵行式打印机已经足够了,但对于高速的激光打印机就显露出不足。

SPP模式下的信号定义:为操作并行口,SPP定义了寄存器,并映射到PC机的I/O空间。

寄存器包括了以并口地址为基址的3块连续的寄存器,并口地址常见为3BCH、378H和278H,其中都包括数据、状态和控制寄存器,分别对应数据、状态和控制信号线操作,通常称为数据端口、状态端口和控制端口。

打印机卡1的地址常为378H,其中数据口0378H、状态口0379H、控制口037AH;打印机卡2的地址常为278H,其中数据口0278H、状态口0279H、控制口027AH。

支持新的IEEE 1284标准的并口,使用8到16个寄存器,地址为378H or 27 8H,即插即用(Plug and Play)兼容的的并口适配器也可以重新加载。

并口的寄存器定义:数据寄存器:所占用的地址是并行接口的基地址,对应于于接口的2-9针状态寄存器:占用的地址是基地址加1,对应于接口的10,11,12,13,15针,是只读寄存器,其中包含一个I RQ中断位(由Ack相反后形成),当有中断发生这个数据位为“0”。

Bit7(引脚11)在输入+5V电平时,数据值为”0”,有反转的特性。

控制寄存器:占用的地址是基地址加2,对应于接口的1,14,16,17针,其中Bit0,Bit1,Bit3有反转的特性。

Bit4为IRQ应用,当向Bit4写入“1”时,将使ACK(引脚10)信号反相后成为中断请求IRQ信号,通常为IRQ5或IRQ7。

并口使用的3BCH、378H和278H三个基地址几乎都支持SPP、ECP和EPP模式(3BCH这个地址在早期的并口打印机适配器上不支持EPP和ECP模式)。

三个不同基地址的地址段如下:一些集成的1284 I/O控制器使用FIFO buffer传输数据称为Fast Centronics或Parallel Port FIFO Mode,也使用SPP协议,但用硬件产生strobe信号来实现控制信号握手,使数据率能超过500KB/s。

然而,这不是IEEE 1284定义的标准模式。

2.2)Nibble模式:用于从打印机或外部设备得到反向数据的常用方式,Nibble模式利用4条状态线把数据从外设传回电脑。

标准的并行口提供5条外设到PC机的信号线,用于指示外设的状态,利用这些信号线,外设可以分2次发送1字节(8-bit)数据,每次发半字节(nibble:4-bit)信息。

因为nACK信号一般用来提供外设中断,所以难以把传输的nibble(半字节)信息通过状态寄存器(Stat us register)合成1字节,需要软件读状态信号并作相应操作来得到正确的字节信息。

Nibble模式的数据率为50kbps(6米电缆),使用新型10米CC-cable电缆的数据率为150 kbps。

Nibble模式的优势在于具有并口的PC机都可以执行这种方式,但只能用于反向通道为低速率的场合。

下表定义了Nibble模式的信号:下图描述了Nibble模式的基本时序Nibble模式数据传输步骤:1. 主机通过设置HostBusy为低表明可以接收数据2. 外设把第一个半字节(nibble)输出到状态线3. 外设设置PtrClk为低指示nibble数据有效4. 主机设置HostBusy为高指示接收到nibble数据,而正在处理5. 外设设置PtrClk为高应答主机6. 重复步骤1到5来接收第二个半字节(nibble)Nibble模式与SPP模式相似,需要软件通过设置和读取并口的控制信号线来实现协议。

Nibble模式与SPP 模式结合建立完整的双向通道,形成最简单的双向传输方式。

从PC机到外设8-bit数据线,反向4-bit数据线,支持单向打印机接口,提供了全速率的前向传输和半速率的反向传输,速率在50KB/s 到150KB/s之间。

2.3)Byte模式:在数据线上实现反向传输的方式Byte模式利用数据线把8-bit数据从外设传输到主机。

标准并行口的8-bit数据线只能从主机向外设单向传输,需要抑制住控制数据线的驱动器,使数据可以从打印机传到电脑。

Byte模式数据传送,一次传送一个字节,与nibble模式下需要的两数据周期不同,速度和由电脑到打印机的一样,在50KB/s 到150KB/s之间,使用新型CC-cable可在10米电缆上达到500kbps。

下表定义了Byte模式的信号:Byte模式数据传输步骤:1. 主机通过设置HostBusy为低表明可以接收数据2. 外设把第一个字节(byte)数据输出到数据线3. 外设设置PtrClk为低指示byte数据有效4. 主机设置HostBusy为高指示接收到byte数据,而正在处理5. 外设设置PtrClk为高应答主机6. 重复步骤1到5来接收其他字节(byte)数据下图描述了Byte模式的基本时序制造商首先在IBM PS/2并口上增加了对8-bit数据线的读取能力,实现Byte模式,使之成为双向口,称为扩展并口的Type 1。