AD8619ARUZ-REEL中文资料

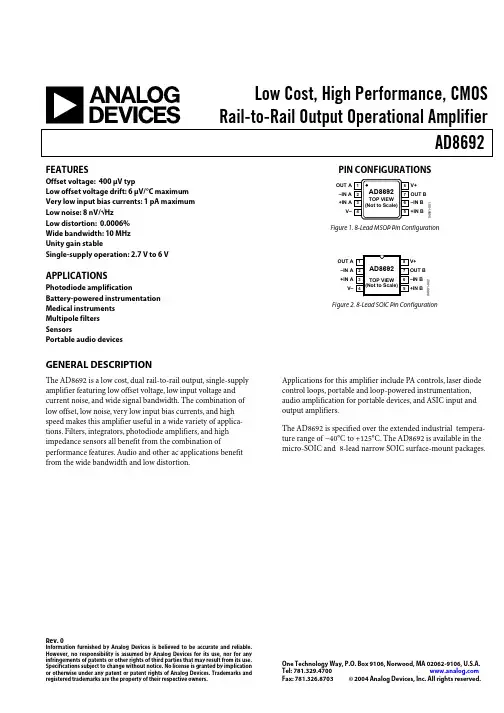

AD8692ARMZ-REEL中文资料

Supply Current/Amplifier

DYNAMIC PERFORMANCE Slew Rate Settling Time Gain Bandwidth Product Phase Margin Total Harmonic Distortion + Noise

Applications for this amplifier include PA controls, laser diode control loops, portable and loop-powered instrumentation, audio amplification for portable devices, and ASIC input and output amplifiers.

REVISION HISTORY 10/04—Revision 0: Initial Version

Typical Performance Characteristics ..............................................6 Outline Dimensions ....................................................................... 11

Conditions

VCM = −0.3 V to +1.6 V VCM = −0.1 V to +1.6 V; −40°C < TA < +125°C

AD9860资料

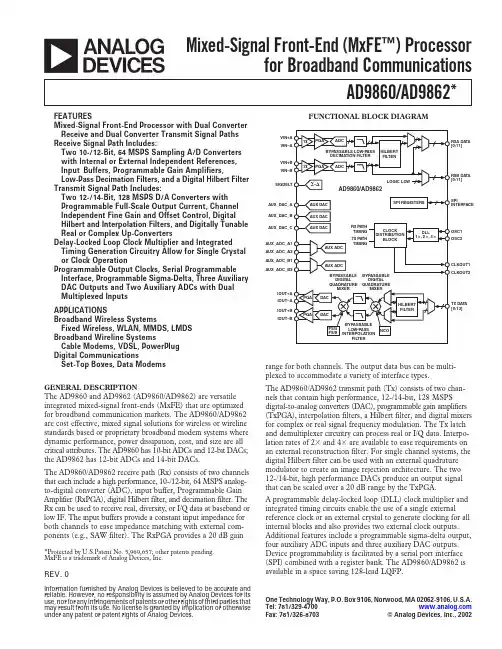

REV.0aInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/ Fax: 781/326-8703© Analog Devices, Inc., 2002AD9860/AD9862*Mixed-Signal Front-End (MxFE ™) Processorfor Broadband Communications*Protected by U.S.Patent No. 5,969,657; other patents pending.MxFE is a trademark of Analog Devices, Inc.GENERAL DESCRIPTIONThe AD9860 and AD9862 (AD9860/AD9862) are versatile integrated mixed-signal front-ends (MxFE) that are optimized for broadband communication markets. The AD9860/AD9862are cost effective, mixed signal solutions for wireless or wireline standards based or proprietary broadband modem systems where dynamic performance, power dissipation, cost, and size are all critical attributes. The AD9860 has 10-bit ADCs and 12-bit DACs;the AD9862 has 12-bit ADCs and 14-bit DACs.The AD9860/AD9862 receive path (Rx) consists of two channels that each include a high performance, 10-/12-bit, 64 MSPS analog-to-digital converter (ADC), input buffer, Programmable Gain Amplifier (RxPGA), digital Hilbert filter, and decimation filter. The Rx can be used to receive real, diversity, or I/Q data at baseband or low IF. The input buffers provide a constant input impedance for both channels to ease impedance matching with external com-ponents (e.g., SAW filter). The RxPGA provides a 20dB gainrange for both channels. The output data bus can be multi-plexed to accommodate a variety of interface types.The AD9860/AD9862 transmit path (Tx) consists of two chan-nels that contain high performance, 12-/14-bit, 128 MSPS digital-to-analog converters (DAC), programmable gain amplifiers (TxPGA), interpolation filters, a Hilbert filter, and digital mixers for complex or real signal frequency modulation. The Tx latch and demultiplexer circuitry can process real or I/Q data. Interpo-lation rates of 2ϫ and 4ϫ are available to ease requirements on an external reconstruction filter. For single channel systems, the digital Hilbert filter can be used with an external quadrature modulator to create an image rejection architecture. The two 12-/14-bit, high performance DACs produce an output signal that can be scaled over a 20 dB range by the TxPGA.A programmable delay-locked loop (DLL) clock multiplier and integrated timing circuits enable the use of a single external reference clock or an external crystal to generate clocking for all internal blocks and also provides two external clock outputs.Additional features include a programmable sigma-delta output,four auxiliary ADC inputs and three auxiliary DAC outputs.Device programmability is facilitated by a serial port interface (SPI) combined with a register bank. The AD9860/AD9862 is available in a space saving 128-lead LQFP.FUNCTIONAL BLOCK DIAGRAMTx DA T A [0:13]SIGDEL T A T A FEATURESMixed-Signal Front-End Processor with Dual Converter Receive and Dual Converter Transmit Signal Paths Receive Signal Path Includes:Two 10-/12-Bit, 64 MSPS Sampling A/D Converters with Internal or External Independent References,Input Buffers, Programmable Gain Amplifiers,Low-Pass Decimation Filters, and a Digital Hilbert Filter Transmit Signal Path Includes:Two 12-/14-Bit, 128 MSPS D/A Converters with Programmable Full-Scale Output Current, Channel Independent Fine Gain and Offset Control, Digital Hilbert and Interpolation Filters, and Digitally Tunable Real or Complex Up-ConvertersDelay-Locked Loop Clock Multiplier and Integrated Timing Generation Circuitry Allow for Single Crystal or Clock OperationProgrammable Output Clocks, Serial Programmable Interface, Programmable Sigma-Delta, Three Auxiliary DAC Outputs and Two Auxiliary ADCs with Dual Multiplexed InputsAPPLICATIONSBroadband Wireless SystemsFixed Wireless, WLAN, MMDS, LMDS Broadband Wireline SystemsCable Modems, VDSL, PowerPlug Digital CommunicationsSet-Top Boxes, Data ModemsAD9860/AD9862–SPECIFICATIONS(V A = 3.3 V ؎ 5%, V D = 3.3 V ؎ 10%, f DAC = 128 MHz, f ADC = 64 MHzNormal Timing Mode, 2؋ DLL Setting, R SET = 4 k⍀, 50 ⍀ DAC Load,–2–REV. 0AD9860/AD9862–3–Test AD9860/AD9862Rx PARAMETERS (continued)Temp Level Min Typ Max Unit DC ACCURACYDifferential Nonlinearity25ºC III±0.3/±0.4LSB Integral Nonlinearity25ºC III±1.2/±5LSB Offset Error25ºC III±0.1%FSR Gain Error25ºC III±0.2%FSR Aperture Delay25ºC III 2.0ns Aperture Uncertainty (Jitter)25ºC III 1.2ps rms Input Referred Noise25ºC III 250µV Reference Voltage ErrorREFT-REFB Error (1 V)25ºC I±1±4mV AD9860 DYNAMIC PERFORMANCE (A IN = –0.5 dBFS, f = 5 MHz)Signal-to-Noise Ratio25∞C I59.0 60.66dBc Signal-to-Noise and Distortion Ratio25∞C I56.0 58.0dBc Total Harmonic Distortion25∞C I–76.5–70.5dBc Spurious Free Dynamic Range25∞C I70.3 81.0dBc AD9862 DYNAMIC PERFORMANCE (A IN = –0.5 dBFS, f = 5 MHz)Signal-to-Noise Ratio25∞C I62.6 64.2dBc Signal-to-Noise and Distortion Ratio25∞C I62.5 64.14dBc Total Harmonic Distortion25∞C I–79.22–73.2dBc Spurious Free Dynamic Range25∞C I77.09 85.13dBc CHANNEL-TO-CHANNEL ISOLATIONTx-to-Rx (A OUT = 0 dBFS, f OUT = 7 MHz)25ºC III >90dB Rx Channel Crosstalk (f1 = 6 MHz, f2 = 9 MHz)25ºC III >80dB PARAMETERSCMOS LOGIC INPUTSLogic “1” Voltage, V IH25ºC II DRVDD – 0.7V Logic “0” Voltage, V IL25ºC II0.4V Logic “1” Current25ºC II12µA Logic “0” Current25ºC II12µA Input Capacitance25ºC III 3pF CMOS LOGIC OUTPUTS (1 mA Load)Logic “1” Voltage, V OH25ºC II DRVDD – 0.6V Logic “0” Voltage, V OL25ºC II0.4V POWER SUPPLYAnalog Supply CurrentsTx (Both Channels, 20 mA FS Output)25ºC I 7076mA Tx Powered Down25ºC I 2.5 5.0mA Rx (Both Channels, Input Buffer Enabled)25ºC I 275307mA Rx (Both Channels, Input Buffer Disabled)25ºC III 245mA Rx (32 MSPS, Low Power Mode, Buffer Disabled)25ºC III 155mA Rx (16 MSPS, Low Power Mode, Buffer Disabled)25ºC III 80mA Rx Path Powered Down25ºC I 5.0 6.0mA DLL25ºC III 12mA Digital Supply CurrentAD9860 Both Rx and Tx Path (All Channels Enabled)2ϫ Interpolation, f DAC = f ADC = 64 MSPS25ºC I 92112mA AD9862 Both Rx and Tx Path (All Channels Enabled)2ϫ Interpolation, f DAC = f ADC = 64 MSPS25ºC I 104124mA Tx Path (f DAC = 128 MSPS)Processing Blocks Disabled25ºC III 45mA 4ϫ Interpolation25ºC III 90mA 4ϫ Interpolation, Coarse Modulation25ºC III 110mA 4ϫ Interpolation, Fine Modulation25ºC III 110mA 4ϫ Interpolation, Coarse and Fine Modulation25ºC III 130mAREV. 0REV. 0–4–AD9860/AD9862Test AD9860/AD9862(20 pF Load)Temp Level Min Typ MaxUnit Minimum Reset Pulsewidth Low (t RL )NA NA 5Clock Cycles Digital Output Rise/Fall Time 25ºC III 2.84ns DLL Output Clock25ºC III 32128MHz DLL Output Duty Cycle25ºC III 50%Tx –/Rx –Interface (See Figures 11 and 12)TxSYNC/TxIQ Setup Time (t Tx1, t Tx3)25ºC III 3ns TxSYNC/TxIQ Hold Time (t Tx2, t Tx4)25ºC III 3ns RxSYNC/RxIQ/IF to Valid Time(t Rx1, t Rx3)25ºC III 5.2ns RxSYNC/RxIQ/IF Hold Time (t Rx2, t Rx4)25ºC III 0.2ns Serial Control Bus (See Figures 1 and 2)Maximum SCLK Frequency (f SCLK )Full III 16MHz Minimum Clock Pulsewidth High (t HI )Full III 30ns Minimum Clock Pulsewidth Low (t LOW )Full III 30ns Maximum Clock Rise/Fall TimeFull III 1ms Minimum Data/SEN Setup Time (t S )Full III 25ns Minimum SEN/Data Hold Time (t H )Full III 0ns Minimum Data/SCLK Setup Time (t DS )Full III 25ns Minimum Data Hold Time (t DH )Full III 0ns Output Data Valid/SCLK Time (t DV )Full III 30ns AUXILARY ADC Conversion Rate 25ºC III 1.25MHz Input Range 25ºC III 3V Resolution 25ºC III 10Bits AUXILARY DAC Settling Time 25ºC III 8m s Output Range 25ºC III 3V Resolution25ºC III 8Bits ADC TIMINGLatency (All Digital Processing Blocks Disabled)25ºC III 7Cycles DAC TimingLatency (All Digital Processing Blocks Disabled)25ºC III 3Cycles Latency (2ϫ Interpolation Enabled)25ºC III 30Cycles Latency (4ϫ Interpolation Enabled)25ºC III 72Cycles Additional Latency (Hilbert Filter Enabled)25ºC III 36Cycles Additional Latency (Coarse Modulation Enabled)25ºC III 5Cycles Additional Latency (Fine Modulation Enabled)25ºC III 8Cycles Output Settling Time (TST) (to 0.1%)25ºCIII35nsSpecifications subject to change without notice.TIMING CHARACTERISTICSTest AD9860/AD9862PARAMETERS (continued)TempLevelMinTyp MaxUnitPOWER SUPPLY (continued)Rx Path (f ADC = 64 MSPS)Processing Blocks Disabled 25ºCIII 9mA Decimation Filter Enabled 25ºC III 15mA Hilbert Filter Enabled25ºC III 16mA Hilbert and Decimation Filter Enabled25ºC III 18.5mANOTES 1% f DATA refers to the input data rate of the digital block.2Interpolation filter stop band is defined by image suppression of 50 dB or greater.Specifications subject to change without notice.REV. 0AD9860/AD9862–5–CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9860/AD9862 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions arerecommended to avoid performance degradation or loss of functionality.ABSOLUTE MAXIMUM RATINGS 1Power Supply (V AS , V DS ) . . . . . . . . . . . . . . . . . . . . . . . . .3.9 V Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . . .5 mA Digital Inputs . . . . . . . . . . . . . . . .–0.3 V to DRVDD + 0.3 V Analog Inputs . . . . . . . . . . . . . .–0.3 V to AVDD (IQ) + 0.3 V Operating Temperature 2 . . . . . . . . . . . . . . . . .–40؇C to +70؇C Maximum Junction Temperature . . . . . . . . . . . . . . . . .150؇C Storage Temperature . . . . . . . . . . . . . . . . . . .–65؇C to +150؇C Lead Temperature (Soldering 10 sec) . . . . . . . . . . . . . .300؇CNOTES 1Absolute maximum ratings are limiting values, to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability under any of these conditions is not necessarily implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.2The AD9860/AD9862 have been characterized to operate over the industrial temperature range (–40؇C to +85؇C) when operated in Half Duplex Mode.EXPLANATION OF TEST LEVELSI.Devices are 100% production tested at 25ºC and guaranteed by design and characterization testing for the extended industrial temperature range (–40ºC to +70ºC).II.Parameter is guaranteed by design and/or characterization testing.III.Parameter is a typical value only.NA.Test level definition is not applicable.THERMAL CHARACTERISTICS Thermal Resistance128-Lead LQFP JA = 29ºC/WORDERING GUIDEModel Temperature Range Package DescriptionPackage Option AD9860BST –40∞C to +70∞C *128-Lead Low Profile Plastic Quad Flatpack (LQFP) ST-128B AD9862BST –40∞C to +70∞C *128-Lead Low Profile Plastic Quad Flatpack (LQFP) ST-128BAD9860PCB Evaluation Board with AD9860AD9862PCBEvaluation Board with AD9862*The AD9860/AD9862 have been characterized to operate over the industrial temperature range (–40؇C to +85؇C) when operated in Half Duplex Mode.REV. 0–6–AD9860/AD9862PIN CONFIGURATIONAGND AVDD DVDD DGND DGND DVDD Tx11/13 (MSB)Tx10/12T x 9/1T x 8/1T x 7/T x 6/T x 5/T x 4/T x 3/T x 2/T x 1/T x 0/N C /T x N C /T x AUX_ADC_A1AGND AVDD AVDD SIGDEL T AUX_DAC_A AUX_DAC_B AUX_DAC_CAGNDDLL_Lock AGND NC AVDD OSC1OSC2AGND CLKSEL AVDD AGND AVDD REFIO FSADJ AVDD AGND IOUT–A IOUT+A AGND AGND IOUT+B IOUT–B T x S Y N D G N D V D S C L S D S D I S E D G N D V D D G N D V D M O D E /T x B L A N R E S E T C L K O U T A G N DA V D DA V D DA G N DV I N +BV I N –BA G N DA G N DV R E FA G N DA G N DV I N –AV I N +AA G N DA V D DA V D DA G N DR E F B _AR E F T _AA G N DA V D DA V D DA U X _A D C _B 2A U X _A D C _B 1A U X _A D C _R E FA U X _A D C _A 2NC = NO CONNECTAD9860/AD9862–7–Pin No.Mnemonic FunctionClock Pins10DLL_Lock DLL Lock Indicator Pin11, 16AGND DLL Analog Ground Pins12NC No Connect13AVDD DLL Analog Supply Pin14OSC1Single Ended Input Clock(or Crystal Oscillator Input)15OSC2Crystal Oscillator Input17CLKSEL Controls CLKOUT1 Rate64CLKOUT2Clock Output Generated from InputClock (DLL Multiplier Settingand CLKOUT2 Divide Factor)65CLKOUT1Clock Output Generated fromInput Clock (1ϫ if CLKSEL = 1or /2 if CLKSEL = 0)Various Pins1AUX_ADC_A1Auxiliary ADC A Input 13, 4, 13AVDD Analog Power Pins2, 9AGND Analog Ground Pins5SIGDELT Digital Output fromProgrammable Sigma-Delta6AUX_DAC_A Auxiliary DAC A Output7AUX_DAC_B Auxiliary DAC B Output8AUX_DAC_C Auxiliary DAC C Output33, 36, 53,DVDD Digital Power Supply Pin59, 61, 66,9334, 35, 52,DGND Digital Ground Pin58, 60, 67,9454SCLK Serial Bus Clock Input55SDO Serial Bus Data Bit56SDIO Serial Bus Data Bit57SEN Serial Bus Enable63RESETB Reset (SPI Registers and Logic) 95AUX_SPI_do Optional Auxiliary ADC Serial BusData Out Bit96AUX_SPI_clk Optional Auxiliary ADC Serial BusData Out Latch Clock97AUX_SPI_csb Optional Auxiliary ADC Serial BusChip Select Bit128AUX_ADC_A2Auxiliary ADC A Input 2126AUX_ADC_B1Auxiliary ADC B Input 1125AUX_ADC_B2Auxiliary ADC B Input 2127AUX_ADC_REF Auxiliary ADC ReferencePin No.Mnemonic FunctionReceive Pins68/70–79D0A to10-/12-Bit ADC Output ofD9A/D11A Receive Channel A80/82–91D0B to10-/12-Bit ADC Output ofD9B/D11B Receive Channel B92RxSYNC Synchronization Clock forChannel A and Channel B Rx Paths98, 99,AVDD Analog Supply Pins104, 105,117, 118,123, 124,100, 103,AGND Analog Ground Pins106, 109,110, 112,113, 116,119, 122,101REFT_B Top Reference Decoupling forChannel B ADC102REFB_B Bottom Reference Decouplingfor Channel B ADC107VIN+B Receive Channel B Differential (+) Input108VIN–B Receive Channel B Differential (؊) Input111VREF Internal ADC Voltage Reference114VIN–A Receive Channel A Differential (؊) Input115VIN+A Receive Channel A Differential (+) Input120REFB_A Bottom Reference Decoupling forChannel A ADC121REFT_A Top Reference Decoupling forChannel A ADCTransmit Pins18, 20AVDD Analog Supply Pins23, 3219, 24,AGND Analog Ground Pins27, 28, 3121REFIO Reference Output, 1.2 V Nominal22FSADJ Full-Scale Current Adjust25IOUT–A Transmit Channel A DACDifferential (؊) Output26IOUT+A Transmit Channel A DACDifferential (+) Output29IOUT+B Transmit Channel B DACDifferential (+) Output30IOUT–B Transmit Channel B DACDifferential (؊) Output37–48/50Tx11/Tx1312-/14-Bit Transmit DAC Datato Tx0(Interleaved Data when Required)51TxSYNC Synchronization Input for Transmitter62MODE/Configures Default Timing Mode,TxBLANK*Controls Tx Digital Power Down*The logic level of the Mode/TxBLANK pin at power up defines the default timingmode; a logic low configures Normal Operation, logic high configures AlternateOperation Mode.PIN FUNCTION DESCRIPTIONSREV. 0AD9860/AD9862DEFINITIONS OF SPECIFICATIONSDifferential Nonlinearity Error (DNL, No Missing Codes)An ideal converter exhibits code transitions that are exactly 1LSB apart. DNL is the deviation from this ideal value. Guaranteed no missing codes to 10-bit resolution indicate that all 1024 codes respectively, must be present over all operating ranges.Integral Nonlinearity Error (INL)Linearity error refers to the deviation of each individual code from a line drawn from “negative full scale” through “positive full scale.” The point used as “negative full scale” occurs 1/2LSB before the first code transition. “Positive full scale” is defined as a level 1 1/2 LSB beyond the last code transition. The deviation is measured from the middle of each particular code to the true straight line.Phase NoiseSingle-sideband phase noise power is specified relative to the carrier (dBc/Hz) at a given frequency offset (1 kHz) from the carrier. Phase noise can be measured directly in Single Tone Trans-mit Mode with a spectrum analyzer that supports noise marker measurements. It detects the relative power between the carrier and the offset (1 kHz) sideband noise and takes the resolution bandwidth (rbw) into account by subtracting 10 log(rbw). It also adds a correction factor that compensates for the implementation of the resolution bandwidth, log display, and detector characteristic. Output Compliance RangeThe range of allowable voltage at the output of a current-output DAC. Operation beyond the maximum compliance limits may cause either output stage saturation or breakdown, resulting in nonlinear performance.Spurious-Free Dynamic Range (SFDR)The difference, in dB, between the rms amplitude of the DAC’s output signal (or ADC’s input signal) and the peak spurious signal over the specified bandwidth (Nyquist bandwidth unless otherwise noted).Pipeline Delay (Latency)The number of clock cycles between conversion initiation and the associated output data being made available.Offset ErrorFirst transition should occur for an analog value 1/2 LSB above –full scale. Offset error is defined as the deviation of the actual transition from that point.Gain ErrorThe first code transition should occur at an analog value 1/2LSB above –full scale. The last transition should occur for an analog value 1 1/2 LSB below the nominal full scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between first and last code transitions.Aperture DelayThe aperture delay is a measure of the Sample-and-Hold Ampli-fier (SHA) performance and specifies the time delay between the rising edge of the sampling clock input to when the input signal is held for conversion.Aperture Uncertainty (Jitter)Aperture jitter is the variation in aperture delay for successivesamples and is manifested as noise on the input to the ADC.Input Referred NoiseThe rms output noise is measured using histogram techniques.The ADC output code’s standard deviation is calculated in LSB and converted to an equivalent voltage. This results in a noisefigure that can be referred directly to the input of the AD9860/ AD9862.Signal-to-Noise and Distortion (S/N+D, SINAD) RatioS/N+D is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for S/N+D is expressed in decibels.Effective Number of Bits (ENOB)For a sine wave, SINAD can be expressed in terms of the number of bits. Using the following formula:N=()SINAD dB–..176602it is possible to get a measure of performance expressed as N,the effective number of bits. Thus, effective number of bits fora device for sine wave inputs at a given input frequency can becalculated directly from its measured SINAD.Signal-to-Noise Ratio (SNR)SNR is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR isexpressed in decibels.Total Harmonic Distortion (THD)THD is the ratio of the rms sum of the first six harmoniccomponents to the rms value of the measured input signal and is expressed as a percentage or in decibels.Power Supply RejectionPower supply rejection specifies the converter’s maximum full-scale change when the supplies are varied from nominal to minimum and maximum specified voltages.Channel-to-Channel Isolation (Crosstalk)In an ideal multichannel system, the signal in one channel will not influence the signal level of another channel. The channel-to-channel isolation specification is a measure of the change that occurs to a grounded channel as a full-scale signal is applied to another channel.REV. 0–8––9–FREQUENCY – MHzTPC 1.AD9862 Tx Output 6 MHzSingle Tone; CLKIN = 32 MHz;DLL 4ϫ SettingFREQUENCY – MHzMAGNITUDE–dBm–20–4020406080100110120–60–80140TPC 4.TxDAC Generating anOFDM Signal; CLKIN = 64 MHz,DLL 2ϫ Settingf OUT – MHz5203510152530THD–dBcTPC 7.TxDAC HarmonicDistortion vs. f OUTFREQUENCY – MHzTPC 2.AD9862 Tx Output 6 MHzSingle Tone; CLKIN = 64 MHz;DLL 2ϫ SettingFREQUENCY – MHzMAGNITUDE–dBm20406080100110120140TPC 5.TxDAC Generating anOFDM Signal; CLKIN = 64 MHz,DLL 2ϫ SettingFREQUENCY– MHzSNR–dB74737271706968TPC 8.Signal-to-Noise Ratio (SNR)vs. f OUTFREQUENCY – MHzTPC 3.AD9862 Tx Output 6 MHzSingle Tone; CLKIN = 128 MHz;DLL 1ϫ SettingFREQUENCY – MHzMAGNITUDE–dBm–20–40–60–80–100–120TPC 6.Zoomed in Plot of FourNotched Carriers of OFDM Signal;CLKIN = 64 MHz, DLL 2ϫ SettingCARRIER FREQUENCY – MHz5IMD–dBc20–60–65–70–75–80–85–9010152530–50–55–95TPC 9.Two Tone Intermodulationvs. f OUT1 (f OUT2 = f OUT1 + 1 MHz)REV. 0AD9860/AD9862FFT OUTPUT – MHz5FFTMAGNITUDE–dBFS20–20–40–60–8010152530–100–120TPC 10.ADC Dual Tone FFT withBuffer Tones at 4.5 MHz and 5.5 MHzf IN – MHz52TPC 13.AD9862 Rx SINADvs. fINat 64 MSPSf IN – MHzTPC 16.AD9860 Rx SINADvs. f IN at 64 MSPSFFT OUTPUT – MHz5FFTMAGNITUDE–dBFS20–20–40–60–8010152530–100–120TPC 11.ADC Dual Tone FFT withoutBuffer Tones at 4.5 MHz and 5.5 MHzf IN – MHzSINAD–dBcTPC 14.AD9862 Rx SINADvs. f IN at 32 MSPSf IN – MHzSINAD–dBc62TPC 17.AD9860 Rx SINADvs. f IN at 32 MSPSFFT OUTPUT – MHz5FFTMAGNITUDE–dBFS20–20–40–60–8010152530–100–120TPC 12.ADC Dual Tone FFT(undersampling) without BufferTones at 69.5 MHz and 70.5 MHzf IN – MHz020050SINAD–dBc150250100300TPC 15.AD9862 Rx SINADvs. f IN at 16 MSPSf IN – MHzSINAD–dBc62TPC 18.AD9860 Rx SINADvs. f IN at 16 MSPSREV. 0–10–AD9860/AD9862INPUT FREQUENCY – MHzT H D – d B c–60–65–70–75–80–85–90–50–55–95–100TPC 19.Rx THD vs. f IN ,F ADC = 64 MSPSINPUT FREQUENCY – MHzS F D R – d B c–60–65–70–75–80–85–90–50–55–95–100TPC 22.Rx SFDR @ 64 MSPSINPUT FREQUENCY – MHzR E L A T I V E A T T E N U A T I O N – d B10–1–2–3–4–5–6TPC 25.Rx Input Attenuationf IN – MHzT H D – d B c–75–80–85–90–70–65–60–55–50TPC 20.Rx THD vs. f IN ,F ADC = 32 MSPS f IN – MHzS F D R – d B c–75–80–85–90–70–65–60–55–50–95TPC 23.Rx SFDR @ 32 MSPS f IN – MHzI N P U T I M P E D A N C E – ⍀60250240230220210200190204080100270260180280TPC 26.Rx Input Buffer Impedance vs. f INf IN – MHzT H D – d B c–75–80–85–90–70–65–60–55–50TPC 21.Rx THD vs. f IN ,F ADC = 16 MSPSf IN – MHz020050S F D R – d B c–75–80–85–90–70150250100–65–60–55–50300–95TPC 24.Rx SFDR @ 16 MSPSf ADC – MSPS04010R x A N A L O G P O W E R – m W30020010004003050205006007008007060TPC 27.Rx Analog Power ConsumptionAD9860/AD9862REGISTER MAP (0x00–0x3F)1NOTES1When writing to a register with unassigned register bit(s), a logic low must be written to the unassigned bit(s). By default, after power up or RESET, all registers are set low, except for the bits in the shaded boxes, which are set high.2DecimalAD9860/AD9862REGISTER BIT DEFINITIONSREGISTER 0: GENERALBIT 7: SDIO BiDir (Bidirectional)Default setting is low, which indicates SPI serial port uses dedi-cated input and output lines (i.e., 4-wire interface), SDIO and SDO Pins, respectively. Setting this bit high configures the serial port to use the SDIO Pin as a bidirectional data pin.BIT 6: LSB FirstDefault setting is low, which indicates MSB first SPI Port Access Mode. Setting this bit high configures the SPI port access to LSB first mode.BIT 5: Soft ResetWriting a high to this register resets all the registers to their default values and forces the DLL to relock to the input clock. The Soft Reset Bit is a one shot register and is cleared immediately after the register write is completed.REGISTER 1: Rx PWRDWNBIT 7: V REF, diff (Power-Down)Setting this bit high will power down the ADC’s differential references (i.e., REFT and REFB).BIT 6: V REF (Power-Down)Setting this register bit high will power down the ADC reference circuit (i.e., V REF).BIT 5: Rx Digital (Power-Down)Setting this bit high will power down the digital section of the receive path of the chip. Typically, any unused digital blocks are automatically powered down.BIT 4/3: Rx Channel B/Rx Channel A (Power-Down)Either ADC or both ADCs can be powered down by setting the appropriate register bit high. The entire Rx channel is powered down, including the differential references, input buffer, and the internal digital block. The bandgap reference remains active for quick recovery.BIT 2/1: Buffer B/Buffer A (Power-Down)Setting either of these bits high will power down the input buffer circuits for the respective channel. The input buffer should be powered down when bypassed. By default, these bits are low and the input buffers are enabled.BIT 0: All Rx (Power-Down)Setting this bit high powers down all circuits related to the receive path.REGISTER 2/3: Rx A/Rx BBIT 7: Bypass Buffer A/Bypass Buffer BSetting either of these bits high will bypass the respective input buf-fer circuit. When the buffer is bypassed, the input signal is routed directly to the switched capacitor SHA input of the RxPGA. When operating with buffer bypassed, it should be powered down.BIT 0–4: RxPGA A/RxPGA BThese 5-bit straight binary registers (Bit 0 is the LSB, Bit 4 is the MSB) provide control for the programmable gain amplifiers in the dual receive paths. A 0 dB to 20 dB gain range is accom-plished through a switched capacitor network with fast settling of a few clock cycles. The step size is approximately 1 dB. The register default setting is minimum gain or hex00. The maximum setting for these registers is hex14.REGISTER 4: Rx MISCBIT 2: HS (High Speed) Duty CycleSetting this bit high optimizes duty cycle of the internal ADC sampling clock. It is recommended that this bit be set high in high speed applications when clock duty cycle affects noise and distortion performance the most. This bit should be set high in conjunction with Clk Dut Enable register bit.BIT 1: Shared RefSetting this bit high forces the dual receive ADCs into a mode to share their differential references to provide superior gain matching. When this option is enabled, the REFT of Channel A and Channel B should be connected together off-chip and the REFB of both channels should be connected.BIT 0: Clk DutySetting this bit high enables an on-chip duty cycle stabilizer (DCS) circuit to generate the internal clock for the Rx block. This option is useful for adjusting for high speed input clocks with skewed duty cycle. The DCS Mode can be used with ADC sampling frequencies over 40 MHz.REGISTER 5: Rx I/F (INTERFACE)BIT 4: Three-stateSetting this bit high will force both Rx data output buses, including the RxSYNC Pin, into a three-state mode.BIT 3: Rx RetimeThe Rx path can use either of the clock outputs, CLKOUT1 or CLKOUT2, to latch the Rx output data. Since CLKOUT1 and CLKOUT2 have slight phase offsets, this provides some timing flexibility with the interface. By default, this bit is low and the Rx output latches use CLKOUT1. Setting this bit will force the Rx output latches to use CLKOUT2.BIT 2: Twos ComplementDefault data format for the Rx data is straight binary. Setting this bit high will generate two’s complement data.BIT 1: Inv RxSyncWhen the receive data is multiplexed onto one data port (i.e., Mux Mode Enabled), the RxSYNC Pin can be used to decode which channel generated the current output data at the active port. Default condition is that RxSYNC is high when Channel A is at the output and is low when Channel B is at the output. Setting this bit high reverses this synchronization.BIT 0: Mux OutSetting this bit high enables the Rx Mux Mode. Default setting is low, which is Dual Port Mode, (i.e., non Rx Mux Mode). When in Rx Mux Mode, both Rx channels share the same output data bus, pins D0A to D9A (for AD9860) or D0A to D11A (for AD9862). The other Rx output bus (pins D0B to D9B or D0B to D11B) outputs a low logic.REGISTER 6: Rx DigitalBIT 3: 2 ChannelSetting this bit low disables the Rx B output data port (pins D0B to D9B or D11B), forcing the output pins to zero. By default, the bit is high and both data paths are active.BIT 2: Keep –veThis bit selects whether the receive Hilbert filter will filter positive or negative frequencies, assuming the filter is enabled. By default this bit is low, which passes positive frequencies. Setting this bit high will configure the filter to pass negative frequencies.BIT 1: HilbertThis bit enables or disables the Hilbert filter in the receive path. By default, this bit is low, which disables the receive Hilbert filter. Setting this bit high enables the receive Hilbert filter.BIT 0: DecimateThis register enables or disables the decimation filters. By default, the register setting is low and the decimation filter is disabled.。

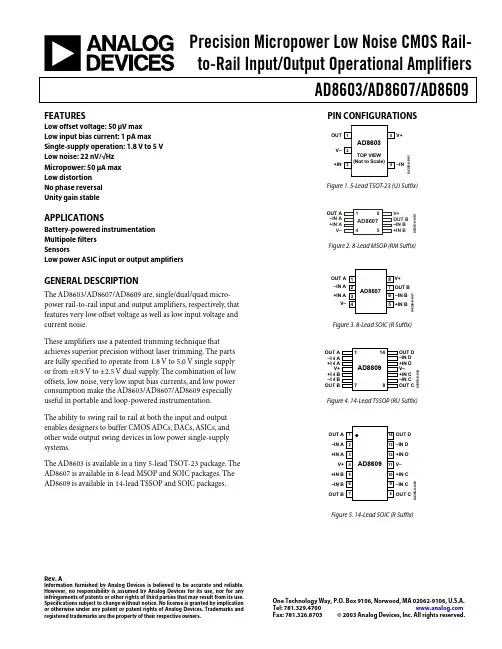

AD8607AR-REEL中文资料

–40°C < TA < +85°C –40°C < TA < +125°C

0 V < VCM < 5 V –40°C < TA < +125°C RL = 10 kΩ, 0.5 V <VO < 4.5 V

AD8607/AD8609

These amplifiers use a patented trimming technique that achieves superior precision without laser trimming. The parts are fully specified to operate from 1.8 V to 5.0 V single supply or from ±0.9 V to ±2.5 V dual supply. The combination of low offsets, low noise, very low input bias currents, and low power consumption make the AD8603/AD8607/AD8609 especially useful in portable and loop-powered instrumentation.

元器件交易网

AD8603/AD8607/AD8609

TABLE OF CONTENTS

Specifications..................................................................................... 3 Absolute Maximum Ratings............................................................ 5 Typical Performance Characteristics ............................................. 6 Applications..................................................................................... 12

AD8610ARZ-REEL资料

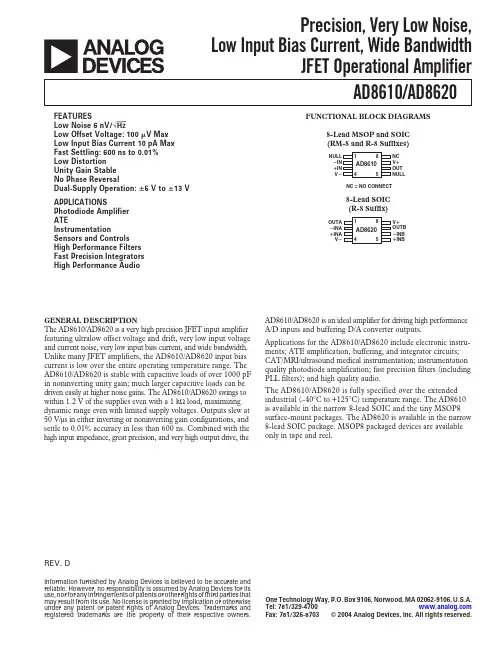

REV.DInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for itsuse, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 Fax: 781/326-8703© 2004 Analog Devices, Inc. All rights reserved.AD8610/AD8620 Precision, Very Low Noise,Low Input Bias Current, Wide BandwidthJFET Operational AmplifierFUNCTIONAL BLOCK DIAGRAMS8-Lead MSOP and SOIC(RM-8 and R-8 Suffixes)؊؉VV؉OUTNULLNCNC = NO CONNECT8-Lead SOIC(R-8 Suffix)؊؉V INB INB ؉FEATURESLow Noise 6 nV/√HzLow Offset Voltage: 100 V MaxLow Input Bias Current 10 pA Max Fast Settling: 600 ns to 0.01%Low DistortionUnity Gain StableNo Phase ReversalDual-Supply Operation: ؎5 V to ؎13 V APPLICATIONSPhotodiode AmplifierATEInstrumentationSensors and ControlsHigh Performance FiltersFast Precision IntegratorsHigh Performance AudioGENERAL DESCRIPTIONThe AD8610/AD8620 is a very high precision JFET input amplifier featuring ultralow offset voltage and drift, very low input voltage and current noise, very low input bias current, and wide bandwidth. Unlike many JFET amplifiers, the AD8610/AD8620 input bias current is low over the entire operating temperature range. The AD8610/AD8620 is stable with capacitive loads of over 1000 pF in noninverting unity gain; much larger capacitive loads can be driven easily at higher noise gains. The AD8610/AD8620 swings to within 1.2 V of the supplies even with a 1 kΩ load, maximizing dynamic range even with limited supply voltages. Outputs slew at 50 V/µs in either inverting or noninverting gain configurations, and settle to 0.01% accuracy in less than 600 ns. Combined with the high input impedance, great precision, and very high output drive, the AD8610/AD8620 is an ideal amplifier for driving high performance A/D inputs and buffering D/A converter outputs. Applications for the AD8610/AD8620 include electronic instru-ments; ATE amplification, buffering, and integrator circuits; CAT/MRI/ultrasound medical instrumentation; instrumentation quality photodiode amplification; fast precision filters (including PLL filters); and high quality audio.The AD8610/AD8620 is fully specified over the extended industrial (–40°C to +125°C) temperature range. The AD8610 is available in the narrow 8-lead SOIC and the tiny MSOP8 surface-mount packages. The AD8620 is available in the narrow 8-lead SOIC package. MSOP8 packaged devices are available only in tape and reel.元器件交易网AD8610/AD8620–SPECIFICATIONS(@ V S = ؎5.0 V, V CM = 0 V, T A = 25؇C, unless otherwise noted.) Parameter Symbol Conditions Min Typ Max Unit INPUT CHARACTERISTICSOffset Voltage (AD8610B)V OS45100µV–40°C < T A < +125°C80200µV Offset Voltage (AD8620B)V OS45150µV–40°C < T A < +125°C80300µV Offset Voltage (AD8610A/AD8620A)V OS85250µV+25°C < T A < 125°C90350µV–40°C < T A < +125°C150850µV Input Bias Current I B–10+2+10pA–40°C < T A < +85°C–250+130+250pA–40°C < T A < +125°C–2.5+1.5+2.5nA Input Offset Current I OS–10+1+10pA–40°C < T A < +85°C–75+20+75pA–40°C < T A < +125°C–150+40+150pA Input Voltage Range–2+3V Common-Mode Rejection Ratio CMRR V CM = –2.5 V to +1.5 V9095dB Large Signal Voltage Gain A VO R L = 1 kΩ, V O = –3 V to +3 V100180V/mV Offset Voltage Drift (AD8610B)∆V OS/∆T–40°C < T A < +125°C0.51µV/°C Offset Voltage Drift (AD8620B)∆V OS/∆T–40°C < T A < +125°C0.5 1.5µV/°C Offset Voltage Drift (AD8610A/AD8620A)∆V OS/∆T–40°C < T A < +125°C0.8 3.5µV/°C OUTPUT CHARACTERISTICSOutput Voltage High V OH R L = 1 kΩ, –40°C < T A < +125°C 3.84V Output Voltage Low V OL R L = 1 kΩ, –40°C < T A < +125°C–4–3.8V Output Current I OUT V OUT > ±2 V±30mA POWER SUPPLYPower Supply Rejection Ratio PSRR V S = ±5 V to ±13 V100110dB Supply Current/Amplifier I SY V O = 0 V 2.5 3.0mA–40°C < T A < +125°C 3.0 3.5mA DYNAMIC PERFORMANCESlew Rate SR R L = 2 kΩ4050V/µs Gain Bandwidth Product GBP25MHz Settling Time t S A V = +1, 4 V Step, to 0.01%350ns NOISE PERFORMANCEVoltage Noise e n p-p0.1 Hz to 10 Hz 1.8µV p-p Voltage Noise Density e n f = 1 kHz6nV/√Hz Current Noise Density i n f = 1 kHz5fA/√Hz Input Capacitance C INDifferential8pF Common-Mode15pF Channel Separation C Sf = 10 kHz137dBf = 300 kHz120dB Specifications subject to change without notice.–2–REV. DREV. D AD8610/AD8620–3–ELECTRICAL SPECIFICATIONS (@ V S= ؎13 V, VCM = 0 V, T A = 25؇C, unless otherwise noted.)ParameterSymbol Conditions Min Typ Max Unit INPUT CHARACTERISTICS Offset Voltage (AD8610B)V OS 45100µV –40°C < T A < +125°C 80200µV Offset Voltage (AD8620B)V OS 45150µV –40°C < T A < +125°C 80300µV Offset Voltage (AD8610A/AD8620A)V OS 85250µV +25°C < T A < 125°C 90350µV –40°C < T A < +125°C 150850µV Input Bias Current I B –10+3+10pA –40°C < T A < +85°C –250+130+250pA –40°C < T A < +125°C –3.5+3.5nA Input Offset CurrentI OS–10+1.5+10pA –40°C < T A < +85°C –75+20+75pA –40°C < T A < +125°C–150+40+150pA Input Voltage Range–10.5+10.5V Common-Mode Rejection Ratio CMRR V CM = –10 V to +10 V90110dB Large Signal Voltage GainA VOR L = 1 k Ω, V O = –10 V to +10 V 100200V/mV Offset Voltage Drift (AD8610B)∆V OS /∆T –40°C < T A < +125°C 0.51µV/°C Offset Voltage Drift (AD8620B)∆V OS /∆T –40°C < T A < +125°C 0.5 1.5µV/°C Offset Voltage Drift (AD8610A/AD8620A)∆V OS /∆T –40°C < T A < +125°C0.83.5µV/°COUTPUT CHARACTERISTICS Output Voltage High V OH R L = 1 k Ω, –40°C < T A < +125°C +11.75+11.84VOutput Voltage Low V OL R L = 1 k Ω, –40°C < T A < +125°C –11.84–11.75V Output CurrentI OUT V OUT > 10 V±45mA Short Circuit Current I SC ±65mA POWER SUPPLYPower Supply Rejection Ratio PSRR V S = ±5 V to ±13 V 100110dB Supply Current/Amplifier I SYV O = 0 V3.0 3.5mA –40°C < T A < +125°C 3.54.0mA DYNAMIC PERFORMANCE Slew RateSR R L = 2 k Ω4060V/µs Gain Bandwidth Product GBP 25MHz Settling Timet S A V = 1, 10 V Step, to 0.01%600ns NOISE PERFORMANCE Voltage Noisee n p-p 0.1 Hz to 10 Hz 1.8µV p-p Voltage Noise Density e nf = 1 kHz 6nV/√Hz Current Noise Density i n f = 1 kHz5fA/√Hz Input Capacitance C IN Differential 8pF Common-Mode 15pF Channel Separation C Sf = 10 kHz 137dB f = 300 kHz120dBSpecifications subject to change without notice.REV. D–4–AD8610/AD8620ORDERING GUIDETemperature Package Package ModelRangeDescription Option BrandingAD8610AR–40°C to +125°C 8-Lead SOIC RN-8AD8610AR-REEL –40°C to +125°C 8-Lead SOIC RN-8AD8610AR-REEL7–40°C to +125°C 8-Lead SOIC RN-8AD8610ARM-REEL –40°C to +125°C 8-Lead MSOP RM-8B0A AD8610ARM-R2–40°C to +125°C 8-Lead MSOP RM-8B0AAD8610ARZ *–40°C to +125°C 8-Lead SOIC RN-8AD8610ARZ-REEL *–40°C to +125°C 8-Lead SOIC RN-8AD8610ARZ-REEL7*–40°C to +125°C 8-Lead SOIC RN-8AD8610BR–40°C to +125°C 8-Lead SOIC RN-8AD8610BR-REEL –40°C to +125°C 8-Lead SOIC RN-8AD8610BR-REEL7–40°C to +125°C 8-Lead SOIC RN-8AD8610BRZ *–40°C to +125°C 8-Lead SOIC RN-8AD8610BRZ-REEL *–40°C to +125°C 8-Lead SOIC RN-8AD8610BRZ-REEL7*–40°C to +125°C 8-Lead SOIC RN-8AD8620AR–40°C to +125°C 8-Lead SOIC RN-8AD8620AR-REEL –40°C to +125°C 8-Lead SOIC RN-8AD8620AR-REEL7–40°C to +125°C 8-Lead SOIC RN-8AD8620BR–40°C to +125°C 8-Lead SOIC RN-8AD8620BR-REEL –40°C to +125°C 8-Lead SOIC RN-8AD8620BR-REEL7–40°C to +125°C8-Lead SOICRN-8*Pb-free partABSOLUTE MAXIMUM RATINGS *Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27.3 V Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V S–– to V S+Differential Input Voltage . . . . . . . . . . . . . . .± Supply Voltage Output Short-Circuit Duration to GND . . . . . . . . . .Indefinite Storage Temperature RangeR, RM Packages . . . . . . . . . . . . . . . . . . . . .–65°C to +150°C Operating Temperature RangeAD8610/AD8620 . . . . . . . . . . . . . . . . . . . .–40°C to +125°C Junction Temperature RangeR, RM Packages . . . . . . . . . . . . . . . . . . . . .–65°C to +150°C Lead Temperature Range (Soldering, 10 sec) . . . . . . . . 300°C*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Package Type JA *JC Unit 8-Lead MSOP (RM)19044°C/W 8-Lead SOIC (RN)15843°C/W*θJA is specified for worst-case conditions; i.e., θJA is specified for a device soldered in circuit board for surface-mount packages.CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8610/AD8620 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.REV. D Typical Performance Characteristics–AD8610/AD8620–5–INPUT OFFSET VOL T AGE – V1486421012N U M B E R O F A MP L I F I E R STPC 1.Input Offset Voltage at ±13 VI N P U T O F F S E T V O L T A G E –V600400–600200–200–400TEMPERATURE – ؇CTPC 4.Input Offset Voltage vs.Temperature at ±5 V (300 Amplifiers)SUPPL Y VOL T AGE – ؎V3.01.502.51.00.52.0013123456789101112S U P P L Y C U R R E N T – m ATPC 7.Supply Current vs.Supply Voltage I N P U TO F F S E T V O L T A G E – V600400؊6002000؊200؊400TEMPERATURE – ؇CTPC 2.Input Offset Voltage vs.Temperature at ±13 V (300 Amplifiers)T C V OS – V/؇C141210864200.20.61.01.41.82.22.6N U M B E R O FA M P L I F I E R S TPC 5.Input Offset Voltage DriftTEMPERATURE – ؇C2.553.052.852.652.952.75S U P P L Y C U R R E N T – m A؊40TPC 8.Supply Current vs.Temperature at ±13 V INPUT OFFSET VOL T AGE – V148642101201618؊250250؊15050150؊50N U M B E R O F A M P L I F I E R STPC 3.Input Offset Voltage at ±5 VCOMMON-MODE VOL T AGE – V3.63.42.02.82.62.42.23.23.0I N P U T BI A S C U R R E N T –p ATPC 6.Input Bias Current mon-Mode VoltageTEMPERATURE – ؇C2.302.652.602.402.502.552.452.35S U P P L Y C U R R E N T – m A؊40TPC 9.Supply Current vs.Temperature at ±5 VREV. D–6–AD8610/AD8620O U T P U T V O L T A G E T O S U P P L Y R A I L – VRESIST ANCE LOAD – ⍀100M10M 1M 100k 10k 1k10000.20.40.60.81.01.21.41.61.8TPC 10.Output Voltage to Supply Rail vs. Load 12.0511.8012.0011.9511.9011.85O U T P U T V O L T A G E H I G H –VTEMPERA TURE – ؇CTPC 13.Output Voltage High vs. Temperature at ±13 VFREQUENCY – Hz10k100k 1M 1k10M 100MC L O S ED -L O O P G A I N – d B؊40؊20206040TPC 16.Closed-Loop Gain vs.FrequencyTEMPERA TURE – ؇C4.254.203.954.154.104.054.00O U T P U T V O L T A G E H I G H – VTPC 11.Output Voltage High vs.Temperature at ±5 VTEMPERA TURE – ؇C؊11.80؊12.05؊11.85؊11.90؊11.95؊12.00O U T P U T V O L T A G E L O W – VTPC 14.Output Voltage Low vs.Temperature at ±13 VTEMPERA TURE – ؇C260100A V O – V /m V220180140240200160120TPC 17.A VO vs. Temperature at ±13 VTEMPERA TURE – ؇C؊3.95؊4.05؊4.30؊4.10؊4.15؊4.20؊4.25؊4.00O U T P U T V O L T A G E L O W – VTPC 12.Output Voltage Low vs.Temperature at ±5 VG A I N – d B40206080100120؊20؊40؊60؊80FREQUENCY – MHzP H A S E – D e g r e e s90450135180225270؊45؊90؊135؊180TPC 15.Open-Loop Gainand Phase vs. FrequencyTEMPERA TURE – ؇C190100180160140120170150130110A V O – V /m V TPC 18.A VO vs. Temperature at ±5 VREV. D AD8610/AD8620–7–P S R R – d BFREQUENCY – Hz60M10k 100k 1M 10M 1001kTPC 19.PSRR vs. Frequency at ±13 V C M R R – d BFREQUENCY – Hz1060M10k 100k 1M 10M1001k 14010080604020120TPC 22.CMRR vs. Frequency TIME – 1s/DIVP -P V O L T A G E N O I S E – 1V /D I VTPC 25.0.1 Hz to 10 Hz Input VoltageNoise P S R R – d B122121116120119118117TEMPERATURE – ؇CTPC 21.PSRR vs. TemperatureTIME – 4s/DIVV O L T A G E – 300m V /D I VTPC 24.Negative OvervoltageRecoveryFREQUENCY – Hz1k100M10k100k1M 10M Z O U T – ⍀TPC 27.Z OUT vs. FrequencyP S R R – d B–401008060400120–2020160140FREQUENCY – Hz60M10k 100k 1M 10M1001kTPC 20.PSRR vs. Frequency at ±5 VTIME – 4s/DIVV O L T A G E – 300m V /D I V0V0VTPC 23.Positive Overvoltage RecoveryFREQUENCY –Hz1,00010011011M10010k101k100kV O L T A G E N O I S E D E N S I T Y – n V TPC 26.Input Voltage Noise vs.FrequencyREV. D–8–AD8610/AD8620FREQUENCY – HzZ O U T – ⍀1009008070605040302010TPC 28.Z OUT vs. FrequencyCAP ACIT ANCE – pF4035030255201510110k 101001k S M A L L S I G N A L O V E R S H O O T – %TPC 31.Small Signal Overshoot vs.Load CapacitanceTIME – 400ns/DIVV O L T A G E – 5V /D I VTPC 34.+SR at G = +1TEMPERA TURE – ؇CI B –p A30002500025851252000150********TPC 29.Input Bias Current vs.TemperatureTIME – 400s/DIVV O L T A G E – 5V /D I VTPC 32.No Phase ReversalTIME – 400ns/DIVV O L T A G E – 5V /D I VTPC 35.–SR at G = +1CAP ACIT ANCE – pF4035030255201510110k101001kS M A L L S I G N A L O V E R S H O O T – %TPC 30.Small Signal Overshoot vs.Load CapacitanceTIME – 1s/DIVV O L T A G E – 5V /D I VTPC rge Signal Response at G = +1TIME – 1s/DIVV O L T A G E – 5V /D I VTPC rge Signal Response at G = –1REV. DAD8610/AD8620–9–TIME – 400ns/DIVV O L T A G E – 5V /D I VTPC 37.+SR at G = –1TIME – 400ns/DIVV O L T A G E – 5V /D I VTPC 38.–SR at G = –1V IN20V p-pCS(dB) = 20 log (V OUT /10 ؋ V IN )Figure 1.Channel Separation Test CircuitFUNCTIONAL DESCRIPTIONThe AD8610/AD8620 is manufactured on Analog Devices, Inc.’s proprietary XFCB (eXtra Fast Complementary Bipolar) process.XFCB is fully dielectrically isolated (DI) and used in conjunc-tion with N-channel JFET technology and trimmable thin-film resistors to create the world’s most precise JFET input amplifier.Dielectrically isolated NPN and PNP transistors fabricated on XFCB have F T greater than 3 GHz. Low T C thin film resistors enable very accurate offset voltage and offset voltage tempcotrimming. These process breakthroughs allowed Analog Devices’world class IC designers to create an amplifier with faster slew rate and more than 50% higher bandwidth at half of the current consumed by its closest competition. The AD8610 is uncondi-tionally stable in all gains, even with capacitive loads well in excess of 1 nF. The AD8610B achieves less than 100 µV of offset and 1 µV/°C of offset drift, numbers usually associated with very high precision bipolar input amplifiers. The AD8610 is offered in the tiny 8-lead MSOP as well as narrow 8-lead SOIC surface-mount packages and is fully specified with supply voltages from ±5 V to ±13 V. The very wide specified temperature range, up to 125°C, guarantees superior operation in systems with little or no active cooling.The unique input architecture of the AD8610 features extremely low input bias currents and very low input offset voltage. Low power consumption minimizes the die temperature and maintains the very low input bias current. Unlike many competitive JFET amplifiers, the AD8610/AD8620 input bias currents are low even at elevated temperatures. Typical bias currents are less than 200pA at 85°C. The gate current of a JFET doubles every 10°C resulting in a similar increase in input bias current over temperature.Special care should be given to the PC board layout to minimize leakage currents between PCB traces. Improper layout and board handling generates leakage current that exceeds the bias current of the AD8610/AD8620.FREQUENCY – kHz35050100150200250300138136120128126124122132130134C S – d BFigure 2.AD8620 Channel Separation GraphPower ConsumptionA major advantage of the AD8610/AD8620 in new designs is the saving of power. Lower power consumption of the AD8610makes it much more attractive for portable instrumentation and for high-density systems, simplifying thermal management, and reducing power supply performance requirements. Compare the power consumption of the AD8610/AD8620 versus the OPA627in Figure 3.TEMPERA TURE – ؇C8765432S U P P L Y C U R R E N T – m AFigure 3.Supply Current vs. TemperatureREV. D–10–AD8610/AD8620Driving Large Capacitive LoadsThe AD8610 has excellent capacitive load driving capability and can safely drive up to 10 nF when operating with ±5 V supply.Figures 4 and 5 compare the AD8610/AD8620 against the OPA627in the noninverting gain configuration driving a 10 k Ω resistor and 10,000 pF capacitor placed in parallel on its output, with a square wave input set to a frequency of 200 kHz. The AD8610 has much less ringing than the OPA627 with heavy capacitive loads.TIME – 2s/DIVV O L T A G E – 20m V /D IVFigure 4.OPA627 Driving C L = 10,000 pFTIME – 2s/DIVV O L T A G E – 20m V /D IVFigure 5.AD8610/AD8620 Driving C L = 10,000 pFThe AD8610/AD8620 can drive much larger capacitances without any external compensation. Although the AD8610/AD8620 is stable with very large capacitive loads, remember that this capacitive loading will limit the bandwidth of the amplifier. Heavy capacitive loads will also increase the amount of overshoot and ringing at the output. Figures 7 and 8 show the AD8610/AD8620 and the OPA627in a noninverting gain of +2 driving 2 µF of capacitance load. The ringing on the OPA627 is much larger in magnitude and continues more than 10 times longer than the AD8610.2FFigure 6.Capacitive Load Drive Test CircuitTIME – 20s/DIVV O L T A G E – 50m V /D I VFigure 7.OPA627 Capacitive Load Drive, A V = +2TIME – 20s/DIVV O L T A G E – 50m V /D I VFigure 8.AD8610/AD8620 Capacitive Load Drive, A V = +2Slew Rate (Unity Gain Inverting vs. Noninverting)Amplifiers generally have a faster slew rate in an inverting unity gain configuration due to the absence of the differential input capacitance. Figures 9 through 12 show the performance of the AD8610 configured in a gain of –1 compared to the OPA627.The AD8610 slew rate is more symmetrical, and both the positive and negative transitions are much cleaner than in the OPA627.REV. D AD8610/AD8620–11–TIME – 400ns/DIVV O L T A G E – 5V /D I VFigure 9.(+SR) of AD8610/AD8620 in Unity Gain of –1TIME – 400ns/DIVV O L T A G E – 5V /D I VFigure 10.(+SR) of OPA627 in Unity Gain of –1TIME – 400ns/DIVV O L T A G E – 5V /D I VFigure 11.(–SR) of AD8610/AD8620 in Unity Gain of –1TIME – 400ns/DIVV O L T A G E – 5V /D IVFigure 12.(–SR) of OPA627 in Unity Gain of –1The AD8610 has a very fast slew rate of 60 V/µs even when config-ured in a noninverting gain of +1. This is the toughest condition to impose on any amplifier since the input common-mode capacitance of the amplifier generally makes its SR appear worse. The slew rate of an amplifier varies according to the voltage difference between its two inputs. To observe the maximum SR as specified in the AD8610 data sheet, a difference voltage of about 2 V between the inputs must be ensured. This will be required for virtually any JFET op amp so that one side of the op amp input circuit is com-pletely off, maximizing the current available to charge and discharge the internal compensation capacitance. Lower differential drive voltages will produce lower slew rate readings. A JFET-input op amp with a slew rate of 60 V/µs at unity gain with V IN = 10 V might slew at 20 V/µs if it is operated at a gain of +100 with V IN = 100mV.The slew rate of the AD8610/AD8620 is double that of the OPA627when configured in a unity gain of +1 (see Figures 13 and 14).TIME – 400ns/DIVV O L T A G E – 5V /D I VFigure 13.(+SR) of AD8610/AD8620 in Unity Gain of +1REV. D–12–AD8610/AD8620diodes greatly interfere with many application circuits such as precision rectifiers and comparators. The AD8610 is free from these limitations.+13V 14VFigure 16.Unity Gain FollowerNo Phase ReversalMany amplifiers misbehave when one or both of the inputs are forced beyond the input common-mode voltage range. Phase reversal is typified by the transfer function of the amplifier,effectively reversing its transfer polarity. In some cases, this can cause lockup and even equipment damage in servo systems, and may cause permanent damage or nonrecoverable parameter shifts to the amplifier itself. Many amplifiers feature compensation circuitry to combat these effects, but some are only effective for the inverting input. The AD8610/AD8620 is designed to prevent phase reversal when one or both inputs are forced beyond their input common-mode voltage range.TIME – 400s/DIVV O L T A G E– 5V /D I VFigure 17.No Phase ReversalTHD Readings vs. Common-Mode VoltageTotal harmonic distortion of the AD8610/AD8620 is well below 0.0006% with any load down to 600 Ω. The AD8610/AD8620outperforms the OPA627 for distortion, especially at frequen-cies above 20 kHz.FREQUENCY – HzT H D +N – %Figure 18.AD8610 vs. OPA627 THD + Noise @ V CM= 0 VTIME – 400ns/DIVV O L T A G E – 5V /D I VFigure 14.(+SR) of OPA627 in Unity Gain of +1The slew rate of an amplifier determines the maximum frequency at which it can respond to a large signal input. This frequency (known as full-power bandwidth, or FPBW) can be calculated from the equation:FPBW SRV PEAK =×()2πfor a given distortion (e.g., 1%).V O L T A G E – 10V /D I VTIME – 400ns/DIVFigure 15.AD8610 FPBWInput Overvoltage ProtectionWhen the input of an amplifier is driven below V EE or above V CC by more than one V BE , large currents will flow from the substrate through the negative supply (V–) or the positive supply (V+),respectively, to the input pins, which can destroy the device. If the input source can deliver larger currents than the maximum forward current of the diode (>5 mA), a series resistor can be added to protect the inputs. With its very low input bias and offset current, a large series resistor can be placed in front of the AD8610 inputs to limit current to below damaging levels. Series resistance of 10 k Ωwill generate less than 25 µV of offset. This 10 k Ω will allow input voltages more than 5 V beyond either power supply. Thermal noise generated by the resistor will add 7.5 nV/√Hz to the noise of the AD8610. For the AD8610/AD8620, differential voltages equal to the supply voltage will not cause any problem (see Figure 15).In this context, it should also be noted that the high breakdown voltage of the input FETs eliminates the need to include clamp diodes between the inputs of the amplifier, a practice that is mandatory on many precision op amps. Unfortunately, clampREV. D AD8610/AD8620–13–FREQUENCY – HzT H D + N – %Figure 19.THD + Noise vs. FrequencyNoise vs. Common-Mode VoltageAD8610 noise density varies only 10% over the input range as shown in Table I.Table I.Noise vs. Common-Mode VoltageV CM at F = 1 kHz (V)Noise Reading (nV/√Hz )–107.21–5 6.890 6.73+5 6.41+107.21Settling TimeThe AD8610 has a very fast settling time, even to a very tight error band, as can be seen from Figure 20. The AD8610 is configured in an inverting gain of +1 with 2 k Ω input and feedback resistors.The output is monitored with a 10×, 10 M, 11.2 pF scope probe.ERROR BAND – %1.2k0.001100.01S E T T L I N G T I M E – n s0.118004001.0k600200Figure 20.AD8610 Settling Time vs. Error BandERROR BAND – %1.2k1.0k 0S E T T L I N G T I M E – n s800600200400Figure 21.OPA627 Settling Time vs. Error BandThe AD8610/AD8620 maintains this fast settling when loaded with large capacitive loads as shown in Figure 22.C L – pF02000500S E T T L I N G T I M E – s100015003.02.00.01.02.51.50.5Figure 22.AD8610 Settling Time vs. Load CapacitanceC L – pF02000500S E T T L I N G T I M E – s10001500Figure 23.OPA627 Settling Time vs. Load Capacitance Output Current CapabilityThe AD8610 can drive very heavy loads due to its high output current. It is capable of sourcing or sinking 45 mA at ±10 V output.The short circuit current is quite high and the part is capable of sinking about 95 mA and sourcing over 60 mA while operating withREV. D–14–AD8610/AD8620supplies of ±5 V. Figures 24 and 25 compare the load current versus output voltage of AD8610/AD8620 and OPA627.LOAD CURRENT – A100.10.000011D E L T A F R O M R E S P E C T I V E R A I L – V10.00010.0010.010.1Figure 24.AD8610 Dropout from ±13 V vs. Load CurrentLOAD CURRENT – A100.10.000011D E L T A F R O M R E S P E C T I V E R A I L – V10.00010.0010.010.1Figure 25.OPA627 Dropout from ±15 V vs. Load CurrentAlthough operating conditions imposed on the AD8610 (±13 V)are less favorable than the OPA627 (±15 V), it can be seen that the AD8610 has much better drive capability (lower headroom to the supply) for a given load current.Operating with Supplies Greater than ±13 VThe AD8610 maximum operating voltage is specified at ±13 V.When ±13 V is not readily available, an inexpensive LDO can provide ±12 V from a nominal ±15 V supply.Input Offset Voltage AdjustmentOffset of AD8610 is very small and normally does not require additional offset adjustment. However, the offset adjust pins can be used as shown in Figure 26 to further reduce the dc offset. By using resistors in the range of 50 k Ω, offset trim range is ±3.3 mV.+V OUTSFigure 26.Offset Voltage Nulling CircuitProgrammable Gain Amplifier (PGA)The combination of low noise, low input bias current, low input offset voltage, and low temperature drift make the AD8610 a perfect solution for programmable gain amplifiers. PGAs are often used immediately after sensors to increase the dynamic range of the measurement circuit. Historically, the large ON resistance of switches, combined with the large I B currents of amplifiers,created a large dc offset in PGAs. Recent and improved monolithic switches and amplifiers completely remove these problems. A PGA discrete circuit is shown in Figure 27. In Figure 27, when the 10 pA bias current of the AD8610 is dropped across the (<5 Ω) R ON of the switch, it results in a negligible offset error.When high precision resistors are used, as in the circuit of Figure 27,the error introduced by the PGA is within the 1/2 LSB requirement for a 16-bit system.Figure 27.High Precision PGA1. Room temperature error calculation due to R ON and I B :∆Ω∆∆V I R Total Offset Offset V Total Offset Offset Trimmed V Total Offset OS B ON OSOS =×=×==+=+=+≅25105105pA pV () (_) V pV V AD8610AD8610µµ2. Full temperature error calculation due to R ON and I B :∆ΩV I R OS B ON (C)(C)(C)pA .nV @@@85858525015375°=°×°=×=3. Temperature coefficient of switch and AD8610/AD8620combined is essentially the same as the T C V OS of the AD8610: ∆∆∆∆∆∆∆∆V T total V T V T I R V T total OS OS OS B ON OS /()/()/()/().V/C .nV/C .V/C =+×=°+°≅°AD86100500605µµ。

AD8326ARP-REEL资料

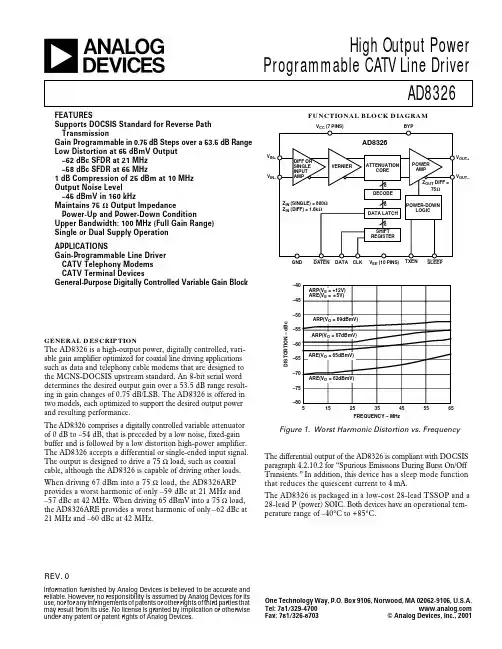

High Output Power Programmable CATV Line Driver AD8326

FUNCTIONAL BLOCK DIAGRAM

VCC (7 PINS) BYP

AD8326

VIN+ DIFF OR SINGLE INPUT AMP VOUT+ VERNIER

ATTENUATION CORE

1 dB Compression Point Differential Output Impedance OVERALL PERFORMANCE Worst Harmonic Distortion

Max Gain, f = 10 MHz Transmit Enable and Transmit Disable Mode f = 14 MHz, VOUT = 67 dBmV @ Max Gain f = 21 MHz, VOUT = 67 dBmV @ Max Gain f = 42 MHz, VOUT = 67 dBmV @ Max Gain f = 65 MHz, VOUT = 67 dBmV @ Max Gain 16 QAM, VOUT = 67 dBmV Adj Ch Wid = Tr Ch Wid = 160 KSYM/SEC Min to Max Gain Max Gain, VIN = 0 V to 0.25 V p-p Min Gain, TXEN = 0, 65 MHz, V IN = 0.25 V p-p Max Gain, TXEN = 0, 42 MHz, V IN = 0.25 V p-p Max Gain, TXEN = 0, 65 MHz, V IN = 0.25 V p-p All Gains, SLEEP, 65 MHz, V IN = 0.25 V p-p

AD648KR-REEL7中文资料

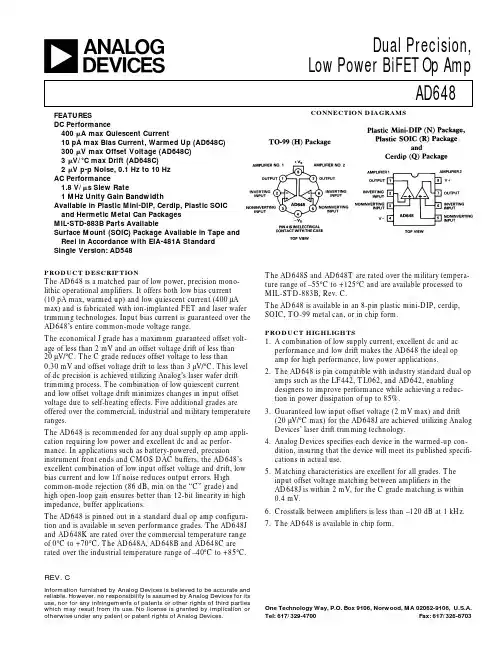

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

AD9661AKR-REEL资料

VREF –50 25 0.1 –10 130 –32 0.95 120 2.50 2 1.0

VREF + 1.6 +50 1.6 0 +32 1.05

V µA MHz V µA MHz mV V/V mA V mA µA MHz ns ns ns ns ns ns nA V pF V V V V µA mA V mV/°C mA mA/mA V Ω V mA

CHOLD = 33 pF, RF = 1 kΩ, CF = 2 pF

VOUT = 2.5 V PULSE = LOW, DISABLE = LOW PULSE = LOW, DISABLE = HIGH Output Current –3 dB

5.25 5.0 1.0

2.9 3.2

200 3.9 3.7 1.5 1.5 13 3

LASER DIODE

OUTPUT

8

AD9661A

ANALOG POWER MONITOR VREF

IMONITOR

1:1

SENSE IN IMONITOR 1.0V

REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. © Analog Devices, Inc., 1995 One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

AD7874ARZ-REEL中文资料

One Technology Way, P.O. Box 9106, Norwood, M329-4700 Fax: 617/326-8703

元器件交易网

AD7874–SPECIFICATIONS external. All specifications T

Parameter SAMPLE-AND-HOLD Acquisition Time2 to 0.01% Droop Rate2, 3 –3 dB Small Signal Bandwidth3 Aperture Delay2 Aperture Jitter2, 3 Aperture Delay Matching2 SAMPLE-AND-HOLD AND ADC DYNAMIC PERFORMANCE Signal-to-Noise Ratio Total Harmonic Distortion Peak Harmonic or Spurious Noise Intermodulation Distortion 2nd Order Terms 3rd Order Terms Channel-to-Channel Isolation2 DC ACCURACY Resolution Relative Accuracy Differential Nonlinearity Positive Full-Scale Error4 Negative Full-Scale Error4 Full-Scale Error Match Bipolar Zero Error Bipolar Zero Error Match ANALOG INPUTS Input Voltage Range Input Current REFERENCE OUTPUTS REF OUT REF OUT Error @ +25°C TMIN to TMAX REF OUT Temperature Coefficient Reference Load Change REFERENCE INPUT Input Voltage Range Input Current Input Capacitance3 LOGIC INPUTS Input High Voltage, VINH Input Low Voltage, VINL Input Current, IIN Input Capacitance, CIN3 LOGIC OUTPUTS Output High Voltage, VOH Output Low Voltage, VOL DB0–DB11 Floating-State Leakage Current Floating-State Output Capacitance Output Coding POWER REQUIREMENTS VDD VSS IDD ISS Power Dissipation A Version B Version S Version Units 2 1 500 0 40 200 4 2 1 500 0 40 200 4 2 2 500 0 40 200 4 µs max mV/ms max kHz typ ns min ns max ps typ ns max

AD7417ARU-REEL中文资料