北大 internet高级程序设计 lecture5-Makefile

《高级程序设计语言》课件

技能和解决实际问题的能力。

学习目标

掌握多种高级程序设计语 言的基本语法、数据类型 、控制结构等基础知识。

熟悉面向对象编程思想, 了解类、对象、继承、多 态等概念及其在各种高级 语言中的实现。

掌握常用数据结构和算法 ,能够编写高效的程序。

提高分析问题、解决问题 的能力,培养良好的编程 习惯和团队协作精神。

06 并发和并行程序设计

并发和并行程序设计的基本概念

01

并发程序设计

指在单个处理器上实现多个任务同 时执行的一种程序设计方法。

任务划分

将一个大的任务划分为多个小的任 务,每个任务可以独立执行。

03

02

并行程序设计

指利用多个处理器同时执行多个任 务的一种程序设计方法。

任务调度

根据系统资源和任务优先级,合理 安排任务的执行顺序。

04

Spark:一种基于大数据处理的并行计算框架,用于处理大规模数据 集。

并行编程的挑战和解决方案

数据依赖性

并行程序中任务之间的数据依赖关系可能导致死锁或竞争条件。解 决方案包括使用同步原语(如锁、信号量)或避免数据依赖性。

负载均衡

并行程序中任务执行时间的不均衡可能导致资源利用率低下。解决 方案包括任务划分和调度优化。

继承

子类继承父类的属性 和方法,实现代码复 用。

多态

同一消息发送给不同 的对象,产生不同的 行为。

类和对象

类是对象的模板,定 义了对象的属性和方 法。

类和对象的关系是抽 象和具体的关系。

对象是类的实例,具 有类所定义的属性和 方法。

继承和多态

继承

子类继承父类的属性和方法,可 以添加或覆盖父类的方法。

编译期类型擦除

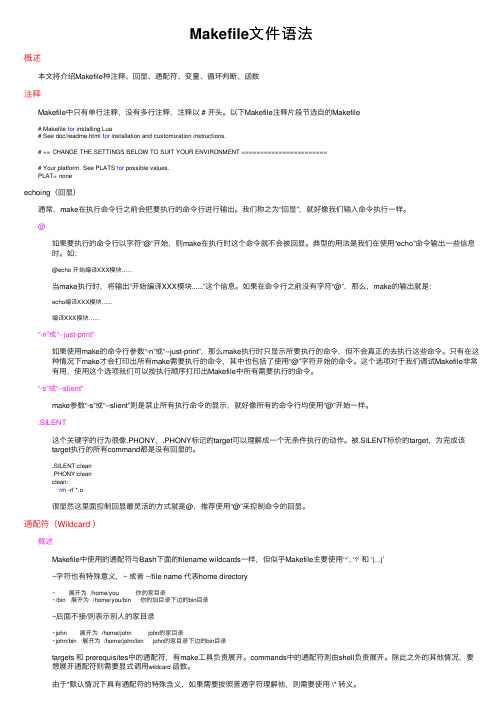

Makefile文件语法

Makefile⽂件语法概述本⽂将介绍Makefile种注释、回显、通配符、变量、循环判断、函数注释Makefile中只有单⾏注释,没有多⾏注释,注释以 # 开头。

以下Makefile注释⽚段节选⾃的Makefile# Makefile for installing Lua# See doc/readme.html for installation and customization instructions.# == CHANGE THE SETTINGS BELOW TO SUIT YOUR ENVIRONMENT =======================# Your platform. See PLATS for possible values.PLAT= noneechoing(回显)通常,make在执⾏命令⾏之前会把要执⾏的命令⾏进⾏输出。

我们称之为“回显”,就好像我们输⼊命令执⾏⼀样。

@如果要执⾏的命令⾏以字符“@”开始,则make在执⾏时这个命令就不会被回显。

典型的⽤法是我们在使⽤“echo”命令输出⼀些信息时。

如:@echo 开始编译XXX模块......当make执⾏时,将输出“开始编译XXX模块......”这个信息。

如果在命令⾏之前没有字符“@”,那么,make的输出就是:echo编译XXX模块......编译XXX模块......“-n”或“--just-print”如果使⽤make的命令⾏参数“-n”或“--just-print”,那么make执⾏时只显⽰所要执⾏的命令,但不会真正的去执⾏这些命令。

只有在这种情况下make才会打印出所有make需要执⾏的命令,其中也包括了使⽤“@”字符开始的命令。

这个选项对于我们调试Makefile⾮常有⽤,使⽤这个选项我们可以按执⾏顺序打印出Makefile中所有需要执⾏的命令。

“-s”或“--slient”make参数“-s”或“--slient”则是禁⽌所有执⾏命令的显⽰,就好像所有的命令⾏均使⽤“@”开始⼀样。

github上用makefile编译的项目

github上用makefile编译的项目GitHub是一个受欢迎的代码托管平台,可以用于管理和分享各种项目。

在GitHub上,很多项目使用Makefile来编译和构建代码。

Makefile是一种用于自动化构建的文件,其中包含了构建项目所需的命令和规则。

在本文中,我们将讨论GitHub上使用Makefile编译的项目,并探讨Makefile的一些常见用法和优势。

首先,我们需要了解Makefile的基本语法和结构。

Makefile由一系列规则组成,每个规则包含了一个目标以及构建目标所需的命令。

例如,以下是一个简单的Makefile示例:```all: main.c function1.o function2.ogcc -o program main.c function1.o function2.ofunction1.o: function1.cgcc -c function1.cfunction2.o: function2.cgcc -c function2.c```上述Makefile中定义了三个规则。

第一个规则`all`是一个特殊规则,它指定了一个默认的目标,并定义了编译程序所需的命令。

接下来的两个规则`function1.o`和`function2.o`定义了编译两个源文件的命令。

通过运行`make`命令,Makefile将根据规则自动执行这些命令,并构建项目。

使用Makefile可以有一些优势,特别是对于大型项目或项目依赖于许多文件的情况。

以下是一些Makefile的优点:1.自动化构建:Makefile定义了源代码构建所需的一系列命令,通过运行`make`命令,可以自动执行这些命令来构建项目。

这样可以大大减少手动输入命令的工作量,提高开发效率。

2.快速增量编译:Makefile使用文件的时间戳来确定哪些文件需要重新编译。

因此,如果只有部分文件发生了更改,只有这些文件需要重新编译,而其他文件则可以跳过。

makefile debug编译

makefile debug编译摘要:1.编译的概述2.Makefile 的作用3.debug 编译的流程4.Makefile debug 编译的具体步骤5.debug 编译的优点与局限性正文:编译的概述编译是将源代码转换为目标代码的过程,通常由编译器完成。

在软件开发过程中,编译是一个重要的环节,用于检查代码的正确性和实现软件的功能。

根据不同的需求,编译过程可以分为多种类型,如调试编译、优化编译等。

本文将介绍一种常见的编译类型:debug 编译,并说明如何使用Makefile 进行debug 编译。

Makefile 的作用Makefile 是一个文本文件,用于描述软件项目的编译过程。

它包含了编译所需的命令、依赖关系和编译选项等信息。

通过Makefile,开发者可以方便地管理编译过程,自动化地完成源代码到目标代码的转换。

在debug 编译中,Makefile 可以帮助开发者配置编译选项,以便于调试代码。

debug 编译的流程debug 编译的流程通常包括以下几个步骤:1.配置编译选项:根据开发者的需求,为编译器添加调试相关的选项,如-g(生成调试信息)、-O0(不优化)等。

2.编译源代码:使用编译器,按照Makefile 中指定的编译选项,编译源代码。

3.生成目标代码:编译成功后,会生成目标代码(如可执行文件、库文件等)。

4.运行调试器:使用调试器运行目标代码,以便于开发者检查代码的运行状态和调试错误。

Makefile debug 编译的具体步骤使用Makefile 进行debug 编译的具体步骤如下:1.创建Makefile:在项目根目录下创建一个名为Makefile 的文本文件。

2.编写Makefile:在Makefile 中,编写编译规则和依赖关系。

例如:```all: main.o -o mainmain.o: main.ct$(CC) $(CFLAGS) -c main.cmain: main.ot$(CC) $(LDFLAGS) -o main main.o```在这个例子中,我们使用GCC 编译器(CC)进行编译,并添加了-g 和-O0 选项,用于生成调试信息和不优化目标代码。

Makefile中一些特殊符号的意义

Makefile中⼀些特殊符号的意义在makefile中,有时会接触到⼀些以特殊字符打头的命令,⽐如@, -, +,如果之前没有接触过的话,会感觉⽐较奇怪,其实,多是⼀些为了实现特定⾏为模式⽽引⼊的标记符。

命令⾏以'@'打头的含义:在执⾏到的时候不回显相应的命令内容,只显⽰命令的输出。

命令⾏以'-'打头的含义:在执⾏到的时候如果发⽣错误(退出返回⾮零状态)时,不中断make过程。

命令⾏以'+'打头的含义: makefile中以+开头的命令的执⾏不受到 make的-n,-t,-q三个参数的影响。

我们知道,在make的时候,如果加上-n, -t, -q这样的参数,都是不执⾏相应命令的,⽽以'+'开头的命令,则⽆论make命令后⾯是否跟着三个参数,都会被执⾏。

附:make命令参数make的参数下⾯列举了所有GNU make 3.80版的参数定义。

其它版本和产商的make⼤同⼩异,不过其它产商的make的具体参数还是请参考各⾃的产品⽂档。

“-b”“-m”这两个参数的作⽤是忽略和其它版本make的兼容性。

“-B”“--always-make”认为所有的⽬标都需要更新(重编译)。

“-C <dir>;”“--directory=<dir>;”指定读取makefile的⽬录。

如果有多个“-C”参数,make的解释是后⾯的路径以前⾯的作为相对路径,并以最后的⽬录作为被指定⽬录。

如:“make –C ~hchen/test –C prog”等价于“make –C ~hchen/test/prog”。

“—debug[=<options>;]”输出make的调试信息。

它有⼏种不同的级别可供选择,如果没有参数,那就是输出最简单的调试信息。

下⾯是<options>;的取值:a —— 也就是all,输出所有的调试信息。

makefile debug编译

makefile debug编译【最新版】目录1.Makefile 概述2.debug 编译的含义3.Makefile 中的 debug 编译4.如何进行 Makefile debug 编译5.总结正文1.Makefile 概述Makefile 是一种用于自动化构建和编译软件的脚本文件,通常用于Unix 和类 Unix 系统中。

它由一系列的规则和指令组成,用于指定源代码文件、编译器、链接器和其他工具,以便构建可执行文件。

2.debug 编译的含义debug 编译是一种编译方式,用于在编译过程中添加调试信息,以便于开发者在运行程序时能够追踪代码的执行过程,找出程序中的错误和问题。

3.Makefile 中的 debug 编译在 Makefile 中,要进行 debug 编译,需要使用一定的指令和规则。

通常,需要使用“CFLAGS”变量来指定编译器选项,其中包括添加调试信息的选项,例如“-g”。

同时,还需要使用“DEBUG”变量来指定是否进行debug 编译,例如,“DEBUG=on”表示进行 debug 编译,“DEBUG=off”表示不进行 debug 编译。

4.如何进行 Makefile debug 编译具体进行 Makefile debug 编译的步骤如下:(1) 在 Makefile 中设置“DEBUG”变量为“on”,例如,“DEBUG=on”;(2) 在 Makefile 中设置“CFLAGS”变量,添加调试选项“-g”,例如,“CFLAGS=-g”;(3) 保存 Makefile 文件;(4) 在命令行中,进入到 Makefile 所在的目录;(5) 执行“make”命令,进行编译。

这样,编译器就会在编译过程中添加调试信息,生成的可执行文件可以在运行时进行调试。

5.总结Makefile 是一种重要的构建工具,能够帮助开发者自动化构建和编译软件。

debug 编译是开发过程中常用的一种编译方式,可以帮助开发者找出程序中的错误和问题。

makefile基本使用方法

makefile基本使用方法makefile是一种用来管理和自动化构建程序的工具。

它可以根据源代码文件的依赖关系和编译规则来自动构建目标文件和可执行文件。

makefile的基本使用方法如下:1. 创建makefile文件:在项目的根目录下创建一个名为makefile 的文件。

2. 定义变量:在makefile中,可以使用变量来存储一些常用的参数和路径,以便于后续的使用。

例如,可以定义一个名为CC的变量来指定编译器的名称,如:CC=gcc。

3. 编写规则:在makefile中,可以使用规则来指定如何编译源代码文件和生成目标文件。

一个规则由两部分组成:目标和依赖。

目标是要生成的文件,依赖是生成目标文件所需要的源代码文件。

例如,可以编写以下规则:```target: dependency1 dependency2command1command2```其中,target是目标文件,dependency1和dependency2是依赖的源代码文件,command1和command2是生成目标文件所需要执行的命令。

4. 编写默认规则:在makefile中,可以使用一个默认规则来指定如何生成最终的可执行文件。

默认规则的目标通常是可执行文件,依赖是所有的源代码文件。

例如,可以编写以下默认规则:```all: target1 target2```其中,target1和target2是生成的目标文件。

5. 编写clean规则:在makefile中,可以使用clean规则来清理生成的目标文件和可执行文件。

例如,可以编写以下clean规则: ```clean:rm -f target1 target2```其中,target1和target2是要清理的目标文件。

6. 运行make命令:在命令行中,使用make命令来执行makefile 文件。

make命令会自动根据规则和依赖关系来编译源代码文件和生成目标文件。

例如,可以运行以下命令:``````make命令会根据makefile文件中的规则和依赖关系来编译源代码文件并生成目标文件和可执行文件。

makefile 中文手册 第四章 _ Makefile的规则

第四章:Makefile的规则本章我们将讨论Makefile的一个重要内容,规则。

熟悉规则对于书写Makefile至关重要。

Makefile中,规则描述了在何种情况下使用什么命令来重建一个特定的文件,此文件被称为规则“目标”(通常规则中的目标只有一个)。

规则中出目标之外的罗列的其它文件称为“目标”的依赖,而规则的命令是用来更新或者创建此规则的目标。

除了makefile的“终极目标”所在的规则以外,其它规则的顺序在makefile文件中没有意义。

“终极目标”就是当没有使用make 命令行指定具体目标时,make默认的更新的哪一个目标。

它是makefile文件中第一个规则的目标。

如果在makefile中第一个规则有多个目标的话,那么多个目标中的第一个将会被作为make的“终极目标”。

有两种情况的例外:1. 目标名以点号“.”开始的并且其后不存在斜线“/”(“./”被认为是当前目录;“../”被认为是上一级目录);2. 模式规则的目标。

当这两种目标所在的规则是Makefile的第一个规则时,它们并不会被作为“终极目标”。

“终极目标”是执行make的唯一目的,其所在的规则作为第一个被执行的规则。

而其它的规则是在完成重建“终极目标”的过程中被连带出来的。

所以这些目标所在规则在Makefile中的顺序无关紧要。

因此,我们书写的makefile的第一个规则应该就是重建整个程序或者多个程序的依赖关系和执行命令的描述。

4.1 一个例子我们来看一个规则的例子:foo.o : foo.c defs.h # module for twiddling the frobscc -c -g foo.c这是一个典型的规则。

看到这个例子,大家应该能够说出这个规则的各个部分之间的关系。

不过我们还是要把这个例子拿出来讨论。

目的是让我们更加明确地理解Makefile的规则。

本例第一行中,文件“foo.o”是规则需要重建的文件,而“foo.c”和“defs.h”是重建“foo.o”所要使用的文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ห้องสมุดไป่ตู้ How Does it Work?

• In Unix, when you type the command “make” the operating system looks for a file called either “makefile” or “Makefile”.

– There are exceptions to this but we will assume that you will always have the “makefile” or “Makefile” file resident in the directory of where your program resides.

– # – # This is a comment – projecte.exe : main.obj io.obj

# this is also a comment.

Rules

• Rules tell make when and how to make a file. The format is as follows:

– A rule must have a dependency line and may have an action or shell line after it. The action line is executed if the dependency line is out of date. – Example:

Shell Lines

• The indented lines (must have tab) that follow each dependency line are called shell lines. Shell lines tell make how to build the target. • A target can have more than one shell line. Each line must be preceded by a tab. • After each shell is executed, make checks to see if it was completed without error. • You can ignore this but I would not at this point.

How Does it Work?

• The “make” utility is recursive. For instance, if a very low level utility is the only thing changed, it could cause all of the modules within a program to be re-compiled. • After the utility finishes the file, it goes through and checks all of the dependencies again to make sure all are up to date.

hello.o: hello.cpp

g++ -c hello.cpp

– This shows hello.o as a module that requires hello.cpp as source code. If the last modified date of hello.cpp is newer than hello.o, than the next line (shell line) is executed. – Together, these two lines form a rule.

• You can override this by placing a “-” in front of the shell command, but I would not do this.

– Example: - gcc –o my my.o mylib.o

Macros

• Comes from the Greek word makros meaning large. • Basically it is a shorthand or alias used in the makefile • A string is associated with another usually larger string • Inside the file, to expand a macro, you have to place the string inside of $( ) . • The whole thing is expanded during execution of the make utility.

clean:

rm -rf *o hello

The Tree

hello

main.o

factorial.o

hello.o

factorial.o

factorial.cpp hello.cpp

main.cpp clean

Components of a Makefile

• • • • • • Comments Rules Dependency Lines Shell Lines Macros Inference Rules

•

• • • •

At the running of the make utility, the time and date when Project.exe was last built are compared to the dates when main.obj and io.obj were built. If either main.obj or io.obj have new dates, then the shell line after the dependency line is executed. The make process is recursive in that it will check all dependencies to make sure they are not out of date before completing the build process. It is important that all dependencies be placed in a descending order in the file. Some files may have the same dependencies. For instance, suppose that two files needed a file called bitvect.h. What would the dependency look like: main.obj this.obj: bitvect.h

• This file contains a series of directives that tell the “make” utility how to compile your program and in what order. • Each file will be associated with a list of other files by which it is dependent. This is called a dependency line. • If any of the associated files have been recently modified, the make utility will execute a directive command just below the dependency line.

Comments

• A comment is indicated by the character “#”. All text that appears after it will be ignored by the make utility until the end of line is detected. • Comments can start anywhere. There are more complex comment styles that involve continuation characters but please start each new comment line with an # and avoid the more advanced features for now. • Example

Simple Example

hello: main.o factorial.o hello.o g++ main.o factorial.o hello.o -o hello

main.o: main.cpp g++ -c main.cpp factorial.o: factorial.cpp g++ -c factorial.cpp hello.o: hello.cpp g++ -c hello.cpp

Dependency Lines

• The lines with a “:” are called dependency lines.

– – To the left are the dependencies To the right are the sources needed to make the dependency.

Lecture 5 Makefile

Introduction

• The “make” utility in Unix is one of the original tools designed by S. I. Fieldman of AT&T Bell labs circa 1977. There are many version. • What is “make”?: The tool is designed to allow programmers to efficiently compile large complex programs with many components easily. • You can place the commands to compile a program in a Unix script but this will cause ALL modules to be compiled every time. • The “make” utility allows us to only compile those that have changed and the modules that depend upon them.