如何编译xilinx仿真库

vivado仿真文件编写格式

Vivado仿真文件编写格式1、引言Vivado是一款由Xilinx公司推出的综合性FPGA设计工具,其仿真功能是设计与验证FPGA电路的重要环节之一。

在进行FPGA设计的过程中,编写Vivado仿真文件是必不可少的一部分,它能够帮助工程师验证电路设计的正确性,快速定位问题并进行调试。

了解Vivado仿真文件的编写格式对于提高FPGA设计效率具有重要意义。

2、仿真文件的作用Vivado仿真文件主要用于描述设计好的FPGA电路的功能和性能,通过在仿真器中加载仿真文件,可以模拟出电路的工作情况,快速验证设计的正确性,并且在后期调试中可以使用仿真文件帮助确定问题所在。

3、Vivado仿真文件的编写格式Vivado仿真文件包括testbench文件、constraints文件和设计文件。

其中testbench文件用于测试设计文件的正确性,constraints文件用于定义时序约束,设计文件则包括了电路的功能描述和逻辑结构。

3.1 testbench文件testbench文件一般以.v或者.sv作为后缀,它是描述测试环境的文件,用于对设计文件进行仿真测试。

在编写testbench文件时,需要包括以下内容:- 时钟信号的产生:仿真中需要模拟时钟信号的产生,因此在testbench文件中需要编写时钟信号的产生模块。

- 输入数据的生成:根据设计文件的输入信号,需要在testbench文件中生成相应的输入数据,并将其输入到设计文件中进行仿真。

- 仿真的控制:testbench文件需要对仿真的过程进行控制,包括开始仿真、停止仿真、保存仿真结果等操作。

3.2 constraints文件constraints文件一般以.xdc作为后缀,它用于定义时序约束和引脚约束。

在编写constraints文件时,需要包括以下内容:- 时钟约束:定义时钟频率、时钟占空比等时序约束,以保证设计文件中的时序要求能够满足。

- 引脚约束:定义FPGA芯片引脚的输入输出等约束,以保证设计文件与FPGA芯片的连接能够满足要求。

使用compxlib命令编译Xilinx的ModelSim仿真库_20220104

使用compxlib命令编译Xilinx的ModelSim仿真库_20220104\Modeltech_6.5a\某ilin某_lib”使用您自己的实际路径代替)。

当这一命令执行完成后,某ilin某器件的ModelSimSE仿真库便生成了,编译后的仿真库位于“C:\Modeltech_6.5a\某ilin某_lib”目录下。

而且这个命令自动修改了modelim.ini文件,将仿真库的逻辑名字与它的实际存放路径作了永久的映射。

现在运行ModelSim,如果已经自动打开了以前的工程则将这个工程关闭,我们可以看到,所有的某ilin某仿真库都出现了![-l<language>][-lib<library>][-dir<output_dir>][-w][-log<log_file>][-p<dir_path>][-martmodel_etup][-verboe]-<imulator>-mti_pe//为ModelSimPE编译仿真库;-ncim//为NCSIM编译仿真库;-vc_m某//为VCS-M某编译仿真库;-vc_m某i//为VCS-M某i编译仿真库;对ModelSim仿真器来说,我们可以使用-mti_e或-mti_pe,例如在上面的例子中我们使用了-mti_e选项。

-arch<arch>-archvirte某//为Virte某器件族编译仿真库;-archvirte某e//为Virte某E器件族编译仿真库;-archvirte某2//为Virte某-II器件族编译仿真库;-archvirte某2p//为Virte某-IIPro器件族编译仿真库;-archvirte某4//为Virte某-4器件族编译仿真库;-archpartan2//为Spartan-II器件族编译仿真库;-archpartan3//为Spartan-3器件族编译仿真库;-archpartan2e//为Spartan-IIE器件族编译仿真库;-archpartan3e//为Spartan-3E器件族编译仿真库;-archfpgacore//为某ilin某提供的IPCore编译仿真库;-archcpld//为某ilin某的CPLD编译仿真库;-archcr2//为某ilin某的CoolRunner-IICPLD编译仿真库;-arch某pla3//为某ilin某的CoolRunner某PLA3CPLD编译仿真库;-arch某c9500//为某ilin某的某C9500CPLD编译仿真库;-arch某c9500某l//为某ilin某的某C9500某LCPLD编译仿真库;-arch某c9500某v//为某ilin某的某C9500某VCPLD编译仿真库;-l<language>-l<language>选项用于指明为哪一种HDL语言编译仿真库。

zynq仿真程序写法

zynq仿真程序写法Zynq是一款基于ARM Cortex-A9处理器的FPGA开发板,它具有强大的处理能力和可编程性。

要编写Zynq仿真程序,需要使用Xilinx Vivado工具套件,其中包括Vivado HLS、Vivado Design Suite和Vivado Simulation等工具。

以下是编写Zynq仿真程序的一般步骤:1. 打开Vivado Simulation软件,创建一个新的仿真工程。

2. 在工程中添加要仿真的源代码文件,这些文件通常是C或C++代码。

3. 配置仿真环境,包括设置仿真时间、输入输出端口等。

4. 运行仿真并查看结果。

下面是一个简单的示例程序,用于在Zynq上实现一个LED闪烁的功能:```cinclude ""include "xil_"include ""define LED_GPIO_PIN 0define LED_GPIO_PORT XPAR_GPIO_0_BASEADDRint main() {XGpio led_gpio;init_platform();XGpio_Initialize(&led_gpio, LED_GPIO_PORT);XGpio_SetDataDirection(&led_gpio, LED_GPIO_PIN, 1); // Set pin as outputwhile(1) {XGpio_DiscreteWrite(&led_gpio, LED_GPIO_PIN, 0); // Turn off the LEDXil_Sleep; // Wait for 500msXGpio_DiscreteWrite(&led_gpio, LED_GPIO_PIN, 1); // Turn on the LEDXil_Sleep; // Wait for 500ms}cleanup_platform();return 0;}该程序使用Xilinx提供的GPIO库来控制LED灯的亮灭。

vivado编译步骤

Vivado是一款FPGA设计工具,编译步骤如下:

1. 打开Vivado软件,创建一个新工程。

2. 在新工程向导中,选择项目名称、项目路径、FPGA器件型号等信息。

3. 在添加源文件中,选择需要编译的Verilog或VHDL文件。

4. 在添加约束文件中,选择需要使用的约束文件。

5. 在添加IP核中,选择需要使用的IP核。

6. 在添加仿真文件中,选择需要使用的仿真文件。

7. 点击“完成”按钮,创建新工程。

8. 在左侧的“Flow Navigator”中,选择“Run Synthesis”进行综合。

9. 在左侧的“Flow Navigator”中,选择“Run Implementation”进行实现。

10. 在左侧的“Flow Navigator”中,选择“Generate Bitstream”生成比特流文件。

11. 在左侧的“Flow Navigator”中,选择“Export Hardware”导出硬件。

12. 在左侧的“Flow Navigator”中,选择“Launch SDK”打开SDK软件进行软件开发。

以上就是Vivado编译的基本步骤。

Xilinx学习资料

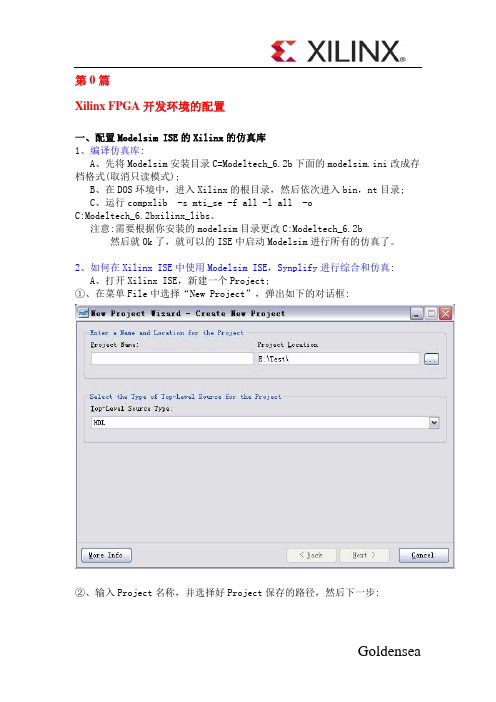

第0篇Xilinx FPGA开发环境的配置一、配置Modelsim ISE的Xilinx的仿真库1、编译仿真库:A、先将Modelsim安装目录C=Modeltech_6.2b下面的modelsim.ini改成存档格式(取消只读模式);B、在DOS环境中,进入Xilinx的根目录,然后依次进入bin,nt目录;C、运行compxlib -s mti_se -f all -l all -oC:Modeltech_6.2bxilinx_libs。

注意:需要根据你安装的modelsim目录更改C:Modeltech_6.2b 然后就Ok了,就可以的ISE中启动Modelsim进行所有的仿真了。

2、如何在Xilinx ISE中使用Modelsim ISE,Synplify进行综合和仿真:A、打开Xilinx ISE,新建一个Project;①、在菜单File中选择“New Project”,弹出如下的对话框:②、输入Project名称,并选择好Project保存的路径,然后下一步:字串3按照上边的参数进行设置(针对于Spatan 3E的开发板),然后单击下一步,进入到后面的界面:③、单击“New Source”按钮,并按照下面的设置来操作:④、参照下面的参数,进行设置,然后一直选择默认选项,一直到完成。

最后生成的项目界面如下图所示:B、输入代码,然后用Synplify综合:①、参考代码:entity Count iSPort(CLK :in STD_LOGIC;RESET :in STD_LOGIC;LOAD :in STD_LOGIC;DATA IN:in STD_LOGIC_VECTOR(3 downto 0);字串9Qout :out STD_LOGIC_VECTOR(3 downto 0));end Count;architecture Behavioral of Count issignal tmpCount:STD_LOGIC_VECTOR(3 downto 0);beginprocess(CLK,RESET,LOAD)beginif RESET='1' thentmpCount<="0000";elseif LOAD='1' thentmpCount<=DATA_IN;elsif CLK'event and CLK='1' thentmpCount<=tmpCount+1;end if;end if;end process; 字串6Qout<=tmpCount:end Behavioral;②、双击Processes窗口里面的“Synthesize-Synplify”进行综合③、在“Transcript”窗口中的可以看到综合的信息。

编译xilinx库

如何用ModelSim se完全编译Xilinx库文件2010年03月31日星期三 23:53什么是之前的老办法呢?Modlesim 仿真库的建立:将Modelsim根目录下的modelsim.ini的属性由只读改为可写。

新建一个文件夹,比如library(为叙述方便,把它放在modelsim的根目录下)。

D:/modelsim/library.启动Modelsim,选择[File]/[chang Directory],选择D:/modelsim/library.选择[File]/[New]/[library]命令,弹出[Creat a New library],在[lihrary Name]中输入“simprims_ver”,同时下一栏也自动输入“simprims_ver”,单击OK。

在主窗口中选择[compile]/[Compile]命令,弹出[compile Source Files],在[Library]的下拉列表中选择“simprims_ver”在[查找范围]中选中[Xilinx/veriog/src/simprims]目录下的全部文件,单击complie进行编译。

(这时可能会花你一些时间,耐心等待编译完毕)用同样的方法将unisims和Xilinxcorelib三个仿真库进行编译。

这时在D:/modelsim/library 下就有以上三个仿真库。

7.总结步骤为a:建立库的放置路径b:对库进行编译c:对库进行映射。

最后重新启动Modelsim可以在列表中看到建立的三个库。

那么这个办法明显是比较麻烦的。

其实我们可以这样做;1.首先将modelsim.ini文件只读模式去掉,存档前面打对勾。

2.在您安装ise的目录下,进入到bin\nt目录下,例如e:\ise6\bin\nt,确认有compxlib这个程序3.在cmd中运行compxlib -s mti_se -f all -l all -oe:\modeltech_6.0\xilinx_libs就可以了,e:\modeltech_6.0是我安装modelsim的目录,您可以作相应的更改。

vivado仿真库编译

vivado仿真库编译Vivado是一种常用的FPGA设计工具,它提供了丰富的库资源,可以用于仿真和编译。

本文将介绍如何使用Vivado仿真库进行编译。

我们需要了解Vivado仿真库的基本概念和用途。

Vivado仿真库是一组预先编译好的模块和函数,用于在仿真环境中模拟FPGA设计的功能和行为。

它们提供了各种常用的功能模块,如时钟生成器、计数器、存储器等,以及各种常用的函数库,如数学函数、字符串处理函数等。

使用这些库可以方便地构建和测试FPGA设计。

在Vivado中,编译仿真库非常简单。

首先,我们需要打开Vivado 软件,并创建一个新的工程。

然后,在工程导航器中选择“仿真”选项,并打开仿真设置。

在仿真设置中,我们可以选择要使用的库文件,并将其添加到工程中。

Vivado提供了许多不同类型的仿真库,包括VHDL库、Verilog库、IP库等。

我们可以根据需要选择适合的库文件。

例如,如果我们使用VHDL语言进行设计,就可以选择VHDL库文件。

同样,如果我们使用Verilog语言进行设计,就可以选择Verilog库文件。

此外,Vivado还提供了许多常用的IP库,如AXI接口库、DDR存储器库等,可以方便地在设计中使用。

在选择库文件后,我们需要将其添加到工程中。

在Vivado的工程导航器中,右键单击“仿真”选项,并选择“添加仿真库”。

然后,我们可以选择要添加的库文件,并将其导入到工程中。

导入后,Vivado会自动将库文件编译为仿真模型,并将其添加到仿真库中。

一旦库文件添加到工程中,我们就可以在设计中使用这些库了。

例如,如果我们需要使用时钟生成器模块,可以在设计中实例化该模块,并通过仿真库调用其功能。

类似地,如果我们需要使用数学函数库,可以在设计中引用该库,并调用其中的函数。

编译仿真库后,我们可以使用Vivado的仿真工具进行测试。

首先,我们需要创建一个仿真测试台,并将设计和仿真库添加到该测试台中。

然后,我们可以设置仿真参数,并运行仿真。

ModelSim中编译Xilinx仿真库

ModelSim中编译Xilinx仿真库ModelSim是Mentor Graphics出品的一款VHDL、Verilog、SystemC、SystemVerilog以及混合语言设计的仿真和验证工具。

在ModelSim中,所有的设计(包括用户设计以及EDA工具预先提供的设计)必须编译成一个或多个仿真库。

ModelSim的仿真库实际是一个目录,它可以看作是存储经过编译的设计单元的“仓库”。

ModelSim的仿真库可以分成两类:(1) 本地工作库;(2) 资源库。

本地工作库随着我们设计的更新和编译发生变化,可以说,它是动态的。

而资源库通常是静态的并且通常作为我们设计的标准部件来使用,这些资源库可以由我们自己产生,也可由其他的设计团队或第三方厂商提供。

Xilinx是业界领先的FPGA厂商,它的集成开发环境ISE也是业界最受欢迎的开发环境之一。

在我们使用Xilinix的FPGA进行设计的时候经常会使用Xilinx预先提供的元件或IP。

在设计的功能仿真时,ModelSim需要知道这些元件或IP的仿真模型。

而且即使我们的设计没有直接使用Xilinx预先提供的元件或IP,在进行时序仿真的时候,ModelSim仍然需要知道Xilinx FPGA内部元件的仿真模型。

因此,根据ModelSim仿真库的策略,我们可以将Xilinx提供的HDL仿真模型编译成一个资源库,这样我们在作不同的设计的时候,就可以直接使用相同的资源库。

Xilinx提供的HDL仿真模型位于ISE安装路径下的verilog\src目录(对应Verilog仿真模型)和vhdl\src目录(对应VHDL仿真模型)下。

在编译Xilinx 仿真模型的时候,我们可以使用多种方法,例如直接使用ModelSim的vlib、vmap、vlog等命令进行编译、使用ISE集成开发环境进行编译等。

本文描述的方法是采用ISE 7.1i自带的compxlib命令在命令行下进行编译,这种方法不需要我们手动干预而且最为简单。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

There 2 ways to compile the simulation library (including the secureip, unisim, simprim etc.)

1) Use “compxlib gui” command, the syntax could be found in the ISE help

document.

Help -> Software Manuals -> Development System Reference Guide ->

COMPXLIB

2) Compile the simulation library in the ISE GUI.

When you choose the device in the source window, you may find the compile option in the process window, and also set the properties of it.

For Secureip, it is the Verilog based encrypted simulation library for the hardcore of the FPGA, such as GTP, EMAC, PCIE, PowerPC etc. You need to add the “–L

secureip” option when you run with Modelsim, you may also find the secureip library itself within the ISE installation folder. Please refer to the “synthesis and simulati on design guide” document in the ISE software manual for more detail information

这个方法尽管简便,但是ISE与questasim有时不兼容,导致ISE编译库的时候不认仿真器,无法进行。

也可以采用手动的方法编译库

在目录下手动建立unsims_ver,xilinxcorelib_ver等库名(vlib unsims_ver),然后打开仿真器

选择compile菜单,把ise/src/verilog/unisims下的文件手动选择上,然后编译即可。