6简单时序电路实验

《电子技术基础》第6章时序逻辑电路的分析与设计-1

6.1 时序逻辑电路的基本概念

1. 时序电路的一般化模型

I1 Ii

O1

Oj

Sm 特点: Ek 1)时序逻辑电路由组合电路(逻辑门)和存储电路( 一般由触 发器构成) 组成。 2)电路的输出由输入信号和原来的输出状态共同决定.

4/9/2019 12:58:22 PM

… … S1 …

… E1 … …

组合电路

1/0 1/0 1/0

01 01 0/0 10 10

00

11

10

01

0/1 11 11

1/1

0/0

电路进行减1计数 。 电路功能:可逆4进制计数器 Y可理解为进位或借位端。

4/9/2019 12:58:22 PM

D2 Q

n 1

(3) 根据状态方程组和输出方程列出状态表

Sn→Sn+1

S = Q2Q1Q0

Q

n 1 0

Q Q

n 1

n 0

Q

n 1 1

Q

n 0

n 1 Q2 Q1n

状态表

n 1 n n 1 n 1 n Q Q Q Q Q Q 0 1 0 1 2

n 2

(4) 画出状态图 0 1 0 1 0 1 0 1 1 0 0 0 1 0 0 0

存储电路

时序电 路输入 信号

I1

Ii

O1 Oj

组合电路

时序电 路输出 信号

存储电路激 励信号(触发 器的输入)

… …

… …

存储电路输 出信号 (电路状态S) 各触发器的状态Q

S1 Sm …

E1

… Ek

存储电路

各信号之间的逻辑关系方程组为:

O = F1(I,Sn) E = F2

第6章 时序逻辑电路

J 和 K 接为互反,相当于一个D触发器。时钟相连 是同步时序电路。

电路功能: 有下降沿到来时,所有Q端更新状态。

2、移位寄存器 在计算机系统中,经常要对数据进行串并转换,移 位寄存器可以方便地实现这种转换。

左移移位寄存器

•具有左右移位功能的双向移位寄存器

理解了前面的左移移位寄存器,对右移移位寄存器 也就理解了,因位左右本身就是相对的。实际上,左右 移位的区别在于:N触发器的D端是与 Q N+1相连,还是 与Q N-1相连。

第六章 时序逻辑电路

如前所述,时序逻辑电路的特点是 —— 任一时刻 的输出不仅与当前的输入有关,还与以前的状态有关。

时序电路以触发器作为基本单元,使用门电路加以 配合,完成特定的时序功能。所以说,时序电路是由组 合电路和触发器构成的。

与学习组合逻辑电路相类似,我们仍从分析现成电 路入手,然后进行时序逻辑电路的简单设计。

状态化简 、分配

用编码表示 给各个状态

选择触发器 的形式

确定各触发器 输入的连接及 输出电路

NO 是否最佳 ?

YES

设计完成

下面举例说明如何实现一个时序逻辑的设计:

书例7-9 一个串行输入序列的检测电路,要求当序

列连续出现 4 个“1”时,输出为 1,作为提示。其他情 况输出为 0。

如果不考虑优化、最佳,以我们现有的知识可以很

第二步: 状态简化

前面我们根据前三位可能的所有组合,设定了 8 个

状态A ~ H,其实仔细分析一下,根本用不了这么多状态。

我们可以从Z=1的可能性大小的角度,将状态简化为

4 个状态:

a

b

c

d

A 000

B 100

D 110

第6章 时序逻辑电路(sequential logic)

第6章 时序逻辑电路(Sequential Logic)Sequential logic指的是接收到一触发信号才会改变输出的电路,由于要在触发信号出现时才会改变输出情况,因此在触发信号未出现时具有记忆功能。

在VHDL中,sequential logic一般都会写在process之中,下面会将process 的语法做一简单的介绍,并会描述各种不同的sequential logic的表示方式。

6-1 Process的语法结构Process是sequential logic必须使用的语法,以下是process的语法结构。

[ Label : ]process[(sensitivity list)]Declaration Zone;begin .process Body Zone;end process [Label];在process的语法结构中,第一个出现的是Label,它的中括号表示其可以被省略。

Label的目的在于更能让人一目了然地知道之后的process是什么作用,既然要有这种目的,其命名自然相当重要。

否则让人看后更迷糊的1abel还不如省略的好。

在process之后放在中括号内的小括号叫做sensitivity list,是一个敏感信号的列表,当括号内的信号逻辑状态改变时,process的内部才会开始执行动作。

在process之后与begin之前所包含的区域我们称之为Declaration Zone,其作用在于声明一些在这个process中才有的特殊对象,如variable ,file等。

在begin之后的则是process要处理信号的区域,也是整个process的核心区域。

当完成信号状态的设定后,要有end process作为一个process的结束。

若之前使用了1abel的话,在end process之后还要把label补上。

以下是一个没有特别声明的process。

ARstDFF : process (rst, clk)beginif rst = ‘0’ thenq <= ‘0’;elsif clk =’1’ and clk’event thenif ce = ‘0’ thenq <= d;end if;end if;end process ARstDFF;在本例中ARstDFF是一个1abel,其主要目的是在描述后面的process是一个Asynchronise Reset D_type Flip-flop(异步复位D型触发器)。

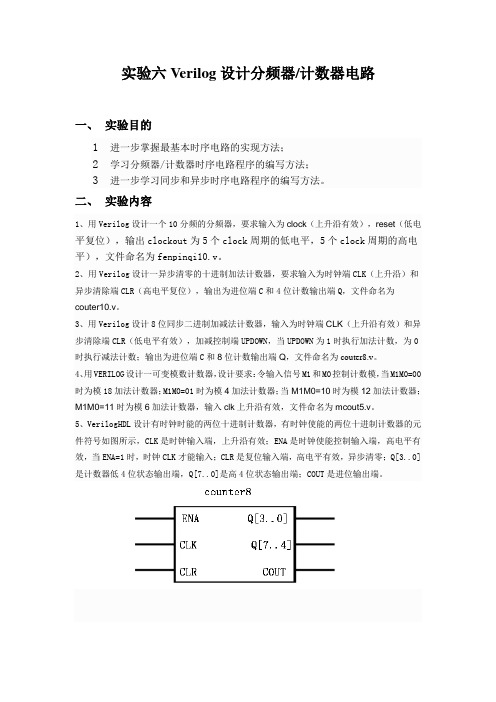

实验六Verilog设计分频器计数器电路

实验六Verilog设计分频器/计数器电路一、实验目的1进一步掌握最基本时序电路的实现方法;2学习分频器/计数器时序电路程序的编写方法;3进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为5个clock周期的低电平,5个clock周期的高电平),文件命名为fenpinqi10.v。

2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。

三、实验步骤:第一个实验:1、打开QuartusII,新建一个工程f_fenpinq10yjq2、新建一个Verilog HDL文件3、输入程序:module fenpinqi10(clk,reset,clkout);input clk,reset;output clkout;reg clkout;reg[2:0] cnt;always @(posedge clk , negedge reset)beginif(!reset)begin clkout<=0;cnt<=0;endelse if(cnt==4)begin cnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule4、设置顶层实体名(点settings>general >下拉选fenpinqi10)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真结果如下:总结:仿真结果与实验一的题意相符,所以仿真正确。

时序实验报告总结

时序实验报告总结时序实验报告总结时序实验是计算机科学中的一项重要实验,旨在通过设计和实现时序电路,来加深对数字电路和时序逻辑的理解。

本文将对我在时序实验中的学习和总结进行分享。

实验一:时序电路设计在时序电路设计实验中,我通过学习时序逻辑的基本概念和设计原理,成功完成了一个简单的时序电路设计。

通过该实验,我深入理解了时钟信号、触发器和状态机的概念,并学会了使用Verilog语言进行时序电路的建模和仿真。

实验二:时序电路优化时序电路优化实验是进一步提高时序电路设计能力的关键一步。

在该实验中,我通过对已有电路的分析和优化,实现了电路的性能提升。

通过优化电路的关键路径,我成功降低了电路的延迟,并提高了电路的工作速度。

实验三:时序电路测试时序电路测试是保证电路正确性的重要环节。

在该实验中,我学会了使用测试向量和模拟器对时序电路进行测试。

通过设计全面的测试用例和检查电路的输出波形,我成功发现和解决了电路中的一些问题,并提高了电路的稳定性和可靠性。

实验四:时序电路综合时序电路综合是将逻辑电路转化为物理电路的过程。

在该实验中,我学会了使用综合工具将Verilog代码转化为门级电路,并通过对综合结果的分析和优化,提高了电路的面积效率和功耗性能。

实验五:时序电路布局与布线时序电路布局与布线是将逻辑电路映射到芯片上的过程。

在该实验中,我学会了使用布局与布线工具对电路进行布局和布线,并通过对布局和布线结果的分析和优化,提高了电路的可靠性和稳定性。

实验六:时序电路验证时序电路验证是验证电路设计的正确性和可靠性的重要环节。

在该实验中,我学会了使用仿真和验证工具对电路进行验证,并通过对验证结果的分析和优化,提高了电路的正确性和稳定性。

通过以上实验,我深入了解了时序电路的设计、优化、测试、综合、布局与布线以及验证等方面的知识和技能。

通过实践和总结,我不仅提高了对时序电路的理解和掌握,还培养了问题解决和创新能力。

时序实验的学习过程中,我还遇到了一些挑战和困惑。

第六章 时序逻辑电路

Y Q* 0 0 0 1 0 1 0 0 0 1 1

0 0 1 0 0

图6.2.2

6.2.时序逻辑电路的分析方法

三、时序图: 在时钟脉冲 序列的作用下, 电路的状态、输 出状态随时间变 化的波形叫做时 序图。由状态转 换表或状态转换 图可得图6.2.3所 示 图6.2.3

6.2.时序逻辑电路的分析方法

K1 1

6.2.时序逻辑电路的分析方法

(2) 状态方程:

JK触发器的特性方程

Q J Q K Q

*

将驱动方程代入JK触发器的特性方程中,得出电 路的状态方程,即

K1 1 J 1 ( Q 2 Q 3 ) , K 2 ( Q 1Q 3 ) J 2 Q1 , J QQ , K 3 Q2 1 2 3

设初态Q3Q2Q1=000,由状态方程可得:

CLK Q3 Q2 Q1 Q *3 0 0 0 0 0 1 0 0 1 0 2 0 1 0 0 3 4 5 6 0 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 0 0

Q *2 Q *1 Y 0 1 0

Q 1 * ( Q 2 Q 3 ) Q 1 Q 2 * Q 1 Q 2 Q 1Q 3 Q 2 Q * Q Q Q Q Q 1 2 3 2 3 3

1 1 0 0 1 0 0

0 1 0 1 0 0 0

0 0 0 0 0 1 1

由状态转换表可知,为七进制加法计数器,Y为进位 脉冲的输出端。

6.2.时序逻辑电路的分析方法

二、状态转换图: 将状态转换表以图形的方式 直观表示出来,即为状态转换图 由状态转换表可得状态转换图 如图6.2.2所示

CLK Q3 Q2 Q1 0 0 0 0 1 0 0 1 2 0 1 0 3 4 5 6 0 1 1 1 1 1 1 0 0 0 1 1 0 1 1

数字电路与逻辑设计微课版(第6章 时序逻辑电路)教案

第6章时序逻辑电路本章的主要知识点时序逻辑电路的基本知识、时序逻辑电路的分析和设计、关于自启动的修正问题、常用的中规模时序电路。

1.参考学时10学时(总学时32学时,课时为48课时可分配12学时)。

2.教学目标(能力要求)●掌握同步时序逻辑电路的分析和设计方法;●掌握电路挂起的修正方法;●掌握常用的中规模时序逻辑电路(计数器、寄存器)的外部特性及使用方法;●掌握脉冲异步时序逻辑电路的分析和设计方法;●掌握中规模时序逻辑电路的分析和设计方法。

3.教学重点●同步时序逻辑电路的设计:包括设计中的原始状态图、状态表、状态化简、状态编码、确定激励函数和输出函数等;●同步时序逻辑电路的自启动的分析:能根据设计好的电路分析电路是否存在自启动的问题,并学会修正它。

●脉冲异步时序逻辑电路的分析和设计方法:了解和同步时序逻辑电路的分析和设计方法的差异性,并熟练掌握脉冲异步时序逻辑电路的分析和设计方法●中规模时序逻辑电路的外部特性及使用方法:通过理论分析来学习常用中规模时序逻辑电路的外部特性及使用方法,通过具体实例来学习中规模时序逻辑电路的分析和设计方法4.教学难点●原始状态图:学生开始不知道如何增加状态,什么时候增加状态●自启动的修正:学生能分析出挂起,但是对于修正比较困难●脉冲异步时序逻辑电路的分析:当脉冲异步时序逻辑电路的存储电路是没用统一时钟端的钟控触发器时,如何分步找到每个触发器的时钟的跳变时刻对学生来说是一大挑战●计数器的使用方法:掌握置数法、清零法、级联法实现任意模的计数器5.教学主要内容(1)时序逻辑电路概述(15分钟)(2)小规模时序逻辑电路分析(120分钟)➢小规模时序逻辑电路的分析方法和步骤➢小规模同步时序逻辑电路的分析➢小规模异步时序逻辑电路的分析(3)小规模时序逻辑电路设计(180分钟)➢小规模时序逻辑电路的设计方法和步骤➢小规模同步时序逻辑电路的设计➢小规模异步时序逻辑电路的设计(4)常用中规模时序逻辑电路(45分钟)➢集成计数器➢寄存器(5)中规模时序逻辑电路的分析和设计(90分钟)➢中规模时序逻辑电路的分析➢中规模时序逻辑电路的设计6.教学过程与方法(1)时序逻辑电路概述(15分钟)简要介绍时序逻辑电路的结构、特点、分类和描述方法等。

时序逻辑电路实验报告

时序逻辑电路实验报告一、实验目的1、掌握时序逻辑电路的设计过程。

2、了解时序电路器件的构成,用触发器设计一些简单的时序电路。

二、实验原理如果电路任一时刻的输出不仅取决于当时的输入信号,还取决于电路原来的状态,或者说还与以前的输入信号有关,具备这种逻辑功能特点的电路我们称之为时序逻辑电路。

根据时序电路的时钟信号是否相同,即触发器是否同时翻转,又可以把时序电路分为异步时序电路和同步时序电路。

分析一个时序电路,就是要找出给定时序电路的逻辑功能。

步骤如下:1、从给定逻辑图得出每个触发器的驱动方程;2、由驱动方程得到触发器的状态方程,从而得到时序电路的状态方程组;3、根据逻辑图写出时序电路的输出方程。

4、根据得到的方程式画出逻辑图。

5、检查电路是否能够自启动,进行逻辑修改,实现自启动。

而异步时序电路和同步时序电路的分析方法又不尽相同,在异步时序电路中,状态发生转换时,并不是所有触发器都翻转,只有有时钟信号的才计算触发器次态,没有时钟信号的触发器保持状态不变。

如果想使电路的逻辑功能一目了然,可以用状态转换真值表、状态转换图和时序图等三种方法来表示,他们之间可以相互转换。

为一个四位扭环计数器和其工作波形,并且该计数器可以自行启动。

其工作状态为0000→0001 →0011 →0111 →1111 →1110 →1100 →1000,然后再回到0000重新开始计数。

三、实验器件74175是四D型触发器,有公共的清零端和公共时钟信号,包含四组相同的D触发器,上升沿触发,清零端低电平有效。

四、实验内容1、用D触发器7474设计一个异步减法计数器,验证功能并画出逻辑图。

2、制作任意进制加法计数器。

(7进制计数器,同步)3、用JK触发器7476设计一个九进制同步加法计数器,搭建电路验证其功能,并画出逻辑图。

4、用JK触发器和门电路设计111序列信号检测器,有一个信号输入端口X,一个输出端口Y,当X输入序列111时,输出Y=1。