CompacatPCI Express体系结构技术分析

CompactPCI Express总线特点

Compact PCI Express总线特点Compact PCI Express最本质的理念在于可以用欧卡规格实现PCI Express总线的兼容,可以说Compact PCI Express的电气特性规范实质上就是PCI Express 的电气规范。

与早期的PCI体系相比,CompactPCI Express最突出的特点表现在以下几个方面:(1)采用点对点的串行互联技术取代PCI的并行总线结构互联技术,不仅保证了高频率的工作能力,还可以为每一设备分配独享的通道带宽,保证了每个设备的带宽资源,提高了数据传输率。

(2)Compact PCI Express采用串行数据传输机制,将110根Compact PCI 并行数据地址线、控制线、仲裁线、时钟线、系统复位线、中断线减少到4对差分传输线,且串行机制中包括PCI Express所有通信协议。

总线数量的减少使得产品化过程中的PCB制作、布线变得更容易。

同时,Compact PCI Express背板FR4 PCB布线长度可达50厘米,而Compact PCI却局限于PCB布线长度、PCI桥扩展机制的影响。

(3)采用全双工工作模式,发送数据和传输数据可以同时进行,相比于PCI 在一个时钟周期内只能进行单向传输,提高了数据传输效率。

Compact PCI Express 板间互联采用Link点对点连接,每一个Link可由X1、X2、X4、X8、X12、X16、X32个Lane连接,每一个Lane由一对TX差分信号对和一对RX差分信号对组成,数据双向传输。

X1 Lane单向速度为250Mbytes/s,双向即为500Mbytes/s,而传统的33MHz/32Bit Compact PCI总线仅为132 Mbytes/s。

(4)Compact PCI Express采用点对点的互联,Compact PCI则是共享总线带宽,这样,Compact PCI Express速度优势更为明显。

PCIe总线架构深入剖析

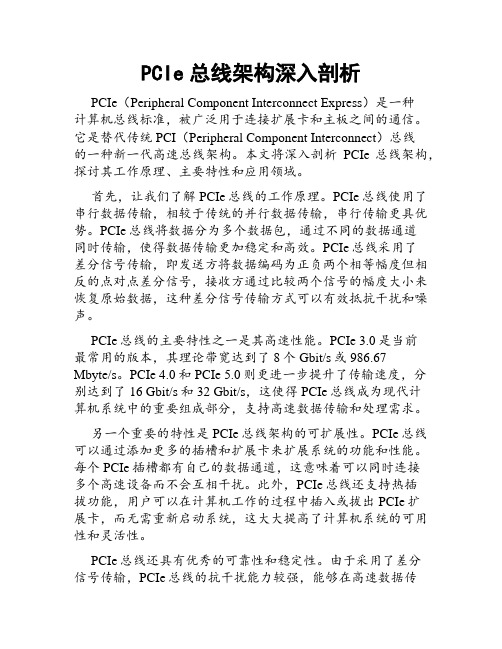

PCIe总线架构深入剖析PCIe(Peripheral Component Interconnect Express)是一种计算机总线标准,被广泛用于连接扩展卡和主板之间的通信。

它是替代传统PCI(Peripheral Component Interconnect)总线的一种新一代高速总线架构。

本文将深入剖析PCIe总线架构,探讨其工作原理、主要特性和应用领域。

首先,让我们了解PCIe总线的工作原理。

PCIe总线使用了串行数据传输,相较于传统的并行数据传输,串行传输更具优势。

PCIe总线将数据分为多个数据包,通过不同的数据通道同时传输,使得数据传输更加稳定和高效。

PCIe总线采用了差分信号传输,即发送方将数据编码为正负两个相等幅度但相反的点对点差分信号,接收方通过比较两个信号的幅度大小来恢复原始数据,这种差分信号传输方式可以有效抵抗干扰和噪声。

PCIe总线的主要特性之一是其高速性能。

PCIe 3.0是当前最常用的版本,其理论带宽达到了8个Gbit/s或986.67Mbyte/s。

PCIe 4.0和PCIe 5.0则更进一步提升了传输速度,分别达到了16 Gbit/s和32 Gbit/s,这使得PCIe总线成为现代计算机系统中的重要组成部分,支持高速数据传输和处理需求。

另一个重要的特性是PCIe总线架构的可扩展性。

PCIe总线可以通过添加更多的插槽和扩展卡来扩展系统的功能和性能。

每个PCIe插槽都有自己的数据通道,这意味着可以同时连接多个高速设备而不会互相干扰。

此外,PCIe总线还支持热插拔功能,用户可以在计算机工作的过程中插入或拔出PCIe扩展卡,而无需重新启动系统,这大大提高了计算机系统的可用性和灵活性。

PCIe总线还具有优秀的可靠性和稳定性。

由于采用了差分信号传输,PCIe总线的抗干扰能力较强,能够在高速数据传输中保持稳定的连接。

此外,PCIe总线还支持错误检测和重新发送机制,确保数据的完整性和准确性。

pcie体系结构标准教材

pcie体系结构标准教材

目前市场上主要有三本关于PCIe体系结构标准的教材:

1.《PCI Express System Architecture》(第一版,第二版,第三版):这是PCI-SIG组织编写的官方教材,详细介绍了PCIe的原理、架构、传输协议和电气特性等,适合需要深入了解PCIe技术的读者。

2.《PCI Express Technology

3.0》:作者Ravi Budruk和Don Anderson,是PCI-SIG认证的PCIe教材,详细介绍了PCIe 3.0版本的架构、规范和协议,同时还提供了大量实例和案例分析。

3.《PCI Express System Architecture》:作者Minden,是一本针对初学者的PCIe教材,从基础概念出发,逐步介绍了PCIe 技术的发展、架构和功能。

书中还包含了实际应用案例和示例代码,帮助读者更好地理解和应用PCIe技术。

根据个人的学习需求和水平,可以选择适合自己的教材进行学习和参考。

基于Compact PCI Express总线的计算机体系架构研究

1 6

基 于 C mp cP x rs o a tCIE pe s总线 的计 算 机体 系架 构 研究

鉴 于 如 此 众 多 的优 势 , CIE总线 有 着 巨 大 的 发 展 潜 力 , CP —

其 在 一 般 用 途 的定 位 使 其 在 灵 活 性 方 面 具 有 明 显 的 优 势 ,这 确 保 了它 有 着 广 泛 的应 用 前 景 。 3 C mp cP x rs o a t CI pe s总线 计 算 机 体 系 结构 E 31 系 统 体 系结 构 . C mp cP x rs o a t CI pe s总线 计 算 机 总线 在 两 个 设 备 之 间 点 E 对 点 串行 互 联 ,与 P 及 CP 总线 计 算 机所 有 设 备 共 享 同一 CI CI 条 总线 资 源不 同 , P I E总 线 采 用 点 对 点 技 术 , 够 为 每 一 块 C C— 能

bo d ar an hi sp ed er b . l tde cr te or ou d ft e y t m b e on d gh e s i al usAt as, s i be h f egr n o h s s e as d Compa t E r s bu c PCI xp e s s Key wor : m p t E pr s , chtc u e,wi dsCo ac PCI x e sar i t r s t e ch

高 了数 据 传 输 速 度 。其 在 物 理 层 上 提 供 的 1 3 ~ 2速 可 选 信 道 带

宽 特 性 更 使 其 可 以轻 松 实 现 近 乎 “ 限 ” 无 的扩 展 传 输 能 力 。

表 1 CP — CIE总 线峰 值 带宽

PCIExpress系统体系结构标准教材

PCIExpress系统体系结构标准教材第1章体系结构展望1.1 第⼀代总线:ISA,EISA,VESA第⼆代总线:PCI, AGP, PCI-X第三代总线:PCIE1.2 PCIE的存储器、IO和配置地址空间与PCI和PCI-X的地址空间相同。

现有的驱动⽆需改动可以在PCIE运⾏中断控制器在南桥33MHz的PCI峰值带宽为4KB*33=133MB/s1.3 I/O总线体系结构1) PCI设备使⽤4个中断信号(INTA#,B,C,C) 触发中断控制器的中断请求,然后中断控制器向CPU声明INTR信号2) 3种类型的地址空间配置地址空间:每个PCI功能最多有256B, CPU通过北桥的IO映射数据和地址端⼝间接访问配置空间3)最新⼀代的intel PCI芯⽚组,把南北桥换成了MCH, ICH4)PCI-X ⽐PCI 频率更⾼,PCI-X设备可以插⼊PCI插槽,反之亦然。

PCI-X 峰值达到1064MB/s第2章体系结构概述2.1 PCIE 事务通信涉及处理层数据包(Transaction Layer packet, TLP) 的收发PCIE事务包括:1)存储器事务,2)IO事务,3)配置事务,4)消息事务2.2 PCIE的设备层有处理层,数据链路层,物理层;对应的数据包为TLP, DLLP, PLP1)处理层有虚拟信道缓冲区(VC缓冲区),流控,TLP排序,QoS也在此层(PCI不⽀持QoS);缓冲区⽤于数据的收发,流控避免缓冲区溢出;流控是硬件⾃动管理的;QoS 指的是以不同的优先级,确定的延迟及带宽路由不同应⽤程序的数据包通过结构的能⼒。

如视频对时间要求⾼,SCSI对正确性要求⾼,所以视频数据包的优先级⾼。

VC仲裁会优先通过视频数据包 2)流量类别TC,是数据包的⼀个TLP头字段, TC会映射到虚拟信道VC可实现最多8个VC缓冲区,2.3 ⾮报告存储器读事务两个阶段:请求者发送存储器读请求TLP给完成者;接收来⾃完成者的带数据的完成。

CompacatPCIExpress体系结构技术分析

随着信息技术和计算机技术的飞速发展,未来社会将是一个高效的数字化社会。

大量的数据、语音、图形和图像等信息需要进行实时感知和处理,应用需求对计算机的带宽、吞吐量和可扩展的体系结构提出来越来越高的要求。

在计算机的体系结构技术中,计算机I/O技术始终是一个十分重要的关键技术。

其技术特性决定了计算机I/O的处理能力,进而决定了计算机的整体性能以及应用环境。

从根本上讲,无论现在还是将来,I/O技术都将制约着计算机技术的应用与发展,尤其在高端计算领域。

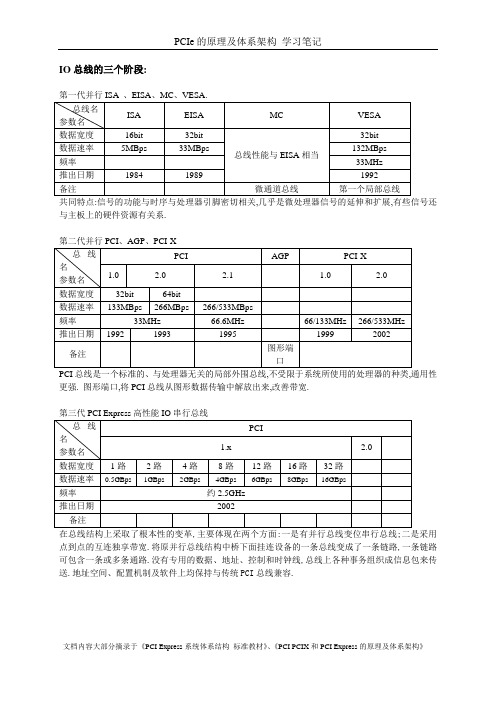

计算机总线体系结构经过了三代的发展。

第一代总线包括ISA、EISA、VESA和微通道(MicroChannel)总线,第二代总线包括PCI、AGP和PCI-X总线,PCIExpress是用来互连计算和通信平台应用中外围设备的第三代高性能I/O总线。

虽说PCI自20世纪90年代初诞生以来,已经成为计算机最成功的总线互连技术之一,但由于PCI并行体系结构的局限,使它在性能和可扩展性方面难以有较大的提升,因此PCIExpress技术应运而生。

在过去的两年里,美军基于紧凑型CompactPCI的应用越来越广泛,频繁的数据输入/输出,用户对数据总线带宽提出了新的要求,目前美军也正在计划用PCIExpress总线技术代替PCI技术,解决现有的计算机局限于PCI体系结构,带宽不够宽,伸缩性不强,信息吞吐量不够大,不能实时处理语音、数据图像等大容量信息的问题,同时,从计算机的模块化、可热插拔、高可靠性和坚固性出发,美军也正对基于CompactPCI结构的PCIExpress计算机展开研究。

1国内外研究现状由于PCIExpress技术是第三代先进的I/O总线技术,代表未来十年计算机总线技术的发展方向,因此各国都在对该项技术展开深入的研究。

1.1国内研究现状目前,国内成立了计算机行业协会PICMG/P.R.C分会,密切跟踪国际最新计算机技术和标准。

国内在基于CompactPCI结构的计算机和网络产品的研发方面有较好的技术基础,基于CompactPCI结构的路由器等网络产品已经在国内外市场广泛应用,基于CompactPCI结构的计算机也批量装备部队。

PCI Express体系结构

PCI Express体系结构PCI Express1/0互连技术是一种新兴的用于芯片间和板间互连的、高性能、点到点、基于报文交换的新型1/0互连技术,它作为新一代的I/0体系结构和互连技术,主要具有如下技术特点:(1)采用基于报文交换的点对点高速串行传输技术,以及基于交换的拓扑结构替代传统的共享总线结构,提供高带宽、可扩展的1/0互连。

单向数据传输速率可达到2.5Gb/S,峰值带宽可达到I0Gb/s。

(2)支持多重市场以及新兴应用:统一式I/0架构,支持台式机、移动设备、服务器、通信平台、工作站以及嵌入型设备。

(3)兼容PCI的软件模式:不需要任何修改就能引导现有的操作系统,具有与PCI兼容的配置与设备驱动程序接口,降低了开发成本。

(4)支持多平台连接类型:芯片对芯片,板对板等。

(5)支持多种先进功能:流控机制、电源管理、RAS技术、支持热插拔、服务质量、可扩展性等。

图1 PCI系统拓扑结构传统的PCI系统如图1所示,采用多个设备共享一个数据传送通路共享总线方式,使用集中式仲裁式结构,一个设备必须先从“中心仲裁器”进入共享PCI 总线,而后才可以通过PCI总线将数据传输给目标设备,并且在任何时间只能实现单向传输。

因此,一旦总线上挂接的设备增多,则每台设备的实际带宽就会下降,所以不能有效的满足对内部与外部带宽和性能都要求很高的应用。

PCI Express系统拓扑结构PCI Express系统则采用点对点连接方式连接所有设备,各设备在同一系统内能够以不同的频率运行,每一个设备分配独立通道,以满足不同设备的通信需要,从而解决了PCI所面临的瓶颈问题,减少了硬件冲突。

通常,一个典型的PCI Express系统(如图2所示)主要由以下几部分组成:(1)Root Complex,集成在北桥芯片的root complex用于处理器和内存子系统与I/0设备之间的连接;(2)交换器(Switch),它取代了传统架构中的I/0桥接器,用来为I/0总线提供输出端,支持在不同终端设备间进行对等通信;(3)PCI桥接器(PCI bridge),用来与传统PCI设备连接;(4)终端设备(endpoint)。

PCIe的原理及体系架构_学习笔记

IO总线的三个阶段:第一代并行ISA 、EISA、MC、VESA.共同特点:信号的功能与时序与处理器引脚密切相关,几乎是微处理器信号的延伸和扩展,有些信号还与主板上的硬件资源有关系.第二代并行PCI、AGP、PCI-XPCI总线是一个标准的、与处理器无关的局部外围总线,不受限于系统所使用的处理器的种类,通用性更强. 图形端口,将PCI总线从图形数据传输中解放出来,改善带宽.第三代PCI Express高性能IO串行总线在总线结构上采取了根本性的变革,主要体现在两个方面:一是有并行总线变位串行总线;二是采用点到点的互连独享带宽.将原并行总线结构中桥下面挂连设备的一条总线变成了一条链路,一条链路可包含一条或多条通路.没有专用的数据、地址、控制和时钟线,总线上各种事务组织成信息包来传送.地址空间、配置机制及软件上均保持与传统PCI总线兼容.第一代和第二代都是并行总线,有多条地址线、数据线和控制线,挂接多个设备,称为下挂式总线(Multi-Drop),总线带宽由多个设备共享.通过提高数据宽度和频率来改善带宽的代价是挂接的电器负载减少(由于功耗增加和静态定时减少).PCIx与PCI相比:由于采用了PLL,频率更高性能更好;在地址和数据的基础上增加属性,从而可以高效管理缓冲区;分离事务协议相对延迟事务协议来说,提高了总线利用效率;可不需要中断引脚,改用消息信号中断(带内)体系结构,中断效率更高.基于PCI总线的结构最基本的PCI总线平台包含三级总线:FSB(Front-Side Bus)、PCI和ISA,FSB是处理器子系统的总线(Host总线),总线定义完全取决于系统所用的处理器;PCI局部总线是一个完全与处理器无关的总线,不受限微处理器的种类;ISA总线(IO扩展总线),也有采用EISA或MC总线的.不同的总线之间通过相应的桥芯片来连接.平台中两极桥是必须的,一是Host到PCI的(常称为主桥——Host桥),即北桥;另一个是PCI总线的桥(常称为扩展总线桥),即南桥.最基本的基于PCI总线的平台PCI地址空间映射x86 CPU的内存与I/O独立编址,I/O对应寄存器,内存对应RAM.因此,访问IO空间用IO读写指令,访问内存空间用内存读写指令.IO读写一般用于低速传输一些状态、控制寄存器的读写等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Ab l c sr t a

T r u h a ay i h u e a d t c nc l h r c e i i. i a e o ie o a a P h o g n l n t e t i g n r t / u r ht tr n e h ia c a a tr t t s z g d o e s c h p p r c mb n s C mp c t ・

Cltc n lg n ClE p e s t c n lg o p o o e a t c nc l x e t t n a d a p o c o h e l ain o h i — e h oo y a d P x r s e h oo y t r p s e h ia p ca i n p r a h f r te r ai t ft e h e o z o gh p r r n e c mp t rwhc s hg — a d d h e p n il , d lr e . O — wa p be r l b e a d r g dz d e f ma c o u e ih i i h b n wit x a sbemo u i d h c s p a l, i l n u ge i o az ea e K y rs P x r s , o a aP , r htc u e b n wi t e wo d :ClE p e sC mp c t Cl c i t r a d d h a e

计 算 机总 线 体 系 结 构 经 过 了 互代 的发 展 。第 一 代总 线 包 括

IA、 IA、 E A和 微通道 ( co Ch n e) S ES V S Mir a n 总线 , J 第二 代总线 包 括 P 、 GP和 P 一 Cl A Cl×总线 , ClE pe s是用 来互 连计 算 P x rs 和通信平 台应 用 中外 围 没备 的第 三代 高性 能 J 总线 。虽 说 / O

屈 涛 ( 中国电子科技集团公 司第十五研究所 , 北京 108 ) 00 3

摘 要

通 过 对 第三 代 I 总 线 体 系 结构 和技 术 特 性 进 行 分 析 说 明 , Co a aP 技 术 和 P x rs / O 将 mp c tCl ClE pe s技 术 相 结 合 , 实 为 现 高带 宽 、 高可 扩展 性 、 块化 、 插 拔 以及 高 可 靠 、 固性 强 的 高性 能 计 算 机 提 供 了技 术展 望 和途 径 。 模 热 坚

在 计 算机 的体 系 结 构技 术 中 ,计 算 机 J 技 术 始终 是一 个 / O

十分重要的关键技术。其技术特性决定 了计算机 I 的处理 能 / O 力 , 而决定 了汁算机 的整体性能以及应用环境 。从根本上讲 , 进 无论 现在还足将来 , O 技术都将 制约着 汁算 机技术 的应用 与 J / 发展 , 尤其在高端计算领域。

随 着信 息 技 术 和计 算机 技 术 的飞 速 发 展 ,未 来 社 会 将 是 一

在 P E pe s 技 术研 究 方 面 , 内针 对 P x rs CJ x rs 国 Cl pe s体 E 系 结 构 技 术 的 研 究 正 在 展 开 , 对 P x rs 系 结 构 的计 针 ClE p e s体 算 机 正在 推 出 , 于 P x rs 基 ClE pe s的各 种 应 用 板 卡 已经 推 出并 走 J 际 应 用 。 如 : 于 P x rs 旬实 基 ClE pe s的 4 8 1 X显 卡 已经 X、X、6 开 发 成 功 并 走 向实 际运 用 ; 于 P x rs 基 ClE p e s的 千 兆 以 太 网 接 口 1也 已有 产 品推 出 并实 用 化 ; 于 P lE pe s的 WL N通 4 基 C x rs A 信 卡 已经 有 产 品 推 出 并 实用 化 。 一些 P 口的膻 用 板 卡 , 对 C接 J 由 于 相 关 厂 家 的 F G 器 件 已 经 过 了 P x rs PA C E pe s相 容 性 测 试 J 大 会的 验 证 , 在 众 多 P x rs 并 Cl pe s应 用 中使 用 , 过 对 F G E 通 P A 中 已 有 的 高 速 收 发 器 模 块 l 有 的 P x rs P核 进 行研 及现 ClE pe s I 究 ,利 用 F GA 器 件 的 可 重 构 性 ,可 为 各 接 口向 P x rs P ClE p e s 接 口转 换 提 供 解 决 方 案 。 因 此 , 以 国 内在 基 于 P x rs 系 结 构 主 机 和 接 可 CIE p e s体

维普资讯

1 O

C mp c t Cl x rs o a aP pe s体系结构技术分析 E

C mp c tC x s 体系结构技术分析 o aP E pe s a I r

An lss o mp c P lE p e s Ar ht c u e a d T c n lg ay i f Co a t C x r s c i t r n e h oo y e

口板 的研 究 方 面 已经 具 备一 定 的 基础 。 12 国 外 研 究 现 状 I

个高效的数字化社会。大最 的数据 、 音 、 语 图形 和图像等信息需

要 进 行 实 时感 知 和 处 理 , 用 需求 对计 算机 的 带 宽 、 应 吞吐 量 和 - 口 丁

扩展的体系结构提出来 越来越高的要 求。