编程说明

VLT HVAC 变频器编程指南说明书

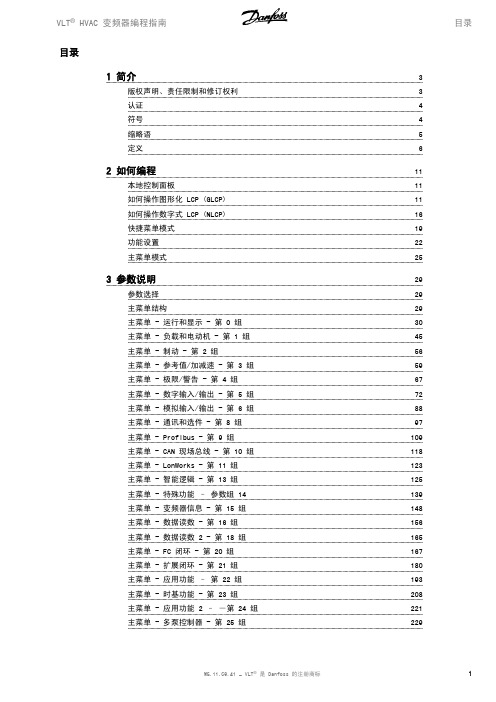

目录1 简介3版权声明、责任限制和修订权利3认证4符号4缩略语5定义62 如何编程11本地控制面板11如何操作图形化 LCP (GLCP)11如何操作数字式 LCP (NLCP)16快捷菜单模式19功能设置22主菜单模式253 参数说明29参数选择29主菜单结构29主菜单 - 运行和显示 - 第 0 组30主菜单 - 负载和电动机 - 第 1 组45主菜单 - 制动 - 第 2 组56主菜单 - 参考值/加减速 - 第 3 组59主菜单 - 极限/警告 - 第 4 组67主菜单 - 数字输入/输出 - 第 5 组72主菜单 - 模拟输入/输出 - 第 6 组88主菜单 - 通讯和选件 - 第 8 组97主菜单 - Profibus - 第 9 组109主菜单 - CAN 现场总线 - 第 10 组118主菜单 - LonWorks - 第 11 组123主菜单 - 智能逻辑 - 第 13 组125主菜单 - 特殊功能 – 参数组 14139主菜单 - 变频器信息 - 第 15 组148主菜单 - 数据读数 - 第 16 组156主菜单 - 数据读数 2 - 第 18 组165主菜单 - FC 闭环 - 第 20 组167主菜单 - 扩展闭环 - 第 21 组180主菜单 - 应用功能 – 第 22 组193主菜单 - 时基功能 - 第 23 组208主菜单 - 应用功能 2 – -第 24 组221主菜单 - 多泵控制器 - 第 25 组229主菜单 - 模拟 I/O 选件 MCB 109 - 第 26 组2414 疑难解答251报警字255警告字256扩展状态字257故障消息2585 参数列表263参数选项263默认设置263 0-** 操作/显示264 1-** 负载/电动机265 2-** 制动265 3-** 参考值/加减速266 4-** 极限/警告266 5-** 数字输入/输出267 6-** 模拟输入/输出268 8-** 通讯和选件269 9-** Profibus270 10-** CAN 现场总线270 11-** LonWorks271 13-** 智能逻辑控制器271 14-** 特殊功能272 15-** 变频器信息273 16-** 数据读数274 18-** 信息和读数275 20-** FC 闭环276 21-** 扩展 闭环277 22-** 应用功能278 23-** 基于时间的功能279 24-** 应用功能 2279 25-** 多泵控制器280 26-** 模拟输入输出选件 MCB 109281索引28211本指南适用于软件版本为 3.3.x 的所有 VLT HVAC Drive 变频器。

库卡机器人编程语法-概述说明以及解释

库卡机器人编程语法-概述说明以及解释1.引言1.1 概述概述库卡机器人编程语法是指在库卡机器人系统中使用的编程语言规则和规范。

库卡机器人是一种广泛应用于工业生产领域的工业机器人,它能够执行各种任务,并协助人类完成繁重、危险或重复性高的工作。

在库卡机器人编程语法中,我们需要了解语法结构、关键字、表达式和指令等方面的知识。

掌握这些知识有助于我们编写出高效、准确、安全的机器人程序,实现对机器人的精确控制。

库卡机器人编程语法具有以下几个特点:首先,它是一种结构化的编程语言,具有清晰的程序组织结构,便于代码的编写和维护;其次,它支持多种类型的数据和变量,如整数、浮点数、字符串等,以及各种运算符和逻辑操作符,使得程序设计更加灵活;再次,它提供了丰富的控制结构和函数库,能够满足不同的编程需求;最后,它还具备错误处理和调试机制,方便我们定位和修复程序中的错误。

库卡机器人编程语法的学习和掌握对于使用和开发库卡机器人系统至关重要。

正确地使用编程语法可以提高机器人系统的工作效率和准确性,减少人为错误的发生。

同时,熟练地掌握库卡机器人编程语法可以为后续的高级功能开发和应用打下基础,为机器人系统的进一步发展提供支持。

本篇文章将系统地介绍库卡机器人编程语法的要点和基本知识,并结合实际例子进行解读和应用。

通过对概述的研究和学习,读者可以对库卡机器人编程语法有一个全面而深入的了解,为后续的学习和应用打好基础。

1.2 文章结构文章结构部分的内容:在本文中,我们将以库卡机器人编程语法为主题,对其进行深入探讨和分析。

文章主要分为引言、正文和结论三部分。

引言部分首先概述了文章的主题,即库卡机器人编程语法,并简要介绍了本文的结构和目的。

正文部分将着重介绍库卡机器人编程语法的要点。

其中,2.1节将详细阐述库卡机器人编程语法的第一个要点,包括语法的基本概念、常用指令和编程规范等内容。

2.2节则将对库卡机器人编程语法的第二个要点进行探讨,探讨其在实际应用中的具体用法和注意事项。

STM32WB BLE 协议栈编程手册说明书

PM0271编程手册STM32WB BLE协议栈编程指南引言本文档的主要目的是为开发人员提供有关如何使用STM32WB BLE协议栈API和相关事件回调开发低功耗蓝牙(BLE)应用的一些参考编程指南。

本文档介绍了允许访问STM32WB片上系统所提供的低功耗蓝牙功能的STM32WB低功耗蓝牙协议栈库框架、API接口和事件回调。

本编程手册还提供一些与低功耗蓝牙(BLE)技术有关的基本概念,以便将STM32WB BLE协议栈API、参数及相关事件回调与BLE协议栈特性联系起来。

用户必须具备有关BLE技术及其主要功能的基本知识。

有关STM32WB系列和低功耗蓝牙规范的更多信息,请参考本文档结尾处的第6节“参考文档”。

STM32WB是一种功率极低的低功耗蓝牙(BLE)单模网络处理器,符合蓝牙规范v5.3并支持主设备或从设备角色。

手册结构如下:• 低功耗蓝牙(BLE)技术的基本原理• STM32WB BLE协议栈库API和事件回调概述• 如何利用STM32WB库API和事件回调设计应用(使用“switch case”事件处理程序提供一些示例,而不使用事件回调框架)PM0271概述1 概述本文档适用于STM32WB系列基于双核Arm®的微控制器。

注意:Arm是Arm Limited(或其子公司)在美国和/或其他地区的注册商标。

2 低功耗蓝牙技术低功耗蓝牙(BLE)无线技术由蓝牙技术联盟(SIG)开发,目的是使设备能够以极低功耗标准使用纽扣电池工作数年。

传统蓝牙作为一种无线技术标准,可以取代连接便携式和/或固定式电子设备的线缆,但是由于采取了快速跳频、以连接为导向的行为方式和相对复杂的连接流程,无法采用电池供电的方式。

低功耗蓝牙设备的功耗仅为标准蓝牙产品的一小部分,让使用纽扣电池的设备能够无线连接到启用了标准蓝牙的设备。

图1. 支持低功耗蓝牙技术的以钮扣电池供电的设备低功耗蓝牙技术广泛应用于传输少量数据的传感器应用中:• 汽车• 运动与健身• 医疗• 娱乐• 家庭自动化• 安全和接近感测2.1BLE协议栈架构低功耗蓝牙技术已被蓝牙核心规范4.0正式采纳(参见第6节参考文件)。

sin x泰勒级数展开的python编程-概述说明以及解释

sin x泰勒级数展开的python编程-概述说明以及解释1.引言1.1 概述概述:sin x是一种基本的三角函数,常用于描述周期性现象或波动振动问题。

在数学中,sin x可以通过泰勒级数来近似表示。

泰勒级数展开是将一个函数在某个点的附近进行多项式逼近的方法,可以将复杂的函数转化为简单的多项式来进行计算和分析。

本文旨在通过使用Python编程语言实现sin x的泰勒级数展开,来探讨其原理和应用。

文章将从sin x的定义与特性入手,介绍泰勒级数展开的原理,并详细解释如何使用Python编写程序来实现这一展开过程。

通过编程实例,读者将能够理解泰勒级数展开的计算方法和在Python中的具体实现步骤,同时也能加深对sin x函数的理解。

文章将以以下内容逐步展开:首先,在引言部分给出了本文的目的和整体结构;接下来,就sin x的定义和特性进行介绍,包括正弦函数的图像特点和基本性质;然后,将详细解释泰勒级数展开的原理,包括级数的推导和收敛条件;最后,通过使用Python编程语言来实现sin x的泰勒级数展开,并给出具体的代码实例和运行结果。

文章的结论部分将对实现结果进行总结和分析,探讨编程应用展望,并对整篇文章进行总结,并展望未来可能的扩展方向。

通过阅读本文,读者将能够深入了解sin x的泰勒级数展开,掌握使用Python编程来实现该展开的方法,同时也能够在实际应用中运用所学知识解决相关问题。

1.2文章结构文章结构部分的内容通常包括对整篇文章的组织和内容安排的介绍。

在这个部分,你可以描述每个章节的主要内容和目的,以及这些章节之间的逻辑关系。

下面是一个可能的编写方式:1.2 文章结构本文将主要围绕sin x的泰勒级数展开展开,通过Python编程实现该展开式的计算。

文章分为引言、正文和结论三个主要部分。

在引言部分,我们将给出这篇文章的概述,简要介绍sin x的定义和特性,以及本文的目的。

正文部分将具体讨论sin x的定义与特性(2.1小节),以及泰勒级数展开的原理(2.2小节)。

汇编多文件编程-概述说明以及解释

汇编多文件编程-概述说明以及解释1.引言1.1 概述汇编多文件编程是一种在汇编语言中使用多个文件来编写程序的技术。

在传统的汇编程序中,所有的代码都是写在一个文件中的,当程序变得庞大时,这会导致代码的可读性和可维护性变得非常困难。

汇编多文件编程通过将不同功能的代码分开存放在不同的文件中,使得程序结构更清晰,代码逻辑更容易理解。

通过合理地划分文件,我们可以将不同的功能模块独立编写,便于单独测试和调试,提高了代码的复用性和可扩展性。

在汇编多文件编程中,我们通常将主程序和不同的功能模块分别写在不同的文件中。

这些文件可以包含代码、数据和常量等信息。

通过在主程序中调用其他文件中的函数和变量,我们可以实现不同文件之间的交互和数据共享。

汇编多文件编程还可以提高代码的模块化程度,降低了编写和维护程序的难度。

它使得团队合作开发更加便捷,每个成员可以独立地编写和测试自己负责的部分,最后再进行整合。

总之,汇编多文件编程是一种有效的编程技术,它能够提高程序的可读性、可维护性和可扩展性。

通过合理地划分和组织代码,我们可以更好地编写和管理复杂的汇编程序。

在本文中,我们将介绍汇编语言的基础知识,以及如何使用多文件进行汇编编程的概念和方法。

1.2 文章结构文章结构部分的内容可以包括以下内容:文章结构部分旨在介绍本文的整体组织架构,用以引导读者了解本篇长文的内容安排和逻辑结构。

本文主要分为引言、正文和结论三个部分。

引言部分对本文的主题进行概述,并介绍文章的背景和意义。

通过简要介绍汇编多文件编程的概念和应用领域,引发读者对该主题的兴趣,并提出本文的目的和研究问题。

正文部分是本文的核心内容,主要分为两个小节:汇编语言基础和多文件编程概念。

在汇编语言基础部分,将介绍汇编语言的定义、特点和基本语法,为读者建立起对汇编语言的基本认识。

在多文件编程概念部分,将详细探讨多文件编程的原理和应用,包括多文件编程的优势、实现方法和注意事项,以及多文件编程在实际项目开发中的应用案例。

Intel 64和IA-32架构软件开发人员手册第三卷(3A,3B,3C和3D) 系统编程指南说明书

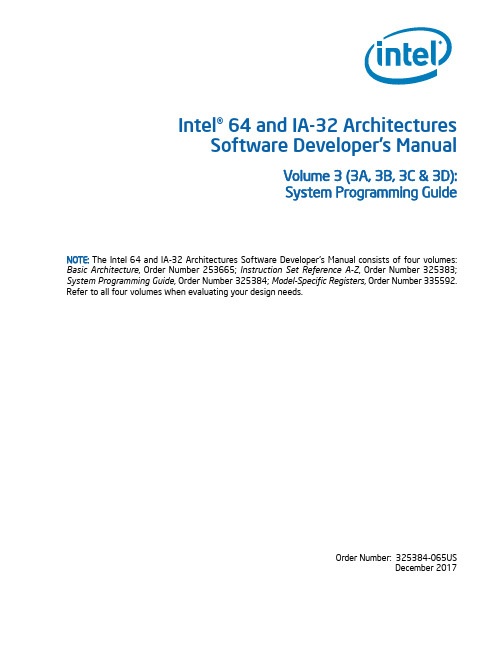

Intel® 64 and IA-32 ArchitecturesSoftware Developer’s ManualVolume 3 (3A, 3B, 3C & 3D):System Programming GuideNOTE: The Intel 64 and IA-32 Architectures Software Developer's Manual consists of four volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A-Z, Order Number 325383; System Programming Guide, Order Number 325384; Model-Specific Registers, Order Number 335592. Refer to all four volumes when evaluating your design needs.Order Number: 325384-065USDecember 2017Intel technologies features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at , or from the OEM or retailer.No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifica-tions. Current characterized errata are available on request.This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmapsCopies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting /design/literature.htm.Intel, the Intel logo, Intel Atom, Intel Core, Intel SpeedStep, MMX, Pentium, VTune, and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.*Other names and brands may be claimed as the property of others.Copyright © 1997-2017, Intel Corporation. All Rights Reserved.CONTENTSPAGECHAPTER 1ABOUT THIS MANUAL1.1INTEL® 64 AND IA-32 PROCESSORS COVERED IN THIS MANUAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1 1.2OVERVIEW OF THE SYSTEM PROGRAMMING GUIDE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4 1.3NOTATIONAL CONVENTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6 1.3.1Bit and Byte Order. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6 1.3.2Reserved Bits and Software Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7 1.3.3Instruction Operands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8 1.3.4Hexadecimal and Binary Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8 1.3.5Segmented Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8 1.3.6Syntax for CPUID, CR, and MSR Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9 1.3.7Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9 1.4RELATED LITERATURE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10CHAPTER 2SYSTEM ARCHITECTURE OVERVIEW2.1OVERVIEW OF THE SYSTEM-LEVEL ARCHITECTURE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1 2.1.1Global and Local Descriptor Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3 2.1.1.1Global and Local Descriptor Tables in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.1.2System Segments, Segment Descriptors, and Gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.1.2.1Gates in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.1.3Task-State Segments and Task Gates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.3.1Task-State Segments in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.4Interrupt and Exception Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.4.1Interrupt and Exception Handling IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.5Memory Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.1.5.1Memory Management in IA-32e Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.1.6System Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.1.6.1System Registers in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.1.7Other System Resources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.2MODES OF OPERATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.2.1Extended Feature Enable Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9 2.3SYSTEM FLAGS AND FIELDS IN THE EFLAGS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9 2.3.1System Flags and Fields in IA-32e Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11 2.4MEMORY-MANAGEMENT REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11 2.4.1Global Descriptor Table Register (GDTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12 2.4.2Local Descriptor Table Register (LDTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12 2.4.3IDTR Interrupt Descriptor Table Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12 2.4.4Task Register (TR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13 2.5CONTROL REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13 2.5.1CPUID Qualification of Control Register Flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-19 2.6EXTENDED CONTROL REGISTERS (INCLUDING XCR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19 2.7PROTECTION KEY RIGHTS REGISTER (PKRU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21 2.8SYSTEM INSTRUCTION SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21 2.8.1Loading and Storing System Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-23 2.8.2Verifying of Access Privileges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-23 2.8.3Loading and Storing Debug Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-24 2.8.4Invalidating Caches and TLBs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-24 2.8.5Controlling the Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-25 2.8.6Reading Performance-Monitoring and Time-Stamp Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-25 2.8.6.1Reading Counters in 64-Bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26 2.8.7Reading and Writing Model-Specific Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26 2.8.7.1Reading and Writing Model-Specific Registers in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26 2.8.8Enabling Processor Extended States. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26Vol. 3A iiiCONTENTSiv Vol. 3A PAGECHAPTER 3PROTECTED-MODE MEMORY MANAGEMENT3.1MEMORY MANAGEMENT OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1 3.2USING SEGMENTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2 3.2.1Basic Flat Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3 3.2.2Protected Flat Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3 3.2.3Multi-Segment Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4 3.2.4Segmentation in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5 3.2.5Paging and Segmentation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5 3.3PHYSICAL ADDRESS SPACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6 3.3.1Intel® 64 Processors and Physical Address Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6 3.4LOGICAL AND LINEAR ADDRESSES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6 3.4.1Logical Address Translation in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7 3.4.2Segment Selectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7 3.4.3Segment Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8 3.4.4Segment Loading Instructions in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9 3.4.5Segment Descriptors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9 3.4.5.1Code- and Data-Segment Descriptor Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12 3.5SYSTEM DESCRIPTOR TYPES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13 3.5.1Segment Descriptor Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-14 3.5.2Segment Descriptor Tables in IA-32e Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-16CHAPTER 4PAGING4.1PAGING MODES AND CONTROL BITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1 4.1.1Three Paging Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1 4.1.2Paging-Mode Enabling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3 4.1.3Paging-Mode Modifiers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4 4.1.4Enumeration of Paging Features by CPUID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5 4.2HIERARCHICAL PAGING STRUCTURES: AN OVERVIEW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6 4.332-BIT PAGING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7 4.4PAE PAGING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13 4.4.1PDPTE Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-13 4.4.2Linear-Address Translation with PAE Paging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-14 4.54-LEVEL PAGING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19 4.6ACCESS RIGHTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28 4.6.1Determination of Access Rights . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-29 4.6.2Protection Keys . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-31 4.7PAGE-FAULT EXCEPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-31 4.8ACCESSED AND DIRTY FLAGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-33 4.9PAGING AND MEMORY TYPING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-34 4.9.1Paging and Memory Typing When the PAT is Not Supported (Pentium Pro and Pentium II Processors). . . . . . . . . . . . . .4-34 4.9.2Paging and Memory Typing When the PAT is Supported (Pentium III and More Recent Processor Families). . . . . . . . . .4-34 4.9.3Caching Paging-Related Information about Memory Typing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-35 4.10CACHING TRANSLATION INFORMATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-35 4.10.1Process-Context Identifiers (PCIDs). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-35 4.10.2Translation Lookaside Buffers (TLBs). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-36 4.10.2.1Page Numbers, Page Frames, and Page Offsets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-36 4.10.2.2Caching Translations in TLBs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-37 4.10.2.3Details of TLB Use. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-37 4.10.2.4Global Pages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-38 4.10.3Paging-Structure Caches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-38 4.10.3.1Caches for Paging Structures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-38 4.10.3.2Using the Paging-Structure Caches to Translate Linear Addresses. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-40 4.10.3.3Multiple Cached Entries for a Single Paging-Structure Entry. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41 4.10.4Invalidation of TLBs and Paging-Structure Caches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41 4.10.4.1Operations that Invalidate TLBs and Paging-Structure Caches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41 4.10.4.2Recommended Invalidation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-43 4.10.4.3Optional Invalidation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-44 4.10.4.4Delayed Invalidation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-45 4.10.5Propagation of Paging-Structure Changes to Multiple Processors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-46 4.11INTERACTIONS WITH VIRTUAL-MACHINE EXTENSIONS (VMX). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-47 4.11.1VMX Transitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-47CONTENTSPAGE 4.11.2VMX Support for Address Translation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-474.12USING PAGING FOR VIRTUAL MEMORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-47 4.13MAPPING SEGMENTS TO PAGES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-48CHAPTER 5PROTECTION5.1ENABLING AND DISABLING SEGMENT AND PAGE PROTECTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1 5.2FIELDS AND FLAGS USED FOR SEGMENT-LEVEL ANDPAGE-LEVEL PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2 5.2.1Code-Segment Descriptor in 64-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3 5.3LIMIT CHECKING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4 5.3.1Limit Checking in 64-bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5 5.4TYPE CHECKING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5 5.4.1Null Segment Selector Checking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6 5.4.1.1NULL Segment Checking in 64-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6 5.5PRIVILEGE LEVELS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6 5.6PRIVILEGE LEVEL CHECKING WHEN ACCESSING DATA SEGMENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8 5.6.1Accessing Data in Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9 5.7PRIVILEGE LEVEL CHECKING WHEN LOADING THE SS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10 5.8PRIVILEGE LEVEL CHECKING WHEN TRANSFERRING PROGRAM CONTROL BETWEEN CODE SEGMENTS . . . . . . . . . . . . . . . . 5-10 5.8.1Direct Calls or Jumps to Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10 5.8.1.1Accessing Nonconforming Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11 5.8.1.2Accessing Conforming Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12 5.8.2Gate Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13 5.8.3Call Gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13 5.8.3.1IA-32e Mode Call Gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14 5.8.4Accessing a Code Segment Through a Call Gate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15 5.8.5Stack Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17 5.8.5.1Stack Switching in 64-bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19 5.8.6Returning from a Called Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20 5.8.7Performing Fast Calls to System Procedures with theSYSENTER and SYSEXIT Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20 5.8.7.1SYSENTER and SYSEXIT Instructions in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21 5.8.8Fast System Calls in 64-Bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22 5.9PRIVILEGED INSTRUCTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23 5.10POINTER VALIDATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24 5.10.1Checking Access Rights (LAR Instruction) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24 5.10.2Checking Read/Write Rights (VERR and VERW Instructions). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25 5.10.3Checking That the Pointer Offset Is Within Limits (LSL Instruction). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25 5.10.4Checking Caller Access Privileges (ARPL Instruction). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26 5.10.5Checking Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27 5.11PAGE-LEVEL PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27 5.11.1Page-Protection Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.2Restricting Addressable Domain. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.3Page Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.4Combining Protection of Both Levels of Page Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.5Overrides to Page Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29 5.12COMBINING PAGE AND SEGMENT PROTECTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29 5.13PAGE-LEVEL PROTECTION AND EXECUTE-DISABLE BIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30 5.13.1Detecting and Enabling the Execute-Disable Capability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30 5.13.2Execute-Disable Page Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30 5.13.3Reserved Bit Checking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31 5.13.4Exception Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32CHAPTER 6INTERRUPT AND EXCEPTION HANDLING6.1INTERRUPT AND EXCEPTION OVERVIEW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1 6.2EXCEPTION AND INTERRUPT VECTORS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1 6.3SOURCES OF INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2 6.3.1External Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2 6.3.2Maskable Hardware Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3 6.3.3Software-Generated Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4Vol. 3A v。

VLT Micro Drive FC 51 编程指南说明书

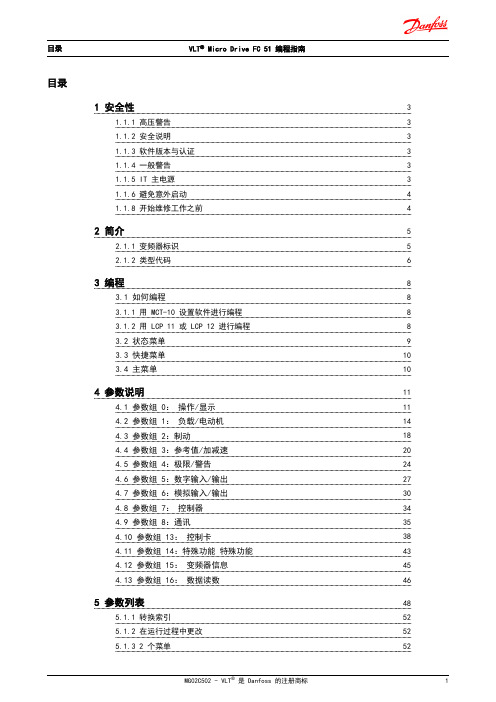

目录1 安全性31.1.1 高压警告31.1.2 安全说明31.1.3 软件版本与认证31.1.4 一般警告31.1.5 IT 主电源31.1.6 避免意外启动41.1.8 开始维修工作之前42 简介52.1.1 变频器标识52.1.2 类型代码63 编程83.1 如何编程83.1.1 用 MCT-10 设置软件进行编程83.1.2 用 LCP 11 或 LCP 12 进行编程83.2 状态菜单93.3 快捷菜单103.4 主菜单104 参数说明114.1 参数组 0: 操作/显示114.2 参数组 1: 负载/电动机144.3 参数组 2:制动184.4 参数组 3:参考值/加减速204.5 参数组 4:极限/警告244.6 参数组 5:数字输入/输出274.7 参数组 6:模拟输入/输出304.8 参数组 7: 控制器344.9 参数组 8:通讯354.10 参数组 13: 控制卡384.11 参数组 14:特殊功能 特殊功能434.12 参数组 15: 变频器信息454.13 参数组 16: 数据读数465 参数列表485.1.1 转换索引525.1.2 在运行过程中更改525.1.3 2 个菜单525.1.4 类型525.1.5 0-** 操作/显示535.1.6 1-** 负载/电动机535.1.7 2-** 制动535.1.8 3-** 参考值/加减速545.1.9 4-** 极限/警告545.1.10 5-** 数字输入/输出545.1.11 6-** 模拟输入/输出555.1.12 7-** 控制器555.1.13 8-** 通讯和选件555.1.14 13-** Smart Logic565.1.15 14-** 特殊功能565.1.16 15-** 变频器信息565.1.17 16-** 数据读数576 故障排查586.1.1 报警字、警告字和扩展状态字60索引631安全性1.1.1高压警告只要变频器 与主电源相连,它便带有危险电压。

SmartController CR2530 CR2532 编程手册说明书

7391003 / 08 10 / 2018内容1关于本手册51.1版权 (5)1.2概述:ecomatmobile 装置文档模块 (6)1.3符号和格式是什么意思? (7)1.4本文档的结构是怎样的? (8)1.5说明沿革(CR253n) (10)2安全说明112.1请注意! (11)2.2需要预先具备哪些知识? (12)2.3控制器的启动运行状况 (12)2.4注意事项:序列号 (12)3系统描述133.1关于装置的信息 (13)3.2硬件说明 (14)3.2.1硬件结构 (14)3.2.2输入端(技术) (17)3.2.3输出端(技术) (23)3.2.4关于配线的注意事项 (30)3.2.5关于簧片继电器的安全说明 (30)3.2.6状态LED (31)3.3接口说明 (32)3.3.1CAN 接口 (33)3.4软件说明 (34)3.4.1装置的软件模块 (35)3.4.2CODESYS 项目的编程说明 (37)3.4.3工作状态 (41)3.4.4装置的性能极限 (44)4配置474.1设定运行时系统 (48)4.1.1重新安装运行时系统 (48)4.1.2更新运行时系统 (50)4.1.3检验安装 (50)24.2设定编程系统 (51)4.2.1手动设定编程系统 (51)4.2.2通过模板设定编程系统 (55)4.3一般功能配置 (55)4.3.1系统变量 (55)4.4输入端和输出端功能配置 (56)4.4.1配置输入端和输出端(默认设定) (56)4.4.2配置输入端 (57)4.4.3配置输出端 (62)4.5变量 (67)4.5.1保留变量 (67)4.5.2网络变量 (68)5IFM 功能元件695.1针对装置CR2530 的IFM 库 (69)5.1.1库ifm_CR2530_V03yyzz.LIB (70)5.1.2库ifm_RAWCan_NT_Vxxyyzz.LIB (71)5.1.3库ifm_CANopen_NT_Vxxyyzz.LIB (72)5.1.4库ifm_J1939_NT_Vxxyyzz.LIB (73)5.2针对装置CR2530 的IFM 功能元件 (75)5.2.1输出端功能元件 (75)5.2.2功能元件:RAW-CAN(第2 层) (77)5.2.3功能元件:CANopen (115)5.2.4功能元件:SAE J1939 (172)5.2.5功能元件:处理输入值 (216)5.2.6功能元件:输出端功能 (229)5.2.7功能元件:系统 (238)6诊断和错误处理2656.1诊断 (265)6.2故障 (265)6.3响应系统错误 (266)6.3.1响应错误消息的进程示例 (266)6.4CAN / CANopen: 错误和错误处理 (266)7附录2677.1系统标志 (268)7.2地址分配和I/O 工作模式 (269)7.2.1I/O 地址/变量 (269)7.2.2可能的输入端/输出端工作模式 (272)37.3集成I/O 模块:说明 (276)7.3.1系统说明I/O 模块ExB01 (276)7.3.2I/O 模块的配置 (291)7.3.3集成I/O 模块的对象目录 (305)7.3.4I/O 模块的运行 (346)7.3.5针对集成ExB01 I/O 模块的系统标志 (349)7.3.6I/O 模块错误消息 (350)7.4错误表 (353)7.4.1错误标志 (353)7.4.2错误:CAN / CANopen (353)8专业术语355 9指数37241 关于本手册内容版权 (5)概述:ecomatmobile 装置文档模块 (6)符号和格式是什么意思? (7)本文档的结构是怎样的? (8)说明沿革(CR253n) (10)2021.1 版权46224 © ifm electronic gmbh保留所有权利。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LD-D型MP3音乐打铃扩音机补充说明

手动播放

1、自动播放,直接按下数字键,大于5的曲目按5+后再按数字键。

2、手动播放可进行单曲和连续连续播放。

在校时状态下,按下“星期”键5秒,显示“CE--NO”,此时为单曲播放(播放完一首歌后自动停止播放),再按“星期”键5秒,显示“CE--ER”,此时为连续播放(播放完一首后自动播放下一首),每按“星期”键5秒,显示状态在二者之间转换。

手动编程

1、调整“功能”键至编程状态(编程灯亮),此时星期灯闪动。

2、调整“星期”键,选择打铃方式——七天编程、六天编程、五天编程或单天独立编程等,如调整星期一至星期日灯全亮,为七天编程。

3、选择好打铃方式后,按“存储”键。

特别注意:用户初次使用,在进行完本步骤时就进行总清。

按“清除/停止”键2秒,总清灯亮,屏显示“——”,约一分钟后,总清完毕。

重复第1、第2再进行后面的操作。

总清时,清除掉的程序与选择的打铃方式有关,若七天编程时,总清七天的内容。

在初次总清时,要在七天编程状态下进行。

4、调整“时间”至打铃点,调整“曲目”,选择相应曲目,然后按“存储”键,存储灯亮起,表示该次打铃点已存入。

5、重复第4步操作,直至将所有打铃点存储完毕。

特别注意:存储过程中若有错误,可利用“清除/停止”键,进行单点清除。

在已存入的打铃点上(此时存储灯亮),按一下“清除/停止”键,存储灯灭,表示此打铃点已清除,然后存入正确的打铃点。

6、所有打铃点存储完毕后,可按下“时间”,检查一遍所有的打铃点是否正确。

7、确认打铃点正确无误后,调整“功能”至自动状态,便可正常工作。

说明:若用户时间表上要求某一天的程序与其它不同,可进行以下操作。

将程序编完后,调整“星期”键,使这一天灯亮,按下“存储”键。

此时可进行两种操作。

一是按下“总清”,将这一天的程序全部清除掉,然后按照第3、4、5、6步骤,将这一天的程序输入进去。

二是若这一天与其它六天只有几个打铃点不同,可将这一天未存入的打铃点存进去,将多存入的清除掉。