组合逻辑电路描述

合集下载

组合逻辑电路

Y2 A2 A1 A0 m2 Y3 A2 A1A0 m3

Y6 A2 A1A0 m6 Y7 A2 A1A0 m7

3. 5. 2二进制译码器的应用

一、用译码器实现组合逻辑电路

因为n个输入变量的二进制泽码器的输出为其对应的2n个最小 项(或最小项的反),而任一逻辑函数均可表示为最小项表达 式(即标准与或式)的形式,故利用二进制泽码器和门电路可 实现单输出或多输出组合逻辑电路的设计。使用方法为:当泽 码器的输出为低电平有效时,选用与非门;当泽码器的输出为 高电平有效时,选用或门。

(4) 分析电路的逻辑功能。由真值表可以看出:当A, B输入状 态相同时,Y=0;当A同时,Y=1。故此电路具有异或门的逻 辑功能,所以该电路是由4B输入状态不个与非门构成的异或 逻辑电路。

上一页 下一页 返回

3.2 组合逻辑电路的分析

「例3.2.2]已知组合逻辑电路如图3.2.2所示,试分析该电路 的逻辑功能。

当输入A3=1时,低位片CT74LS138(1)因A3 =1而禁止泽码, 输出 Y0 ~ Y7 均为高电平1,高位片CT74LS138(2)工作,这时 输入A3A2A1A0 ,在1000~1111之间变化时, Y8 ~ Y15 对应的输 出端输出有效的低电平0。

中,I 7的优先级别最高,I6 次之,其余依此类推,I 0 的级别最 低。

上一页 下一页 返回

3. 4 编码器

也就是说,当 I7 =0时,其余输入信号不沦是0还是1都不起作 用,电路只对 I 7 进行编码,输出 Y2Y1Y0 = 000,此码为反码,其 原码为111,其余类推。可见,这8个输入信号优先级别的高 低次序依次为 I 7、I 6、I 5、I 4、I 3、I 2、I1、I 0

3. 5. 1二进制译码器 将输入二进制代码按其原意转换成对应特定信号输出的逻辑

第五章 组合逻辑电路的VHDL语言描述

BEGIN

PROCESS ( a, datain ) BEGIN IF ( datain = '1' ) THEN dataout <= '0' ; ELSE dataout <= '1' ; END IF ; END PROCESS ; END ARCHITECTURE behavioral_2 ; --RTL描述方式 ,MAX中需要加入时钟a

第5章

组合逻辑电路的VHDL描述

仿真波形

第5章

组合逻辑电路的VHDL描述

5.1.5 2输入同或门电路

LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY cynxor2 IS PORT ( datain1, datain2 : IN STD_LOGIC ; dataout : OUT STD_LOGIC ) ; END ENTITY cynxor2 ; ARCHITECTURE behavioral OF cynxor2 IS BEGIN

END ENTITY cyxor2 ;

ARCHITECTURE behavioral OF cyxor2 IS BEGIN dataout <= datain1 XOR datain2 ; END ARCHITECTURE behavioral ;

第5章

组合逻辑电路的VHDL描述

LIBRARY IEEE ;

第5章

组合逻辑电路的VHDL描述

LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY cynot IS

PORT ( a, datain : IN STD_LOGIC ; END ENTITY cynot ; ARCHITECTURE behavioral_2 OF cynot IS dataout : OUT STD_LOGIC ) ;

组合逻辑电路

输出Y.~Y.为低电平0有效。代码1010~1111

没有使用,称为伪码。由上表可知,当输入伪

码1010~1111时,输出Y9~Y0都为高电平1, 不会出现低电平0。因此译码器不会产生错误译

码。

图13.7 二-十进制译码器逻辑图

1.3 译 码 器

10

1.3 译 码 器

11

1.3.3 BCD-7段显示译码器

二进制码器是用于把二进制 代码转换成相应输出信号的译码 器。常见的有2线-4线译码器、 3线-8线译码器和4线-16线译码 器等。如图13.5所示为集成3线 -8线译码器74LS138的逻辑图 。

图13.5 3线-8线译码器逻辑图

1.3 译 码 器

9

1.3.2 二-十进制译码器

将4位BCD码的10组代码翻译成0~9这10个

图1.11 数据选择器

1. 4选1数据选择器

图1.12所示为4选1数据选择器的逻辑图 ,A1、A0是地址端。D0~D3是4个数据端 ,ST是低电平有效的使能端,具有两个互 补输出端Y和Y。对于不同的二进制地址输 入,可按地址选择D0~D3中一个数据输出 。其功能如表13.8所示。

图1.12 4选1数据选择器逻辑图

1

1.1 组合逻辑电路的分析与设计

2

1.1.1 组合逻辑电路的分析方法

组合逻辑电路的分析是根据给定的逻辑电路图,弄清楚它的逻辑功 能,求出描述电路输出与输入之间的逻辑关系的表达式,列出真值表 。一般方法如下所述。

1)根据给定的逻辑电路的逻辑图,从输入端向输出端逐级写出各 个门对其输入的逻辑表达式,从而写出整个逻辑电路的输出对输入的 逻辑函数表达式。

2)利用逻辑代数运算法则化简逻辑函数表达式。 3)根据化简后的逻辑函数表达式,列出真值表,使逻辑功能更加 清晰。 4)根据化简后的逻辑函数表达式或真值表,分析逻辑功能。 下面通过一个例子说明组合逻辑电路的分析方法。

第9章组合逻辑电路

P1 A

P2 B C

P3 BC P4 P1 P2 A(B C)

P5 A P3 ABC

Y P4 P5 A(B C) ABC

(2)用卡诺图化简输出函数表达式。

Y A(B C) ABC A(B C) ABC AB AC AB AC

0

1

0

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

表9.2 真值表

9.1.3组合逻辑电路的设计

(3)由真值表写出输出变量函数表达式并化简:

Y ABC ABC ABC ABC AB BC AC (4)画出逻辑电路如图9.2所示。

AB

C 00 01 11 10

A

00 0 1 0

(1)确定输入、输出变量,定义逻辑状态的含义。

设A、B、C代表三个人,作为电路的三个输入变量,当A、 B、C为1时表示同意,为0表示不同意。将Y设定为输出变 量,代表决意是否通过的结果,当Y为1表示该决意通过, 当Y为0表示决意没有通过。

(2)根据题意列出真值表,如表9.2所示。

A

B

C

Y

0

0

0

0

0

• (2)根据真值表写逻辑表达式,并化简成最简“与或” 逻辑表达式。

• (3)选择门电路和型号。 • (4)按照门电路类型和型号变换逻辑函数表达式 • (5)根据逻辑函数表达式画逻辑图。

• 例9.2 设计一个三人表决器电路,当两个或两个以上的人 表示同意时,决意才能通过。 解:根据组合逻辑电路的设计方法,可按如下步骤进行。

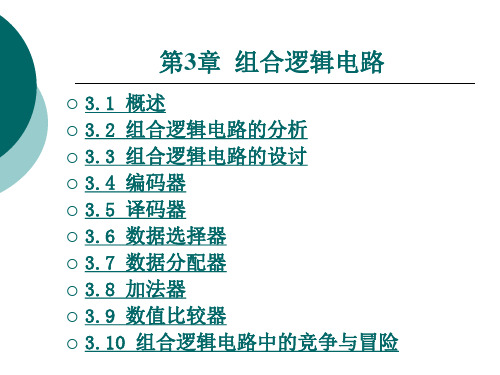

第3章-组合逻辑电路

一、二进制译码器(最小项译码器) 输入:一组二进制代码 输出:一组与输入代码一一对应的高、低电平信号。

例:3位二进制(3线-8线)译码器框图如下所示:

图3.3.5

3线-8线译码器框图

二进制译码器可采用二极管与门阵列或三极管集 成门电路等构成。

(1)二极管与门阵列译码器电路 0(0V) 1(3V)

表3-3-4

74LS42功能表

74LS42逻辑电路图及各输出表达式如下所示:

Y 0 Y 1 Y 2 Y 3 Y 4 Y5 Y 6 Y 7 Y8 Y9 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0

Y3

Y2

Y1

Y0

§3.3 若干常用的组合逻辑电路

目前,一些常用的逻辑电路已经制成了中、小 规模集成化电路产品。

§3.3.1 编码器(Encoder)

“编码”:即为了区分一系列不同的事物,将其 中的每个事物用一个二值代码表示。 编码器的逻辑功能:把输入的每一个高、低电平 信号变成一个对应的二进制代码。

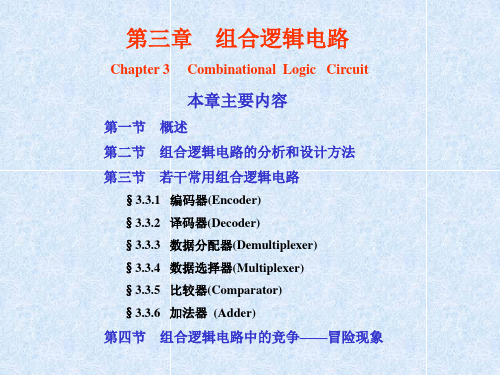

第三章

Chapter 3

组合逻辑电路

Combinational Logic Circuit

本章主要内容

第一节 第二节 第三节 概述 组合逻辑电路的分析和设计方法 若干常用组合逻辑电路

§3.3.1 编码器(Encoder) §3.3.2 译码器(Decoder) §3.3.3 数据分配器(Demultiplexer)

例:3位二进制(3线-8线)译码器框图如下所示:

图3.3.5

3线-8线译码器框图

二进制译码器可采用二极管与门阵列或三极管集 成门电路等构成。

(1)二极管与门阵列译码器电路 0(0V) 1(3V)

表3-3-4

74LS42功能表

74LS42逻辑电路图及各输出表达式如下所示:

Y 0 Y 1 Y 2 Y 3 Y 4 Y5 Y 6 Y 7 Y8 Y9 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0

Y3

Y2

Y1

Y0

§3.3 若干常用的组合逻辑电路

目前,一些常用的逻辑电路已经制成了中、小 规模集成化电路产品。

§3.3.1 编码器(Encoder)

“编码”:即为了区分一系列不同的事物,将其 中的每个事物用一个二值代码表示。 编码器的逻辑功能:把输入的每一个高、低电平 信号变成一个对应的二进制代码。

第三章

Chapter 3

组合逻辑电路

Combinational Logic Circuit

本章主要内容

第一节 第二节 第三节 概述 组合逻辑电路的分析和设计方法 若干常用组合逻辑电路

§3.3.1 编码器(Encoder) §3.3.2 译码器(Decoder) §3.3.3 数据分配器(Demultiplexer)

数字逻辑与计算机组成 第3章 组合逻辑电路

硬件资源:7个4输入与门、1个7输入或门

10

1.4 组合逻辑电路设计

利用布尔代数化简, 以减少逻辑门数和输入端数 X·Y+X·Y’=X

F = SN3N2N1N0(1,2,3,5,7,11,13) =N3’N0+N3’ N2’ N1 N0’+N3 N2’ N1 N0+N3 N2 N1’ N0

非法值 • 信号值不能被有效识别为高电平或低电平,处于不确定状态。 例如:下图中的信号X

不管A是0还是1,F结点都会同时 被高电平和低电平驱动,可能导 致在F结点处之间有较大电流流动 ,使电路发热而被损坏

16

1.5 无关项、非法值和高阻态

例:设计一个检测电路,当NBCD(8421)码数值大于5时,输出为1

最简输出表达式

函数转换:独立逻辑门、中间组件、可编程器件

画出逻辑电路图 逻辑器件的标准符号,输入、输出信号、器件标识

评价电路

电路分析:功能、缺陷、电气特性等

9

1.4 组合逻辑电路设计

例1:素数检测器的设计

列出真值表

• 4-bit input, N3N2N1N0

写出最小项表达式 F = SN3N2N1N0(1,2,3,5,7,11,13)

输出变量:故障信号F 正常工作为0,发生故障为1

故障状态 真 值 表 RY G F

0 0 01 0 0 10 0 1 00 0 1 11 1 0 00 1 0 11 1 1 01 1 1 11

13

1.4 组合逻辑电路设计

逻辑抽象结果

真值表

RY G F

000 1 001 0 010 0 011 1 100 0 101 1 110 1 111 1

每个输入端和输出端只有高电平、

《数字电子技术》第3章 组合逻辑电路

Y1 I2 I3 I6 I7

Y3 ≥1 I9 I8

Y3

I2I3I6I7

&

Y0 I1 I3 I5 I7 I9

I1I3I5I7I9

I9 I8

逻辑图

Y2

Y1

Y0

≥1

≥1

≥1

I7I6I5I4

I3I2

(a) 由或门构成

Y2

Y1

I1 I0 Y0

&

&

&

I7I6I5I4

I3I2

(b) 由与非门构成

A

消除竞争冒险

B

C

Y AB BC AC

2

& 1

1

3

&

4

&

5

≥1

Y

3.2 编码器

编码

将具有特定含义的信息编 成相应二进制代码的过程。

编码器(即Encoder)

实现编码功能的电路

被编 信号

编 码 器

编码器

二进制编码器 二-十进制编码器

二进制 代码 一般编码器

优先编码器 一般编码器 优先编码器

(1) 二进制编码器

A B F AB AB B

&

&

00

1

01

0

C

&

F &

10 11

0F AABA BC1 AB &

1

AAB BC AB

(4)分析得出逻辑功A能 A B B C AB

A =1

同或逻辑 AB AB B

F

F AB AB A☉B

3.1.3 组合逻辑电路的设计

组合逻辑电路的设计就是根据给出的实际逻 辑问题求出实现这一关系的逻辑电路。

Y3 ≥1 I9 I8

Y3

I2I3I6I7

&

Y0 I1 I3 I5 I7 I9

I1I3I5I7I9

I9 I8

逻辑图

Y2

Y1

Y0

≥1

≥1

≥1

I7I6I5I4

I3I2

(a) 由或门构成

Y2

Y1

I1 I0 Y0

&

&

&

I7I6I5I4

I3I2

(b) 由与非门构成

A

消除竞争冒险

B

C

Y AB BC AC

2

& 1

1

3

&

4

&

5

≥1

Y

3.2 编码器

编码

将具有特定含义的信息编 成相应二进制代码的过程。

编码器(即Encoder)

实现编码功能的电路

被编 信号

编 码 器

编码器

二进制编码器 二-十进制编码器

二进制 代码 一般编码器

优先编码器 一般编码器 优先编码器

(1) 二进制编码器

A B F AB AB B

&

&

00

1

01

0

C

&

F &

10 11

0F AABA BC1 AB &

1

AAB BC AB

(4)分析得出逻辑功A能 A B B C AB

A =1

同或逻辑 AB AB B

F

F AB AB A☉B

3.1.3 组合逻辑电路的设计

组合逻辑电路的设计就是根据给出的实际逻 辑问题求出实现这一关系的逻辑电路。

电工电子技术及应用 第十章 组合逻辑电路及其应用

级别最低。 也就是说, 当 = 0 时, 其余输入信号无论是 0 还是 1 都不起作用, 电路只对 进行编码

, 输出

为反码, 其原码为 111。 又如, 当 = 1、 = 0 时, 则电路只对 进行编码

, 输出

原码为 110。 其余类推。

第 10 章 组合逻辑电路及其应用

(2) 选通输入端 的作用。 当 = 1 时, 门 G1输出 0, 所有输出与或非门都被封锁, 输出

10.2 组合逻辑电路的分析

第 10 章 组合逻辑电路及其应用

1. 分析方法 逻辑电路的分析, 就是根据已知的逻辑电路图来分析电路的逻辑功能。 其分析步骤如下:

(1) 写出输出变量对应于输入变量的逻辑函数表达式。 由输入级向后递推, 写出每个门输出对应于输入的逻辑关系, 最后得出输出信号对应于输入信号的逻辑

从输出量来看, 若组合逻辑电路只有一个输出量, 则称为单输出组合逻辑电路; 若组合逻辑电路有多个 输出量, 则称为多输出组合逻辑电路。 任何组合逻辑电路, 不管是简单的还是复杂的, 其电路结构均满足如 下特点: 由各种类型逻辑门电路组成, 电路的输入和输出之间没有反馈, 电路中不含存储单元。

第 10 章 组合逻辑电路及其应用

第 10 章 组合逻辑电路及其应用

10.3.1 编码器

为了区分一系列不同的事物, 将其中的每个事物用一个二值代码表示, 这就是编码的含义。 在二值逻辑

电路中, 信号都是以高、 低电平的形式给出的。 因此, 编码器的逻辑功能就是把输入的每一个高、 低电平

信号编成一个对应的二进制代码。图 10.3.1 所示为 8 线—3 线优先编码器 CT74148 的逻辑图

可由输入

决定; 当 X= 1 时, 则表示本级编码器不再编码, 输出

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

组合逻辑电路描述

reg [1:0] Sel; reg [7:0] A, B,C,D; reg [7:0] Y1, Y2, ; …… always @( Sel or A or B or C or D ) begin Y1、Y2在有些分支中 、 在有些分支中 …… 没有明确的赋值, 没有明确的赋值,导致出现 case(Sel) 2’b00: Y1 = A; 不必要的Latch 不必要的 2’b01: Y 2= B; 2’b10: Y1 = C; 2’b11: Y 2= D; default: Y1 = ~(A&B) ; endcase …… end ……

assign赋值语句中,被赋值的变量/信号一定为wire类型。

对复杂的组合逻辑结构,用always (敏感表) Stm形式加以描述

组逻辑电路描述

描述结构: Data Path Control Path 具体电路形式: Multiplexers Encoder / priority encoder Decoder Comparator Alu Logic /arithmetic operations

Outputs

Y2 Y1 Y0 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1

组合逻辑电路描述

reg [7:0] A; reg [2:0]Y; …….. always @(A) begin if (A==8’b00000001) Y=3’b000; else if (A==8’b00000010) Y=3’b001; else if (A==8’b00000100) Y=3’b010; else if (A==8’b00001000) Y=3’b011; else if (A==8’b00010000) Y=3’b100; else if (A==8’b00100000) Y=3’b101; else if (A==8’b01000000) Y=3’b110; else if (A==8’b10000000) Y=3’b111; else Y=3’bxxx; end reg [7:0] A; reg [2:0]Y; …….. always @(A) casex(A) 8’b00000001: 8’b00000010: 8’b00000100: 8’b00001000: 8’b00010000: 8’b00100000: 8’b01000000: 8’b10000000: default: endcase

1 , X , Z }中的一个, 中的一个, 中的一个

外层的case语句是满的, 但内层的case语句不满, 产生Latch以保持Y1

组合逻辑电路描述

module examp1(A1, B1, C1, A2, B2, C2, D2, Y1, Y2); input [8:0] A1, B1, C1, A2, B2, C2, D2; output [10:0] Y1, Y2; reg [10:0] Y1, Y2; always @(A1 or A2 or B1 or B2 or C1 or C2 or D1 or D2) begin Y1 <= A1 + B1 + C1 + D1 ; Y2 <= ( A2 + B2 ) + ( C2 + D2 ) ; end A2 endmodule + A1 B2 B1 C1 D1

组合逻辑电路描述

多路选择开关 二选一开关建议用if…else…结构描述; 三/四选一开关可用if…else…结构、 case/casex/casez结构描述 多选一开关建议不采用if…else…结构描 述 HDL描述中,注意if…else…及其结构嵌套 结构、case/casex/casez结构的完整性。

组合逻辑电路描述

reg [1:0] Sel1, Sel2; reg [7:0] A, B,C,D; reg [7:0] Y1; …… always @( Sel1or Sel2 or A or B or C or D ) begin …… case(Sel1) 每一个二进制数的取值为{ 每一个二进制数的取值为 0, 2’b00: Y1 = A + 1; 即有四种可能的取值 2’b01: Y 1= A + B; 2’b10: Y1 = !C ; 2’b11: case (Sel2) 2’b00: Y1 = D - A; 2’b01: Y1 = A & B; 2’b10: Y1 = A | B; 2’b11: Y1 = ! D; endcase default: Y1 = ~(A&B) ; endcase …… end ……

组合逻辑电路描述

编码/解码电路

将一组形式的二进制数据转化为另一种形式的二进制数据

形式上,编码 解码电路可采用 解码电路可采用: 形式上,编码/解码电路可采用:

if …else 及其嵌套结构 及其嵌套结构; case/casex/casez描述结构; 描述结构; 描述结构 for 循环结构(一般避免采用) 循环结构(一般避免采用)

+

+ +

+

Y1 C2 D2

Y2

+

组合逻辑电路描述

…….. reg [7:0] A, B, C, D, E, F, G, H; reg [8:0] Sum; reg [1:0] sel; ………. always (sel or A or B or C or D or E or F or G or H) A begin Sum=9’b0; B case (Sel) 2’b00: Sum = A +B; C 2’b01: Sum = C + D; D 2’b10: Sum = E + F; E 2’b11: Sum = G + H; F endcase G end H ………..

Sum +

组合逻辑电路描述

描述方式 对简单的电路结构,可用连续赋值语句加以描 述;

reg [7:0] a,b; wire [7:0] c; assign c= a&b; reg a, b, cin; wire sum, cout; assign {sum,cout}= {a^b^c, (a&b)|(a&c)|(b&c)};

组合逻辑电路描述

reg [1:0] Sel; reg [7:0] A, B,C,D; reg [7:0] Y; …… always @( Sel or A or B or C or D ) begin …… case(Sel) 2’b00: Y = A; 分支不满 2’b01: Y = B; 出现Latch 2’b10: Y = C; 2’b11: Y = D; endcase …… end …… reg [1:0] Sel; reg [7:0] A, B,C,D; reg [7:0] Y; …… always @( Sel or A or B or C or D ) begin …… case(Sel) 2’b00: Y = A; 2’b01: Y = B; 2’b10: Y = C; 2’b11: Y = D; default: ; endcase …… 分支虽满,但属于值保持, end 出现Latch ……

设计描述

从16位乘法器的设计谈起

组合逻辑电路 描述

组合逻辑电路描述

同步时序逻辑电路的时钟频率直接取决于组合通 路(包括数据通路、控制通路)的延迟时间; 在深亚微米工艺条件下,组合逻辑通路的延迟时 间与组合逻辑通路的延迟级数(即逻辑级数)密 切相关; 降低组合逻辑通路的逻辑级数成为组合通路设计 优化的关键因素; 组合逻辑电路的功耗及其所占用的芯片面积直接 与电路中的单元数目、逻辑连线数目相关; 减少组合逻辑电路实现所需的单元及连线数目成 为组合逻辑电路设计优化的重要因素。

组合逻辑电路描述

inputs

A7 A6 A5 A4 A3 A2 A1 A0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0

Y=3’b000; Y=3’b001; Y=3’b010; Y=3’b011; Y=3’b100; Y=3’b101; Y=3’b110; Y=3’b111; Y=3’bxxx;

组合逻辑电路描述

有时也可用for 循环结构描述编码/解码逻辑电路, 但一般不建议采用(综合结果很差)

reg [7:0] A, B; reg [2:0] I, Y; …… for (I=0; I<=7;I=I+1) begin B=A; B[I] = 1’b0; if (A[I]==1’b1 && B==8’b0) Y=I; else Y=3’bxxx; end ……

逻辑模拟结果正确

综合结果差!!!

组合逻辑电路描述

inputs

A7 A6 A5 A4 A3 A2 A1 A0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 x 0 0 0 0 0 0 1 x x 0 0 0 0 0 1 x x x 0 0 0 0 1 x x x x 0 0 0 1 x x x x x 0 0 1 x x x x x x 0 1 x x x x x x x

什么情况下会引入Latch? 条件或分支语句中,对信号赋值说明不完全、 条件或分支语句中,对信号赋值说明不完全、 且信号在条件或分支语句前没有初始赋值。 且信号在条件或分支语句前没有初始赋值。

组合逻辑电路描述

…… reg A1,A2,B1,B2; reg En1,En2; reg Y1,Y2,M; …… always @( En1 or En2 or A1 or A2 or B1 or B2) begin En1=0时,Y1取值情形 if (En1) Y1 = A1; 没有说明,产生Lacth if (En2) begin Y2 = !((A2 & B2) | B1) ; M = Y2 | Y1; En2=0时,Y2、M的取值情形 end 没有说明,产生Lacth以保持M、Y2 end 的取值 ……