第06章 输入输出接口和中断技术(第4部分) 微机原理与接口技术 课件

合集下载

《微机原理与接口技术》课件——第6章输入输出及中断系统

பைடு நூலகம்

CB

AB

DB

CPU

数据端口

状态端口

I/O

设

备

译

码

控制端口

图7.3 I/O接口的基本结构

I/O接口

5、I/O端口的编址 微机系统中,I/O端口的编址方式分为统一编址和独立编址两大类。在Intel 80x86系列微机中,采用独立编址方式。 (1). I/O端口的统一编址方式 统一编址又称存储器映象编址(Memory-mapping Address Coding),就是将I/O端口看成是存储器空间的一个组成部分,按照存储器单元的编址方法统一编排地址号,每个I/O端口占用一个地址。这样,CPU对I/O端口的输入/输出操作如同对存储单元的读/写操作一样,对存储器的各种寻址方式也同样适用于I/O端口。

DB

输

出

设

备

&

数据

地址

译码器

数据端口

译码输出

地址总线

DB

状态端口

译码输出

状态

寄存器

BUSY

+5 V

锁

存

器

Q

D

数据总线DB

来自CPU

选通信号

ACK

WR

IO

/

M

R

&

RD

IO

/

M

图7.9 查询式输出的接口电路

(2)程序中断的输入/输出方式 该方式借助于CPU响应外部中断请求的能力,实现输入输出的控制。简单地说,就是外设将准备就绪的信号转换成有效的中断请求信号通知给CPU,CPU响应中断后,在中断服务子程序中执行I/O指令,进行数据传送。 查询传送方式是由CPU来查询外设的状态,CPU处于主动地位,而外设处于被动地位。中断传送方式则是由外设主动向CPU发出请求,等候CPU处理,在没有发出请求时,CPU和外设都可以独立进行各自的工作。

微机原理与接口技术课件PPT

汇编语言的优点

汇编语言具有高效、可移植性、 可维护性等优点,适用于编写操 作系统、编译器等关键软件。

汇编语言的缺点

汇编语言编写复杂,容易出错, 且可移植性较差,需要针对不同 的计算机体系结构进行修改。

高级语言

01

高级语言的定义

高级语言是一种抽象程度更高的 编程语言,它使用更接近自然语 言的语法和语义。

实验提供参考。

THANKS FOR WATCHING

感谢您的观看

串行接口的数据传输速率比并行 接口慢,但只需要一根数据线, 因此成本较低。

03

串行接口的常见标准包括RS-232 、RS-422和USB。

04

中断控制器

中断控制器是微机中的一 种重要组件,它负责管理 计算机系统中断的处理。

中断控制器可以管理硬件 设备的中断请求,例如键 盘、鼠标和计时器等。

ABCD

并行接口通常用于连接打印机、磁盘驱动器等高速设备, 因为这些设备需要快速传输大量数据。

并行接口的常见标准包括ECP、EPP和USB。

串行接口

01

串行接口是一种数据传输方式, 它通过单个数据线逐位传输数据 。

02

串行接口通常用于连接鼠标、调 制解调器等低速设备,因为这些 设备不需要快速传输大量数据。

语音识别和图像处理

利用微机原理与接口技术,可以实现语音识 别和图像处理等功能,提高办公自动化水平 。

在家用电器中的应用

1 2 3

智能家居控制

微机原理与接口技术可以用于智能家居控制,实 现家用电器的远程控制和自动化控制。

电视和音响设备控制

通过微机原理与接口技术,可以实现电视和音响 设备的智能控制,提供更加便捷和智能的娱乐体 验。

微机原理及接口技术课件

外存储器是微机系统中的低速存储器, 用于长期存储大量数据和程序。

中央处理器是微机系统的核心,负责执 行程序中的指令。

内存储器是微机系统中的高速存储器, 用于存储程序和数据。

微机系统的软件结构

微机系统的软件结构包括系统软件和 应用软件。

应用软件是根据特定需求开发的软件 ,如办公软件、图像处理软件等。

通过微机接口实验,使 学生掌握微机接口的基 本原理和应用技术,培 养学生对微机系统的综 合分析和设计能力。

微机接口实验通常包括 以下几个方面的内容

通过实验箱或实验板等 硬件设备,让学生了解 并掌握各种硬件接口的 工作原理和性能特点。

通过编写软件程序,让 学生掌握各种输入/输出 控制方式、中断处理、 DMA传输等软件接口的 控制原理和编程方法。

计算机的基本组成 包括运算器、控制 器、存储器、输入 输出设备。

控制器是计算机的 指挥中心,负责控 制和协调计算机的 各个部件。

输入输出设备用于 与外部进行信息交 流,如键盘、鼠标 和显示器等。

微机系统的硬件结构

微机系统的硬件结构包括中央处理器、 内存储器、外存储器、输入输出设备等 。

输入输出设备用于与外部进行信息交流 ,如键盘、鼠标和显示器等。

接口技术

包括串行接口、并行接口、USB接口等技术 ,实现微机与其他设备的通信。

C/C语言

一种高级编程语言,广泛应用于微机应用系 统的开发。

中断技术

实现微机应用系统中断处理和任务调度的重 要技术。

06

CATALOGUE

微机接口实验及课程设计

微机接口实验的目的与内容

目的

内容

硬件接口实验

软件编程实验

综合实验

。

串行接口的实现

中央处理器是微机系统的核心,负责执 行程序中的指令。

内存储器是微机系统中的高速存储器, 用于存储程序和数据。

微机系统的软件结构

微机系统的软件结构包括系统软件和 应用软件。

应用软件是根据特定需求开发的软件 ,如办公软件、图像处理软件等。

通过微机接口实验,使 学生掌握微机接口的基 本原理和应用技术,培 养学生对微机系统的综 合分析和设计能力。

微机接口实验通常包括 以下几个方面的内容

通过实验箱或实验板等 硬件设备,让学生了解 并掌握各种硬件接口的 工作原理和性能特点。

通过编写软件程序,让 学生掌握各种输入/输出 控制方式、中断处理、 DMA传输等软件接口的 控制原理和编程方法。

计算机的基本组成 包括运算器、控制 器、存储器、输入 输出设备。

控制器是计算机的 指挥中心,负责控 制和协调计算机的 各个部件。

输入输出设备用于 与外部进行信息交 流,如键盘、鼠标 和显示器等。

微机系统的硬件结构

微机系统的硬件结构包括中央处理器、 内存储器、外存储器、输入输出设备等 。

输入输出设备用于与外部进行信息交流 ,如键盘、鼠标和显示器等。

接口技术

包括串行接口、并行接口、USB接口等技术 ,实现微机与其他设备的通信。

C/C语言

一种高级编程语言,广泛应用于微机应用系 统的开发。

中断技术

实现微机应用系统中断处理和任务调度的重 要技术。

06

CATALOGUE

微机接口实验及课程设计

微机接口实验的目的与内容

目的

内容

硬件接口实验

软件编程实验

综合实验

。

串行接口的实现

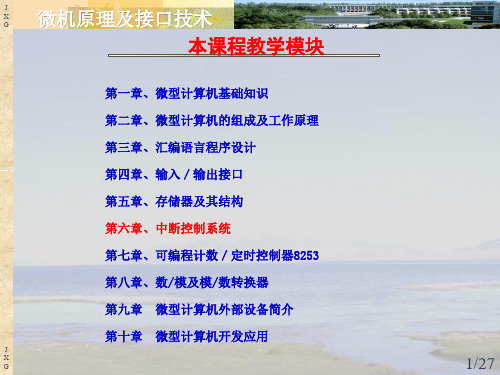

《微机原理及接口技术》第六章

2、CPU对中断的响应

关中断:CPU响应中断后,发中断响应(INTA)信号的同时,内部自动实现关中断 保留断点:封锁IP+1,入栈保存CS:IP。 保护现场:由中断服务程序先将有关REG入栈保存。

给出中断入口、转相应的中断服务程序:中断服务程序起始地址,执行中断服务。

恢复现场:将中断服务程序入栈保存的REG内容弹出,恢复现场。 开中断与返回:中断服务的最后一条指令,出栈恢复CS:IP,恢复主程序运行,使IF自动恢

第十章

J X G

微型计算机开发应用

1/27

J X G

微机原理及接口技术 第六章、中断控制系统

本章要点:

J X G

中断的基本概念 中断处理过程 可编程中断控制器8259A的结构、功能 可编程中断控制器8259A的应用

2/27

J X G

微机原理及接口技术 6.1

一、中断的基本概念

中断系统

J X G

微机原理及接口技术

三、外部中断

8086芯片设置有两条中断请求信号输入引脚:NMI和INTR引脚,用于外部中断 源产生的中断请求,可分为以下两种: 1、可屏蔽中断 INTR (18脚) INTR线上的请求信号是电平触发的。当IF=0,CPU中断不响应,这种情况称为 可屏蔽中断。可屏蔽中断通过指令设置IF中断标志位,达到控制的目的。 STI CLI ;IF←1,开中断,CPU才能响应INTR线上的中断请求。 ;IF←0,关中断,CPU不响应INTR线上的中断请求。

对于系统专用中断,系统将自动提供0~4中断类型号,保证系统自动转到处理程序。

J X G

对于可屏蔽中断INTR,外接口电路产生中断类型号。目前8259A产生。

第章输入输出接口及中断技术X课件

“0”

IO接口电路

0

1

0

74LS138

看看具体 工作过程

输入

输出

Y0 Y1 Y2 Y3 Y4 Y5

Y6 Y7

A5 A6 A7

IOW

A B C

G2B G2A G1

74LS138

DMA CS(8237) INTR CS(8259) T/C CS(8253) PPI CS(8255)

WRTNMIREG (写NMI屏蔽寄存器)

+5v

“1”

“1”

“1”

“0”

I O 接 口 电 路

Hale Waihona Puke 74LS688低3位由A2、A1、A0决定为111

高7位由决定DIP开关通过比较器74LS688

DIP开关

四、使用可编程逻辑器件译码 (GAL、FPGA、CPLD)

是借助EDA手段可以设计专门的译码器,例如

AEN A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2. 状态信息 状态信息作为CPU与外设之间交换数据时的联络信息,反映了当前外设所处的工作状态,是外设通过接口送往CPU的。CPU通过对外设状态信号的读取,可得知输入设备的数据是否准备好、输出设备是否空闲等情况。对于输入设备,一般用准备好(READY)信号的高低来表明待输入的数据是否准备就绪;对于输出设备,则用忙(BUSY)信号的高低表示输出设备是否处于空闲状态,如为空闲状态,则可接收CPU输出的信息,否则CPU要暂停送数。因此,状态信息能够保障CPU与外设正确地进行数据交换。

小 结

返回

二、端口(PORT)

I/O端口:是指I/O接口中存放数据信息、状态信息和控制信息,CPU可以读/写的一组寄存器或特定电路,被称为I/O端口。 一般接口通常有数据端口、控制端口、状态端口 数据端口:(I、O) 输入数据端口(I):保存外设给CPU的数据 输出数据端口(O):保存CPU给外设的数据 状态端口:(I) 存放I/O设备或接口本身的工作状态信息 控制端口:(O) 存放CPU给外设或接口电路的命令

IO接口电路

0

1

0

74LS138

看看具体 工作过程

输入

输出

Y0 Y1 Y2 Y3 Y4 Y5

Y6 Y7

A5 A6 A7

IOW

A B C

G2B G2A G1

74LS138

DMA CS(8237) INTR CS(8259) T/C CS(8253) PPI CS(8255)

WRTNMIREG (写NMI屏蔽寄存器)

+5v

“1”

“1”

“1”

“0”

I O 接 口 电 路

Hale Waihona Puke 74LS688低3位由A2、A1、A0决定为111

高7位由决定DIP开关通过比较器74LS688

DIP开关

四、使用可编程逻辑器件译码 (GAL、FPGA、CPLD)

是借助EDA手段可以设计专门的译码器,例如

AEN A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2. 状态信息 状态信息作为CPU与外设之间交换数据时的联络信息,反映了当前外设所处的工作状态,是外设通过接口送往CPU的。CPU通过对外设状态信号的读取,可得知输入设备的数据是否准备好、输出设备是否空闲等情况。对于输入设备,一般用准备好(READY)信号的高低来表明待输入的数据是否准备就绪;对于输出设备,则用忙(BUSY)信号的高低表示输出设备是否处于空闲状态,如为空闲状态,则可接收CPU输出的信息,否则CPU要暂停送数。因此,状态信息能够保障CPU与外设正确地进行数据交换。

小 结

返回

二、端口(PORT)

I/O端口:是指I/O接口中存放数据信息、状态信息和控制信息,CPU可以读/写的一组寄存器或特定电路,被称为I/O端口。 一般接口通常有数据端口、控制端口、状态端口 数据端口:(I、O) 输入数据端口(I):保存外设给CPU的数据 输出数据端口(O):保存CPU给外设的数据 状态端口:(I) 存放I/O设备或接口本身的工作状态信息 控制端口:(O) 存放CPU给外设或接口电路的命令

微机原理与接口技术课件 06 基本输入输出接口67页PPT

25、学习是劳动,是充满思想的劳动。——乌申斯基

谢谢!

21、要知道对好事的称颂过于夸大,也会招来人们的反感轻蔑和嫉妒。——培根 22、业精于勤,荒于嬉;行成于思,毁于随。——韩愈

23、一切节省,归根到底都归结为时间的节省。——马克思 24、意志命运往往背道而驰,决心到最后会全部推倒。——莎士比亚

微机原理与接口技术课件 06 基本输 入输出接口

51、没有哪个社会可以制订一部永远 适用的 宪法, 甚至一 条永远 适用的 人们通常会发现,法律就是这样 一种的 网,触 犯法律 的人, 小的可 以穿网 而过, 大的可 以破网 而出, 只有中 等的才 会坠入 网中。 ——申 斯通 54、法律就是法律它是一座雄伟的大 夏,庇 护着我 们大家 ;它的 每一块 砖石都 垒在另 一块砖 石上。 ——高 尔斯华 绥 55、今天的法律未必明天仍是法律。 ——罗·伯顿

谢谢!

21、要知道对好事的称颂过于夸大,也会招来人们的反感轻蔑和嫉妒。——培根 22、业精于勤,荒于嬉;行成于思,毁于随。——韩愈

23、一切节省,归根到底都归结为时间的节省。——马克思 24、意志命运往往背道而驰,决心到最后会全部推倒。——莎士比亚

微机原理与接口技术课件 06 基本输 入输出接口

51、没有哪个社会可以制订一部永远 适用的 宪法, 甚至一 条永远 适用的 人们通常会发现,法律就是这样 一种的 网,触 犯法律 的人, 小的可 以穿网 而过, 大的可 以破网 而出, 只有中 等的才 会坠入 网中。 ——申 斯通 54、法律就是法律它是一座雄伟的大 夏,庇 护着我 们大家 ;它的 每一块 砖石都 垒在另 一块砖 石上。 ——高 尔斯华 绥 55、今天的法律未必明天仍是法律。 ——罗·伯顿

微型计算机输入输出和中断课件

微型计算机输入 输பைடு நூலகம்和中断课件

目录

• 引言 • 微型计算机的输入输出 • 中断的基本概念 • 中断控制器 • 中断服务例程 • 微型计算机的中断应用

01

引言

课程介绍

01

02

03

课程名称:微型计算机输入输 出和中断

课程性质:专业必修课

适用对象:计算机科学与技术 、软件工程、电子信息工程等

专业本科生

中断的定义和作用

定义

中断是计算机在执行程序过程中,由于出现某种特殊情况,使得计算机暂时停 止正在执行的程序,转去执行相应的处理程序,处理完毕后再返回原程序继续 执行。

作用

中断是计算机系统中实现多任务并发执行的重要机制,它使得CPU能够及时响 应外部事件,提高计算机的实时性和响应能力。

中断的分类

硬件中断

1. 保存被中断程序的现场信息(如寄存器值)

处理流程 2. 执行中断处理程序,完成相应的操作

3. 恢复被中断程序的现场信息

4. 返回到被中断程序继续执行

06

微型计算机的中断应用

中断在实时处理中的应用

实时任务调度

中断可以用于实时任务的调度,当某个实时任务的时间要求 到达时,产生中断,系统响应中断并执行相应的任务处理程 序,保证实时任务的及时完成。

由硬件设备产生的中断,如键盘、鼠标、串 口等。

自愿中断

由程序自愿产生的中断,如进程切换、系统 调用等。

软件中断

由操作系统或应用程序产生的中断,如系统 调用、异常等。

非自愿中断

由程序非自愿产生的中断,如硬件故障、电 源掉电等。

中断处理过程

中断请求

当某个外部事件发生时,相应的设备 会向CPU发出中断请求。

目录

• 引言 • 微型计算机的输入输出 • 中断的基本概念 • 中断控制器 • 中断服务例程 • 微型计算机的中断应用

01

引言

课程介绍

01

02

03

课程名称:微型计算机输入输 出和中断

课程性质:专业必修课

适用对象:计算机科学与技术 、软件工程、电子信息工程等

专业本科生

中断的定义和作用

定义

中断是计算机在执行程序过程中,由于出现某种特殊情况,使得计算机暂时停 止正在执行的程序,转去执行相应的处理程序,处理完毕后再返回原程序继续 执行。

作用

中断是计算机系统中实现多任务并发执行的重要机制,它使得CPU能够及时响 应外部事件,提高计算机的实时性和响应能力。

中断的分类

硬件中断

1. 保存被中断程序的现场信息(如寄存器值)

处理流程 2. 执行中断处理程序,完成相应的操作

3. 恢复被中断程序的现场信息

4. 返回到被中断程序继续执行

06

微型计算机的中断应用

中断在实时处理中的应用

实时任务调度

中断可以用于实时任务的调度,当某个实时任务的时间要求 到达时,产生中断,系统响应中断并执行相应的任务处理程 序,保证实时任务的及时完成。

由硬件设备产生的中断,如键盘、鼠标、串 口等。

自愿中断

由程序自愿产生的中断,如进程切换、系统 调用等。

软件中断

由操作系统或应用程序产生的中断,如系统 调用、异常等。

非自愿中断

由程序非自愿产生的中断,如硬件故障、电 源掉电等。

中断处理过程

中断请求

当某个外部事件发生时,相应的设备 会向CPU发出中断请求。

微型计算机原理与接口技术-第6章输入输出与中断技术ppt课件

四、简单的输出接口举例

锁存器:由D触发器构成〔具有锁存功能〕

通常一个器件包含8个D触发器

常用芯片:

74LS273

74LS273

S

74LS374

S CP Di Qi 0 X X0 1 ↑ 11 1 ↑ 00

D0~D7

A0

A1

▪ ▪

&

▪

A7

IOW

≥

A8 A9

▪& ▪ ▪

A15

74LS273

与

非

用于存储器芯片选通

门

A15 与

~

非

用于I/O芯片选通

A12

门

IO/M

8088最小方式下的原理图

READY RESET

8284A

CLK READY RESET ALE

A19 ~A8 AD7~AD0

8088

+5V

MN/MX DEN DT/R

IO/M

WR RD HOLD HLDA INTR

INTA

存

储

地址 锁存储器

A0 ~ A19

器

8282 地址总线〔20根〕

系

〔三片〕

统

D0 ~ D7 收发器 8286 数据总线〔8根〕 〔一片〕

控制总线

I/O 接 口

节

6.2 简单接口电路

一、 接口电路的根本构造

译码

AB

电路

CPU DB

控制

CB

逻辑

数据输入存放器 (or 三态门)

数据输出存放器 (锁存器)

形状存放器 (or 三态门)

符号 ’8’ ’9’ ’A’ ’B’ ’C’ ’D’ ’E’ ’F’