用FPGA实现浮点FFT处理器的研究

高速浮点FFT处理器的FPGA实现

计数器

H

蝶运模 型 块

蓑I 会l _ ~输 M I

R A 一 一

-

t 控制 器

输I t { 数据

R A

何 最后 ・ 缀写地 址

模

M

块

r :。 h i -

31浮点蝶形运算单 .

31 自定制浮点数据格式 .1 .

图 2 FT F 处理器结构图

F b 2 0 e. 0 6

文章编号:17— 59( 0 6 0 —0 0 0 63 14 20 ) 106— 4

高速浮点 F T处理器的 F GA实现 F P

丁智泉 ,张红雨

( 电子科技 大学电子工程 学院,成都 605 ) 10 4

摘 要 :介 绍 了一种 基 于 F GA 的 12 点 自定义 2 位 浮点 F T处理 器的设 计 。采 用改进 的蝶 形 P 04 4 F

件 x v 00来实现 F T处理器。 c l0 F

3 F T 处理 器 结 构 F

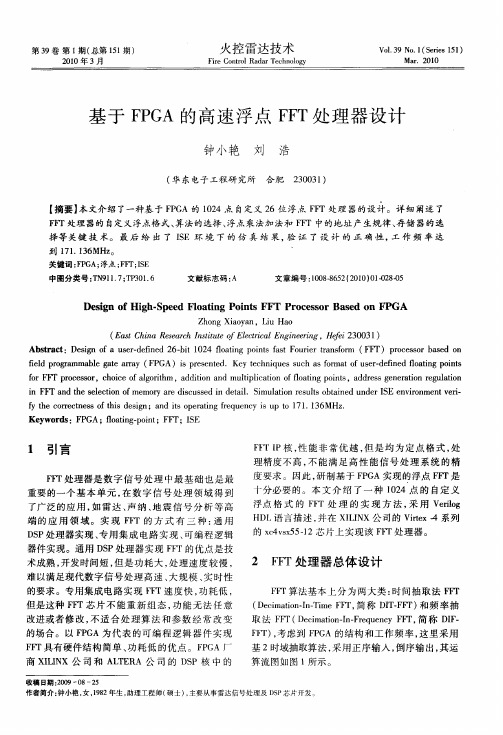

本文中的 F T信号处理器的结构如 2所示。从罔 2 F 中可以看到浚H可 处理器包括: 蝶形运算单元、 旋转因子 R M 、 O 输入数据 R M、 【 A 输}数据 R M 、同址运算 R M 、 I A A 计数器 、 地址产生器和主控制器。

维普资讯

第 1卷 第 1 9 期

20 06年 2月

四川理工学院学报 (自 然科 学版 )

J OURNA1 OF S CHUAN . I UNI VERS T OF I Y

v0 .1 1 9No. 1

S IN E&E CE C NGI E I G( T R C E EE TON、 NE R N NA U ALS INC DII

采用FPGA实现FFT算法

采用FPGA实现FFT算法随着数字技术的快速发展,数字信号处理已深入到各个学科领域。

在数字信号处理中,许多算法如相关、滤波、谱估计、卷积等都可通过转化为离散傅立叶变换(DFT)实现,从而为离散信号分析从理论上提供了变换工具。

但DFT计算量大,实现困难。

快速傅立叶(FFT)的提出,大大减少了计算量,从根本上改变了傅立叶变换的地位,成为数字信号处理中的核心技术之一,广泛应用于雷达、观测、跟踪、高速图像处理、保密无线通信和数字通信等领域。

目前,硬件实现FFT算法的方案主要有:通用数字信号处理器(DSP)、FFT专用器件和现场可编程门阵列(FPGA)。

DSP具有纯软件实现的灵活性,适用于流程复杂的算法,如通信系统中信道的编译码、QAM映射等算法。

DSP完成FFT运算需占用大量DSP的运算时间,使整个系统的数据吞吐率降低,同时也无法发挥DSP软件实现的灵活性。

采用FFT专用器件,速度虽能够达到要求。

但其外围电路复杂,可扩展性差,成本昂贵。

随着FPGA发展,其资源丰富,易于组织流水和并行结构,将FFT实时性要求与FPGA器件设计的灵活性相结合,实现并行算法与硬件结构的优化配置,不仅可以提高处理速度,并且具有灵活性高。

开发费用低、开发周期短、升级简单的特点。

针对某OFDM系统中FFT运算的实际需要,提出了基于FPGA的设计来实现FFT算法,并以16位长数据,64点FFT为例,在Quartus Ⅱ软件上通过综合和仿真。

2 FFT原理及算法结构FFT是离散傅立叶变换(DFT)的快速算法。

对于N点离散的有限长时问序列x(n),其傅里叶变换为:完成N点的DFT需要N2次复数乘法和N(N-1)次复数加法。

点数大时,计算量也大,所以难以实现信号的实时处理。

FFT的基本思想是利用旋转因子WN的周期性、对称性、特殊性以及周期N的可互换性,将长度为N点的序列DFT运算逐次分为较短序列的DFT运算,合并相同项,大大减少了计算量。

基于FPGA的数据采集与处理技术的研究

3、FPGA-based Data Acquisition and Processing System:该系统将数 据采集、处理和传输等功能集成到FPGA中,实现了数据的快速处理和传输。但 系统复杂度高,开发难度较大。

结论与展望

本次演示对基于FPGA的数据采集与处理技术的研究进行了详细探讨。目前,该 领域已取得了显著的成果,但仍存在一些不足和挑战。例如,如何优化算法以 降低硬件资源消耗、提高数据处理速度和精度等问题仍需进一步研究。

文献综述

目前,ARM和FPGA已经在数据采集领域得到了广泛的应用。ARM是一种32位的 微处理器,具有高速的计算能力和丰富的外设接口,可以方便地应用于数据采 集系统中。而FPGA则是一种可编程逻辑器件,具有高度的灵活性和并行计算能 力,可以大大提高数据采集的速度。

然而,现有的ARM与FPGA相结合的数据采集技术还存在一些不足之处。首先, 由于ARM和FPGA的时钟频率不同,容易导致数据传输的同步问题。其次,现有 的技术往往没有充分挖掘ARM和FPGA的潜力,导致数据采集速度和精度还有待 提高。

系统设计

基于FPGA的数据采集与处理系统设计需要结合数据采集和处理的过程,将两者 有机地结合起来。具体步骤如下:

1、确定系统需求:明确系统需要实现的功能和性能指标,如采样频率、分辨 率、数据处理速度等。

2、选择合适的硬件:根据需求,选择合适的FPGA芯片、ADC、传感器等硬件 组件。

3、设计数据采集电路:根据传感器类型和性能指标,设计数据采集电路,包 括信号的放大、滤波、A/D转换等。

研究现状

自20世纪80年代FPGA问世以来,数据采集与处理技术取得了长足的进步。目 前,基于FPGA的数据采集与处理技术主要分为两大类:直接数据采集和间接数 据采集。直接数据采集通过FPGA内部的逻辑资源实现数据采集和处理的同步进 行,具有实时性强的优点,但逻辑资源消耗较大;间接数据采集先将数据传输 到FPGA外部的存储器,再通过软件对数据进行处理,具有数据处理能力强的优 点,但实时性较差。

基于FPGA的FFT算法硬件实现

基于FPGA的FFT算法硬件实现引言:FFT是一种用于将时域信号转换为频域信号的算法,常用于信号处理和图像处理领域。

由于FFT的高计算复杂度,硬件实现可以提供更高的计算效率和并行处理能力。

本文将介绍基于FPGA的FFT算法硬件实现,并详细解释算法的原理和实现过程。

一、快速傅里叶变换(FFT)算法简介快速傅里叶变换(FFT)是一种将一个N点离散序列转换为频域离散序列的算法。

它的时间复杂度为O(NlogN),相比于传统的傅里叶变换算法的时间复杂度O(N^2),FFT算法具有更高的计算效率。

FFT算法的核心思想是将一个N点离散序列划分为其各个子序列,然后再分别计算各个子序列的傅里叶变换,并将结果通过一系列的蝶形运算合并得到最终的频域信号。

二、FFT算法的硬件实现原理基于FPGA的FFT算法实现可以充分发挥FPGA的并行计算能力和灵活性。

硬件实现的核心是设计一个包含多个计算单元的并行处理模块。

常见的FFT硬件实现架构包括基于蝶形运算的位递归FFT算法和基于矩阵运算的线性变换FFT算法。

1.基于蝶形运算的位递归FFT算法实现首先将输入序列分为奇数位和偶数位两个子序列,然后分别对这两个子序列进行FFT计算。

然后将得到的结果通过蝶形运算合并得到最终的频域信号。

在硬件实现中,可以设计一个包含多个蝶形运算单元的并行计算模块。

每个蝶形运算单元包括两个输入通道和两个输出通道,通过并行计算可以同时进行多个蝶形运算操作,提高计算效率。

2.基于矩阵运算的线性变换FFT算法实现线性变换FFT算法将FFT计算表示为矩阵运算的形式,可以充分利用FPGA的向量计算能力。

这种实现方法将输入序列表示为一个复数矢量,然后通过矩阵运算得到最终的频域信号。

在硬件实现中,可以设计一个包含多个矩阵运算单元的并行计算模块。

每个矩阵运算单元可以同时对多个输入进行矩阵运算,提高计算效率。

三、基于FPGA的FFT算法硬件实现步骤1.硬件资源规划:根据需要计算的样本点数N,确定所需的FPGA资源,包括DSP片上资源、BRAM资源和IO资源等。

FPGA FFT_IP核函数的使用说明

FPGA FFT_IP核函数的使用说明一.基本性能特点:(1)采用基-4算法和基-4/2混合基算法;采用频域抽取方式(DIF)的FFT算法;(2)输入数据采用定点方式输入(输入数据为real、imag ,但没有exponent),在运算过程中采用块浮点方式进行运算,使用块浮点结构能够获得最大的SNR 和最少逻辑需求之间的平衡;输出采用指数形式输出(即包含real、imag、exponent),输出结果为:“数据”×(2^(-“指数”));(3)可以完成的FFT变换长度为2^m(6≤m≤14),即64~16384点;数据位宽为8~24bits;(4)如果输入的数据向量不够N点(FFT设置中的转换长度,例如:1024等),则FFT_IP核函数会在输入数据的后面自动进行补0填充,扩展成N点的数据。

(5)输入、输出数据采用有符号复数表示,都采用自然排序方式;(6)支持单倍输出(Signal-output)和四输出(Quad-output)引擎(engine);(7)多路I/O数据流模式:流(Streaming)、缓冲突发(Buffer Burst)、突发(Burst);(8)Version_2.1.0版本的FFT_IP核函数采用的是Atlantic Interface接口协议;Version_7.2版本的FFT_IP核韩式采用的是Avalon Streaming(ST) Interface接口协议。

(9)Version_2.1.0版本不支持RTL级Modelsim仿真,Version_7.2版本支持。

也就是说,2.1.0版本的FFT_IP核函数不能再自己新建的工程中通过QuartusII调用Modelsim进行RTL的仿真。

二.IP_Core的参量设置:(1)Twiddle Precision表示的是旋转因子的位宽精度;Data Precision表示的是输入、输出数据位宽精度。

注意:旋转因子的位宽精度必须小于或等于数据的位宽精度;(2)在Complex Multiplier Implementation选择栏中的Structure列表中选择期望的复数乘法器结构复数乘法器可以使用4个实数乘法器和2个加法/减法器完成,或使用3个乘法器、5个加法器和一些附加的延时单元完成。

基于FPGA的高速FFT算法实现

( r a , ai a n .o e neTcnl y C agh 10 3 C ia A Rl bN t n l i fDf s ehoo ,h nsa4 0 7 , hn ) o U v e g

Ab ta t T e S e d pa ste motcu ilp r n te hg — s e d dgtlp o esn n te E sr c : h p e ly h s rca ati i ・ p e ii rc sig i W h h a h rc ie .n ti p p r f s, aallF r c r sraie ytkn d a tg fa u d c P e evr I s a e , rtap rl F oewa e l d b a ig a v na eo b n a eo F GA h i e z n f

维普资讯

No 2 . Ap . 2 O r,07

微

处

理

机

第2 期

20 07年 4月

MI CROP ROC S ES ORS

基于 FG P A的高速 F T算 法 实 现 F

鲍 庆龙 , 刘 平

( 国防科技大学 A R国家重点实验室, T 长沙 4 07 ) 10 3 摘 要: E 型接收机的高速数字处理 中, 在 W 运算速度是影响系统性能的重要环节之一。结合

一

势。同时运用数字Байду номын сангаас号处理技术对信号进行多分辨

分析获取雷达信号的原始细微特征。由于 E 接收 W 机需要覆盖 比较宽 的瞬时带宽 , 必须使用高速的 A /

法 的工具 。

D P 理器构成 的 F I S处 F’ 处理机采用循 环编码 算法 , 程序量小 , 但存在大量 的冗余运算 , 且需要许 多跳转操作 , 处理速度较慢 , 不能满足数字化接收机 实时性的要求 。在多处理 器构成 的并行处理 系统 中, 使用抽取的方法实现对输入数据的分解 , 达到并 行处理 的目的, 可显著提高计算的速度 , 但在进行大 点数的 F T F 计算时, 存在并行算法与 D P处理器的 S

基于FPGA的高速浮点FFT处理器设计

器件 实现 。通 用 D P处 理器 实 现 F T的优 点 是 技 S F 术成熟 , 发 时间 短 , 是 功耗 大 , 开 但 处理 速 度 较 慢 , 难 以满 足现 代数 字 信 号处 理 高 速 、 规 模 、 时性 大 实

i F n e s lc in o mo y ae d s u s d i ea l i lt n r s l b an d u d rI E e v rn n e - n F T a d t ee t f h o me r r ic s e d ti n .S mu ai e u t o ti e n e n i me t i o s S o vl

Abtat ei f sr e n d2 -i 12 ot gpit f t or rt n ̄ m ( F )poesrbsdo s c:D s no ue— f e 6b 0 4 f a n o s a ui as r F T rcso ae n r g a di t l i n sF e r i d rg m be a r f l porm a l gt ary( P A)i pee t .K yt h iussc s oma o sr e ndf a n o t e a e a FG s rsne d e c nq e uha fr t f e- f e ot gpi s e u di l i n

Hale Waihona Puke ‘ De i n o g S e o tn i t sg fHi h- pe d Fl a i g Po n s FFT o e s r Ba e o PGA Pr c s o s d n F

用FPGA实现FFT的方法

用FPGA实现FFT的方法使用FPGA(Field-Programmable Gate Array)实现FFT(Fast Fourier Transform)可以提供高性能的信号处理能力。

FFT是一种将时域信号转换为频域信号的算法,广泛应用于数字信号处理、通信系统、图像处理等领域。

下面将介绍一种常见的方法来使用FPGA实现FFT。

首先,需要了解FFT算法的基本原理。

FFT将长度为N的离散时间信号x(n)转换为N个频谱分量X(k),其中k=0,1,...,N-1、FFT算法的核心是蝶形运算,通过将信号分解成不同的频率分量并逐步组合来实现。

下面是使用FPGA实现FFT的具体步骤:1.设计数据缓存器:在FPGA内部设计一个数据缓存器用于存储输入信号x(n)和输出信号X(k)。

缓存器的宽度和深度取决于输入信号的采样位数和FFT的长度。

2. 数据采集与预处理:使用FPGA的输入模块采集外部信号,并通过FIFO(First In First Out)缓冲区将数据传输到数据缓存器中。

为了提高计算速度,可以使用预处理方法如窗函数、数据重排等来优化输入信号的质量。

3.蝶形运算模块设计:FFT算法的核心是蝶形运算。

在FPGA中,设计一个蝶形运算模块用于计算FFT算法中的每一个蝶形运算,即通过求解两个复数的乘积,并进行加法运算得到结果。

该模块需要实现乘法器和加法器,并对数据进行并行计算。

4.快速蝶形运算网络构建:将蝶形运算模块按照FFT算法中的乘积因子进行连接,并根据FFT的长度设计合适的网络结构。

可以使用串行-并行方式或并行-串行方式来实现FFT算法。

需要注意的是,为了减少延迟,可以采用流水线技术来提高运算速度。

5.数据输出与后处理:设计一个输出模块将计算得到的频域信号X(k)输出到外部。

可以通过FPGA的输出模块将数据传输到外部存储器、显示器或其他设备进行后续处理。

6. 时钟和时序设计:在FPGA中需要设计合适的时钟频率和时序来保证FFT算法的准确性和稳定性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

国防科技大学学报第26卷第6期JOURNAL OF NATIONAL UNIVERSITY OF DEFENSE TECHNOLOGY Voi.26No.62004文章编号:1001-2486(2004)06-0061-04用FPGA实现浮点FFT处理器的研究*王远模,赵宏钟,张军,付强(国防科技大学电子科学与工程学院,湖南长沙410073)摘要:针对定点FFT处理器精度不高的缺点,提出了浮点格式FFT处理器的FPGA硬件实现方案。

详细阐述了FFT处理器的自定制浮点格式确定、算法选择和浮点加法实现等关键技术。

该处理器已投入使用,工作性能稳定,系统时钟80MHz,完成1024点FFT/IFFT运算只需64!s,误差小于-80dB。

关键词:FPGA;FFT;蝶形运算中图分类号:TN47 文献标识码:AThe Realization of Flolating-point FFT Processor with FPGA ChipWANG Yuan-mo,ZHAO Hong-zhong,ZHANG Jun,FU Oiang(Coiiege of Eiectronic Science and Engineering,Nationai Univ.of Defense Technoiogy,Changsha410073,China)Abstract:The FPGA reaiization of a fioating-point FFT processor is proposed to get over the poor precision of the fixed-point FFT processor.The definition of the fioating-point format,the seiection of arithmetic and the key technigues of the FPGA reaiization are discussed.Such a processor has been put into service and has stabie performance.Its operating freguency is 80MHz and it can finish1024point FFT/IFFT in64!s with an error iess than-80dB.Key words:FPGA;FFT;butterfiy computation在现代雷达、通信、图像处理等领域中,数字信号处理系统经常要进行高速、高精度的FFT运算。

实现FFT有两种方式:通用DSP实现和专用集成电路实现。

通用DSP实现的优点是硬件开发和软件编程技术成熟、开发时间短,缺点是硬件电路复杂、功耗大。

专用集成电路实现的优点是速度快、功耗低,整个FFT运算由一块芯片完成,缺点是开发时间长、成本高。

现场可编程逻辑阵列(FPGA:Fieid Programmabie Gate Array)是一种半定制集成电路,具有面向数字信号处理算法的物理结构。

用FPGA 实现FFT处理器具有硬件系统简单、功耗低的优点,同时具有开发时间较短、成本较低的优势。

国内外学者在用FPGA实现FFT处理器方面做了大量的工作[1~3],取得了许多成果。

但是在这些处理器中,由于数据格式采用定点方式,处理精度不高,不能满足高性能信号处理系统的精度要求,为此,本文提出了浮点数据格式的FFT处理器的硬件实现,并用FPGA器件(XC2V1000)实现了一个可变长度的FFT/IFFT处理器。

1 关键技术1.1 自定制浮点数据格式在标准IEEE单精度浮点格式中,其数值用32bit表示。

其中,bit31是符号位,用!表示;bit30~ bit23是指数位,用"表示;bit22~bit0是尾数位,用#表示。

则数值$有如下表示:{)(1)$=(-1)!X2"-127X(1.#)(";0)$=0 ("=0用FPGA实现标准浮点格式的FFT处理器时,占用资源严重。

为了克服这个缺点,该处理器内部采用自定制的浮点数据格式。

为了确定合适的自定制浮点格式,下面分析蝶形运算对处理器中的数据动态范围的影响[4]。

基2蝶形运算用数学式表示有*收稿日期:2004-05-20作者简介:王远模(1973—),男,博士生。

X m +1(p )=X m (p )+X m (g )·W r N X m +1(g )=X m (p )-X m (g )·W {r N (2)其中,X m (p )和X m (g )为输入数据,X m +1(p ),X m +1(g )为输出数据,W r N 是1的一个复根,称为旋转因子。

由式(2)可得[4]:I X m +1(p )I 2+I X m +1(g )I 2[]212!=2I X m (p )I 2+I X m (g )I 2[]212(3)max {I X m (p )I ,I X m (g )I }S max {I X m +1(p )I ,I X m +1(g )I }S 2max {I X m (p )I ,I X m (g )I }(4)因此,蝶形运算使输出数据的模值扩大到输入数据的2倍。

在实际工程应用中,FFT 运算的输入数据通常是中频采样、变频、滤波后的12-bit 、16-bit 、32-bit 定点数据。

浮点数据的动态范围由指数确定,该处理器中用6-bit 表示,能表示380dB 动态范围内的数据。

浮点数尾数的位数决定FFT 运算的处理精度,在高性能的信号处理系统中,要求其运算误差足够小,一般在-80dB 以下。

根据理论分析和仿真,该处理器用17-bit 表示浮点数的尾数。

根据以上分析,自定制浮点数据格式用24-bit 表示:bit23是符号位,用S 表示;bit22~bit17是指数位,用e'表示;bit16~bit0是尾数位,用f '表示。

其数值1表示为:1=(-1)S >2e'-127>(1.f') (e';0)1=0 (e'=0{)(5)用FPGA(XCV1000)实现两个标准格式的浮点实数相加需要584个slices ;实现两个自定制格式的浮点实数相加只需要277个slices ;实现两个标准格式的浮点实数相乘需要285个slices 和4个MULT18X18s ;实现两个自定制格式的浮点实数相乘只需要50个slices 和1个MULT18X18s ,所以,在处理器内部采用自定制浮点数据格式能有效减少实现处理器的硬件资源占用。

1.2 FFT 算法选择提高FFT 处理速度的四个主要技术途径是采用流水线结构、并行运算、增加蝶形处理单元数目和高基数结构[4]。

确定算法中的基数r 时,必须综合考虑算法的处理速度、算法的运算量以及硬件实现算法的资源占用等因素。

基2算法由1个复数乘法和2个复数加法组成,而一个基4算法由3个复数乘法和8个复数加法组成。

虽然基4算法的运算速度是基2算法的2倍,但是基4蝶形硬件实现的资源占用是实现2蝶形的2倍多。

另外,基4算法要求FFT 的处理长度N =4m (m 为自然数),在工程实际中有时不能满足该条件(如N =512)。

综合考虑,该处理器选用基2算法。

1.3 浮点加法器的实现实现基2蝶形运算时,由于并行、流水实现的实数加法多达14个,实现浮点加法的硬件电路复杂,因此,其设计技术直接决定着处理器的性能。

两浮点数[5]相加通过以下步骤来完成:(1)浮点加法的对阶处理;(2)对阶处理后的尾数相加;(3)对相加后的结果进行规格化处理。

FPGA 器件由大量结构规整的slice 组成,每个slice 结构如图2所示,包括两个4输入函数(LUT /RAM16/SRL )、2个进位逻辑(CY )、2个算术逻辑(Arithmetic Logic )、2个数据选择器逻辑(MUXFx )和2-bit 缓冲存储(Register )等资源。

对阶处理是实现浮点加法的最复杂、最关键的步骤。

传统的对阶处理用桶形移位器来实现,该方法占用硬件资源多,功耗大。

本处理中,结合slice 结构特点,采用基于数据选择器的方法实现。

实现对阶处理,就是将指数小的浮点数的尾数向右移I 位(I 为两浮点数的指数差),移出后的高位补上符号位。

对阶处理实现可以由一系列数据选择器(2选1,4选1,8选1,16选1等)组合完成,选择器的输入是二进制补码表示的较小指数的浮点数尾数DA 18~DA 0(DA 18为符号位)和0,选择器26 国防科技大学学报 2004年第6期输出就是对阶处理结果DB 18~DB 0,数据选择器控制码S 5S 4S 3S 2S 1S 0是指数差I 的二进制表示。

为了便于理解,以DB 1的实现为例,当I =0时,DB 1=DA 1;当I =1时,DB 1=DA 2;……;当I =17时,DB 1=DA 18;当I >17时,DB 1=0。

也就是说,DB 1是一个以DA 18~DA 1和0为输入数据,以I 为控制码的19选1的选择器输出。

一个slice 能实现4选1逻辑,两个slice 能实现8选1逻辑,4个slice 能实现16选1逻辑。

对浮点加法的结果进行规格化处理,需要知道前导(0/1)的位数(有效位数前面的符号位数),从而确定规格化时位移的位数。

结合FPGA 结构特点,利用其专门高速进位逻辑通道,实现前导(0/1)的快速判定。

需要规格化数用Sm K m K -1…m 1m 0表示,其中,S 表示符号位,输出前导(0/1)判定结果LZA i (0S i S I ),输出位为1表示对应位为符号位。

LZA 0=m KS (I =0)LZA i =(m K -iS )LZA i -1 (1S i S I {)(6)其中,符号 表示异或逻辑操作, S 表示S 的逻辑非。

采用桶形移位方法实现两个浮点数相加需要663个slices ,采用基于数据选择器的方法实现两个浮点数相加需要277个slices 。

所以,采用基于数据选择器的方法实现加法能有效节约资源、降低功耗。

2 FPGA 实现2.1 处理器总体设计基于FPGA 实现的浮点FFT /IFFT 处理器结构如图1所示。

图1 处理器结构Fig.1 Architecture of processor该处理器有以下特点:(1)处理器内部采用24-bit 自定制浮点格式,能够兼顾处理器的处理性能和资源占用;(2)采用基2蝶形运算单元结构,减少FPGA 资源占用;(3)内置三组数据存储器,保证蝶形运算全速工作,提高处理器处理能力;(4)处理器进行FFT 运算或IFFT 运算以及运算长度N =512或N =1024由外部控制信号决定;(5)自定制浮点格式的旋转因子以只读RAM 的方式存储在FPGA 片上资源Block RAMs 内。