全差分套筒式共源共栅放大器及其共模反馈电路解读

共源共栅放大器的分析

共源共栅放大器的分析1.基本结构和工作原理当输入信号施加在共源共栅放大器的输入端(栅极)时,栅极结电容Cgs会对输入信号起到隔离作用。

通过共源共栅放大器的源极电压调整,可以改变输出电压的增益和相位。

工作原理:当输入信号施加在栅极上时,栅极电阻Rg将输入电流转换为输入电压,并施加到栅极上。

当栅极电压超过阈值电压,漏极电流开始流动。

漏极电流经过源极电阻Rs,形成输出电压。

由于栅极和源极之间存在电容Cgs,所以输出电压的幅频特性非常好,可以达到高频的放大。

2.放大性能分析(1)集大于放大倍数:共源共栅放大器的电压放大倍数由源极电阻Rs决定,与负载电阻RL共同决定。

较小的Rs和RL能够提高放大倍数。

(2) 输入阻抗:共源共栅放大器的输入阻抗由输入电阻Rg和栅极结电容Cgs共同决定。

较大的Rg和较小的Cgs能够提高输入阻抗。

(3)输出阻抗:共源共栅放大器的输出阻抗由源极电阻Rs和漏极电阻Rd共同决定。

较小的Rs和Rd能够提高输出阻抗。

(4)漏极电流偏置:通过控制栅极电压和源极电阻,可以调整共源共栅放大器的偏置电压和偏置电流。

适当选择偏置电流可以减小失调,提高放大器的线性度。

(5) 高频特性:由于栅极和源极之间存在电容Cgs,共源共栅放大器在高频范围有较好的性能,能够实现高频信号的放大。

3.稳定性分析4.应用领域总结:共源共栅放大器是一种常见的放大电路,其工作原理基于MOSFET。

通过调整偏置电流、增加负反馈等手段,可以改善共源共栅放大器的性能。

共源共栅放大器在应用中具有广泛的用途,是电子设备中不可或缺的一部分。

全差分套筒式共源共栅放大器及其共模反馈电路

一毕业设计(论文)进展情况60为什么要使用两级放大器,两级放大器的优点:单级放大器输出对管产生的小信号电流直接流过输出阻抗,因此单级电路增益被抑制在输出对管的跨导与输出阻抗的乘积。

在单级放大器中,增益是与输出摆幅是相矛盾的。

GB GB GB ()()()p p z的相位裕量,所以2.2 10LC因此由补偿电容最小值即可以得到2m112'1g (/)(/)2/12N W L W L K I ==≅ 用负ICMR 公式计算5Dsat V 由式(12)我们可以得到下式15(min)IC SS GS Dsat V V V V =++如果5DS V 的值小于100mv ,可能要求相当大的5(/)W L ,如果5Dsat V 小于0,则ICMR 的设计要求则可能太过苛刻,因此,我们可以减小5I 或者增大5(/)W L 来解决这个问题,我们为了留一定的余度我们(min)IC V 等于-1.1V 为下限值进行计算152511(min)Dsat IC TN SS I V V V V β=---()则可以得到的5Dsat V 进而推出555'2552(/)()Dsat S W L K V ==(I )11/1≅即有58(/)(/)11/1W L W L =≅为了得到60°的相位裕量,6m g 的值近似起码是输入级跨导1m g 的10倍(allen 书p.211例6.2-1),我们设us g g m m 9421016==,为了达到第一级电流镜负载(M3和M4)的正确镜像,要求46SG SG V V =,图中x ,y 点电位相同我们可以得到6644(/)(/)64/1m m gW L W L g ==进而由6662(/)m Pd g K W L I '=我们可以得到直流电流 22m6m667''6666g g 113.72(/)2d d I I A K W L K S μ==== 同样由电流镜原理,我们可以得到7755(/)(/)32/1d d IW L W L I ==3、仿真和测量 (1)DC 分析图2 VOUT 、M5管电流、M7管电流、Vx 与Vy 与输入共模电压变化的关系图4 测量共模输入范围的电路图图5 运放的输入共模电压范围从图中可以得到输入共模范围满足设计指标(-1V~2V)(3)测量输出电压范围在单位增益结构中,传输曲线的线性收到ICMR 限制。

全差分增益提高运算放大器的分析与设计

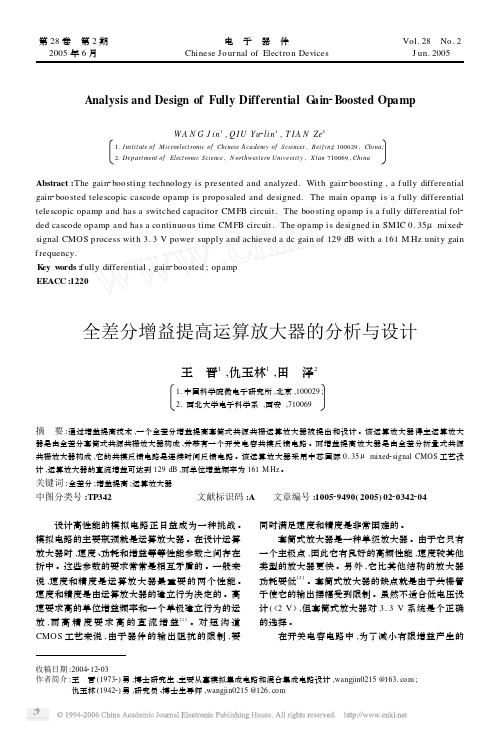

第28卷 第2期2005年6月电 子 器 件Chinese Journal of Elect ron Devices Vol.28 No.2J un.2005Analysis and Design of Fully Differential G ain 2Boosted OpampW A N G J i n 1,Q I U Yu 2li n 1,T I A N Ze21.I nstit ute of Microelect ronic of Chinese A cadem y of S ciences ,Bei j ing 100029,China;2.Depart ment of Elect ronic Science ,N ort hwestern Universit y ,X i ’an 710069,ChinaAbstract :The gain 2boosting technology is presented and analyzed.Wit h gain 2boosting ,a f ully differential gain 2boo sted telescopic cascode opamp is propo saled and designed.The main opamp is a f ully differential telescopic opamp and has a switched capacitor CM FB circuit.The boo sting opamp is a f ully differential fol 2ded cascode opamp and has a co ntinuous time CM FB circuit.The opamp is designed in SM IC 0.35μmixed 2signal CMOS p rocess wit h 3.3V power supply and achieved a dc gain of 129dB wit h a 161M Hz unity gain f requency.K ey w ords :f ully differential ,gain 2boo sted ;opamp EEACC :1220全差分增益提高运算放大器的分析与设计王 晋1,仇玉林1,田 泽21.中国科学院微电子研究所,北京,100029;2.西北大学电子科学系,西安,710069收稿日期:2004212203作者简介:王 晋(19732)男,博士研究生,主要从事模拟集成电路和混合集成电路设计,wangjin0215@ ;仇玉林(19422)男,研究员、博士生导师,wangjin0215@摘 要:通过增益提高技术,一个全差分增益提高套筒式共源共栅运算放大器被提出和设计。

共源共栅放大器的分析

共源共栅放大器的分析本学期学习了《集成电路设计方法》这一门课程,感谢谢老师一直悉心地教导,让我们收获良多。

通过这门课程,我们对集成电路工艺、mos器件有了一点了解,知道怎样使用EDA软件,以及掌握了一些基本的集成电路的分析与设计方法。

其中,共源共栅放大器那一节课令我印象深刻,下面我就以这一小节为例,来谈谈我听课后的感受和收获。

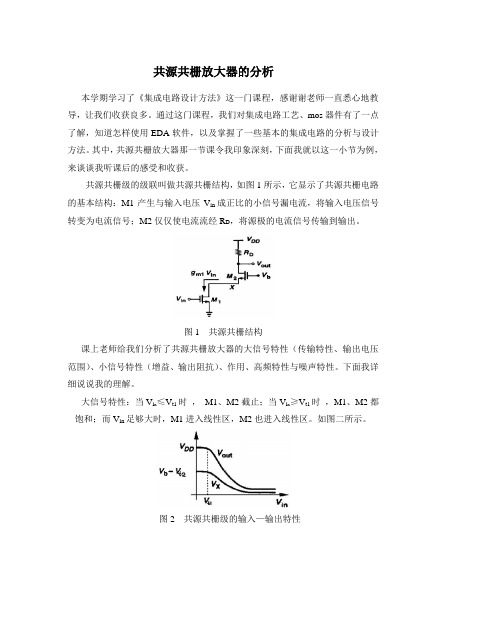

共源共栅级的级联叫做共源共栅结构,如图1所示,它显示了共源共栅电路的基本结构:M1产生与输入电压V in成正比的小信号漏电流,将输入电压信号转变为电流信号;M2仅仅使电流流经R D,将源极的电流信号传输到输出。

图1 共源共栅结构课上老师给我们分析了共源共栅放大器的大信号特性(传输特性、输出电压范围)、小信号特性(增益、输出阻抗)、作用、高频特性与噪声特性。

下面我详细说说我的理解。

大信号特性:当V in≤V t1时,M1、M2截止;当V i n≥V t1时,M1、M2都饱和;而V in足够大时,M1进入线性区,M2也进入线性区。

如图二所示。

图2 共源共栅级的输入—输出特性分析偏置条件:为了保证M1工作于饱和区,必须满足Vx ≥Vin-Vt1.假如M1和M2都处于饱和区,则VX 主要由Vb决定:V x=V b-V GS2。

因此V b≥V in+V GS2-V t1 ,如图3所示。

为了保证M2饱和,必须满足Vout ≥Vb-VT2,如果Vb的取值是M1处于饱和区边缘,则Vout ≥Vin-Vt1+VGS2-Vt2。

从而保证M1和M2工作在饱和区的最小输出电平等于M1和M2的过驱动电压之和。

图3 共源共栅电路的偏置电压。

共源共栅差分放大电路

共源共栅差分放大电路

共源共栅差分放大电路是一种常用的差分放大电路结构。

它由两个MOSFET (MOS场效应晶体管)组成,一个作为共源放大器,另一个作为共栅放大器,通过它们的互补工作,使得差分输入信号能够被放大并传输。

在共源共栅差分放大电路中,差分输入信号被分别输入到两个MOSFET的源极,而栅极则分别连接到共源放大器和共栅放大器的输出信号。

通过这种方式,当输入差分信号变动时,共源放大器和共栅放大器的工作状态会相应调整,使得差分信号被放大,而共模信号(即两个输入信号的平均值)则不会被放大。

共源共栅差分放大电路具有以下特点:

1.具有高增益和高输入阻抗,能够放大微弱的差分信号。

2.具有良好的共模抑制比,能够抑制共模信号的放大,减小对差分信号的干扰。

3.输出信号的相位与输入信号相反,可以实现相位反转的功能。

这种差分放大器常用于模拟电路中,如操作放大器、振荡器、滤波器等电路中。

它在信号处理和通信系统中起着重要的作用。

全差分运算放大器结构框图解析 常见的全差分运算放大器电路分析

全差分运算放大器结构框图解析常见的全差分运算放大器电路分析全差分(运算放大器)就是一种具有差分输入,差分输出结构的运算(放大器)。

(差分放大器)相对于单端输出的放大器具有如下一些优势。

首先,由于随着CMOS 工艺尺寸不断缩小,从0.5μm 减小至0.35μm,0.18μm,90nm,(芯片)的(供电)电压也不断减小从5V降到3.5V,1.8V,1.2V甚至更低。

在如此低的供电电压的情况下,单端输出的运算放大器很难能理想地工作,为了保证电路能够得到足够大的(信号)摆幅,我们需要采用全差分的运算放大器结构。

其次,全差分运算放大器能够有效抑制电路的共模信号,并且能够减小电路的偶次谐波失真。

但是为了得到这些性能,全差分运算放大器需要一个共模反馈环路来控制输出的共模电平。

理想情况下,这个共模反馈控制环路会使得输出的共模电平稳定在VDD/2。

所以,一个全差分放大器通常由主放大器和共模反馈环路两部分组成,它在现代的(电路设计)中应用非常广泛。

1.全差分运算放大器结构框图共模反馈的基本思想就是由一个共模采样电路取得电路的输出共模信号,然后把共模信号与一个参考信号相比较,将比较后的误差信号放大后再输入主放大器以调节输出共模电压。

对于输入的差分信号来说,共模反馈环路不会对交流信号产生影响,相当于说共模环路对于交流是开路的。

所以,电路的差分增益和相位就由主放大器决定。

但是,对于输入的共模信号,共模反馈环路决定了输出的共模电平,这时,共模环路的增益和相位就会对电路的输出共模电平的精度和稳定性产生影响。

全差分放大器在应用中的一种电路形式,差分输出的信号摆幅vO1-vO2 为单端信号vO1(vO2)摆幅的两倍,所以在输出端可以有较大的输出动态范围,相对于单端输出提高了处理信号的幅度能力。

2. 常见的全差分运算放大器电路(a)是普通的全差分放大器电路,通常作为一个放大器的输入级部分。

图7-3(b)是折叠式全差分运算放大器电路,它的增益会比较大,可以达到60~70dB,但同时会消耗比较大的功耗,因为它有四条支路需要(电流)。

一种具有高增益和超带宽的全差分跨导运算放大器

0中国集成电路设计♦China lntegrated Circult一种具有高增益和超带宽的全差分跨导运算放大器罗杨贵1,曾以成1,邓欢2,唐金波21.湘潭大学物理与光电工程学院;2.湖南毂梁微电子有限公司摘要:基于GSMC0.18um CM OS工艺,设计了一种应用于12位ADC的全差分运算放大器。

为了提高增益,在套筒式共源共栅结构上运用了增益提高技术。

为了提高输入跨导,采用隔离效果更好的深N阱CMOS作为输入端,从而提升增益带宽。

为了降低功耗,利用单端放大器作为辅助运放。

整体电路结构简单优化。

仿真结果表明,运算放大器直流开环增益大于100dB,单位增益带宽大于800M H z,相位裕度大于70毅,完全满足目标ADC的性能要求,是一种新型且质量较高的运放,也可应用于其它场合。

关键词:增益提高;套筒式共源共栅;高增益带宽;深N阱中图分类号:TN432文献标识码:AA Fully Differential Transconductance Operational Amplifierwith high Gain and ultra GBWLUO Yang-gui,ZENG YirCheng1,DENG Huan2,TANG Jn-bo21.SchoolofPhysicsand Opibe]ectronics,X iangtan University;2.H unan Greai-Leo M icroe]ectronicsCO.LTDAbstract:Based on theGM SC0.18um CM OS process,a fuUy differentialoperationalam plifierlbr12-bitADC is designed.In orderto increase the gain,a gain-enhancing technique is used on the te]escopic cascode structure.In order to increase input transconductance,the deep N-W elltansistorwith better isolation function was used as the input,thereby to enhance the gain bandwidth.In order to reduce power consumption,a single-ended amplifier is used as an auxiliary operational amplifier.The overall circuit structure is simple and optimized.The simulation results show that the operational amplifier DC open-loop gain is greater than100dB,the unity gain bandwidth is greater than800MHz, and the phase margin is greater than70毅,which fully meets the performance requirements of ADC.It is a new and high-quality operational amplifier that can also be applied to other applications.Keywords:Gain enhancement;Telescopic cascode;High gain bandwidth;Deep N_well0引言模数转换器作为连接模拟信号与数字信号的桥梁,越来越显示出其重要性。

全差分套筒式共源共栅放大器及其共模反馈电路

In general speaking, only the level of operational amplifiers, such as sleeve operational amplifiers, frequency response is fast, low gain;Two stage operational amplifier gain high, unit gain bandwidth.After considering the above factors, to design a fully-differential sharing sleeve source gate amplifier and the structure of common mode feedback circuit.In guarantee gain excellent cases, the frequency response of the op-amp single pole characteristics in order to optimize unit gain bandwidth.

套筒共源共栅运算放大器的mos管参数计算

套筒共源共栅运算放大器的mos管参数计算套筒共源共栅运算放大器是一种常用的MOS管参数计算方法。

它通过调整栅极电压和源极电压来改变MOS管的工作状态,从而实现放大器的放大功能。

在本文中,将介绍套筒共源共栅运算放大器的原理和参数计算方法,并分析其在电路设计中的应用。

我们来了解一下套筒共源共栅运算放大器的原理。

套筒共源共栅运算放大器由一个N沟道MOS管和一个P沟道MOS管组成。

N沟道MOS管的栅极和源极相连,P沟道MOS管的栅极和源极也相连,两个管子的漏极相连,形成一个共源共栅的结构。

在工作时,通过调整栅极电压和源极电压,可以使MOS管处于不同的工作状态,从而实现放大器的功能。

接下来,我们将介绍如何计算套筒共源共栅运算放大器的MOS管参数。

首先,需要确定放大器的工作状态。

常用的工作状态有三种:截止区、线性区和饱和区。

在截止区,MOS管的栅极电压低于阈值电压,导通电流接近于零;在线性区,MOS管的栅极电压高于阈值电压,导通电流与栅极电压成线性关系;在饱和区,MOS管的栅极电压高于阈值电压,导通电流接近饱和值。

根据放大器的需求,选择合适的工作状态。

确定工作状态后,需要计算MOS管的参数。

其中,重要的参数有:跨导、输出电阻和增益。

跨导是指输入电压变化与输出电流变化的比值,反映了放大器对输入信号的放大能力;输出电阻是指输出电压变化与输出电流变化的比值,反映了放大器对负载的驱动能力;增益是指输出信号幅度与输入信号幅度的比值,反映了放大器的放大倍数。

为了计算这些参数,需要使用MOS管的模型和相关的公式。

常用的MOS管模型有:简单MOS模型、小信号MOS模型和大信号MOS 模型。

根据实际情况选择合适的模型,并根据公式计算参数。

我们来分析一下套筒共源共栅运算放大器在电路设计中的应用。

套筒共源共栅运算放大器具有输入阻抗高、输出阻抗低、增益稳定等优点,适用于电压放大、电流放大、功率放大等场合。

在实际应用中,可以根据需要调整栅极电压和源极电压,以达到最佳的放大效果。

全差分套筒式共源共栅放大器及其共模反馈电路的研究

全差分套筒式共源共栅放大器及其共模反馈电路的研究全差分套筒式共源共栅放大器是一种常用的放大器电路,可以用于增强信号的幅度和增加输出功率。

它具有高增益、低噪声和较大的输出功率等优点,被广泛应用于通信器材、音频放大器和高速数据传输等领域。

本文将详细介绍全差分套筒式共源共栅放大器的原理、特点以及常见的共模反馈电路。

全差分套筒式共源共栅放大器的原理是在输入端同时接入两个信号,一个信号经过源极耦合电容输入到栅极,另一个信号则经过栅极调制放大输出。

这种设计使得差模信号增益大,共模信号增益小,从而提高了放大器的性能。

同时,采用套筒式结构可以提供较大的输出功率,使得放大器在输出端有更大的动态范围。

全差分套筒式共源共栅放大器的特点有以下几个方面。

首先,由于共源共栅结构的存在,放大器具有较高的输入阻抗和输出阻抗,可以有效地减少信号传输的损耗。

其次,通过差模信号和共模信号的分离处理,放大器具有较低的噪声和失真。

此外,套筒式结构能够提供较大的输出功率,适合于高功率放大应用。

为了进一步提高放大器的性能,常常采用共模反馈电路。

共模反馈电路可以抑制共模干扰,提高放大器的共模抑制比,减少信号传输中的干扰和噪声。

一种常见的共模反馈电路是通过电阻和电容网络将共模信号的反馈接入到放大器的源极,通过控制源极电流的差异,来实现共模信号的抑制。

这种反馈电路能够有效地提高放大器的共模抑制比,提供更清晰的信号输出。

总之,全差分套筒式共源共栅放大器是一种具有高增益、低噪声和较大输出功率的放大器电路。

通过合理设计和优化,可以实现更好的性能和应用效果。

而共模反馈电路则进一步提高了放大器的性能,减少了信号传输中的干扰和噪声。

通过研究全差分套筒式共源共栅放大器及其共模反馈电路,可以更好地应用于实际的工程设计和应用中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一 毕业设计(论文)进展情况运算放大器是许多模拟系统和混合数字信号系统中的一个完整部分,也是构成这些系统的基本单元. 因而设计高性能的运算放大器可以使系统的总体性能得到提高。

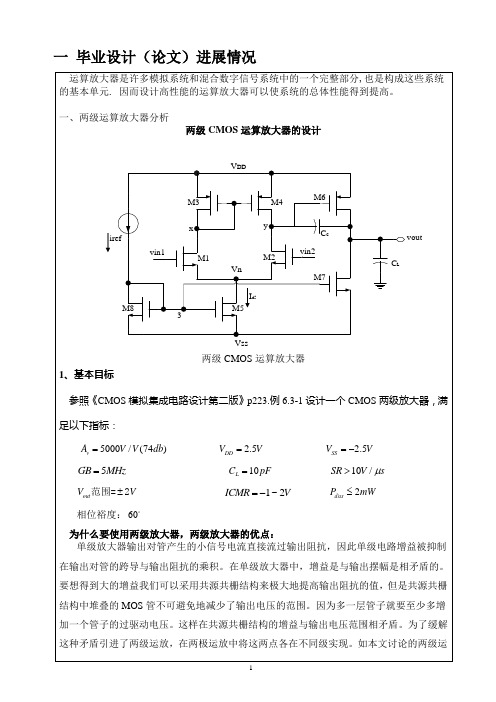

一、两级运算放大器分析两级CMOS 运算放大器的设计V DDV SSM1M2M3M4M5M6M7M8VnC LC cvoutvin1vin2irefxy3I d5两级CMOS 运算放大器1、基本目标参照《CMOS 模拟集成电路设计第二版》p223.例6.3-1设计一个CMOS 两级放大器,满足以下指标:5000/(74)v A V V db = 2.5DD V V = 2.5SS V V =-5GB MHz = 10L C pF = 10/SR V s μ>out V V ±范围=2 1~2ICMR V =- 2diss P mW ≤ 相位裕度:60为什么要使用两级放大器,两级放大器的优点:单级放大器输出对管产生的小信号电流直接流过输出阻抗,因此单级电路增益被抑制在输出对管的跨导与输出阻抗的乘积。

在单级放大器中,增益是与输出摆幅是相矛盾的。

要想得到大的增益我们可以采用共源共栅结构来极大地提高输出阻抗的值,但是共源共栅结构中堆叠的MOS 管不可避免地减少了输出电压的范围。

因为多一层管子就要至少多增加一个管子的过驱动电压。

这样在共源共栅结构的增益与输出电压范围相矛盾。

为了缓解这种矛盾引进了两级运放,在两极运放中将这两点各在不同级实现。

如本文讨论的两级运放,大的增益靠第一级与第二级相级联而组成,而大的输出电压范围靠第二级这个共源放大器来获得。

典型的无缓冲CMOS 运算放大器特性 边界条件要求工艺规范 见表2、3电源电压 %105.2±±V电源电流 100Μa 工作温度范围0~70°特性要求增益 dB 70≥增益带宽 ≥5MHz建立时间 s μ1≤ 摆率 s /5μV ≥ICMR ≥V 5.1± CMRR ≥60dB PSRR ≥60dB 输出摆幅 ≥V 5.1±输出电阻 无,仅用于容性负载失调 mV 10±≤噪声 ≤100Hz nV (1kHz 时) 版图面积≤50002)(最小沟道长度⨯ 表1 典型的无缓冲CMOS 运算放大器特性2、两级放大电路的电路分析图1中有多个电流镜结构,M5,M8组成电流镜,流过M1的电流与流过M2电流1,23,45/2d d d I I I ==,同时M3,M4组成电流镜结构,如果M3和M4管对称,那么相同的结构使得在x ,y 两点的电压在Vin 的共模输入范围内不随着Vin 的变化而变化,为第二极放大器提供了恒定的电压和电流。

图1所示,Cc 为引入的米勒补偿电容。

表2 0.5m μ工艺库提供的模型参数CSMC 0.5um Double Poly Mix CMOS process model 工艺参数 0th V ox t 0μ NMOS 0.7016 1.28E-8 404.257 PMOS -0.9508 1.24E-8 219.5单位Vm2cmV S⋅表3 一些常用的物理常数常数符号常数描述 值单位KT室温下 214.14410-⨯ J0ε自由空间介电常数 148.85410-⨯ F cm ox ε二氧化硅的介电常数-133.510⨯F cm利用表2、表3中的参数/OX ox ox C t ε= 0ox K C μ'=计算得到2110/NK A V μ'≅ 262/PK A V μ'≅ 第一级差分放大器的电压增益为:1124m v ds ds g A g g -=+ (1)第二极共源放大器的电压增益为6267m v ds ds g A g g -=+ (2)所以二级放大器的总的电压增益为16261224675246672()()m m m m v v v ds ds ds ds g g g g A A A g g g g I I λλλλ===++++ (3)相位裕量有111121180tan ()tan ()tan ()60M GB GB GBp p z ---Φ=±---=要求60°的相位裕量,假设RHP 零点高于10GB 以上11102tan ()tan ()tan (0.1)120v GBA p ---++=102tan ()24.3GBp -= 所以2 2.2p GB ≥ 即622.2()m m L cg gC C > 由于要求60 的相位裕量,所以626210()10m m m m c cg gg g C C >⇒>可得到 2.20.2210Lc L C C C >==2.2pF 因此由补偿电容最小值2.2pF ,为了获得足够的相位裕量我们可以选定Cc=3pF 考虑共模输入范围:在最大输入情况下,考虑M1处在饱和区,有3131(max)(max)DD SG n IC n TN IC DD SG TN V V V V V V V V V V --≥--⇒≤-+ (4)在最小输入情况下,考虑M5处在饱和区,有1515(min)(min)IC SS GS Dsat IC SS GS Dsat V V V V V V V V --≥⇒≤++ (5)而电路的一些基本指标有11m v C gp A C =- (6)62m L gp C =- (7)61m C g z C = (8) 1m C gGB C = (9)CMR:正的CMR 5in313()()DD T T I V V V β--+(最大)=V 最大最小 (10)负的CMR 5in151()()SS T DS I V V V β+++(最小)=V 最大饱和 (12)由电路的压摆率5d CI SR C =得到 5d I =(3*10-12)()10*106)=30μA(为了一定的裕度,我们取40iref A μ=。

)则可以得到,1,23,45/220d d d I I I A μ===下面用ICMR 的要求计算(W/L)353'2331()()[]DD SG TN I WL K V V V =-+≅11/1 所以有3()W L =4()WL =11/1由1m CgGB C =,GB=5MHz ,我们可以得到6121510231094.2m g s πμ-=⨯⨯⨯⨯=GB 是单位增益带宽P1是3DB 带宽 GB=1p A v ⋅即可以得到2m112'1g (/)(/)2/12N W L W L K I ==≅ 用负ICMR 公式计算5Dsat V 由式(12)我们可以得到下式15(min)IC SS GS Dsat V V V V =++如果5DS V 的值小于100mv ,可能要求相当大的5(/)W L ,如果5Dsat V 小于0,则ICMR 的设计要求则可能太过苛刻,因此,我们可以减小5I 或者增大5(/)W L 来解决这个问题,我们为了留一定的余度我们(min)IC V 等于-1.1V 为下限值进行计算152511(min)Dsat IC TN SS I V V V V β=---()则可以得到的5Dsat V 进而推出555'2552(/)()Dsat S W L K V ==(I )11/1≅即有58(/)(/)11/1W L W L =≅为了得到60°的相位裕量,6m g 的值近似起码是输入级跨导1m g 的10倍(allen 书p.211例6.2-1),我们设us g g m m 9421016==,为了达到第一级电流镜负载(M3和M4)的正确镜像,要求46SG SG V V =,图中x ,y 点电位相同我们可以得到6644(/)(/)64/1m m gW L W L g ==进而由6662(/)m Pd g K W L I '=我们可以得到直流电流 22m6m667''6666g g 113.72(/)2d d I I A K W L K S μ==== 同样由电流镜原理,我们可以得到7755(/)(/)32/1d d IW L W L I ==3、仿真和测量 (1)DC 分析图2 VOUT 、M5管电流、M7管电流、Vx 与Vy 与输入共模电压变化的关系1.1 Vss<vin<Vth+VssM1,M2,M3,M4工作在截止区。

由于管子宽长比的设定而使得M1,M2,M3,M4都工作截止区时V (x ),V (y )点的的电压大约在1.95v 左右,因此M6的V sg 小于其阈值电压,M6处于截止状态。

此时M5,M7的Vgs 相等为定值,即为M8与电流源内阻的分压,且大于其阈值电压,故M5,M6管子应当处于饱和或者线性区,而此时Vss 的电流接近40u ,即接近Iref ,所以M5,M7管子电流接近0,因此我们可以得到M5,M7管都处于线性区。

1.2 Vin> Vth+VssM3,M4工作在饱和区。

而由于此时电流不是很大,导致SG 3,4V 不是很大,这样导致Vx 的电压还是比较高,所以M1,M2工作在饱和区。

M5由于这个时候的电流不很大,仍然工作在线性区。

即这时M1,M2,M3,M4都工作在饱和区,M5工作在线性区. M6会随着Vx 电压的下降而导通。

而刚开始导通时,Vout 的比较小(这是由于M7管此时仍然处于线性区,DS7V 较小),SD6V 比较大而使得M6管工作在饱和区。

随着Vin 的进一步的增大,M5的电流增大,M5的漏极电压也随着增大,最后一直到M1,M2,M3,M4,M5都工作在了饱和区。

而此时Vy 的电压变得恒定了。

(2)测量输入共模范围运算放大器常采用如图3所示的单位增益结构来仿真运放的输入共模电压范围,即把运放的输出端和反相输入端相连,同相输入端加直流扫描电压,从负电源扫描到正电源。

得到的仿真结果如图3所示(利用MOS 管的GD 极性相反来判断放大器的同相端与反相端)V INV DDV SSI DDI SSC LV OUT图3 测量共模输入范围的原理图图4 测量共模输入范围的电路图图5 运放的输入共模电压范围从图中可以得到输入共模范围满足设计指标(-1V~2V)(3)测量输出电压范围在单位增益结构中,传输曲线的线性收到ICMR 限制。

若采用高增益结构,传输曲线的线性部分与放大器输出电压摆幅一致,图6为反相增益为10的结构,通过R L 的电流会对输出电压摆幅产生很大的影响,要注意对其的选取,这里我们选取R L =50K Ω,R=60K Ω.图8为输出电压范围V INV DDV SSC LV OUT 10RRRL图6 测量输出电压范围的原理图图7 测量输出电压范围的电路图图8 输出电压的范围可以看出输出电压摆率大概在-2V~2V之间,基本满足要求(4)测量增益与相位裕度相位裕度是电路设计中的一个非常重要的指标,用于衡量负反馈系统的稳定性,并能用来预测闭环系统阶跃响应的过冲,定义为:运放增益的相位在增益交点频率时(增益幅值等1的频率点为增益交点),与-180°相位的差值。