Altium Designer Summer 09 AD9 PCB LAYOUT布线设计规则说明

AltiumDesignerSummer09使用教程讲解

操作教程

把Altium Designer Summer 09转化成中文

刚装好的DXP是英文的,我们需要把它转化成中 文

1.选择DXP选项卡中的Preferences选项

在DXP System-General中选择Use Localzed resources

点击Place按钮可以放置元 件

安装元件库

点击元件库,在这里可以安装一些常用的元件库或 封装库,安装Library\Pcb\Dual-In-Line Package.PcbLib

查找元件

如果在常用元件库中找不到想要元件,可以点击查找按钮, 然后在文本框中输入元件名字,范围选择路径中的库,路 径选择你的安装目录,如下图。

其它很有用的按钮还有地、电源、放置元件、放 置端口、忽略检查等等,鼠标悬停在上面可以得 到按钮的信息

所有悬空的引脚最好接上”忽略ERC检查“标志

编译原理图文件

编译一个原理图文件就是 在设计文档中检查原理图 和电气规则错误

点击项目管理-Compile Document(编译文档) 可以进行编译

如果系统找到了这个 封装,会在下面的预 览中见到它

把单片机设置为DIP40,把MAX118设置 为DIP-28/D38.7

修改封装

复位电路

复位电路就用我们之 前画的按键复位电路

找到开关SW-PB和相 应的电容电阻添加

晶振部分

晶振部分由一个无源 晶振和两个电容组成

选中晶振(XTAL), 摆放好电容和地,把 两端连到单片机的18、 19号口上

放置单片机

查找并放置AT89C55WD(或P89C54X2BN)和 MAX118EPI。

修改封装

PCB设计教程Altium_Designer_Summer_09

2009-11-1 20:32

图6-2新建电路原理图

添加电路原理图到工程当中

如果添加到工程中的电路原理图以空文档的形式被打开,可以通过在工程文件名上点击右键并且在工程面板中选择Add Existing to Project 选项,选择空文档并点击 Open。更简单的方法是,还可以在Projects面板中简单地用鼠标拖拽拉空白文档到工程文档列表中的面板中。该电路原理图在Source Documents工程目录下,并且 已经连接到该工程。

画电路原理图

接下来可以开始画电路原理图。本章将使用如图6-3所示的电路图为例进行讲解。这个电路是由两个2N3904三极管组成的非稳态多谐振荡器。

图6-3 非稳态多谐振荡器

加载元件和库

Altium Designer为了管理数量巨大的电路标识,电路原理图编辑器提供了强大的库搜索功能。虽然元件都在默认的安装库中,但是还是很有必要知道如何通过从库中 去搜索元件。按照下面的步骤来加载和添加图6-3电路所需的库。 首先我们来查找型号为2N3904的三极管。 1.点击Libraries标签显示Library面板,如图6-4。 2.在Library面板中点击Search in按钮,或者通过选择Tools>>Find Component,来打开Libraries Search对话框,如图6-5所示。 3.对于这个例子必须确定在Options设置中,Search in 设置为Components。对于库搜索存在不同的情况,使用不同的选项。 4.必须确保Scope设置为Libraries on Path 并且Path包含了正确的连接到库的路径。如果在安装软件的时候使用了默认的路径,路径将会是Library。可以通过点击文 件浏览按钮来改变库文件夹的路径。对于这个例子还需得确保Include Subdirectories复选项框已经勾选。 5.为了搜索所有3904的所有索引,在库搜索对话框的搜索栏输入*3904*。使用*标记来代替不同的生厂商所使 用的不同前缀和后缀。 6.点击Search 按钮开始搜索。搜索启动后,搜索结果将在库面板中显示。

Altium Designer Summer 09使用教程

把DXP转化成中文

重新启动DXP,就变成中文版的了

创建一个新项目

在文件-创建菜单中选择项目-PCB项目

再在同样的地方选择创建新原理图文件,我们就 可以开始编辑原理图了 下图展示了当几个文件和编辑器同时打开并且窗 口进行平铺时的界面。

开始一个原理图设计

在你开始绘制电路图之前首先要做的是设置正确的文档选 项。完成以下步骤: 从菜单选择设计-文档选项,文档选项对话框打开。在此 我们需要修改的是将图纸大小设置为标准A4格式。

按Shift+F查找相似对象 在提示框内Comment 项选择Same后再单击 “应确定会出提示框, 在Hide项单击取消打“√”,原理 图界面就同步显示参数。 单击右上角“×”关闭提 示框,修改成功。

添加PCB文件

在开始PCB设计之前, 需要把PCB文件添加 到项目中来。 点击Project面板,在 已有的项目上点击右 键,就可以追加新文 件或者已有文件到项 目中来了

编辑原理图元件库

许多时候,在现有的库中找不到我们所需要的元 件,这时候,就需要自己新建一个元件 点击文件-创建-库-原理图库

放置单片机

查找并放置AT89C55WD(或P89C54X2BN)和 MAX118EPI。

修改封装

有的时候,选用的元件封装并不是我们想要的, 这时候,可以双击元件修改元件属性 看到元件属性对话框的右下角,查看是否有类型 为Footprint的项,如果有,则编辑,否则追加一 项。

模数转换器部分

在Miscellaneous Connectors.IntLib(常 用连接器件中找到 MHDR1X2(2口连接 器)作为信号的输入 部分 将数据线连入总线 将A0、A1、A2和单片 机的P2.0、 P2.1、 P2.2相连作为选通地 址

Altium Designer Summer 09使用教程资料

模数转换器部分

? 把WR连到单片机的 WR,CS连到P2.7, RD连到单片机的 RD, INT连到 INT0 (P3.2 ), 右图中是利用网络标 签来完成这种连接的

? 别忘了电源部分,将 芯片的电源和地连上机的 电源和地都接上

? 将单片机的引脚写上 相应的网络标签

? 将每个引脚对应的总线引脚标出(D0-D7)

模数转换器部分

? 在Miscellaneous Connectors.IntLib (常 用连接器件中找到 MHDR1X2 (2口连接 器)作为信号的输入 部分

? 将数据线连入总线 ? 将A0、A1、A2和单片

机的P2.0、 P2.1、 P2.2相连作为选通地 址

把DXP转化成中文

? 重新启动DXP,就变成中文版的了

创建一个新项目

? 在文件-创建菜单中选择项目 -PCB项目

? 再在同样的地方选择创建新原理图文件,我们就 可以开始编辑原理图了

? 下图展示了当几个文件和编辑器同时打开并且窗 口进行平铺时的界面。

开始一个原理图设计

? 在你开始绘制电路图之前首先要做的是设置正确的文档选 项。完成以下步骤:

复位-更新变化表

更新变化

? 点击“使变化生效”按钮,可以看到“检查”一 栏都打上了勾

更新变化

? 这时点击“执行变化”按钮,可以看到“完成” 一栏都打上了勾,这时候,标识符已经自动添加 完毕

编译原理图文件

? 仔细检查原理图文件, 如果无误的话就可以 编译了,如果编译信 息里面没有 Error(错 误),那么原理图就 画好了

添加电源线约束

? 右键点击Routing/Width,新建规则并命名。 ? 选择网络,选取对象+5V ? 将Minimum、Preferred 和 Maximum宽度栏改为25mil

Altium Designer Summer 09使用教程资料[文字可编辑]

![Altium Designer Summer 09使用教程资料[文字可编辑]](https://img.taocdn.com/s3/m/7c8cabd7ad02de80d5d84048.png)

? 放置元件之后,双击元件会出现元件属性对话框,如下图。 ? 我们一般需要注意的是写标识符,选择是否镜像,输入元件参数和选

择PCB封装

11

放置导线

? 按空格键可以旋转元件 ? 放置元件之后,接下来就是把它们

连接起来。 ? 注意右上的工具条(如右中图),

第一个按钮是放置导线,点击它, 光标将变为十字形状。 ? 将光标放在R1的上端。当你放对位 置时,一个红色的连接标记(大的 星形标记)会出现在光标处。这表 示光标在元件的一个电气连接点上。 ? 左击固定第一个导线点。移动光标 你会看见一根导线从光标处延伸到 固定点。 ? 将光标移到R1的右边C3的左端, 左击在该点固定导线。在第一个和 第二个固定点之间的导线就放好了。

Altium Designer Summer 09

操作教程

1

把Altium Designer Summer 09 转化成中文 ? 刚装好的DXP是英文的,我们需要把它转化成中

文 ? 1.选择DXP选项卡中的 Preferences 选项

2

? 在DXP System-General中选择Use Localzed resources

28

复位-更新变化表

18

修改封装

? 在库名中选中 DualIn-Line Package.PcbLib (请 先安装此库),在名 称中输入 DIP-40

? 如果系统找到了这个 封装,会在下面的预 览中见到它

? 把单片机设置为 DIP40,把MAX118 设置 为DIP-28/D38.7

19

修改封装

20

复位电路

? 复位电路就用我们之 前画的按键复位电路

? 把EA接高电平 ? 最后,把所有不用的

Altium_Designer_Summer_09批量修改元件参数

总结归纳的一些修改技巧,分享如何在Altium Designer 中运用查找编辑集体整批修改功能Altium Designer 提供了非常强大搜索修改功能,有List 和Inspector 等对话框,可以在原理图或PCB 文件中对器件进行集体修改。

在原理图文件中,左键选中器件,右键点击,在拖出的菜单里左键选中Find Similar Objects, 则出现选中界面,在这个界面里,所有的选项都可以设置为约束条件来进行查找,比如,在Description行,在ANY 栏里点一下,在Any 旁的箭头的选项中选为SAME,点击OK,就可以找出所有同一个描述的器件;Current Footprint 行箭头的选项中选为SAME,点击OK 这样就可以找出所有同一个封装的器件;Part Comment 行箭头的选项中选为SAME,点击OK 这样就可以找出所有同一个注释的器件,等等,如此设置可以进行各种各样的搜索。

点击OK 以后,就会跳出搜索结果界面。

如下图所示,如图所示,这是以Part Comment 为条件找到的三个符合条件对象,这时,如果我想一起修改着三个器件的属性,比如说封装,只要将DIP14 改为SOP14,然后在Inspector 界面其他地方左键点击,则修改就有效了。

如果要一个个修改的话,可以左键点击View\Workspace Panel\SCH\List,则进入列表界面,如下图所示,在列表界面里就可以一个个对所选的器件进行修改。

在PCB 文件中,左键选中器件,右键点击,在拖出的菜单里左键选中Find Similar Objects,则出现选中界面,在这个界面里,所有的选项都可以设置为约束条件来进行查找,比如,在CurrentFootprint 行,在Any 栏里点一下,在Any 旁的箭头的选项中选为SAME,点击OK,就可以找出所有同一个封装的器件;Part Comment 行在Any 栏里点一下,在Any 旁的箭头的选项中选为SAME,点击OK 这样就可以找出所有同一个注释的器件,等等,如此设置可以进行各种各样的搜索。

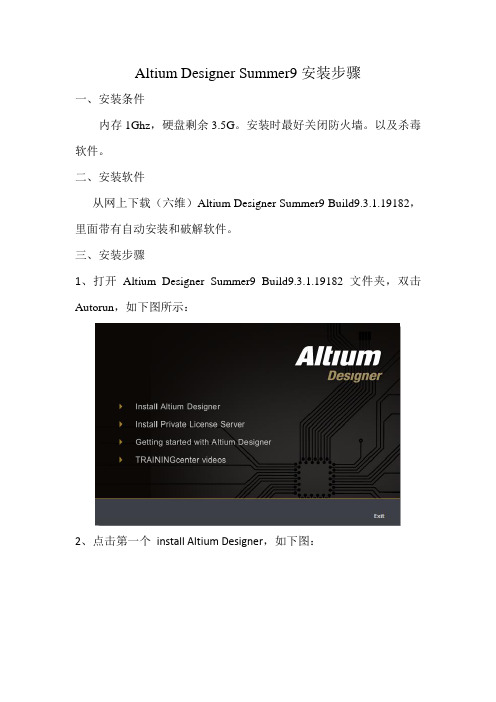

Altium Designer Summer9安装步骤

Altium Designer Summer9安装步骤一、安装条件内存1Ghz,硬盘剩余3.5G。

安装时最好关闭防火墙。

以及杀毒软件。

二、安装软件从网上下载(六维)Altium Designer Summer9 Build9.3.1.19182,里面带有自动安装和破解软件。

三、安装步骤1、打开Altium Designer Summer9 Build9.3.1.19182文件夹,双击Autorun,如下图所示:2、点击第一个install Altium Designer,如下图:点击next,选择I accept the license agreement,点击Next,点击Next,如果安装在C盘,直接点击Next即可,如果安装在D盘,点击Browse,如下,将C改成D即可,点击ok,Next,如下,点击Next,如下,点击Next,等待完成,安装完成四、破解步骤1、打开Altium Designer Summer9 Build9.3.1.19182文件夹中的AD9-Crack文件夹,运行AD9KeyGen,如下图,2、点击“打开模板”,加载ad9.ini(在AD9-Crack文件夹中),如想修改注册名,只需修改:TransactorName=horosehorose用你自己的名字替换,其它参数在单机版的情况下无需修改3、点击“生成协议”,保存生成的alf文件到你的安装目录下,如下,在这里保存名字为abc.alf.如下,点击保存,如下,4、运行AD9-Crack文件夹中的ads09crack,对安装目录下的dxp.exe文件补丁,注意运行破解时软件没有运行点击Patch,如下点击Y,在安装目录下找到dxp.exe,如下点击打开,如下点击Exit 退出。

5、启动DXP,运行菜单DXP->My Account,如下,点击Add Standalone License file,在安装目录下选择.alf文件,如下打开即可,破解成功。

altiumdesignersummer09出现的问题解决方案【最新精选】

altium designer Summer09出现的问题解决方案在编译原理图时,引脚和连线旁边出现很多红线,提示error:signal with no driver。

原理图没有加入到Project里。

第一次导入没问题,但是改了个元件的封装,在更新一下(Design—Update SCH),点击导入时出现Unkown Pin。

解决方案一:把第一张PCB删掉,新建一个PCB再倒入。

解决方案二:把改过的元件在PCB中删除,再倒入。

以上问题本应该是没问题的,但是可能是我们使用的盗版软件的原因。

用altium designer画完图编译后,出现几百警告,几乎的所有的都是Off grid pin画的图在项目中去编译,独立的不能编译,如果文件不在项目中的话,就会出现你说的不在网络的提示。

你的元件没有在原理图上真正形成电气上的连接。

你的元件库没有被软件别。

没有你建一个项目文件,把你的原理图放在里去做编译,这样就不会出错了。

是因为你原理图中的元件引脚尺寸和你设置的栅格尺寸不对应,导致系统无法识别而报错,引脚长度尺寸必需设置成栅格尺寸的整数倍!!!你把你做的原理图元件重新再画一遍,再编译,问题解决双面板应该都有哪些Layer?Top Layer 顶层铜皮,双面板必须要Bottom Layer 底层铜皮,双面板必须要Top OverLayer 顶层丝印,一般需要,也有节约成本不做的。

Bottom OverLayer 底层丝印,一般不需要,底层放原件的话,也可以加。

Top/Bottom Soldermask 顶层底层阻焊层,就是“绿油”,一般需要,也有节约成本不做的。

Mechinical 1/4 机械层1/4,板边以及板内开槽,1无金属化,4有金属化。

Keepout 禁止布线区域,不自动布线的话可以不要。

然而中国的现实是用Keepout做板框成了行规,你要正规地给他们机械层往往还不会做了。

Top/Bottom Pastemask 顶层底层钢板层,如果要批量焊接SMD器件的板子,需要定做钢板,这两层不在PCB上,是生产需要的工装.Multilayer 多层,在所有层上都存在的东西,比如直插器件的焊盘,这层一般是必须的,不要试图关闭它。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一. 网络类(Net Classes)的组建:

方法一:原理图中执行Place——Directives——Net Class

按Tab键,设置好相关名称属性回车,每个归属此类网络均要放置。

方法二:PCB中执行Design——Classes…命令,按下图右键执行Net Classes——Add Class命令会生产New Class,右键更名成所需要的网络类名称,单击添加归属于此网络类的网络成

员。

二. 差分网络类(Differential Pair Classes)的组建:

方法一:原理图中执行Place——Directives——Differential Pair

按Tab键,设置好相关名称属性回车,每个归属此类网络均要放置。

方法二:

步骤1:PCB中执行Design——Classes…命令,按下图右键执行Differential Pair Classes——Add Class命令会生产New Class,右键更名成所需要的差分网络类名称,单击添加归属于此网络

类的网络成员(前提是需要事先建立差分对网络)。

步骤2:建立差分对网络,PCB中执行View——Workspace Panels——PCB——PCB命令打开PCB面板,面板切换至Differential Pairs Editor,点击选择相应的差分网络类后再点击按钮Add,输入自定义的网络差分对名称,同时设置定义好对应的差分网络(Positive Net和Negative Net)。

也可以通过双击Differential Pairs Editor面板中的差分网络类或执行Design——Classes…命令,把所建立的差分网络对归属到对应的差分网络类。

三. ROOM相关:

1. ROOM的组建:主要目的是用于设置个别器件内部的铺铜或布线间距。

PCB中执行Design ——Rooms——Place Rectangular Room命令,按Tab键,设置好相关名称属性,在PCB中相应的器件封装上面画好Room区域。

2. 原理图导入PCB时是否生产单页ROOM

在PCB中执行Project——Project Options…

把下图中框选的勾选项来决定是否生成原理图单页ROOM

1. 间距(Clearance)设置:

2. 线宽(Width )设置:

3. 差分对布线(Differential Pairs Routing)设置:

4.

5.

6.

7. 设计规则优先级的调整:同一类规则的优先级栏数字越小则优先级越高,可以通过调整面

板左下角的Priorties按钮调整优先级。

五. PCB网络等长及阻抗说明:

1. MDIO差分网络组: 差分阻抗100欧,线宽距6/9mil,差分网络等长1070mil,误差+/-10mil,起始参照网络差分组MDIO3_P/N;

2. GMAC网络组: 阻抗50欧,线宽距7/7mil,网络等长2455mil,误差+/-10mil,起始参照网络GMAC_RXDV;

3. LCD MIPI差分网络组: 差分阻抗100欧,线宽距6/9mil,差分网络等长1785mil,误差+/-10mil,起始参照网络差分组MIPI_D3P/N;

4. SLVDS差分网络组: 差分阻抗100欧,线宽距6/9mil,差分网络等长1620mil,误差+/-10mil,起始参照网络差分组LVDS_Y0P/N;

5. SDCARD0网络组: 阻抗50欧,线宽距7/7mil,网络等长1380mil(参照SD0_CLK网络),加上上拉布线网络等长1535mil,误差+/-10mil;

6. RGB_M1网络组:使用板对板连接器SCSI40P_1.27_MALE,封装PIN针脚四行,行距75mil,因连接器内部针脚长度差异,PCB布线时每行需要依次增减75mil以调整布线总长。

起始布线参照网络LCD_CLK;

[ LCD_R7,LCD_R5,LCD_R3,LCD_R1,LCD_CLK ] ,阻抗50欧,线宽距7/7mil,网络等长3100mil,误差+/-10mil;

[ LCD_G0,LCD_R6,LCD_R4,LCD_R2,LCD_R0 ] ,阻抗50欧,线宽距7/7mil,网络等长3100-75x1=3025mil,误差+/-10mil;

[ LCD_G2,LCD_G4,LCD_G6,LCD_B0,LCD_B2 ,LCD_B4,LCD_B6,LCD_DE,LCD_HSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长3100-75x2=2950mil,误差+/-10mil;

[ LCD_G1,LCD_G3,LCD_G5,LCD_G7,LCD_B1 ,LCD_B3,LCD_B5,LCD_B7,LCD_VSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长3100-75x3=2875mil,误差+/-10mil;

7. DLVDS差分网络组: 差分阻抗100欧,线宽距6/9mil,差分网络等长1110mil,误差+/-10mil,起始参照网络差分组RXINO+/-;

8. B_RGB网络组:使用板对板连接器SCSI40P_1.27_FEMALE,封装PIN针脚四行,行距75mil,因连接器内部针脚长度差异,PCB布线时每行需要依次增减75mil以调整布线总长。

起始布线参照网络LCD_DE;

[ LCD_G1,LCD_G3,LCD_G5,LCD_G7,LCD_B1 ,LCD_B3,LCD_B5,LCD_B7,LCD_VSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长2140-75x1=2065mil,误差+/-10mil;

[ LCD_G2,LCD_G4,LCD_G6,LCD_B0,LCD_B2 ,LCD_B4,LCD_B6,LCD_DE,LCD_HSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长2140mil,误差+/-10mil;

[ LCD_G0,LCD_R6,LCD_R4,LCD_R2,LCD_R0 ] ,阻抗50欧,线宽距7/7mil,网络等长2140+75x1=2215mil,误差+/-10mil;

[ LCD_R7,LCD_R5,LCD_R3,LCD_R1,LCD_CLK ] ,阻抗50欧,线宽距7/7mil,网络等长2140+75x2=2290mil,误差+/-10mil;

9. RGB_M2网络组:使用板对板连接器SCSI40P_1.27_MALE,封装PIN针脚四行,行距75mil,因连接器内部针脚长度差异,PCB布线时每行需要依次增减75mil以调整布线总长。

起始布线参照网络LCD_R0;

[ LCD_R7,LCD_R5,LCD_R3,LCD_R1,LCD_CLK ] ,阻抗50欧,线宽距7/7mil,网络等长3025+75x1=3100mil,误差+/-10mil;

[ G0,LCD_R6,LCD_R4,LCD_R2,LCD_R0 ] ,阻抗50欧,线宽距7/7mil,网络等长3025mil,误差+/-10mil;

[ G2,G4,G6,B0,B2 ,B4,B6,LCD_DE,LCD_HSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长3025-75x1=2950mil,误差+/-10mil;

[ G1,G3,G5,G7,B1 ,B3,B5,B7,LCD_VSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长3025-75x2=2875mil,误差+/-10mil;

六. 走线式铺铜网络备注,避免遗忘:

1. BL-VDD_TF_3V3

2. TL-VSYS_IN

3. BL-VSYS_IN

4. BL-D3V3_HUB

5. BL-VDD_PHY_3V3

6. TL-VDD_5V4

7. BL_I2S_D3V3

8. TL_VDD_5V TL_VDD_5V

9. TL_NetD5_2

10. BL_VDD_5V BL_VDD_5V

11. TL_VDD_CORE

12. BL_VDD_12V。