基于verilog的交通灯程序

基于verilog的交通灯设计(状态机)

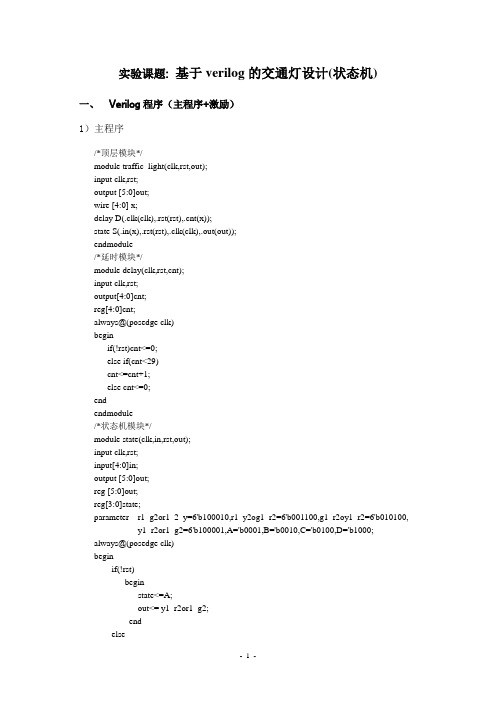

实验课题:基于verilog的交通灯设计(状态机)一、Verilog程序(主程序+激励)1)主程序/*顶层模块*/module traffic_light(clk,rst,out);input clk,rst;output [5:0]out;wire [4:0] x;delay D(.clk(clk),.rst(rst),.cnt(x));state S(.in(x),.rst(rst),.clk(clk),.out(out));endmodule/*延时模块*/module delay(clk,rst,cnt);input clk,rst;output[4:0]cnt;reg[4:0]cnt;always@(posedge clk)beginif(!rst)cnt<=0;else if(cnt<29)cnt<=cnt+1;else cnt<=0;endendmodule/*状态机模块*/module state(clk,in,rst,out);input clk,rst;input[4:0]in;output [5:0]out;reg [5:0]out;reg[3:0]state;parameter r1_g2or1_2_y=6'b100010,r1_y2og1_r2=6'b001100,g1_r2oy1_r2=6'b010100, y1_r2or1_g2=6'b100001,A='b0001,B='b0010,C='b0100,D='b1000;always@(posedge clk)beginif(!rst)beginstate<=A;out<= y1_r2or1_g2;endelsebegincase(state)A: beginif(in<25)state<=A;elsebeginstate<=B;out<=r1_g2or1_2_y;endendB: beginif(in>24)state<=B;elsebeginstate<=C;out<=r1_y2og1_r2;endendC: beginif(in<25)state<=C;elsebeginstate<=D;out<=g1_r2oy1_r2;endendD: beginif(in>24)state<=D;elsebeginstate<=A;out<=y1_r2or1_g2;endendendcaseendendendmodule2)激励module test;reg clk,rst;wire [5:0]out;traffic_light test(clk,rst,out);initialbeginclk='b1;forever #5 clk=~clk;endinitialbeginrst='b0;#10 rst='b1;#500 rst='b0;#10 rst='b1;endendmodule二、实验波形图截图三、波形分析输出out[5:0]分别对应:out[5]:主干道红灯out[4]:主干道黄灯out[3]:主干道绿灯out[2]:支干道红灯out[1]:支干道黄灯out[0]:支干道绿灯初始状态为:主干道红灯亮,支干道绿灯亮。

用verilog语言编写交通灯程序

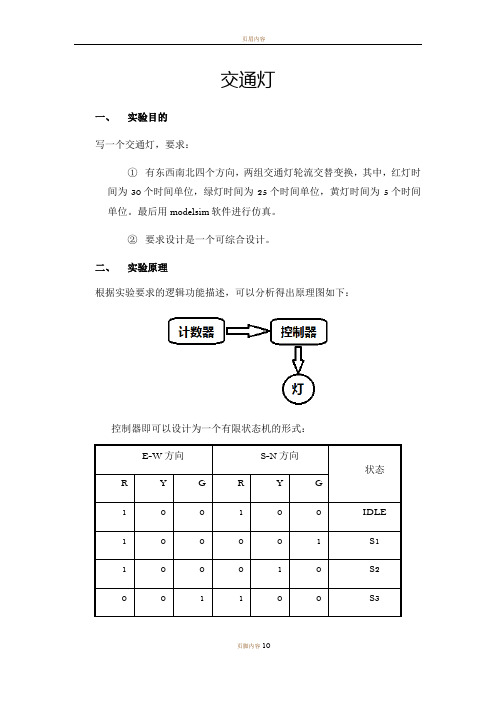

交通灯一、实验目的写一个交通灯,要求:①有东西南北四个方向,两组交通灯轮流交替变换,其中,红灯时间为30个时间单位,绿灯时间为25个时间单位,黄灯时间为5个时间单位。

最后用modelsim软件进行仿真。

②要求设计是一个可综合设计。

二、实验原理根据实验要求的逻辑功能描述,可以分析得出原理图如下:控制器即可以设计为一个有限状态机的形式:E-W方向S-N方向状态R Y G R Y G100100IDLE100001S1100010S2001100S3010100S4根据实验要求画出控制器的状态转移图如下:三、代码1、源代码(1)控制器模块module traffic_lights(clk,rst,count,ew,sn);input clk,rst;input[5:0] count;output[2:0] ew,sn;reg[2:0] ew,sn;reg[3:0] state;parameter Idle=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100; always @(posedge clk)if(!rst)beginstate<=Idle;endelsecasex(state)Idle: if(rst)beginstate<=s1;ends1: if(count=='d25)beginstate<=s2;ends2: if(count=='d30)beginstate<=s3;ends3: if(count=='d55)beginstate<=s4;ends4: if(count=='d60)beginstate<=s1;endendcasealways @(posedge clk)beginif(!rst)beginew<=3'b100;sn<=3'b100;endelsecasex(state)Idle: if(rst)beginew<=3'b100;sn<=3'b001;ends1: if(count=='d25)beginew<=3'b100;sn<=3'b010;ends2: if(count=='d30)beginew<=3'b001;sn<=3'b100;ends3: if(count=='d55)beginew<=3'b010;sn<=3'b100;ends4: if(count=='d60)beginew<=3'b100;sn<=3'b001;enddefault: state<=Idle;endcaseendendmodule(2)计数器模块module counter(en,clk,rst,out);output[5:0]out;input en,clk,rst;reg[5:0] out;always@(posedge clk or negedge rst)beginif(!rst)out<='d0;else if(!en&&out<'d60)out<=out+1;elseout<='d1;endendmodule(3)将控制器与计数器进行连接module traffic_lights_top(out,clk,rst,en,ew,sn); input clk,rst,en;output[2:0] ew,sn;output[5:0]out;wire[5:0] out;traffic_lights u1(.clk(clk),.rst(rst),.count(out),.ew(ew),.sn(sn));counter u2(.en(en),.clk(clk),.rst(rst),.out(out));endmodule2、激励`timescale 1ns/100ps module traffic_lights_tb;reg clk,rst,en;wire[2:0] ew,sn;wire[5:0]out;traffic_lights_top m(.clk(clk),.rst(rst),.en(en),.ew(ew),.sn(sn),.out(out));always#5 clk=~clk;initialen<=1;initialbeginclk<=1;en<=0;rst<=0;#5 rst<=1;endendmodule四、仿真波形(图一)(图二)五、波形说明波形图中,从上至下依次为:时钟信号clk、复位信号rst、计数器使能端en、东西方向上灯的状态ew、南北方向上灯的状态sn、计数器的输出out。

基于Verilog的交通灯控制器的设计

武汉科技大学课题:交通灯控制器的设计编号:17指导老师:冯玉林班级:自动化0703班姓名:筱启…………………………坚持,就是胜利………………………目 录1. 设计内容与要求 (2)2. 交通灯控制系统的组成框图 (3)3. 交通灯控制电路的设计 (4)4. 交通灯控制电路设计的难点与解决方法 (5)5. 交通灯控制电路的Verilog 语句 (6)5. 交通灯控制电路的程序和波形分析 (12)6. EPF10K10LC84-4芯片引脚分配图 (20)7. 实验小结 (21)一、 设计内容与要求① 设计一个十字路口交通信号灯的定时控制电路。

要求红、绿灯按一定的规律亮和灭,并在亮灯期间进行倒计时,并将运行时间用数码管显示出来。

②绿灯亮时,为该车道允许通行信号,红灯亮时,为该车道禁止通行信号。

要求主干道每次通行时间为99秒,支干道每次通行时间为30秒。

每次变换运行车道前绿灯闪烁,持续时间为5秒。

即车道要由主干道转换为支干道时,主干道在通行时间只剩下5秒钟时,绿灯闪烁显示,支干道仍为红灯,以便主干道上已过停车线的车继续通行,未过停车线的车停止通行。

同理,当车道由支干道转换为主干道时,支干道绿灯闪烁显示5秒钟,主干道仍为红灯。

③ 对红、绿灯的运行时间要能比较方便的进行重新设置。

④ 添加左转灯的控制,可自行到实际十字路口观看规律并实现。

对器件进行在系统编程和实验验证。

⑤用Verilog 语言对设计进行描述,设计一个测试方案,通过Muxplus 对设计进行仿真验证。

并能够下载到实验板上调试成功。

二、交通灯控制系统的组成框图交通信号灯控制原理图绿 灯 左拐灯红 灯 绿 灯 左拐灯红 灯 交通信号灯控制系统框图三、交通灯控制电路的设计交通灯控制器设计的重点是控制电路的设计,根据设计要求分析,控制电路的算法可用下图所示的ASM图描述。

各状态的详细说明如下:S0状态:主干道绿灯亮,支干道红灯亮,此时若主干道有车等待左拐,而且主干道绿灯已亮足规定的时间间隔Ts;在主干道绿灯亮了(Ts-5)s后,则开始闪亮,直至绿灯亮了Ts;控制器发出状态转换信号Tempm==0,输出从状态S0转换到S1。

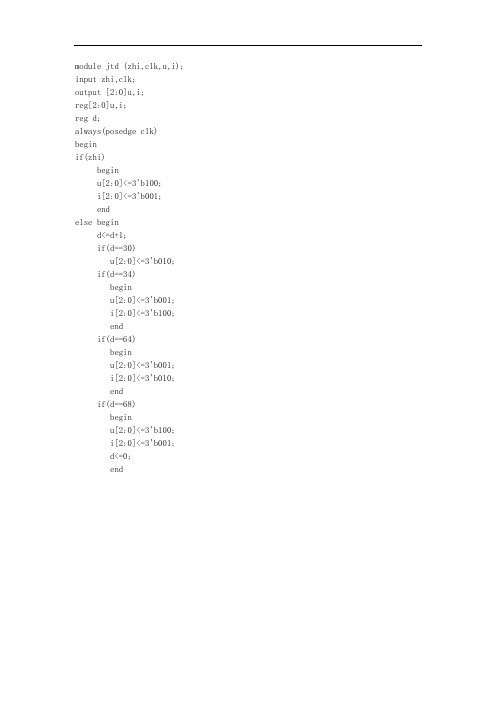

verilog交通灯设计

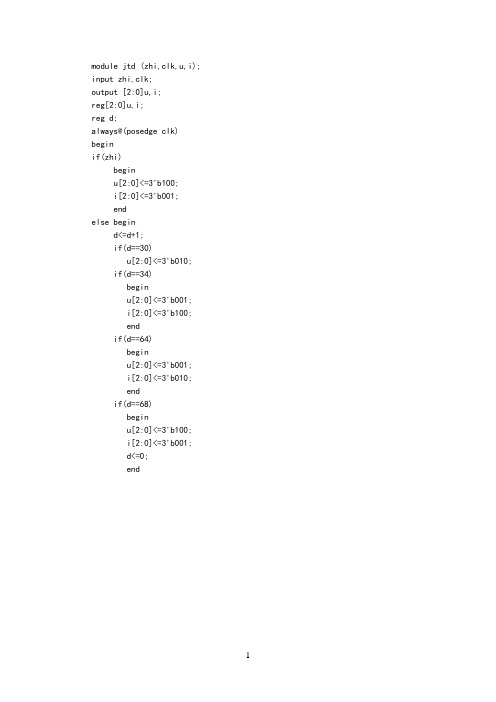

module jtd (zhi,clk,u,i); input zhi,clk;output [2:0]u,i;reg[2:0]u,i;reg d;always@(posedge clk) beginif(zhi)beginu[2:0]<=3'b100;i[2:0]<=3'b001;endelse begind<=d+1;if(d==30)u[2:0]<=3'b010; if(d==34)beginu[2:0]<=3'b001; i[2:0]<=3'b100; endif(d==64)beginu[2:0]<=3'b001; i[2:0]<=3'b010; endif(d==68)beginu[2:0]<=3'b100; i[2:0]<=3'b001; d<=0;endmodule jtd(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [5:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s0;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin u[2:0]<=3'b010;i[2:0]<=3'b001;d=d+1;if(d==4)begin state<=s2;d=0;end else state<=s1;ends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin u[2:0]<=3'b001;i[2:0]<=3'b010;d=d+1;if(d==4)begin state<=s4;d=0;end else state<=s3;enddefault: state<=s4;endcaseendendendmodule黄灯闪module jtde(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [6:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin d=d+1;if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s1;endif(d==3)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==4)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s2;d=0;endends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin d=d+1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d=0;endenddefault: state<=s4;endcaseendend黄灯闪且倒计时module mnb(zhi,u,i,clk,rst,ugx,usx,igx,isx);input zhi,clk,rst;output [2:0]u,i;output [3:0]ugx,usx,igx,isx;reg [2:0]u,i;reg[4:0]state;reg [4:0]ugx,usx,igx,isx;reg [6:0]d,e,f;initialbegin d<=0;e<=30;f<=34;endparameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=0;usx<=0;igx<=0;isx<=0;if(zhi)beginstate<=s0;d<=0;e<=30;f<=35;end else state<=s4;ends0:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30)begin state<=s1;d<=0;e<=4;f<=4;end else state<=s0;ends1:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;e<=e-1;f<=f-1;if(d==0)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==3)beginu[2:0]<=3'b000;i[2:0]<=3'b001;state<=s2;d<=0;e<=35;f<=30;endends2:beginu[2:0]<=3'b001;i[2:0]<=3'b100;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30) begin state<=s3;d<=0;e<=4;f<=4;end else state<=s2;ends3:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e<=e-1;f<=f-1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d<=0;endenddefault: state<=s4;endcaseendendendmodule黄灯闪。

Verilog代码(计数器、交通灯、串并转换)

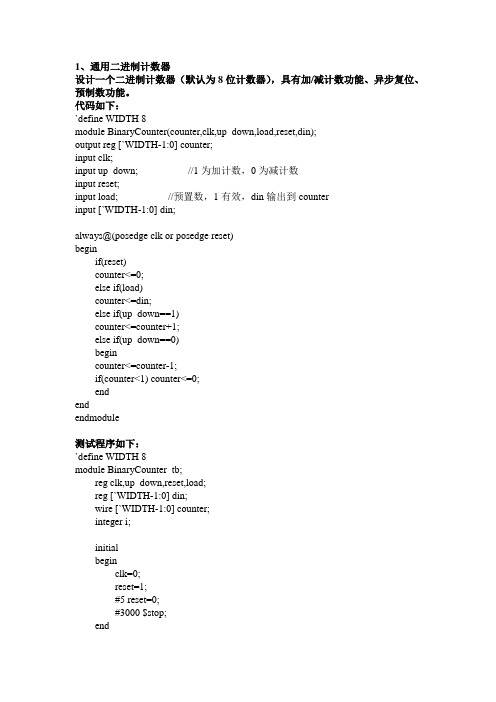

1、通用二进制计数器设计一个二进制计数器(默认为8位计数器),具有加/减计数功能、异步复位、预制数功能。

代码如下:`define WIDTH 8module BinaryCounter(counter,clk,up_down,load,reset,din);output reg [`WIDTH-1:0] counter;input clk;input up_down; //1为加计数,0为减计数input reset;input load; //预置数,1有效,din输出到counterinput [`WIDTH-1:0] din;always@(posedge clk or posedge reset)beginif(reset)counter<=0;else if(load)counter<=din;else if(up_down==1)counter<=counter+1;else if(up_down==0)begincounter<=counter-1;if(counter<1) counter<=0;endendendmodule测试程序如下:`define WIDTH 8module BinaryCounter_tb;reg clk,up_down,reset,load;reg [`WIDTH-1:0] din;wire [`WIDTH-1:0] counter;integer i;initialbeginclk=0;reset=1;#5 reset=0;#3000 $stop;endalways #5 clk=~clk;/*always@(posedge clk)beginup_down={$random}%2;load={$random}%2;din={$random}%256;end*/initialbegin#5;for(i=0;i<256;i=i+3)begindin=i;#10;endendinitialbeginup_down=1;load=1;#20 load=0;#30 load=1;#30 load=0;endalways #200 up_down=~up_down;BinaryCounter bcounter(.counter(counter),.clk(clk),.up_down(up_down),.load(load),.reset(reset),.din(din));endmodule波形图如下:图1 二进制计数器波形图图2 二进制计数器波形图从图像可看出,20s-50s为加计数,50s-80s时load=1,执行置数功能,80s-200s 时up_down=1,为加计数,200s-280s时up_down=0,为减计数。

verilog交通灯设计说明

module jtd (zhi,clk,u,i); input zhi,clk;output [2:0]u,i;reg[2:0]u,i;reg d;always(posedge clk)beginif(zhi)beginu[2:0]<=3'b100;i[2:0]<=3'b001;endelse begind<=d+1;if(d==30)u[2:0]<=3'b010; if(d==34)beginu[2:0]<=3'b001; i[2:0]<=3'b100; endif(d==64)beginu[2:0]<=3'b001; i[2:0]<=3'b010; endif(d==68)beginu[2:0]<=3'b100; i[2:0]<=3'b001; d<=0;endmodule jtd(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [5:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always(posedge clk)beginif(!rst) begin state<=s0;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin u[2:0]<=3'b010;i[2:0]<=3'b001;d=d+1;if(d==4)begin state<=s2;d=0;end else state<=s1;ends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin u[2:0]<=3'b001;i[2:0]<=3'b010;d=d+1;if(d==4)begin state<=s4;d=0;end else state<=s3;enddefault: state<=s4;endcaseendendendmodule黄灯闪module jtde(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [6:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin d=d+1;if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s1;endif(d==3)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==4)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s2;d=0;endends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin d=d+1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d=0;endenddefault: state<=s4;endcaseendend黄灯闪且倒计时module mnb(zhi,u,i,clk,rst,ugx,usx,igx,isx);input zhi,clk,rst;output [2:0]u,i;output [3:0]ugx,usx,igx,isx;reg [2:0]u,i;reg[4:0]state;reg [4:0]ugx,usx,igx,isx;reg [6:0]d,e,f;initialbegin d<=0;e<=30;f<=34;endparameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=0;usx<=0;igx<=0;isx<=0;if(zhi)begin state<=s0;d<=0;e<=30;f<=35;end else state<=s4;ends0:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30)begin state<=s1;d<=0;e<=4;f<=4;end else state<=s0;ends1:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;e<=e-1;f<=f-1;if(d==0)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;endif(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;d<=d+1;state<=s1;endif(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;endif(d==3)beginu[2:0]<=3'b000;i[2:0]<=3'b001;state<=s2;d<=0;e<=35;f<=30;endends2:beginu[2:0]<=3'b001;i[2:0]<=3'b100;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e<=e-1;f<=f-1;if(d==30) begin state<=s3;d<=0;e<=4;f<=4;end else state<=s2; ends3:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e<=e-1;f<=f-1; if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d<=0;endenddefault: state<=s4;endcaseendendendmodule黄灯闪。

4 基于Verilog_HDL设计的交通灯——代码

input clr,clk;

output red_led,yellow_led,green_led,a,b,c,d,e,f,g,p,sel;

endcase

else begin

if(timer>8'h46)timer<=8'h00;

else if(timer==8'h?0)timer<=timer-4'h7;

else timer<=timer-1'b1;

end

endmodule

anydiv_clk anydiv_clk1(.cki(clk),.f(2'd2),.cko(second)),

anydiv_clk2(.cki(clk),.f(12'd1000),.cko(scanclk));

deled deled(.in(din),.a(a),.b(b),.c(c),.d(d),.e(e),.f(f),.g(g),.dp(p));

assign red_led=(state==red)?1:0;

assign green_led=(state==green)?1:0;

assign yellow_led=(state==yellow)?1:0;

always@(posedge clk or negedge clr) //posedge state_clk or

if(q>8'h46)q=8'h01;

else if(q==8'h?0)q=q-4'h7;

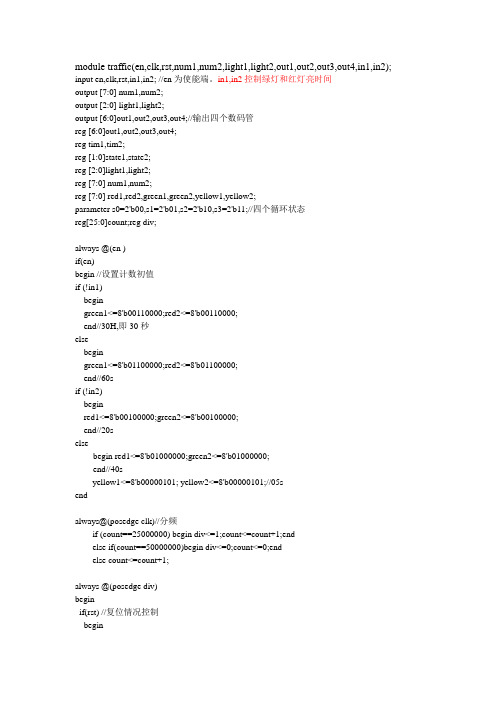

交通灯控制系统 verilog

module traffic(en,clk,rst,num1,num2,light1,light2,out1,out2,out3,out4,in1,in2); input en,clk,rst,in1,in2; //en为使能端。

in1,in2控制绿灯和红灯亮时间output [7:0] num1,num2;output [2:0] light1,light2;output [6:0]out1,out2,out3,out4;//输出四个数码管reg [6:0]out1,out2,out3,out4;reg tim1,tim2;reg [1:0]state1,state2;reg [2:0]light1,light2;reg [7:0] num1,num2;reg [7:0] red1,red2,green1,green2,yellow1,yellow2;parameter s0=2'b00,s1=2'b01,s2=2'b10,s3=2'b11;//四个循环状态reg[25:0]count;reg div;always @(en )if(en)begin //设置计数初值if (!in1)begingreen1<=8'b00110000;red2<=8'b00110000;end//30H,即30秒elsebegingreen1<=8'b01100000;red2<=8'b01100000;end//60sif (!in2)beginred1<=8'b00100000;green2<=8'b00100000;end//20selsebegin red1<=8'b01000000;green2<=8'b01000000;end//40syellow1<=8'b00000101; yellow2<=8'b00000101;//05sendalways@(posedge clk)//分频if (count==25000000) begin div<=1;count<=count+1;endelse if(count==50000000)begin div<=0;count<=0;endelse count<=count+1;always @(posedge div)beginif(rst) //复位情况控制beginlight1<=3'b001;num1<=green1;endelse if(en)begin //使能有效开始控制计数if(!tim1) //开始控制begin //主干道交通灯点亮控制tim1<=1;case(state1)//状态机s0:begin num1<=green1;light1<=3'b001;state1<=s1;end s1:begin num1<=yellow1;light1<=3'b010;state1<=s2;end s2:begin num1<=red1;light1<=3'b100;state1<=s3;ends3:begin num1<=yellow1;light1<=3'b010;state1<=s0;end default:light1<=3'b100;endcaseendelsebegin //倒数计时if(num1>0)if(num1[3:0]==0)beginnum1[3:0]<=4'b1001;num1[7:4]<=num1[7:4]-1;//十位减1endelse num1[3:0]<=num1[3:0]-1; //个位减1 if(num1==1) tim1<=0;endendelsebeginlight1<=3'b010;num1=2'b00;tim1<=0;endendalways @(posedge div ) //从干道beginif(rst) //复位情况控制beginlight2<=3'b100;num2<=red2;endelse if(en)beginif(!tim2)begintim2<=1;case(state1)s0:begin num2<=red2;light2<=3'b100;state2<=s1;ends1:begin num2<=yellow1;light2<=3'b010;state2<=s2;ends2:begin num2<=green2;light2<=3'b001;state2<=s3;ends3:begin num2<=yellow2;light2<=3'b010;state2<=s0;enddefault:light2<=3'b100;endcaseendelsebegin //倒数计时if(num2>0)if(num2[3:0]==0)beginnum2[3:0]<=4'b1001;num2[7:4]<=num2[7:4]-1;endelse num2[3:0]<=num2[3:0]-1;if(num2==1) tim2<=0;endendelsebegintim2<=0;state2<=2'b00;light2<=3'b010;endendalways @(posedge clk)begin //数码管译码显示case(num1[3:0])4'b0000: out1<=~7'b0111111; //0 ,3F4'b0001: out1<=~7'b0000110; //1 ,064'b0010: out1<=~7'b1011011; //2 ,5B4'b0011: out1<=~7'b1001111; //3 ,4F4'b0100: out1<=~7'b1100110; //4 ,664'b0101: out1<=~7'b1101101; //5 ,6D4'b0110: out1<=~7'b1111101; //6 ,7D 4'b0111: out1<=~7'b0000111; //7 ,07 4'b1000: out1<=~7'b1111111; //8, 7F 4'b1001: out1<=~7'b1101111; //9, 6F default: out1<=~7'b0111111; //0 ,3F endcaseendalways @(posedge clk)begin //数码管译码显示case(num1[7:4])4'b0000: out2<=~7'b0111111; //0 ,3F 4'b0001: out2<=~7'b0000110; //1 ,06 4'b0010: out2<=~7'b1011011; //2 ,5B 4'b0011: out2<=~7'b1001111; //3 ,4F 4'b0100: out2<=~7'b1100110; //4 ,66 4'b0101: out2<=~7'b1101101; //5 ,6D 4'b0110: out2<=~7'b1111101; //6 ,7D 4'b0111: out2<=~7'b0000111; //7 ,07 4'b1000: out2<=~7'b1111111; //8, 7F 4'b1001: out2<=~7'b1101111; //9, 6F default: out2<=~7'b0111111; //0 ,3F endcaseendalways @(posedge clk)begin //数码管译码显示case(num2[3:0])4'b0000: out3<=~7'b0111111; //0 ,3F 4'b0001: out3<=~7'b0000110; //1 ,06 4'b0010: out3<=~7'b1011011; //2 ,5B 4'b0011: out3<=~7'b1001111; //3 ,4F 4'b0100: out3<=~7'b1100110; //4 ,66 4'b0101: out3<=~7'b1101101; //5 ,6D 4'b0110: out3<=~7'b1111101; //6 ,7D 4'b0111: out3<=~7'b0000111; //7 ,07 4'b1000: out3<=~7'b1111111; //8, 7F 4'b1001: out3<=~7'b1101111; //9, 6F default: out3<=~7'b0111111; //0 ,3F endcaseendalways @(posedge clk)begin //数码管译码显示case(num2[7:4])4'b0000: out4<=~7'b0111111; //0 ,3F 4'b0001: out4<=~7'b0000110; //1 ,06 4'b0010: out4<=~7'b1011011; //2 ,5B 4'b0011: out4<=~7'b1001111; //3 ,4F 4'b0100: out4<=~7'b1100110; //4 ,66 4'b0101: out4<=~7'b1101101; //5 ,6D 4'b0110: out4<=~7'b1111101; //6 ,7D 4'b0111: out4<=~7'b0000111; //7 ,07 4'b1000: out4<=~7'b1111111; //8, 7F 4'b1001: out4<=~7'b1101111; //9, 6F default: out4<=~7'b0111111; //0 ,3F endcaseendendmodule。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

module traffic(clk,sm_bit,key,sm_seg,en,rst,hold,light1,light2);

input clk;//定义时钟引脚

input rst,en; //定义复位和使能引脚

output [7:0]sm_bit;//定义数码管位选引脚

output [7:0]sm_seg;//定义数码管段选引脚

output[2:0]light1,light2;//定义两个方向交通灯

reg [7:0]sm_bit_r;

reg [7:0]sm_seg_r;

reg [3:0]disp_dat;;//定义数码管显示数据寄存器

reg[24:0]count;//定义计数器寄存器

reg sec;//定义秒信号寄存器

reg tim1,tim2,st1,st2;//定义tim1位倒计时是否到达的位标识

reg[1:0]state1,state2,ste;//定义一些状态

reg[2:0]light1,light2;

reg[3:0]num;

reg[7:0]num1,num2;//num1和num2的值为倒计时的值

reg[7:0]red1,red2,green1,green2,yellow1,yellow2;//定义红黄蓝灯的一些状态

assign sm_bit=sm_bit_r;

assign sm_seg=sm_seg_r;

always@(posedge clk)

begin

count=count+1'b1;

if(count==25'd2*******)//时间达到一秒

begin

count=25'd0;

sec=~sec;

end

end

always@(posedge clk)

begin

case (count[17:15])

3'd0:disp_dat = num1[3:0];//秒个位

3'd1:disp_dat = num1[7:4]; //秒十位

3'd2:disp_dat = 4'ha; //显示"-"

3'd3:disp_dat = num2[3:0]; //分个位

3'd4:disp_dat = num2[7:4]; //分十位

3'd5:disp_dat = 4'ha; //显示"-"

endcase

case(count[17:15]) //选择数码管显示位3'd0:sm_bit_r = 8'b11111110; //选择第一个数码管显示

3'd1:sm_bit_r = 8'b11111101; //选择第二个数码管显示

3'd2:sm_bit_r = 8'b11111011; //选择第三个数码管显示

3'd3:sm_bit_r = 8'b11110111; //选择第四个数码管显示

3'd4:sm_bit_r = 8'b11101111; //选择第五个数码管显示

3'd5:sm_bit_r = 8'b11011111; //选择第六个数码管显示

3'd6:sm_bit_r = 8'b10111111; //选择第七个数码管显示

3'd7:sm_bit_r = 8'b01111111; //选择第八个数码管显示endcase

end

always @(posedge clk)

begin

case(disp_dat)

4'h0:sm_seg_r = 8'hc0; //显示0

4'h1:sm_seg_r = 8'hf9; //显示1

4'h2:sm_seg_r = 8'ha4; //显示2

4'h3:sm_seg_r = 8'hb0; //显示3

4'h4:sm_seg_r = 8'h99; //显示4

4'h5:sm_seg_r = 8'h92; //显示5

4'h6:sm_seg_r = 8'h82; //显示6

4'h7:sm_seg_r = 8'hf8; //显示7

4'h8:sm_seg_r = 8'h80; //显示8

4'h9:sm_seg_r = 8'h90; //显示9

4'ha:sm_seg_r = 8'hbf; //显示-

default:sm_seg_r = 8'hff; //不显示endcase

end

always@(en)

if(!en)

begin

green1<=8'b00110101;

red1<=8'b00100101;

yellow1<=8'b00000101;

green2<=8'b00100101;

red2<=8'b00110101;

yellow2<=8'b00000101;

end

always@(posedge sec)//南北方向

begin

if(!rst)//复位模块

begin

light1<=3'b001;

num1<=green1;

end

if(!tim1)

begin

tim1<=1;

case(state1)

2'b00:begin num1<=green1;light1<=3'b110;state1<=2'b01;end

2'b01:begin num1<=yellow1;light1<=3'b101;state1<=2'b11;end

2'b11:begin num1<=red1;light1<=3'b011;state1<=2'b10;end

2'b10:begin num1<=yellow1;light1<=3'b101;state1<=2'b00;end//状态机使三个状态一直循环

default:light1<=3'b011;

endcase

end

else

begin

if(num1==1)tim1<=0;

else if(num1>0)

if(num1[3:0]==0)

begin

num1[3:0]<=4'b1001;//倒计时模块

num1[7:4]<=num1[7:4]-1;

end

else num1[3:0]<=num1[3:0]-1;

end

end

always@(posedge sec)//东西方向

begin

if(!rst)//复位模块

begin

light2<=3'b100;

num2<=red2;

end

if(!tim2)

begin

tim2<=1;

case(state2)

2'b00:begin num2<=red2;light2<=3'b011;state2<=2'b01;end

2'b01:begin num2<=yellow1;light2<=3'b101;state2<=2'b11;end

2'b11:begin num2<=green2;light2<=3'b110;state2<=2'b10;end

2'b10:begin num2<=yellow2;light2<=3'b101;state2<=2'b00;end

default:light2<=3'b011;

endcase

end

else

begin

if(num2==1)tim2<=0;

else if(num2>0)

if(num2[3:0]==0)

begin

num2[3:0]<=4'b1001;

num2[7:4]<=num2[7:4]-1;

end

else num2[3:0]<=num2[3:0]-1;

end

end

endmodule。