数字逻辑课后答案 第三章

数字逻辑-习题以及习题答案

AD

F的卡诺图

ACD

G的卡诺图

根据F和G的卡诺图,得到:F G

湖南理工学院计算机与信息工程系通信教研室 陈进制作

第3章习题 3.4 在数字电路中,晶体三极管一般工作在什么状态?

答:在数字电路中,晶体三极管一般工作在饱和导通状态 或者截止状态。

湖南理工学院计算机与信息工程系通信教研室 陈进制作

第3章习题

111110

1100110

⊕ ⊕⊕⊕ ⊕

10 000 1

⊕ ⊕⊕⊕ ⊕⊕

10 101 01

⑵ (1100110)2 = 64+32+4+2 = (102)10 = (0001 0000 0010)8421码

(1100110)2 =( 101?0101 )格雷码

湖南理工学院计算机与信息工程系通信教研室 陈进制作

第2章习题

2.2 用逻辑代数的公理、定理和规则证明下列表达式:

⑴ AB AC AB AC

⑵ AB AB AB AB 1

⑶ AABC ABC ABC ABC

证⑴:AB AC

AB AC

A B A C

AA AC BA BC

证⑶:AABC

A A B C

AB AC

第1章习题 1.3 数字逻辑电路可分为哪两种类型?主要区别是什么?

答:数字逻辑电路可分为组合逻辑电路、时序逻辑电路两 种类型。 主要区别:组合逻辑电路无记忆功能, 时序逻辑电路有记忆功能。

湖南理工学院计算机与信息工程系通信教研室 陈进制作

第1章习题 1.6 将下列二进制数转换成十进制数、八进制数和十六进制数。

第2章习题 2.8 ⑴ ②求出最简或-与表达式。

两次取反法

圈0,求F 最简与或式。

数字逻辑知到章节答案智慧树2023年江西理工大学

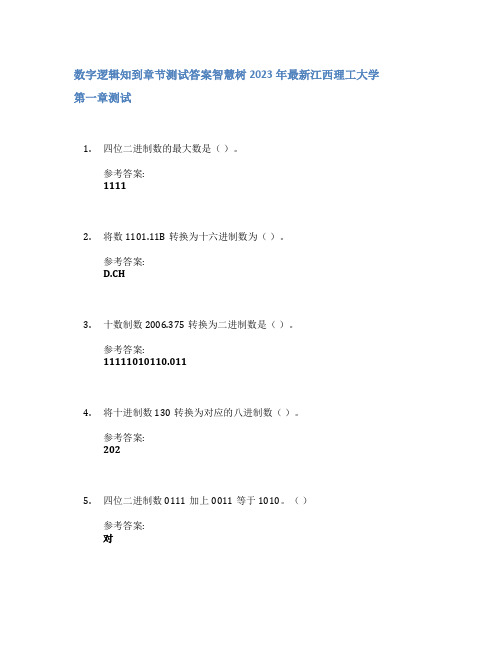

数字逻辑知到章节测试答案智慧树2023年最新江西理工大学第一章测试1.四位二进制数的最大数是()。

参考答案:11112.将数1101.11B转换为十六进制数为()。

参考答案:D.CH3.十数制数2006.375转换为二进制数是()。

参考答案:11111010110.0114.将十进制数130转换为对应的八进制数()。

参考答案:2025.四位二进制数0111加上0011等于1010。

()参考答案:对6.16进制数2B等于10进制数()。

参考答案:437.16进制数3.2等于2进制数()。

参考答案:11.0018.十进制数9比十六进制数9小。

()参考答案:错9.与八进制数(47.3)8等值的数为()参考答案:(100111.011)2;(27.6)1610.有符号数10100101的补码是()。

参考答案:1101101111.[X]补+[Y]补=()。

参考答案:[X+Y]补12.十进制数7的余3码是()。

参考答案:101013.以下代码中为无权码的为()。

参考答案:余三码;格雷码14.格雷码具有任何相邻码只有一位码元不同的特性。

()参考答案:对第二章测试1.逻辑函数的表示方法中具有唯一性的是()。

参考答案:卡诺图;真值表2.在何种输入情况下,“与非”运算的结果是逻辑0。

()参考答案:全部输入是13.逻辑变量的取值1和0可以表示()。

参考答案:电位的高、低;真与假;开关的闭合、断开;电流的有、无4.A’+B’等于()。

参考答案:(AB)’5.以下表达式中符合逻辑运算法则的是()。

参考答案:A+1=16.逻辑函数两次求反则还原,逻辑函数的对偶式再作对偶变换也还原为它本身。

()参考答案:对7.求Y=A(B+C)+CD的对偶式是()。

参考答案:(A+BC)(C+D)8.已知逻辑函数Y的波形图如下图,该逻辑函数式是Y=()。

参考答案:A’BC+AB’C+ABC’9.任意函数的全体最大项之积为1。

()参考答案:错10.下列哪些项属于函数Y(A、B、C、D)=(A’B+C)’D+AB’C’的最小项()。

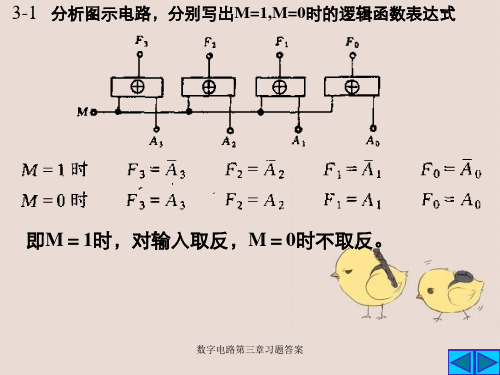

数字逻辑电路第三章部分答案

Hale Waihona Puke 根据与非与非式即可画出逻辑图其实将余3码直接当作一个二进制数十进制bcd代码再加3减去3就还原成为一位十进制数的bcd码设输出变量为ryg且低电平时点亮led即低电平输出有效

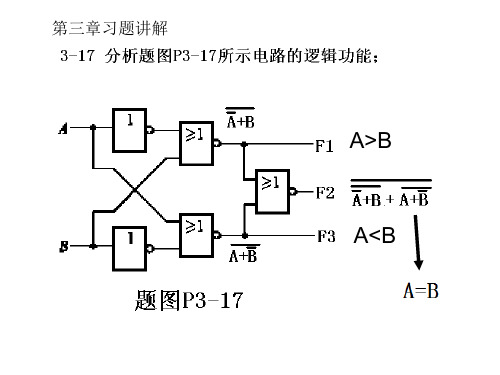

第三章习题讲解

A>B

A<B

同或电路

2线—4线译码电路

结果:

根据与非与非式即可 画出逻辑图

其实,将余3码直接当 作一个二进制 数(十进 制BCD代码再加3), 减去3就(还原)成为 一位十进制数的BCD码

8-1 MUX74151 功能表

功 能 表

S2 X 0 0 0 0 1 1 1 1 输入 S1 X 0 0 1 1 0 0 1 1 S0 X 0 1 0 1 0 1 0 1 使能 E 1 0 0 0 0 0 0 0 0 输出 Y 0 D0 D1 D2 D3 D4 D5 D6 D7 Y Y

设输出变量为R、Y、G,且低电平时点亮LED(即低电平输出有效)。 故可以列出真值表如下:

经变换 ,可以列出真值表如下:

列出最小项表达式 如下:

经变换 ,可以列出真值表如下:

列出最小项表达式 如下:

经变换 ,可以列出真值表如下:

卡诺图:

经变换 ,可以列出真值表如下:

根据简化后的与非与非式,选择合适的门电路 (与非门、OC输出门等)实现电路功能

11

D00 D D11 D D22 D D33 D D44 D D55 D D66 D D77 D

根据:

可得:

D0、D3、D4、D6为1; D1、D2、D5、D7为0。

则F的状态依次为: D0、D1、D2、D3、D4、D5、D6、D7、D0、D1………… 1 0 0 1 1 0 1 0 1 0 : D0、D3、D4、D6为1; D1、D2、D5、D7为0。

《数字逻辑》第3章习题答案

题

【3-1】填空: (1) 逻辑代数中有三种最基本运算: 与 、 或 和 非 ,在此基础上又派生出五种基本运算, 分别为 与非 、 或非 、 异或 、 同或 、和 与或非 。 (2) 与运算的法则可概述为:有 0 出 0 ,全 1 出 1 ;类似地,或运算的法则为 有”1”出”1”, 全”0”出”0” 。 (3) 摩根定理表示为: A B = A B ; A B = A B 。 (4) 函数表达式 Y= AB C D ,则其对偶式为 Y ' = ( A B)C D 。 积的形式结果应为 M ( 0,1,2,4,5,8,9,10)。 (5) 函数式 F=AB+BC+CD 写成最小项之和的形式结果应为 m ((3,6,7,11,12,13,14,15)), 写成最大项之

0 0 1 1 1 1

1 1 0 0 1 1

0 1 0 1 0 1

1 1 0 0 1 0

【3-8】写出下列函数的反函数 F ,并将其化成最简与或式。 (1) F1 ( A D )( B C D)( AB C ) (2) F2 ( A B )( BCD E )( B C E )(C A) (3) F3 A B C A D (4) F4 ( A B)C ( B C ) D 解: (1) F1 AD C (2) F2 AB A C E (3) F3 AB AC A D (4) F4 BC C D ABD A B C 【3-9】用对偶规则,写出下列函数的对偶式 F ,再将 F 化为最简与或式。 (1) F1 AB B C A C (2) F2 A B C D (3) F3 ( A C )( B C D)( A B D) ABC (4) F4 ( A B )( A C )( B C )(C D) (5) F5 AB C CD BD C 解:题中各函数对偶函数的最简与或式如下: (1) F1 A BC AB C (2) F2 A B D A C D (3) F3 AC A BD (4) F4 A BC B C CD (5) F5 ABC D (6) F6 AB C D 【3-10】已知逻辑函数 F A B C , G=A⊙B⊙C,试用代数法证明: F G 。 解:

数字逻辑 课后习题答案

4. 最简电路是否一定最佳?为什么?

解答

一个最简的方案并不等于一个最佳的方案。最佳方案应满足全面的性能指标 和实际应用要求。所以,在求出一个实现预定功能的最简电路之后,往往要根据 实际情况进行相应调整。

2. 数字逻辑电路具有哪些主要特点?

解答

数字逻辑电路具有如下主要特点:

● 电路的基本工作信号是二值信号。 ● 电路中的半导体器件一般都工作在开、关状态。 ● 电路结构简单、功耗低、便于集成制造和系列化生产。产品价格低

廉、使用方便、通用性好。 ● 由数字逻辑电路构成的数字系统工作速度快、精度高、功能强、可

第二章

1 假定一个电路中,指示灯 F 和开关 A、B、C 的关系为 F=(A+B)C

试画出相应电路图。 解答

电路图如图 1 所示。

图1

2 用逻辑代数的公理、定理和规则证明下列表达式:

(1) AB + AC = AB + AC (2) AB + AB + AB + AB = 1 (3) AABC = ABC + ABC + ABC

= (A + B) ⋅ (A + B) =B

( ) F = BC + D + D ⋅ B + C ⋅ (AC + B)

= BC + D + (B + C)(AC + B) = BC + D + BC(AC + B) = BC + D + AC + B = B + D + AC

《数字逻辑》鲍家元、毛文林高等教育出版社课后答案【khdaw_lxywyl】

kh da w. co m

答 案 网

课后答案网

2.21 直接根据逻辑表达式,填写卡诺图并化简下列各式为最简 “与或”表达式。 ⑴ F = B+AC ⑵F=D

2.26 如果输入只有原变量而无反变量。用禁止法将下列函数转换 成可用最少的与非门实现,并画出逻辑图。 ⑴ F = AC BC AB BC (逻辑图略) ⑵ F = AABC•BABC ⑶ F = C AB B AB (逻辑图略) ⑷ F = XY Z (逻辑图略) 2.29 确定习图2-1中的输入变量,并使输出功能为: F (A,B,C,D) = ∑m(6,7,12,13 ) 解: F (A,B,C,D) = (AB) ⊕(BC)

(5) F = (B+C+D) (B+C+D) (A+C+D)

ww

⑹ F = D+BC+ABC = (B+C+D) (B+C+D) (A+C+D)

w.

⑸ F = AC+BD = (A+C) (B+C)

课

= (A+D) (B+C) (B+D)

后

(6) F = (B+D) (B+C) (A+C+D) (A+C+D) ⑶ F = ABC+ABD+ACD (7) F = CE = (A+C) (C+D) (B+D) (A+B+C) (8) F = (A+D) (B+D) (A+B+C) (B+C+E) (A+C+E) ⑷ F = AB+CD = (C+D) (B+C) (A+C) 或

课后习题答案_第3章_门电路

数字电子技术基础第三章习题答案3-1 如图3-63a~d所示4个TTL门电路,A、B端输入的波形如图e所示,试分别画出F1、F2、F3和F4的波形图。

略3-2 电路如图3-64a所示,输入A、B的电压波形如图3-64b所示,试画出各个门电路输出端的电压波形。

略3-3 在图3-7所示的正逻辑与门和图3-8所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明F和A、B之间是什么逻辑关系。

答:(1)图3-7负逻辑真值表F与A、B之间相当于正逻辑的“或”操作。

(2)图3-8负逻辑真值表F与A、B之间相当于正逻辑的“与”操作。

3-4 试说明能否将与非门、或非门、异或门当做反相器使用?如果可以,各输入端应如何连接?答:三种门经过处理以后均可以实现反相器功能。

(1)与非门: 将多余输入端接至高电平或与另一端并联;(2)或非门:将多余输入端接至低电平或与另一端并联;(3) 异或门:将另一个输入端接高电平。

3-5 为了实现图3-65所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

答:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;b)多余输入端接低电平或与另两个输入端的一端相连;c) 未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;d )未用或门的两个输入端悬空或都接高电平。

3-6 如要实现图3-66所示各TTL 门电路输出端所示的逻辑关系,请分析电路输入端的连接是否正确?若不正确,请予以改正。

答:a )不正确。

输入电阻过小,相当于接低电平,因此将Ω50提高到至少2K Ω。

b) 不正确。

第三脚V CC 应该接低电平。

c )不正确。

万用表一般内阻大于2K Ω,从而使输出结果0。

因此多余输入端应接低电平,万用表只能测量A 或B 的输入电压。

3-7 (修改原题,图中横向电阻改为6k Ω,纵向电阻改为3.5 k Ω,β=30改为β=80) 为了提高TTL 与非门的带负载能力,可在其输出端接一个NPN 晶体管,组成如图3-67所示的开关电路。

数字电路第三章习题答案

解: 根据题意,该控制电路有三个输入A,B,C; 三个输出G, Y,R。G代表绿灯,Y代表黄灯,R代表红灯。状态赋值如下:1 表示水在电极之上,0表示水在电极之下; 0表示灯亮,1表示灯灭。 按照题意列出的真值表如下。由真值表画出的卡诺图:

数字电路第三章习题答案

3-11

GABAB YABCABC RC

F10 C DAB

F30 CD AB

F20 C DAB

F40 CDAB

解:5号译码器因 E5 0 ,始终处于译码器状态。而1号,2号,3号,4号译码器要受

5号译码器输出控制。(1)当 CD=00时, 只1号译码器译码,其他译码器不译码。当

CD=01时, 只2号译码器译码。(3)当 CD=10时, 只3号译码器译码。当 CD=11时,

Y 1AB A C (B C ) m (1,2,3,7) Y2ABAB m (2,3,4,5)

Y3(AB)(AC) m (0,1,5,7)

Y4ABC ABC m(0,7)

解:先进行化简变换为最小相之和形式:

Y 1 A A B B A C C A A B B C A B C A B C C A BC

数字电路第三章习题答案

3-13 F ( A 3 B 3 ) • ( A 2 B 2 ) A 1 (B 1 ) A 0 ( B 0 )

A和B相等的条件是:最高位相等并且低三位也相等。 所以有:

(A3B3)1 (A 2 B 2 )A 1 ( B 1 )A 0 ( B 0 ) 1 可以把 (A3B3)作为74138待分配的数据,加载到G1控 制端;A2A1A0,B2B1B0分别作为138和151的通道选

数字电路第三章习题答案

3-5 列出题示逻辑图的真值表。图中T331为输出低电平有效的8421码译码器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第三章 时序逻辑

1.写出触发器的次态方程,并根据已给波形画出输出 Q 的波形。

解:

2. 说明由RS 触发器组成的防抖动电路的工作原理,画出对应输入输出波形

解:

3. 已知JK 信号如图,请画出负边沿JK 触发器的输出波形(设触发器的初态为0)

4. 写出下图所示个触发器次态方程,指出CP 脉冲到来时,触发器置“1”的条件。

解:(1)

,若使触发器置“1”,则A 、B 取值相异。

(2),若使触发器置“1”,则A 、B 、C 、D 取值为奇数个1。

5.写出各触发器的次态方程,并按所给的CP 信号,画出各触发器的输出波形(设初态为0)

解:

6. 7. 1

)(1

=+++=+c b a Q

a c

b Q n

n B A B A D +=D C B A K J ⊕⊕⊕==Q A

Q B Q D Q C Q E Q F Q G Q H

2

8. 作出状态转移表和状态图,确定其输出序列。

解:求得状态方程如下 故输出序列为:00011

9. 用D 触发器构成按循环码(000→001→011→111→101→100→000)规律工作的六进制同步计数器

解:先列出真值表,然后求得激励方程

PS NS 输出

N

0 0 0 0 0 1 0

0 0 1 0 1 1 0 0 1 1 1 1 1 0 1 1 1 1 0 1 0 1 0 1 1 0 0 0 1 0 0 0 0 0 1

化简得:

逻辑电路图如下:

10. 用D 触发器设计3位二进制加法计数器,并画出波形图。

n Q 2n Q 1n Q 012+n Q 11+n Q 10+n Q

3

11. 用下图所示的电路结构构成五路脉冲分配器,试分别用简与非门电路及74LS138集成译码器构成这个译码器,并画出连线图。

解:先写出激励方程,然后求得状态方程

得真值表

得状态图

若用与非门实现,译码器输出端的逻辑函数为:

若用译码器74LS138实现,译码器输出端的逻辑函数为:

12

若将下图接成12进制加法器,预置值应为多少?画出状态图及输出波形图。

解:预置值应C=0,B =1,A =1。

13. 分析下图所示同步时序逻辑电路,作出状态转移表和状态图,说明它是Mealy 型电路还是Moore 型电路以及电路的功能。

解: 电路的状态方程和输出方程为: 该电路是Moore 型电路。

当X=0时,电路为模4加法计数器; 当X=1时,电路为模4减法计数器

14. 分析下图所示同步时序逻辑电路,作出状态转移表和状态图,说明这个电路能对何种

序列进行检测?

解:电路的状态方程和输出方程为:由此可见,凡输入序列 “110”,输出就为“1” 。

15. 作“101”序列信号检测器的状态表,凡收到输入序列101时,输出为 1 ;并规定检测的101序列不重叠。

解: 根据题意分析,输入为二进制序列x ,输出为Z ;且电路应具有3个状态: S0、S1、S2。

列状态图和状态表如下:

X =1

X =0

NS / Z PS

16. 某计数器的波形如图示。

解:(1)确定计数器的状态

计数器循环中有7个状态。

17. 对状态表进行编码,并做出状态转移表,用D触发器和与非门实现。

,C=10,D=11,则

电路的状态方程和输出方程为

18. 某时序机状态图如下图所示。

请用“一对一法”设计其电路解:

19.某时序机状态图如下所示,用“计数器法”设计该电路

解:

若编码为:S0=00 S1=01 S2=11 S3=10:

则

次态方程为:

n

n

n

n

n

n

n

n

Q

Q

KQ

Q

K

Q

KQ

Q

K

Q

2

1

2

1

1

2

2

1

1

1

+

+

=

+

=

+

+

4。