数字逻辑电路总复习

数字逻辑复习题

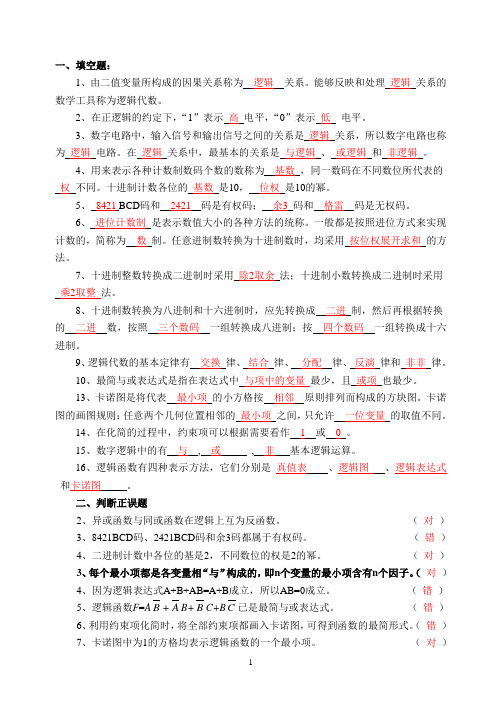

一、填空题:1、由二值变量所构成的因果关系称为逻辑关系。

能够反映和处理逻辑关系的数学工具称为逻辑代数。

2、在正逻辑的约定下,“1”表示高电平,“0”表示低电平。

3、数字电路中,输入信号和输出信号之间的关系是逻辑关系,所以数字电路也称为逻辑电路。

在逻辑关系中,最基本的关系是与逻辑、或逻辑和非逻辑。

4、用来表示各种计数制数码个数的数称为基数,同一数码在不同数位所代表的权不同。

十进制计数各位的基数是10,位权是10的幂。

5、8421 BCD码和2421码是有权码;余3码和格雷码是无权码。

6、进位计数制是表示数值大小的各种方法的统称。

一般都是按照进位方式来实现计数的,简称为数制。

任意进制数转换为十进制数时,均采用按位权展开求和的方法。

7、十进制整数转换成二进制时采用除2取余法;十进制小数转换成二进制时采用乘2取整法。

8、十进制数转换为八进制和十六进制时,应先转换成二进制,然后再根据转换的二进数,按照三个数码一组转换成八进制;按四个数码一组转换成十六进制。

9、逻辑代数的基本定律有交换律、结合律、分配律、反演律和非非律。

10、最简与或表达式是指在表达式中与项中的变量最少,且或项也最少。

13、卡诺图是将代表最小项的小方格按相邻原则排列而构成的方块图。

卡诺图的画图规则:任意两个几何位置相邻的最小项之间,只允许一位变量的取值不同。

14、在化简的过程中,约束项可以根据需要看作1或0。

15、数字逻辑中的有与, 或, 非基本逻辑运算。

16、逻辑函数有四种表示方法,它们分别是真值表、逻辑图、逻辑表达式和卡诺图。

二、判断正误题2、异或函数与同或函数在逻辑上互为反函数。

(对)3、8421BCD码、2421BCD码和余3码都属于有权码。

(错)4、二进制计数中各位的基是2,不同数位的权是2的幂。

(对)3、每个最小项都是各变量相“与”构成的,即n个变量的最小项含有n个因子。

(对)4、因为逻辑表达式A+B+AB=A+B成立,所以AB=0成立。

数字逻辑电路总复习

128

16

4 2 1

二、常用逻辑关系及运算

1. 三种基本逻辑运算:与 、或、非 2. 四种复合逻辑运算: 与非 、或非、与或非、异或 真值表 函数式 逻辑符号

三、逻辑代数的公式和定理

是推演、变换和化简逻辑函数的依据,有些与普通代数相 同,有些则完全不同,要认真加以区别。这些定理中,摩根定 理最为常用。

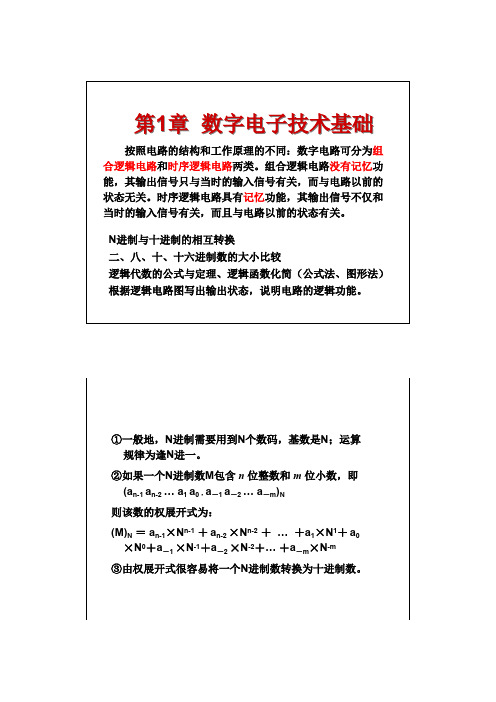

第一章 逻辑代数基础

一、数制和码制 1. 数制:计数方法或计数体制(由基数和位权组成)

种类 十进制

二进制 八进制

基数 09

0 ,1 07

位权 10i

2i 8i

应用 日常

数字电路 计算机程序

备注

2 = 21 8 = 23

十六进制 0 9,A F

16i

计算机程序

16 = 24

各种数制之间的相互转换,特别是十进制→二进制的转换, 要求熟练掌握。

逻辑代数的基本公式 1. 关于常量与变量关系公式

A 0 A (1) A1 A (1’) A 1 1 (2) A 0 0 (2’)

2. 若干定律 交换律:

A B B A (3) A B B A (3’)

( A B) C A ( B C )

2. 码制:常用的 BCD 码有 8421 码、2421 码、5421 码、余 3 码等,其中以 8421 码使用最广泛。

1.十进制数到N进制数的转换 整数部分:除以N看余数 小数部分:乘以N看向整数的进位 2. N进制数转换为十进制数:方法:按权展开 3.基本逻辑和复合逻辑: (1)异或逻辑:特点:相同为0、相异为1 逻辑函数表达式:P = AB=AB+AB (2)同或逻辑:特点:相同为1、相异为0 逻辑函数表达式:P = A⊙ B =AB+AB 异或逻辑与同或逻辑是互非关系:

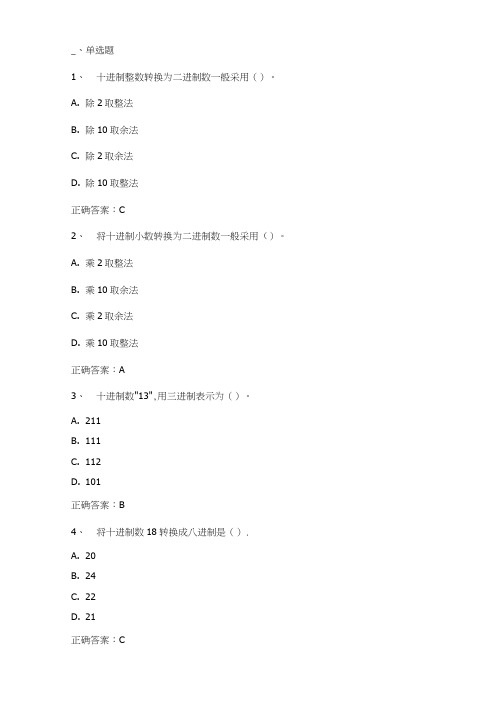

数字逻辑电路复习题与答案

_、单选题1、十进制整数转换为二进制数一般采用()。

A.除2取整法B.除10取余法C.除2取余法D.除10取整法正确答案:C2、将十进制小数转换为二进制数一般采用()。

A.乘2取整法B.乘10取余法C.乘2取余法D.乘10取整法正确答案:A3、十进制数"13",用三进制表示为()。

A.211B.111C.112D.101正确答案:B4、将十进制数18转换成八进制是().A.20B.24C.22D.21正确答案:C5、十进制数25用8421 BCD码表示为()A.10 010100B.0010 0101C.10 101D.10 000101正确答案:B6、以下代码中为恒权码的是()。

A.余3循坏码B右移码C.5211 码D.余3码正确答案:C7、T立八进制数可以用()位二进制数来表示。

A.4B.3C.1D.2正确答案:B&十进制数43用8421BCD码表示为()。

A.10011B.0100 0011C.101011D.1000011正确答案:B9、A+BC=()A.AB+ACB.BCC・(A+B)(A+C)正确答案:C10、4变量逻辑函数的真值表,表中的输入变量的取值应有()种。

A.4B.2C.16D.8正确答案:C11、f 16选1的数据选择器,其选择控制(地址)输入端有()个,数据输入端有16个,输出端有1个。

A.4B.16C.1D.2正确答案:A12、一个译码器若有100个译码输出端,则译码输入端至少有()个。

A.5B.8C.7D.6正确答案:C13、能实现并-串转换的是()。

A.数据选择器B.数据分配器C.译码器D.数值比较器正确答案:A14、欲设计一个3位无符号数乘法器(即3x3),需要6位输入及()位输出信号。

B.6C.4D.5正确答案:B15、4位输入的二逬制译码器,其输出应有()位。

A.4B.1C.8D.16正确答案:D16、对于8线一3线优先编码器,下面说法正确的是()A.有8根输入线,8根输出线B.有8根输入线,3根输出线C.有3根输入线,8根输出线D.有3根输入线,3根输出线正确答案:B17、3线-8线译码电路是()译码器A.八进制B.三进制C.三位二进制D.H-A进制正确答案:C18、实现多输入、单输出逻辑函数,应选()。

数字电路(复习)

②C=1、C=0,即C端为高电平(+VDD)、C端为低电平(0V) 时,TN和TP都具备了导通条件,输入和输出之间相当于开关接通 一样,uO=uI 。

2.三态门电路的输出有高阻态、高电平和低电平3种状态

• 三态门逻辑符号控制端电平的约定

A

1

Y

EN

EN

(a)控制端低电平有效

控制端加低电平信号时,三 态门处于工作状态,Y=A, 加高电平信号时禁止,Y=Z

加法器

能对两个1位二进制数进行相加而求得和及进位的逻辑电 路称为半加器。 能对两个1位二进制数进行相加并考虑低位来的进位,即 相当于3个1位二进制数的相加,求得和及进位的逻辑电路称 为全加器。 实现多位二进制数相加的电路称为加法器。按照进位方 式的不同,加法器分为串行进位加法器和超前进位加法器两 种。串行进位加法器电路简单、但速度较慢,超前进位加法 器速度较快、但电路复杂。 加法器除用来实现两个二进制数相加外,还可用来设计 代码转换电路、二进制减法器和十进制加法器等。

数据分配器

数据分配器的逻辑功能是将1个输入数据传送到 多个输出端中的1个输出端,具体传送到哪一个输出 端,也是由一组选择控制(地址)信号确定。 数据分配器就是带选通控制端即使能端的二进 制译码器。只要在使用中,把二进制译码器的选通 控制端当作数据输入端,二进制代码输入端当作选 择控制端就可以了。 数据分配器经常和数据选择器一起构成数据传 送系统。其主要特点是可以用很少几根线实现多路 数字信息的分时传送。

八进制数

0 1 2 3 4 5 6 7 10 11 12 13 14 15 16 17

十六进制数

0 1 2 3 4 5 6 7 8 9 A B C D E F

门电路 国标符号 曾用符号 美国符号 表达式

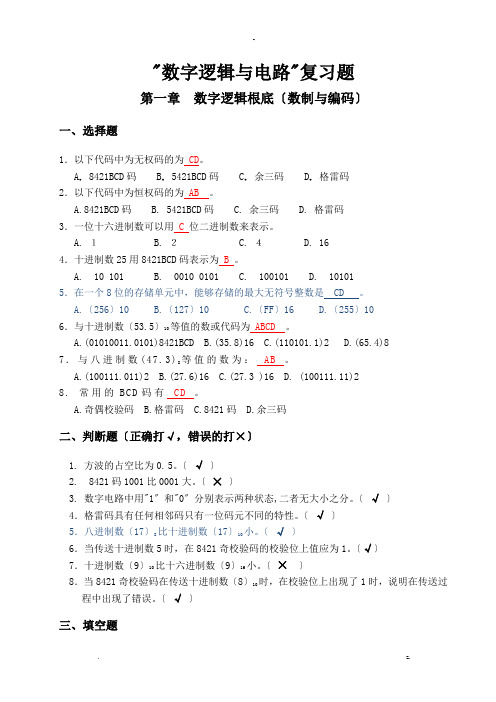

数字逻辑及电路复习题及答案

"数字逻辑与电路"复习题第一章数字逻辑根底〔数制与编码〕一、选择题1.以下代码中为无权码的为 CD。

A. 8421BCD码B. 5421BCD码C.余三码D.格雷码2.以下代码中为恒权码的为 AB 。

A.8421BCD码B. 5421BCD码C. 余三码D. 格雷码3.一位十六进制数可以用 C 位二进制数来表示。

A. 1B. 2C. 4D. 164.十进制数25用8421BCD码表示为 B 。

A. 10 101B. 0010 0101C. 100101D. 101015.在一个8位的存储单元中,能够存储的最大无符号整数是 CD 。

A.〔256〕10B.〔127〕10C.〔FF〕16D.〔255〕10 6.与十进制数〔53.5〕10等值的数或代码为 ABCD 。

A.(01010011.0101)8421BCDB.(35.8)16C.(110101.1)2D.(65.4)87.与八进制数(47.3)8等值的数为:A B 。

A.(100111.011)2B.(27.6)16C.(27.3 )16D. (100111.11)28.常用的BC D码有C D 。

A.奇偶校验码B.格雷码C.8421码D.余三码二、判断题〔正确打√,错误的打×〕1. 方波的占空比为0.5。

〔√〕2. 8421码1001比0001大。

〔×〕3. 数字电路中用"1〞和"0〞分别表示两种状态,二者无大小之分。

〔√〕4.格雷码具有任何相邻码只有一位码元不同的特性。

〔√〕5.八进制数〔17〕8比十进制数〔17〕10小。

〔√〕6.当传送十进制数5时,在8421奇校验码的校验位上值应为1。

〔√〕7.十进制数〔9〕10比十六进制数〔9〕16小。

〔×〕8.当8421奇校验码在传送十进制数〔8〕10时,在校验位上出现了1时,说明在传送过程中出现了错误。

〔√〕三、填空题1.数字信号的特点是在时间上和幅值上都是断续变化的,其高电平和低电平常用 1和 0来表示。

数字逻辑期末复习资料

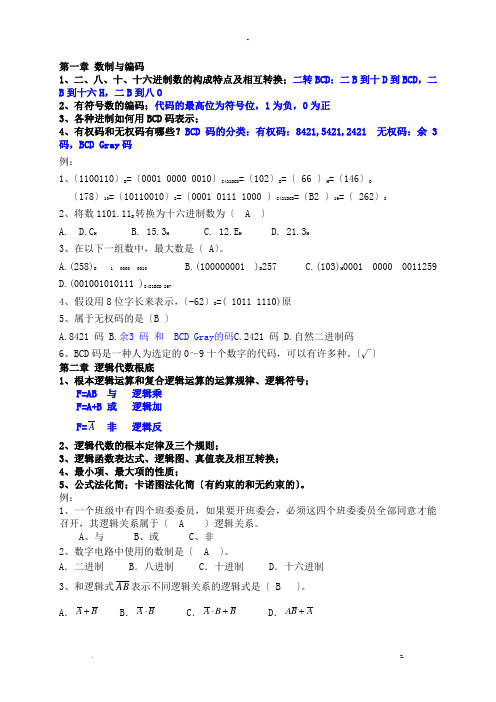

第一章 数制与编码1、二、八、十、十六进制数的构成特点及相互转换;二转BCD :二B 到十D 到BCD ,二B 到十六H ,二B 到八O2、有符号数的编码;代码的最高位为符号位,1为负,0为正3、各种进制如何用BCD 码表示;4、有权码和无权码有哪些?BCD 码的分类:有权码:8421,5421,2421 无权码:余3码,BCD Gray 码 例:1、〔1100110〕B =〔0001 0000 0010〕8421BCD =〔102〕D =〔 66 〕H =〔146〕O〔178〕10=〔10110010〕2=〔0001 0111 1000 〕8421BCD =〔B2 〕16=〔 262〕8 2、将数1101.11B 转换为十六进制数为〔 A 〕A. D.C HB. 15.3HC. 12.E HD. 21.3H 3、在以下一组数中,最大数是〔 A 〕。

A.(258)D1 0000 0010B.(100000001 )B 257C.(103)H 0001 0000 0011259D.(001001010111 )8421BCD 2574、假设用8位字长来表示,〔-62〕D =( 1011 1110)原5、属于无权码的是〔B 〕A.8421 码B.余3 码 和 BCD Gray 的码C.2421 码D.自然二进制码 6、BCD 码是一种人为选定的0~9十个数字的代码,可以有许多种。

〔√〕 第二章 逻辑代数根底1、根本逻辑运算和复合逻辑运算的运算规律、逻辑符号;F=AB 与 逻辑乘 F=A+B 或 逻辑加F=A 非 逻辑反2、逻辑代数的根本定律及三个规则;3、逻辑函数表达式、逻辑图、真值表及相互转换;4、最小项、最大项的性质;5、公式法化简;卡诺图法化简〔有约束的和无约束的〕。

例:1、一个班级中有四个班委委员,如果要开班委会,必须这四个班委委员全部同意才能召开,其逻辑关系属于〔 A 〕逻辑关系。

A 、与B 、或C 、非 2、数字电路中使用的数制是〔 A 〕。

数字电路逻辑门知识点总结

数字电路逻辑门知识点总结一、基本概念1.1 逻辑门的定义逻辑门是数字电路中的基本组成元件,它们用于执行逻辑运算。

逻辑门有不同的类型,比如AND门、OR门、NOT门等。

1.2 逻辑门的功能不同类型的逻辑门执行不同的逻辑运算。

比如,AND门执行逻辑乘法运算,OR门执行逻辑加法运算,而NOT门执行逻辑取反运算。

1.3 逻辑门的符号每种类型的逻辑门都有自己的标准符号,用于表示其在电路图中的位置和连接方式。

比如,AND门的标准符号是一个带有圆点的直线,表示其执行逻辑与运算。

1.4 逻辑门的真值表每种类型的逻辑门都有一个对应的真值表,用于描述其输入和输出之间的关系。

真值表通常包括所有可能的输入组合,以及其对应的输出。

二、基本逻辑门2.1 AND门AND门是逻辑与门的简称,它有两个输入和一个输出。

当所有输入均为高电平时,输出为高电平;否则,输出为低电平。

2.2 OR门OR门是逻辑或门的简称,它同样有两个输入和一个输出。

当任意一个输入为高电平时,输出为高电平;否则,输出为低电平。

2.3 NOT门NOT门是逻辑非门的简称,它只有一个输入和一个输出。

当输入为高电平时,输出为低电平;当输入为低电平时,输出为高电平。

2.4 XOR门XOR门是独占或门的简称,它同样有两个输入和一个输出。

当任一输入为高电平,另一个输入为低电平时,输出为高电平;否则,输出为低电平。

2.5 NAND门NAND门是与非门的简称,它同样有两个输入和一个输出。

当所有输入均为高电平时,输出为低电平;否则,输出为高电平。

2.6 NOR门NOR门是或非门的简称,它同样有两个输入和一个输出。

当任意一个输入为高电平时,输出为低电平;否则,输出为高电平。

2.7 XNOR门XNOR门是独占或非门的简称,它同样有两个输入和一个输出。

当两个输入相等时,输出为高电平;否则,输出为低电平。

三、逻辑门的组合3.1 逻辑门的串联多个逻辑门可以串联在一起,形成更复杂的逻辑功能。

数字逻辑电路考试复习

作业题 P70 题1.11(b)、(d)、(f) 题1.12 ⑴、⑶ P71 题1.13 ⑵ 题1.14 ⑵、⑷ 题1.15 ⑶、⑹

(1-5)

作业题 P71 题1.16(a) P72 题1.17 画出[题1.4] ⑴中函数的逻 辑图

(1-6)

作业题 P135 题2.2 P136 题2.3(a)

Y1 A B 0 A B

Y2 A B

Y3 AB 0 (AB 2-10)

作业题 P139 题2.13 P140 题2.15 P141 题2.16

(2-11)

一、填空题 1、使用(三态门 )可以实现总线结构;使用(OC )门可 实现“线与”逻辑。 2、TTL门输入端口为 “与” 逻辑关系时,多余的 输入端可(悬空 )处理;TTL门输入端口为 “或” 逻 辑关系时,多余的输入端应接(低)电平;CMOS门输 入端口为“与”逻辑关系时,多余的输入端应接(高 ) 电平,具有“或”逻辑端口的CMOS门多余的输入端 应接( 低)电平;即CMOS门的输入端不允许( 悬空)。 3、TTL与非门的电路结构由(输入级)、(中间放大级) 和(输出级 )三部分组成。

5、8个输入的编码器,按二进制编码,其输出的编码 有( 3 ) 位。 6、3个输入的译码器,最多可译码出( 8 ) 路输出。

(3-19)

二、单项选择题 1、在二进制译码器中,若输入有4位代码,则输出有 ( D )信号。 A、 2 个 B、 4个 C、 8个 D、16个 2、若在编码器中有50个编码对象,则要求输出二进 制代码位数为( B )位。 A、5 B 、6 C、10 D、50 3、在在大多数情况下,对于译码器而言( A )。 A、其输入端数目少于输出端数目 B、其输入端数目多于输出端数目 C、其输入端数目与输出端数目几乎相同

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第三章 组合逻辑电路

常用的组合逻辑电路及中规模集成器件 数据选择器: 数据选择器: 74153双4选1数据选择器; 双 选 数据选择器 数据选择器; 用数据选择器设计逻辑电路; 用数据选择器设计逻辑电路; 数据选择器设计3变量逻辑函数 变量逻辑函数。 用8选1数据选择器设计 变量逻辑函数、4变量逻辑函数。 选 数据选择器设计 变量逻辑函数、 变量逻辑函数 利用数据选择器设计组合逻辑电路

17

第五章 时序逻辑电路

对于Q 找出 1由1→0的小方块 找出Q 对于 的小方块 根据 画出卡诺图, 画出卡诺图,其他小方块状态不变

n+1 2 ,

异步十进制计数器

18

第五章 时序逻辑电路

计数器 同步计数器 同步二进制计数器:加 同步二进制计数器 加、减、可逆; 可逆; 同步十进制计数器:加、减 同步十进制计数器: 集成同步十进制加法计数器74160,集成同步 , 集成同步十进制加法计数器 4位二进制计数器 位二进制计数器74161。 位二进制计数器 。 异步计数器 异步二进制计数器:加 异步二进制计数器 加、减、可逆; 可逆; 异步十进制计数器

21

第五章 时序逻辑电路

例子:整体置数将两个同步十进制计数器74160构成 例子:整体置数将两个同步十进制计数器 同步十进制计数器 构成 29进制计数器 进制计数器

进位输出

22

第六章 脉冲波形的产生及整形

施密特触发器、 自激震荡器的基本概念。 施密特触发器、单稳态触发器 、自激震荡器的基本概念。 555定时器构成施密特、单稳态、多谐振荡器的连接方 定时器构成施密特、单稳态、 定时器构成施密特 画电路的工作波形图。 式 ,画电路的工作波形图。

9

第三章 组合逻辑电路

常用的组合逻辑电路及中规模集成器件 译码器: 译码器: 74LS138(3线-8线)二进制译码器; ( 线 线 二进制译码器; 各个控制信号的功能; 各个控制信号的功能; 最小项译码器的概念; 最小项译码器的概念; 74LS138译码器的应用,如函数发生器; 译码器的应用,如函数发生器; 译码器的应用 显示译码器的概念; 显示译码器的概念; BCD—七段显示译码器 七段显示译码器7448,各控制信号的功能。 七段显示译码器 ,各控制信号的功能。

5

第二章 晶体管开关及门电路

双极性三极管的开关特性 截止区 放大区 饱和区 饱和区特征:发射结和集电结都正偏。 饱和区特征:发射结和集电结都正偏。集电极 和发射极呈低阻抗。 和发射极呈低阻抗。

ic ≠ β ib Vbe > 0, Vbc > 0

硅: VCE≈0.3V 锗: VCE≈0.1V

6

第二章 晶体管开关及门电路

15

第五章 时序逻辑电路

CP=1: : 有时钟信号; 有时钟信号; CP=0: : 没有时钟信号。 没有时钟信号。 驱动方程

次态方程

输出方程

16

第五章 时序逻辑电路

对于Q 对于 、Q 找出Q 找出 0由1→0的小方块 的小方块 根据

n+1 1 n+1 3

画出卡诺图, 画出卡诺图,其他小方块 状态不变

数字逻辑电路

天津工业大学信息学院 缪竟鸿 Email:miaojinghong@ :

1

第一章 数学逻辑的基础知识

数制和码制 十进制、 十进制、二进制和十六进制之间的转换 BCD码 码 原码、补码及反码 原码、 逻辑代数的基本公式和常用公式 逻辑代数的基本定理 代入定理 反演定理 对偶定理

11

第四章 触发器

触发器的两个基本特点 基本RS触发器 基本 触发器 或非门构成的基本RS触发器 或非门构成的基本 触发器 与非门构成的基本RS触发器 与非门构成的基本 触发器 时钟触发器 各种功能的时钟触发器: 、 、 、 各种功能的时钟触发器:RS、JK、D、T 触发方式:电平触发(同步式)、边沿触发、主从触发。 触发方式:电平触发(同步式)、边沿触发、主从触发。 )、边沿触发

23

第五章 时序逻辑电路

Q2=0,选择器工作; ,选择器工作; Q2=1,选择器封锁, ,选择器封锁, 输出低电平。 输出低电平。

Y

24

模拟试题

(一)求最简“与或”表达式 求最简“与或”

25

模拟试题

(二)试画出用与非门和反相器实现的下列逻辑函数 表达式

26

模拟试题

(三)根据以给的条件,画出波形图 根据以给的条件,

29

模拟试题

作如图的连接, (六)将74161作如图的连接,试通过分析,画出完整的 作如图的连接 试通过分析, 状态图。 状态图。

30

模拟试题

(七)分析如图所示电路的逻辑功能。 分析如图所示电路的逻辑功能。

31

第三章 组合逻辑电路

此问题是一个优先编码问题 74LS148是8线-3线优先编码 是 线 线优先编码 只用四个输入即可, 器,只用四个输入即可,这 里用7—4,低4位不管;也可 位不管; 里用 , 位不管 以用低四位,但是其他高位 以用低四位, 必须接1(表示无输入信号); 必须接 (表示无输入信号); 求得: 求得:

32

19

第五章 时序逻辑电路

任意进制计数器的构成方法: 任意进制计数器的构成方法: 置零法、置数法。 置零法、置数法。用74160或74161构成任意进 或 构成任意进 制计数器。 制计数器。 RD 异步置零端; 异步置零端; LD 预置数控制端 M>N 情况 M<N 情况(并行进位方式、串行进位方式) 情况(并行进位方式、串行进位方式)

27

模拟试题

(四)实现逻辑函数 和门电路产生如下的逻辑函数的逻辑图。 (1)用74LS138和门电路产生如下的逻辑函数的逻辑图。 ) 和门电路产生如下的逻辑函数的逻辑图

数据选择器产生逻辑函数。 (2)用8选1数据选择器产生逻辑函数。 ) 选 数据选择器产生逻辑函数

28

模拟试题

状态图和Y的波形 (五)通过分析图示电路,画出Q2、Q1、Q0状态图和 的波形 通过分析图示电路,画出 触发器是上升沿触发,波形从Q 时画起)。 (触发器是上升沿触发,波形从 2Q1Q0=000时画起)。 时画起

根据给定条件,画出触发器输出波形图。 根据给定条件,画出触发器输出波形图。

12

第四章 触发器

触发器分类图

13

第四章 触发器

各种触发器表达式的比较14 Nhomakorabea第五章 时序逻辑电路

时序逻辑电路的分析方法 同步时序逻辑电路的分析方法 异步时序逻辑电路的分析方法

求次态; 求次态; 状态代入法; 状态代入法; 卡诺图法

2

第一章 数学逻辑的基础知识

逻辑代数的表示方法 逻辑表达式 真值表 逻辑图 卡诺图 逻辑代数的两种标准形式 最小项形式 最大项形式

3

第一章 数学逻辑的基础知识

逻辑函数的化简 公式法化简 卡诺图化简

习题

4

第二章 晶体管开关及门电路

二极管的开关特性 硅: VT≈0.7V 锗:VT≈0.2V 反向恢复时间: 反向恢复时间:二极管由正向导通转为反向截止所需的 过渡时间。 过渡时间。

20

第五章 时序逻辑电路

例子:整体置零将两个同步十进制计数器74160构成 例子:整体置零将两个同步十进制计数器 同步十进制计数器 构成 29进制计数器 进制计数器 片(II)不出现 不出现 1001状态, 状态, 状态 CO无进位输 无进位输 出,门G1输 输 出脉冲极窄, 出脉冲极窄, 不适合作进位 信号。 信号。进位由 28译码输出。 译码输出。 译码输出

NPN硅三极管共发射极电路三态条件和特性 硅三极管共发射极电路三态条件和特性

7

第二章 晶体管开关及门电路

二级管门电路 与门 或门 三级管门电路 非门 TTL门电路 门电路 与非门 三态门 CMOS门电路 门电路 CMOS反相器 反相器

8

第三章 组合逻辑电路

组合逻辑电路的分析和设计方法 组合逻辑电路的分析方法 组合逻辑电路的设计方法 常用的组合逻辑电路及中规模集成器件 加法器:全加器 加法器 全加器74LS283 全加器 编码器:优先编码器(8线-3线优先编码器,注意: 编码器:优先编码器( 线 线优先编码器,注意: 线优先编码器 输入、输出是原码还是反码) 输入、输出是原码还是反码)