DDR系列设计规范“连接器技术标准

DDR布线规范

DDR布线规范1、DDR3管脚定义》CK/CK# 全局差分时钟,所有控制和地址输⼊信号在CK上升沿和CK#的下降沿交叉处被采样,输出数据选通(DQS、DQS#)参考与CK 和CK#的交叉点。

》CKE为时钟使能信号,使能(⾼)和禁⽌(低)内电路和DRAM上的时钟。

由DDR3 SDRAM配置和操作模式决定特定电路被使能和禁⽌。

CKE为低时,提供预充电和⾃刷新操作(所有Bank都处于空闲),或有效掉电(在任何Bank⾥的⾏有效)。

CKE与掉电状态的进⼊、退出以及⾃刷新的进⼊同步。

CKE与⾃刷新的退出异步,输⼊Buffer(除了CKE、CK#、RESET#和ODT)在掉电期间被禁⽌。

输⼊Buffer(除了CKE和RESET#)在⾃刷新期间被禁⽌。

CKE的参考值是VREFCA。

》CS#为⽚选信号,使能(低)和禁⽌(⾼)命令译码,⼤部分CS#为⾼时,所有命令被屏蔽、CS#提供了多Bank系统的Bank选择功能,CS#是命令代码的⼀部分,CS#的参考值是VREFCA。

》ODT⽚上终端使能。

ODT使能(⾼)和禁⽌(低)⽚内终端电阻,在正常操作使能时,ODT仅对下⾯的引脚有效:DQ[7:0]、DQS、DQS#和DM。

如果通过LOAD MODE命令禁⽌,OTD输⼊被忽略。

OTD的参考值是VREFCA。

》BA0、BA1、BA2为BANK地址输⼊,⽤来确定当前的命令操作对哪个BANK有效。

BA[2:0]定义在LOAD MODE命令器件哪个模式(MR0、MR1、MR2)被装载,BA[2:0]的参考值是VREFCA.》A0~A9、A10/AP、A11、A12/BC#、A13为地址总线,为有效命令提供⾏地址,同时为读、写命令提供列地址和⾃动预充电位(A10),以便从某个Bank的内存阵列⾥选出⼀个位置。

LOAD MODE命令器件,地址输⼊提供⼀个操作码。

地址输⼊的参考值是VRECA。

A12/BC#是在模式寄存器(MR)使能时,A12在读和写命令期间被采样,已决定burst chop(on-the-fly)是否被执⾏(HIGH=BL8执⾏burst chop)或者LOW-BC4不执⾏burst chop。

连接器基本技术要求1

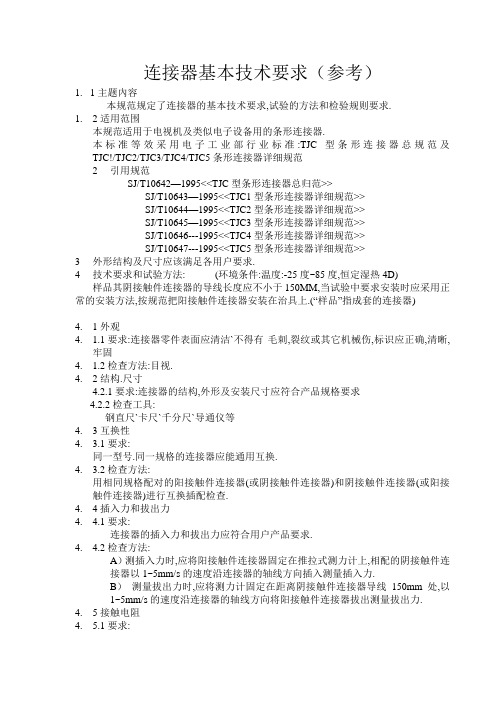

连接器基本技术要求(参考)1.1主题內容本规范规定了连接器的基本技术要求,试验的方法和检验规则要求.1.2适用范围本规范适用于电视机及类似电子设备用的条形连接器.本标准等效采用电子工业部行业标准:TJC型条形连接器总规范及TJC!/TJC2/TJC3/TJC4/TJC5条形连接器详细规范2引用规范SJ/T10642—1995<<TJC型条形连接器总归范>>SJ/T10643—1995<<TJC1型条形连接器详细规范>>SJ/T10644—1995<<TJC2型条形连接器详细规范>>SJ/T10645—1995<<TJC3型条形连接器详细规范>>SJ/T10646---1995<<TJC4型条形连接器详细规范>>SJ/T10647---1995<<TJC5型条形连接器详细规范>>3 外形结构及尺寸应该满足各用户要求.4 技术要求和试验方法: (环境条件:温度:-25度~85度,恒定湿热4D)样品其阴接触件连接器的导线长度应不小于150MM,当试验中要求安装时应采用正常的安装方法,按规范把阳接触件连接器安装在治具上.(“样品”指成套的连接器)4.1外观4. 1.1要求:连接器零件表面应清洁`不得有毛刺,裂纹或其它机械伤,标识应正确,清晰,牢固4. 1.2检查方法:目视.4.2结构.尺寸4.2.1要求:连接器的结构,外形及安装尺寸应符合产品规格要求4.2.2检查工具:钢直尺`卡尺`千分尺`导通仪等4.3互换性4. 3.1要求:同一型号.同一规格的连接器应能通用互换.4. 3.2检查方法:用相同规格配对的阳接触件连接器(或阴接触件连接器)和阴接触件连接器(或阳接触件连接器)进行互换插配检查.4.4插入力和拔出力4. 4.1要求:连接器的插入力和拔出力应符合用户产品要求.4. 4.2检查方法:A)测插入力时,应将阳接触件连接器固定在推拉式测力计上,相配的阴接触件连接器以1~5mm/s的速度沿连接器的轴线方向插入测量插入力.B)测量拔出力时,应将测力计固定在距离阴接触件连接器导线150mm处,以1~5mm/s的速度沿连接器的轴线方向将阳接触件连接器拔出测量拔出力.4.5接触电阻4. 5.1要求:连接器每一接触对间的接触电阻初始值应不大于0.01欧姆,寿命试验后应不大于0.02欧姆4. 5.2检查方法:试验时插合连接器,在测量两端负载DC6±1V/1A的电压,接触电阻值应从测量值中减去所用导线的电阻值.4.6绝缘电阻.4. 6.1要求:连接器相邻接触件间的初始绝缘电阻和恒定湿热试验后的绝缘电阻都≥500MΩ(测量绝缘电阻时必须读取稳定的数值,如果1min内没有稳定值,应在报告中注明.)4. 6.2测试方法:a在最小间距的相邻引出端之间加上规定试验电压500±50V/DC;b测量时应把连接器和导线置于正常工作位置上.4.7耐电压4.7.1要求:连接器相邻接触件间应能承受规定的试验电压的作用而无闪络、飞弧和击穿,漏电流不超最大值.4.7.2测验方法:a将样品的所有引出端交错连接形成两组,每组内不许互相邻近的接触件(触点),样品应依次承受规定的试验电压;b引出端排两排或两排以上时,为了测量每对相邻引出端之间的耐电压,必须组成两种排列的两组.4.8接触件的固定性4.8.1要求:每一接触件在规定的拉力作用下不应从基座中脱出,以评价接触件固定机构耐受正常使用可能遇到的轴向机械应力的能力.4.8.2试验方法:a试验时固定阴(阳)接触连接器,把测力计固定在距离连接器导线150mm处,在连器轴线方向上施加规定的拉力,力的保持时间为5S;b试验接触件数目:每个连接器3个,不足3个接触件时全部测量;c试验所用导线的压接强度应大于接触件的固定性.4.9抗张强度4.9.1要求:连接器每一接触件与导线压接连接的抗张强度应不小于规定;4.9.2试验方法:a在试验装置夹头中夹紧试验样品尾部施加张力,应注意不要压伤接触件或端接件的压接筒;b要使张力沿着压接连接的轴线方向上;c张力试验机的头部应以25mm/min至50mm/min的速度平稳地移动;单独试验每一试验样品,直到一端的导体被拉脱或导线被拉断为止.(每个连接器测3个接触件,不足3个接件时全部测量).4.10可焊性4.10.1要求:连接器接端应容易被熔融焊料湿润,沾锡面积应占浸入面积的90%以上4.10.2试验条件:温度:235±5℃,时间:2±0.5S4.11耐焊接热4.11.1要求:连接器应能承受焊接试验的影响而无损伤4 11.2条件温度:260±5℃,时间;5±1S.4.12温度急变4 .12.1要求:连接器经受温度急变试验后应无影响正常操作的损伤.4. 12.2试验条`件:高温:+85℃,低温:–25℃,5次循环. 鉴定检验:25次循环;接触电阻≤0.02Ω4.13高温4 13.1要求:连接器应能承受规定的高温试验而无影响正常操作的损伤.4.13.2试验条件:温度:+85℃时间:4小时鉴定检验`:240小时4.14恒定湿热4.14.1连接器应能承受规定的严酷度下进行的恒定湿热试验.试验后绝缘电阻耐压应`符合规定,并无影响正常操作的损伤.4.14.2试验条件:时间:4d 鉴定检验:10d 绝缘电阻≥500ΜΩ耐压:1000V(500HZ)4.15振动4.15.1要求:连接器应能承受规定的振动试验,试验后应无影响正常操作的损伤.4.15.2试验方法:a,试验时插合连接器并模拟正常工作状态,安装在印制板上;b,振频为10~500HZ, 振幅值为0.35mm(加速度为50m/S)、每一轴线扫频循环次数10次.4.16机械寿命4.16.1要求:连接器应能承受规定的机械寿命试验,试验后无影响正常操作的损伤.接触电阻应符合规定.带锁紧结构的连接器其紧锁结构应无影响正常操作损伤.4. 16.2方法:插拔50次. 接触电阻≤0.02Ω4.17盐雾4.17.1要求:连接器应能经受规定的盐雾试验的作用,试验后应无露出底金属的严重锈蚀.(注:使用预镀好的成材,其落料面允许有不影响其性能要求的轻微腐蚀.)4.17.2试验条件:样品放在喷雾机内,保持15°-30°斜度不可相互接触;浓度5±1%生理盐水溶液,压缩空气力(1公斤/平方厘米);盐水喷雾量(1-2毫升/80平方厘米/小时);压力桶温度47±1℃;盐水桶温度(和试验室温度)35±1℃;喷雾48小时(规定时间)后,取出样品用水洗净,烘干后检测接触阻抗,需符合规定(接触电阻≤0.02Ω).判定方法:起泡、裂痕等使用标准难以判断者,可用附有标尺的放大镜判定,或由买卖双方事先所协定的方法判定之。

连接器设计规范

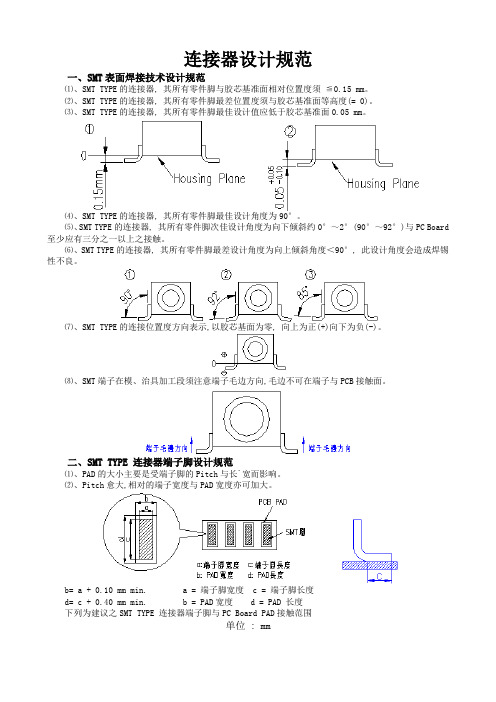

连接器设计规范一、SMT表面焊接技术设计规范⑴、SMT TYPE的连接器, 其所有零件脚与胶芯基准面相对位置度须≦0.15 mm。

⑵、SMT TYPE的连接器, 其所有零件脚最差位置度须与胶芯基准面等高度(= 0)。

⑶、SMT TYPE的连接器, 其所有零件脚最佳设计值应低于胶芯基准面0.05 mm。

⑷、SMT TYPE的连接器, 其所有零件脚最佳设计角度为90°。

⑸、SMT TYPE的连接器, 其所有零件脚次佳设计角度为向下倾斜约0°~2°(90°~92°)与PC Board 至少应有三分之一以上之接触。

⑹、SMT TYPE的连接器, 其所有零件脚最差设计角度为向上倾斜角度<90°, 此设计角度会造成焊锡性不良。

⑺、SMT TYPE的连接位置度方向表示,以胶芯基面为零, 向上为正(+)向下为负(-)。

⑻、SMT端子在模、治具加工段须注意端子毛边方向,毛边不可在端子与PCB接触面。

二、SMT TYPE 连接器端子脚设计规范⑴、PAD的大小主要是受端子脚的Pitch与长`宽而影响。

⑵、Pitch愈大,相对的端子宽度与PAD宽度亦可加大。

b= a + 0.10 mm min. a = 端子脚宽度 c = 端子脚长度d= c + 0.40 mm min. b = PAD宽度 d = PAD 长度下列为建议之SMT TYPE 连接器端子脚与PC Board PAD接触范围单位 : mmPitch 0.50 mm 0.80 mm 1.0 mm 1.27 mm 2.0 mm 2.54 mma 0.20 0.25 0.40 0.40 0.60 0.60b 0.30 0.50 0.60 0.80 1.0 1.20c c c c c c cd c + 0.40 c + 0.40 c + 0.40 c + 0.40c +0.40c + 0.40e 0.20 0.30 0.40 0.47 1.0 1.34a=端子脚宽度;长度;e=PAD与PAD间之距离三、平整度设计建议规范(1)、SMT TYPE的连接器, 其所有零件脚的相对高低位置视为平整度,一般要求为0.10mmMax.(2)、平整度表示方式有下图所列几种方式;对SMT产品标准标示:①、端子间平整度②、端子与胶芯基准面位置度。

DDR布线规则与过程

DDR布线规则与过程DDR(Double Data Rate)是一种高速数据传输技术,广泛应用于计算机内存和图形显示等高性能系统中。

DDR布线规则是为了确保高速信号传输的稳定性和可靠性而制定的一系列设计准则和规定。

本文将详细介绍DDR布线规则及其过程。

一、DDR布线规则的重要性DDR技术的高速性质意味着信号传输时间短,信号噪声和衰减问题更加严重。

因此,DDR布线规则的设计是十分关键的,可以有效地降低信号间干扰、串扰、反射等问题的发生,提高系统的稳定性和可靠性。

二、DDR布线规则的要求1.电源稳定性:要求供电电源电压稳定,电源噪声小。

这可以通过良好的电源布线和滤波电容选择来实现。

2.信号路径长度匹配:DDR数据总线的信号路径要尽可能保持长度一致,以确保数据到达目标时的同步性。

为了实现这一点,可以通过合理的排布布线,尽量减少信号的走向差距。

3.数据总线的分层:DDR需要同时传输数据和控制信号,为了减少信号间的干扰和串扰,可以将数据总线、地址总线和控制总线进行分层布线。

4.阻抗匹配:DDR布线需要保证布线阻抗与驱动器输出阻抗和信号链路阻抗匹配,这可以通过合理选择布线宽度和参数来实现。

一般DDR总线要求的阻抗为50欧姆。

5.信号噪声和干扰控制:DDR信号传输速率较高,因此对信号噪声和干扰的要求也比较高。

可以通过地线的合理设计和布线的分隔来降低信号之间的干扰和串扰。

6.信号层间过渡:DDR布线需要在信号层之间进行适当的过渡,以保证信号在不同层之间的传输质量。

三、DDR布线规则的过程1.系统规划:根据设计要求和系统需求进行布线规划。

包括信号的传输速率、总线宽度、电源供应,以及寄存器、驱动器和接收器等元器件的选择。

2.PCB布局:设计合理的PCB布局,合理安排器件和信号线的位置,减少信号线走向差距。

可以使用CAD软件进行布局,避免布线时出现冲突。

3.信号层划定:根据信号层的需要,对PCB进行分层划定。

数据总线、地址总线和控制总线等可以分层进行布线,以减少干扰和串扰。

DDR硬件设计要点

DDR硬件设计要点C、用于匹配的电压VTT(Tracking Termination Voltage)VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。

DDR的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。

如果使用VTT,则VTT的电流要求是比较大的,所以需要走线使用铜皮铺过去。

并且VTT要求电源即可以吸电流,又可以灌电流才可以。

一般情况下可以使用专门为DDR设计的产生VTT 的电源芯片来满足要求。

而且,每个拉到VTT的电阻旁一般放一个10Nf~100nF的电容,整个VTT电路上需要有uF级大电容进行储能。

在华为的设计中,在使用DDR颗粒的情况下,已经基本全部不使用VTT电源,全部采用电阻上下拉的戴维南匹配,只有在使用内存条的情况下才使用VTT电源。

一般情况下,DDR的数据线都是一驱一的拓扑结构,且DDR2和DDR3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到较好的信号质量。

DDR2的地址和控制信号线如果是多负载的情况下,会有一驱多,并且内部没有ODT,其拓扑结构为走T型的结构,所以常常需要使用VTT进行信号质量的匹配控制。

DDR3可以采用Fly-by 方式走线:一个DDR3设计案例,来分析对比采用高阻抗负载走线和采用主线和负载走线同阻抗两种情况的差异。

如上图,Case1采用的是从内层控制器到各个SDRAM均为50ohm的阻抗设计。

Case2则采用了主线40ohm,负载线60ohm的设计。

对此通过仿真工具进行对比分析。

从以上仿真波形可以看出,使用较高阻抗负载走线的Case2在信号质量上明显优于分支主线都采用同一种阻抗的Case1设计。

而且对靠近驱动端的负载影响最大,远离驱动端的最末端的负载影响较小。

这个正是前面所分析到的,负载的分布电容导致了负载线部分的阻抗降低,如果采用主线和负载线同阻抗设计,反而导致了阻抗不连续的发生。

把负载走线设计为较高的阻抗,用于平衡负载引入的分布电容,从而可以达到整条走线阻抗平衡的目的。

DDR2走线规则

DDR2走线规则叠层设置:1、对于同一组数据线及其对应的DQ STROBE线,如DQ[7:0]、DM0与DQS0、DQS0#,应布在同一层,以减小信号skew。

2、DDR2信号线的参考平面最好是选择地平面(尤其是时钟线),如果基于成本考虑,不得不选用电源层作为参考面,则DDR2供电电源平面需包围整个DDR2走线范围,且边缘要留有余量,电源与地平面间的阻抗在整个带宽范围内要足够低。

线长匹配:1、走线增加一个过孔,大概相当于增加了90mil的传输线长度。

2、对于走线长度应把封装内部引线长度计算在内。

3、各信号线的长度匹配如下表:(控制线:CS、CKE、ODT;命令线:Address、Bank Address、RA S、CAS、WE;数据线:DQ、DM)4、时钟信号差分对的长度差应控制在5mil以内。

5、在能够满足布线空间的情况下,走线长度越短越好,一般控制在5000mil以内,可以以时钟线作为参考线。

串扰:1、对于蛇行走线,各线段之间的间距应至少为走线宽度的两倍(边沿到边沿)。

2、DDR2信号线与非DDR2信号线之间的间距应大于25mil。

3、时钟、DQS等差分线与其它DDR2信号线的间距应大于20mil。

4、同一组命令线,同一组控制线或同一组数据线间的走线间距应大于走线宽度1.5倍(最好2倍以上),而不同组间的信号线间距应大于走线宽度的2倍(最好3倍以上)。

5、在扇出线区域,由于空间限制,不能满足走线宽度和间距要求时,可适当减小走线宽度及减小走线间距,但该扇出线长度应小于500mil。

6、扇出线过孔应尽量靠近焊盘,如有可能,最好打焊盘孔。

7、每条信号线的过孔数最好不要超过两个。

8、VREF参考电压线要有足够低的阻抗,且与其它DDR2信号线的间距大于25mil。

阻抗匹配:1、DDR2 800信号走线单端阻抗应设置成50Ω2、对于控制命令线、时钟线要进行阻抗匹配,可采用源端串联匹配或末端并联匹配。

(源端匹配具有较小的驱动功率,但上升沿时间是末端匹配的两倍,且一般驱动器的HI和LO驱动电阻不一样,较难得到精确的匹配阻值,源端匹配一般只适合于点对点拓扑)。

连接器规范

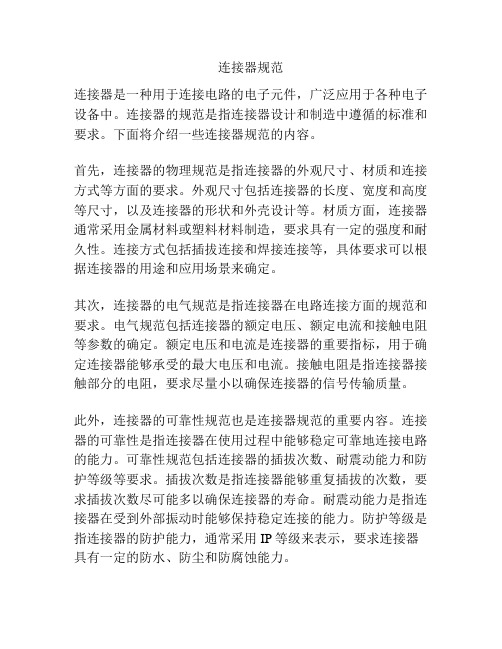

连接器规范连接器是一种用于连接电路的电子元件,广泛应用于各种电子设备中。

连接器的规范是指连接器设计和制造中遵循的标准和要求。

下面将介绍一些连接器规范的内容。

首先,连接器的物理规范是指连接器的外观尺寸、材质和连接方式等方面的要求。

外观尺寸包括连接器的长度、宽度和高度等尺寸,以及连接器的形状和外壳设计等。

材质方面,连接器通常采用金属材料或塑料材料制造,要求具有一定的强度和耐久性。

连接方式包括插拔连接和焊接连接等,具体要求可以根据连接器的用途和应用场景来确定。

其次,连接器的电气规范是指连接器在电路连接方面的规范和要求。

电气规范包括连接器的额定电压、额定电流和接触电阻等参数的确定。

额定电压和电流是连接器的重要指标,用于确定连接器能够承受的最大电压和电流。

接触电阻是指连接器接触部分的电阻,要求尽量小以确保连接器的信号传输质量。

此外,连接器的可靠性规范也是连接器规范的重要内容。

连接器的可靠性是指连接器在使用过程中能够稳定可靠地连接电路的能力。

可靠性规范包括连接器的插拔次数、耐震动能力和防护等级等要求。

插拔次数是指连接器能够重复插拔的次数,要求插拔次数尽可能多以确保连接器的寿命。

耐震动能力是指连接器在受到外部振动时能够保持稳定连接的能力。

防护等级是指连接器的防护能力,通常采用IP等级来表示,要求连接器具有一定的防水、防尘和防腐蚀能力。

最后,连接器的环境规范是指连接器在不同环境条件下使用的要求。

环境规范包括连接器的工作温度范围、湿度范围和抗腐蚀能力等要求。

工作温度范围是指连接器可以正常工作的温度范围,通常要求连接器在-40℃至+85℃的温度范围内正常工作。

湿度范围是指连接器可以正常工作的湿度范围,通常要求连接器在30%至90%的相对湿度范围内正常工作。

抗腐蚀能力是指连接器抵抗腐蚀的能力,要求连接器具有一定的抗腐蚀能力以应对不同的使用环境。

总之,连接器的规范是连接器设计和制造中遵循的标准和要求,包括物理规范、电气规范、可靠性规范和环境规范等方面的内容。

DDR3的相关设计规范

DDR3的相关设计规范DDR3是一种常见的电子产品中使用的随机存取存储器(RAM)类型。

它使用双倍数据率(Double Data Rate,DDR)技术,提供高速数据传输和更高的带宽。

DDR3具有许多设计规范,以下是其中一些重要的规范。

1.精确的电气规范:DDR3的设计需要满足电气规范,以确保可靠的数据传输。

其中包括时钟频率、电压供应、信号幅度和交错延迟等方面的要求。

例如,DDR3的标准供电电压为1.5伏特(V)。

2.时序要求:DDR3的时序要求指定了命令、地址和数据等信号之间的时间关系。

这包括读取和写入操作的延迟时间、复位时间和刷新周期等。

时序要求的正确实现是确保DDR3稳定和可靠性的关键。

3.物理尺寸和连接接口:DDR3的物理尺寸和连接接口规范指定了模块的尺寸、引脚布局和插槽位置等。

这包括模块的长度、宽度和高度,以及引脚的布局和排列方式。

物理尺寸和连接接口规范确保DDR3可以正确地插入和连接到相应的插槽。

4.数据传输带宽:DDR3的设计规范涉及数据传输的带宽要求。

带宽是指每秒钟可以传输的数据量,通常以字节或位为单位。

DDR3的设计需要满足特定的带宽要求,以满足高速数据传输的需要。

5.控制和引脚定义:DDR3的设计规范中包括控制和引脚定义,用于指定不同引脚的功能和使用方式。

这些包括地址线、数据线、控制线、时钟线和电源线等。

控制和引脚定义规范确保正确的信号传输和通信。

6.容量和频率选项:DDR3的设计规范提供了不同容量和频率选项,以满足不同应用需求。

容量选项包括存储器模块的总容量,通常以GB为单位。

频率选项指定了DDR3的传输速率,通常以MHz为单位。

7.错误校正代码(ECC)支持:DDR3的设计规范中还包括对错误校正代码的支持。

ECC是一种能够检测和纠正内存中的错误的技术。

DDR3的设计需要支持ECC功能,以增强数据完整性和可靠性。

综上所述,DDR3的设计规范涵盖了电气规范、时序要求、物理尺寸和连接接口、数据传输带宽、控制和引脚定义、容量和频率选项,以及错误校正代码支持等方面。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(连接器技术标准)

连接器設計準則

---D.D.R系列

核準:審核:制作:

目錄

1.0簡介:-------------------------------------------------------------- 2

2.0產品的結構技術要求:---------------------------------------------- 3

2.6.塑膠本體與Latch干涉尺寸標注及公差分析,如下圖所示:

2.7.塑膠變形定義:

2.8.端子排料方式,如下圖:

2.9.端子電鍍規格采用點鍍方式,如下圖所示:

3.0 產品的一般性規格要求:

產品總長:71.10mm

產品總寬:26.20mm

產品總高:4.00mm/8.00mm ,5.20mm/9.20mm

3.0產品的一般性規格:----------------------------------------------- 7

4.0產品失效性改良方案:---------------------------------------------- 8

1.0產品簡介

0.6mmPitch DDR系列產品,此產品由塑膠本體.端子.Latch.REEL所組成

修改前面過長導致取module困難 修改后module易取

額定電流:0.5A

額定電壓:AC 100V

絕緣阻抗:500MΩ

壽命測試:30次

夾持力測試:0.15kg or more per pin

彈力測試:5.0kg or less per set

4.0產品失效性改良方案:

4.1 塑膠平整度不良,改偷料方式,如下圖:

修改前為側面偷料修改后為底部偷料

4.2 Latch 角斜面過長導致取module時module不易跳出,設計變更修改斜面如下圖:

此產品主要用於NOTE BOOK上對插內存卡.

2.0產品的結構技術要求:

2.1.”SUYIN Mark”位置需進行注明或尺寸標注,如下圖所示:

2.2.DDR 系列成品公規尺寸:

2.3. module插入間隙尺寸分析:

2.4.雙邊接觸分析:

塑膠本體與端子組裝夾口尺寸公差分析:

2.5.塑膠本體與端子干涉尺ቤተ መጻሕፍቲ ባይዱ標注及公差分析,如下圖所示: