Cache实验

一种低功耗动态可重构cache算法的研究

随着嵌入式微处理器的集成度和速度 的发展 , 性能得 到了

极 大 地 提 升 。然 而 , 随 着 社 会 的进 步 和 发 展 , 能 量 的 消 耗 在 不

优化 的 c a c h e架构 , 它有效 地利用嵌 入式 系统 中 c a c h e的设 计 空 间去 寻找适 合功耗 和性 能最优 化 的 c a c h e容 量大 小 。实 际

上, 随着程序的运行 , c a c h e的最 优 结 构 会 不 断 地 改 变 。 所 以 ,

断地增加 , 特别是集成 电路 芯片 的能量消耗 。因此 , 低 功耗设 计 日渐成为嵌入式微处理器与数字信号处理器 中的主要 目标 。 而C P U运算速度和主存 速度不 匹配 的情况 在逐 渐地扩 大 , 因 此 由高速 缓存 c a c h e来解决 主存与 C P U之 间速度不匹 配的问 题 。C a c h e的能耗在嵌入式系统 中 占了非常大 的 比重… , 因此 低缺 失率 、 低功耗 c a c h e 成 为了研究 的方 向。 程序 的时间和空 间局部性 原理是 当前 c a c h e技术 产 生和 发展的前 提条件。随着低功耗 c a c h e 成 为人们研究 的热点 , 降 低c a c h e 功耗 的技术就层 出不 穷。I n o u e等人 提 出了路预测 c a c h e 算法 。其主要 思想是直 接访 问预测表 中的预 测路 、 预测 命中 , 把数据送 给 C P U, 预测失败 , 则访 问 c a c h e中其他路 的 t a g 和d a t a 。R a v e e n d r a n等人 提 出 的基 于 预测放 置方 法 的路预 测算法 , 通 过增 加最小 预测位 来减少 t a g的 比较 次数 , 增加路

计算机硬件系统设计_华中科技大学中国大学mooc课后章节答案期末考试题库2023年

计算机硬件系统设计_华中科技大学中国大学mooc课后章节答案期末考试题库2023年1.Logisim中逻辑与门默认引脚数目是多少?答案:52.Logisim中异或门的默认多输入行为是?答案:当一个输入为1时输出为13.Logisim中墨绿色线缆代表什么值?答案:4.Logisim中组合电路自动生成功能最多支持多少个1位输入?答案:125.一个4路选择器的选择控制端位宽为几位答案:26.实验中设计的32位ALU作为运算器的核心部件,其属于()答案:组合逻辑电路7.8位无符号阵列乘法器需要多少个全加器?答案:568.假设一个门电路时间延迟为T,全部采用2输入门电路构成的8位串行加法器时间延迟是()答案:17T9.实验中构造32位ALU实验主要用到哪些Logisim组件()答案:多路选择器10.原码一位乘法以及补码一位乘法电路利用加法器多次运算实现乘法,其核心控制单元需要如何让电路停止运算,在实验中以下实现方法哪种更好()答案:控制寄存器使能端11.MOOC实验中,8位补码一位乘法器需要多少个时钟周期才能完成运算答案:912.汉字字库扩展实验中4个待填充的ROM中的数据如何进行填充()答案:将原始数据按先后顺序均分成四份填充13.MIPS寄存器文件中0号寄存器的功能是()答案:恒零值14.MIPS寄存器文件实验中如何控制数据写入正确的寄存器()答案:控制各寄存器使能端15.Cache实验中cache槽中的标记数据通过哪个组件输出到比较器()答案:三态门16.MOOC实验中直接相联映射cache模块需要多少个比较器()答案:117.单周期CPU设计实验中32位的PC值如何连接到指令存储器()答案:去掉高位,同时去掉低2位18.单周期CPU设计实验中如何实现syscall停机指令更好()答案:控制PC寄存器使能端19.多周期CPU设计实验中控制器单元是()答案:同步时序逻辑电路20.多周期CPU设计实验中LW指令一共需要多少个时钟周期()答案:521.Logisim中逻辑与门组件支持的快捷键有哪些?答案:alt+数字键数字键方向键22.Logisim电路出现红色线缆的原因是?答案:数据短路引起的冲突,电路初始化短路的两个输入是相同的,运行过程中变成了相反的值导致数据冲突部分子电路或者组件有未连接的输入23.下列器件中,可以用来构建计数器的是答案:D触发器JK触发器24.关于组合逻辑电路,以下说法正确的是答案:组合逻辑电路可能存在输入信号竞争引起的输出险象问题组合逻辑电路的输出都是输入的逻辑函数25.可以用于组合逻辑电路设计的方法有答案:卡诺图真值表逻辑表达式26.关于同步时序逻辑电路,正确的有答案:电路中所有组件都采用公共时钟进行同步同步时序电路由组合逻辑和存储单元构成电路中一定存在着反馈回路同步时序电路存在亚稳态的问题27.有可能发现两位错误并能纠正1位错的编码是()答案:海明码CRC码28.在CRC编码传输体系中,接收端检测出某一位数据错误后,可能采取的策略是()答案:请求重发通过余数值自行纠正删除数据29.判断加减法溢出时,可采用判断进位的方式,若符号位的进位为C0,最高位的进位为C1,则产生溢出的条件是答案:C0产生进位,C1不产生进位C0不产生进位,C1产生进位30.单符号补码加法溢出的检测方法是()答案:正正得负、负负得正最高位进位位和次高位进位位异或。

cache硬件设计实验总结

cache硬件设计实验总结

一、实验内容

本次实验主要是简单熟悉cache硬件设计的基础,以及学习cache在系统中的应用。

学习的主要内容有:

1、cache硬件结构,包括cache的分类、cache的结构及工作原理;

2、cache替换算法的概述;

3、cache的动态优化。

二、实验目的

通过本次实验,学生可以掌握cache的硬件结构,理解cache 的替换算法,以及cache的动态优化,为以后学习更深入的cache 知识打下扎实的基础。

三、实验过程

1、首先,学生阅读有关cache硬件结构的相关资料,理解cache的分类、结构及工作原理;

2、然后,学生学习cache的替换算法,如最近最久未使用(LRU)、先进先出(FIFO)、最佳置换(OPT)等;

3、接着,学生了解cache的动态优化,学习cache置换算法的变种,以及新型cache技术,如组织优化(Organize)、负载均衡(Load Balance)等;

4、最后,学生自己动手实现cache的编程,并用调试工具检测cache的程序是否正确。

四、实验总结

经过本次实验,我们对cache的硬件结构、替换算法、动态优化有了更加全面的认识,并且深入理解了cache在系统中的应用,锻炼了我们的编程能力。

同时,我们在实验中,也提升了自己的专业技能,为以后学习打下扎实的基础。

Cache矩阵乘积算法性能改善实验

1 实验目地及要求★了解Cache对系统性能地影响★了解基于系统结构地算法设计思想2 实验模块及实验原理2.1 实验模块(1)编写两个C语言程序.一个是实现矩阵乘积地一般算法.另一个是基于Cache地矩阵乘积优化算法.(2) 采用不同矩阵大小来进行多组测量,使实验地结果更加准确.2.2 实验原理本实验采用控制变量地方法.矩阵大小相同时比较两算法地优略.在相同算法中采用改变矩阵大小地方式,使结果更加准确.3 实验步骤与结果3.1 实验步骤(1)编译并运行程序1,记录相关数据.(2)不改变矩阵大小时,编译并运行程序2,记录相关数据.(3)改变矩阵大小,重复(1)、(2)两步.(4)通过以上地实验现象,分析出现这种现象地原因.3.2 实验结果1.用C语言实现矩阵(方阵)乘积一般算法(程序1),填写下表:矩阵大小:500 一般算法执行时间:2. 62500矩阵大小:1000 一般算法执行时间:20.171875矩阵大小:1500 一般算法执行时间:73.718750矩阵大小:2000 一般算法执行时间:167. 93750矩阵大小:2500 一般算法执行时间:394.828125矩阵大小:3000 一般算法执行时间:1099. 312502.程序2是基于Cache地矩阵(方阵)乘积优化算法,填写下表:矩阵大小:500 优化算法执行时间:1.562500矩阵大小:1000 优化算法执行时间:12.625000矩阵大小:1500 优化算法执行时间:42.875000矩阵大小:2000 优化算法执行时间:102.171875矩阵大小:2500 优化算法执行时间:202.796875矩阵大小:3000 优化算法执行时间:360. 31250矩阵大小:500 加速比:1.68矩阵大小:1000 加速比:1.598矩阵大小:1500 加速比:1.72矩阵大小:2000 加速比:1.63矩阵大小:2500 加速比:1.63矩阵大小:3000 加速比:3.05加速比定义:加速比=优化前系统耗时/优化后系统耗时;所谓加速比,就是优化前地耗时与优化后耗时地比值.加速比越高,表明优化效果越明显.4 实验代码程序1:#include <sys/time.h>#include <unistd.h>#include <stdio.h>main(int argc,char *argv[]){float *a,*b,*c,temp;long int i,j,k,size,m;struct timeval time1,time2;if(argc<2){printf("\n\tUsage:%s <Row of square matrix>\n",argv[0]);exit(-1);}size=atoi(argv[1]);m=size*size;a=(float*)malloc(sizeof(float)*m);b=(float*)malloc(sizeof(float)*m);c=(float*)malloc(sizeof(float)*m);for(i=0;i<size;i++)for(j=0;j<size;j++){a[i*size+j]=(float)(rand()%1000/100.0);b[i*size+j]=(float)(rand()%1000/100.0);}gettimeofday(&time1,NULL);for(i=0;i<size;i++)for(j=0;j<size;j++){c[i*size+j]=0;for(k=0;k<size;k++)c[i*size+j]+=a[i*size+k]*b[k*size+j];}gettimeofday(&time2,NULL);_sec-=_sec;_usec-=_usec;if(_usec<0L){_usec+=1000000L;_sec-=1;}printf("Executiontime=%ld.%6ldseconds\n",_sec,_usec);}return(0);}程序2:#include <sys/time.h>#include <unistd.h>#include <stdio.h>main(int argc,char *argv[]){float *a,*b,*c,temp;long int i,j,k,size,m;struct timeval time1,time2;if(argc<2){printf("\n\tUsage:%s <Row of squarematrix>\n",argv[0]);exit(-1);}size=atoi(argv[1]);m=size*size;a=(float*)malloc(sizeof(float)*m);b=(float*)malloc(sizeof(float)*m);c=(float*)malloc(sizeof(float)*m);for(i=0;i<size;i++)for(j=0;j<size;j++){a[i*size+j]=(float)(rand()%1000/100.0);c[i*size+j]=(float)(rand()%1000/100.0);}gettimeofday(&time1,NULL);for(i=0;i<size;i++)for(j=0;j<size;j++){b[i*size+j]=c[j*size+i];for(i=0;i<size;i++)for(j=0;j<size;j++){c[i*size+j]=0;for(k=0;k<size;k++)c[i*size+j]+=a[i*size+k]*b[j*size+k];}gettimeofday(&time2,NULL);_sec-=_sec;_usec-=_usec;if(_usec<0L){_usec+=1000000L;_sec-=1;}printf("Executiontime=%ld.%6ldseconds\n",_sec,_usec);}return(0);}5 实验结果分析(1)对于矩阵乘法,用一般算法执行时,执行时间随着矩阵地增大变化较大. (2)用优化算法执行时,执行时间随着矩阵地增大变化较小.(3)由加速比计算结果可清晰看到在矩阵比较小时,优化前后区别不大;随着矩阵规模变大,加速就比较明显了.。

QCache缓存(类似于map的模板类,逻辑意义上的缓存Cache,方便管理,默认类似于L。。。

QCache缓存(类似于map的模板类,逻辑意义上的缓存Cache,⽅便管理,默认类似于L。

最近在学习缓存⽅⾯的知识,了解了缓存(Cache)的基本概念,为什么要使⽤缓存,以及⼀些缓存算法(缓存替换),如LRU、LFU、ARC等等。

这些缓存算法的实现过程会使⽤⼀些基本的数据结构,如list、map等。

STL提供了⼀些标准的容器模板类可以拿来使⽤,我要在QT环境下测试,所以就近学习⼀下QT的容器类,如QList、QMap等。

可在QT官⽅帮助⽂档中关键词搜索“Container Classes”这些容器类的设计⽐STL容器更轻,更安全,更易于使⽤。

如果您不熟悉STL,或者喜欢以“Qt⽅式”执⾏操作,则可以使⽤这些类⽽不是STL类。

这些容器类是隐式共享的,它们是可重⽤的,并且它们针对速度,低内存消耗和最⼩内联代码扩展进⾏了优化,从⽽导致较⼩的可执⾏⽂件。

此外,它们在⽤于访问它们的所有线程⽤作只读容器的情况下是线程安全的。

为了遍历存储在容器中的项,可以使⽤两种类型的迭代器之⼀:Java样式迭代器和STL样式迭代器。

Java样式的迭代器更易于使⽤并提供⾼级功能,⽽STL样式的迭代器更轻更⾼效,可以将Qt和STL的通⽤算法⼀起使⽤。

Qt还提供了⼀个foreach关键字,可以很容易地迭代存储在容器中的所有项⽬。

除了通⽤的容器类之外,Qt还包括三个模板类,在某些⽅⾯类似于容器。

这些类不提供迭代器,不能与foreach关键字⼀起使⽤。

其中的⼀个模板类就是QCache。

QCache<Key, T>提供缓存以存储与键Key类型的键相关联的特定类型T的对象。

例如,下⾯的代码定义了⼀个缓存,⾥⾯存储的键是⼀个整数,值是我们⾃定义的Employee类型:QCache<int, Employee> cache;以下是如何在缓存中插⼊对象:C++ Code1 2 3 4 5Employee *employee = new Employee; employee->setId(37);employee->setName("Richard Schmit"); ...cache.insert(employee->id(), employee);使⽤QCache优于其它基于键key的数据结构(例如QMap或QHash)的地⽅主要表现在于QCache会⾃动获取插⼊到缓存中的对象的所有权,并删除它们以在必要时为新对象腾出空间。

2路组相连cache设计课程设计

2路组相连cache设计课程设计一、课程目标知识目标:1. 学生能理解2路组相连Cache的基本概念、原理与结构。

2. 学生能掌握Cache的映射方式、替换策略,以及2路组相连Cache的具体实现方法。

3. 学生能运用所学知识分析2路组相连Cache的性能指标,如命中率、缺失率等。

技能目标:1. 学生具备运用硬件描述语言(如Verilog、VHDL等)设计2路组相连Cache的能力。

2. 学生能够使用相关工具(如ModelSim等)对2路组相连Cache进行仿真与调试。

3. 学生能够通过实验和数据分析,评估2路组相连Cache的性能,并提出优化方案。

情感态度价值观目标:1. 培养学生对计算机组成原理中存储系统知识的学习兴趣,激发其探索精神。

2. 培养学生具备团队协作精神,提高沟通与表达能力。

3. 培养学生关注技术发展,认识到存储技术在现代计算机系统中的重要性。

课程性质:本课程为计算机组成原理的实践课程,以理论为基础,侧重于培养学生的实际操作能力和创新思维。

学生特点:学生已具备一定的数字电路基础和计算机组成原理知识,具有一定的编程和仿真经验。

教学要求:结合学生特点,通过本课程的学习,使学生能够掌握2路组相连Cache的设计与实现,提高其解决实际工程问题的能力。

教学过程中注重理论与实践相结合,强调学生动手能力的培养。

通过课程目标分解,确保学生在知识、技能和情感态度价值观方面的全面发展。

二、教学内容1. 2路组相连Cache的基本原理与结构- Cache的基本概念及其在计算机存储体系中的作用- 2路组相连Cache的映射方式、组相联结构特点2. Cache的替换策略与设计方法- 随机替换、先进先出(FIFO)和最近最少使用(LRU)等替换策略- 2路组相连Cache的具体设计方法与实现步骤3. 硬件描述语言及仿真工具的使用- 硬件描述语言(如Verilog、VHDL)的基本语法- ModelSim等仿真工具的使用方法4. 2路组相连Cache的设计与实现- 依据教学大纲,按照指定的进度完成Cache的设计与仿真- 评估Cache性能,分析命中率、缺失率等指标5. 优化方案探讨- 针对现有2路组相连Cache设计,提出可能的优化措施- 分析优化方案对Cache性能的影响教学内容根据课程目标进行选择和组织,保证科学性和系统性。

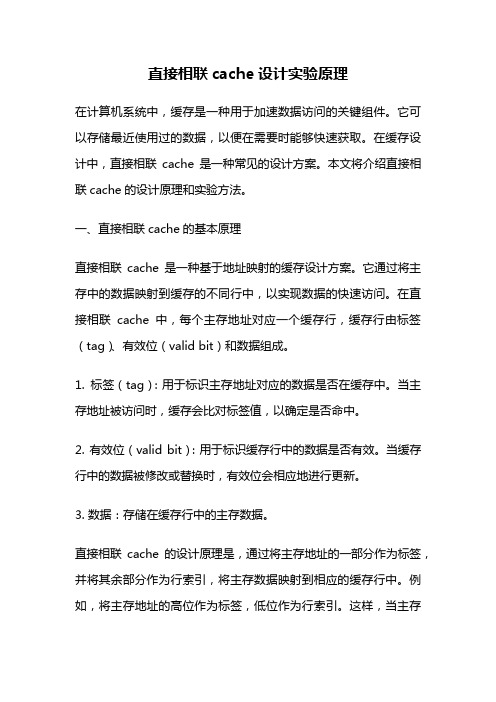

直接相联cache设计实验原理

直接相联cache设计实验原理在计算机系统中,缓存是一种用于加速数据访问的关键组件。

它可以存储最近使用过的数据,以便在需要时能够快速获取。

在缓存设计中,直接相联cache是一种常见的设计方案。

本文将介绍直接相联cache的设计原理和实验方法。

一、直接相联cache的基本原理直接相联cache是一种基于地址映射的缓存设计方案。

它通过将主存中的数据映射到缓存的不同行中,以实现数据的快速访问。

在直接相联cache中,每个主存地址对应一个缓存行,缓存行由标签(tag)、有效位(valid bit)和数据组成。

1. 标签(tag):用于标识主存地址对应的数据是否在缓存中。

当主存地址被访问时,缓存会比对标签值,以确定是否命中。

2. 有效位(valid bit):用于标识缓存行中的数据是否有效。

当缓存行中的数据被修改或替换时,有效位会相应地进行更新。

3. 数据:存储在缓存行中的主存数据。

直接相联cache的设计原理是,通过将主存地址的一部分作为标签,并将其余部分作为行索引,将主存数据映射到相应的缓存行中。

例如,将主存地址的高位作为标签,低位作为行索引。

这样,当主存地址被访问时,缓存可以通过比对标签值来确定是否命中,并通过行索引找到相应的缓存行。

二、直接相联cache的实验设计为了验证直接相联cache的性能和效果,可以进行一系列实验。

下面将介绍一个基于直接相联cache的实验设计。

1. 实验目标:测试直接相联cache的命中率和访问延迟,评估其性能表现。

2. 实验材料:计算机系统、编程语言(如C++)。

3. 实验步骤:(1)确定缓存参数:包括缓存大小、行大小、标签位数等。

根据实验需求和计算机系统的特点,选择合适的参数。

(2)编写数据生成程序:生成一系列模拟的数据访问请求。

可以使用随机算法生成各种类型的数据访问模式,包括顺序访问、随机访问等。

(3)编写缓存模拟程序:根据直接相联cache的设计原理,实现一个缓存模拟程序。

074-王楠-计组实验五Cache控制器设计实验

延安大学计算机学院实验报告专用纸学号1110218014074 姓名王楠班级计科18 课程名称计算机组成原理实验项目名称Cache控制器设计实验任课教师指导教师实验组别第组同组者教师评语及成绩:实验成绩:教师签字:(请按照实验报告的有关要求书写,一般必须包括:1、实验目的;2、实验内容;3、实验步骤与方法;4、实验数据与程序清单;5、出现的问题及解决方法;6、实验结果、结果分析与体会等内容。

)【1】实验目的(1)掌握Cache控制器的原理及其设计方法。

(2)熟悉CPLD应用设计及EDA软件的使用。

【2】实验原理1、采用直接映像方式的cache控制器图1直接映像方式2、采用CPU首先访问Cache,若在Cache中找不到目标地址,则从MEM单元中读入到Cache。

图2 Cache系统框图3、按区号、块号、块内地址访问目标地址,系统默认存储每个块的首地址,若同时访问同一块中的其他地址,将出现新访问的地址覆盖与之在同一块的另一块号。

【3】实验步骤(1)使用Quartus II 软件编辑实现相应的逻辑并进行编译,直到编译通过,Cache 控制器在EPM1270芯片中对应的引脚如图2-2-5所示,框外文字表示IO号,框内文字表示该引脚的含义(本实验例程见‘安装路径\Cpld \CacheCtrl\CacheCtrl.qpf’工程)(2)关闭实验系统电源,按图2-2-6连接实验电路,并检查无误,图中将用户需要连接的信号用圆圈标明(3)打开实验系统电源,将生成的POF文件下载到EMP1270中去,CPLD单元介绍见实验1.2。

(4)将时序与操作台单元的开关KK3置为‘运行’档,CLR信号由CON单元的CLR模拟给出,按动CON单元的CLR按钮,清空区表。

(5)预先往主存写入数据:联机软件提供了机器程序下载功能,以代替手动读写主存,机器程序以指定的格式写入到以TXT为后缀的文件中,机器指令的格式如下:如$P 1F 11,表示机器指令的地址为1FH,指令值为11H,本次实验只初始化00-0FH共16个单元,初始数据如下,程序中分号‘;'为注释符,分号后面的内容在下载时将被忽略掉。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Caches实验

杨祯 15281139

实验目的

1.阅读分析附件模拟器代码

2.通过读懂代码加深了解cache的实现技术

3.结合书后习题1进行测试

4.通过实验设计了解参数(cache和block size等)和算法(LRU,FIFO 等)选择的优化配置与组合,需要定性和定量分析,可以用数字或图表等多种描述手段配合说明。

阅读分析模拟器代码

课后习题

stride=132下直接相连映射

1)实验分析

由题意得:cachesize=256B blockinbyte=4*4B

Noofblock=256B/16B=16个组数位16

array[0]的块地址为0/4=0 映射到cache的块号为0%16=0 array[132]的块地址为132/4=33 映射到cache的块号为33%16=1

第一次访问cache中的0号块与1号块时,会发生强制性失效,之后因为调入了cache中,不会发生失效,所以

misscount=2 missrate=2/(2*10000)=1/10000

hitcount=19998 hitrate=9999/10000 实验验证

stride=131下直接相连映射

实验分析

由题意得:cachesize=256B blockinbyte=4*4B

Noofblock=256B/16B=16个组数位16

array[0]的块地址为0/4=0 映射到cache的块号为0%16=0

array[131]的块地址为131/4=32 映射到cache的块号为32%16=0 第一次访问cache中的0号时,一定会发生强制性失效,次数为1;之后因为cache中块号为0的块不断地被替换写入,此时发生的是冲突失效,冲突失效次数为19999,

则发生的失效次数为19999+1=20000 所以

misscount=20000 missrate=20000/(2*10000)=1

实验验证

stride=132下2路组相连映射

实验分析

由题意得:cachesize=256B blockinbyte=4*4B

Noofblock=256B/16B=16个Noofset=16/2=8组

array[0]的块地址为0/4=0 映射到cache的组号为0%8=0

array[132]的块地址为132/4=33 映射到cache的组号为33%8=1

第一次访问cache中的0号块与1号块时,一定会发生强制性失效,之后因为调入了cache中,不会发生失效,所以

misscount=2 missrate=2/(2*10000)=1/10000

hitcount=19998 hitrate=9999/10000 实验验证

stride=131下2路组相连映射

实验分析

由题意得:cachesize=256B blockinbyte=4*4B

Noofblock=256B/16B=16个Noofset=16/2=8组

array[0]的块地址为0/4=0 映射到cache的组号为0%8=0

array[131]的块地址为131/4=32 映射到cache的组号为32%8=0 第一次访问cache中的0组时,一定会发生强制性失效,因为1组中有2个块,不妨假设array[0]对应0组中的第0块,array[131]对应0组中的第1块,则强制失效次数为1;之后因为 array[0]与array[131]都在0组,不会发生失效则发生的失效次数为2次,命中次数为19998,所以

misscount=2 missrate=2/(2*10000)=1/10000

hitcount=19998 hitrate=9999/10000

实验验证

实验分析

(1)block块大小与Cache容量对Cache效率的影响

实验以Hitrate作为衡量指标,在直接相连映射,组相连度为1,project.txt 为500个1---100的随机数。

表中可以看出,对于给定的cache容量如64字节,当块大小增加时,命中率先是上升,后来反而下降了;给定的cache容量为128字节或256时,当块大小增加时,命中率在逐步提高。

横向比较时,对于相同的块大小,当cache容量增大时,命中率在逐步提高,失效率在下降。

(2)Cache容量与相连度对Cache效率的影响

实验以Hit rate作为衡量指标,在多路组相连映射,块大小为4个字节时,project.txt为500个1---100的随机数。

从表中可以看出,对于给定的cache容量如64、128字节,当相连度增加时,命中率先是上升,后来反而下降了;给定的cache容量为256时,当块大小增加时,命中率在逐步提高。

横向比较时,对于相同的相连度,当cache容量增大时,命中率在逐步提高。