LPC3250 NAND Flash 开发文档

LPC3220_vs_LPC3250

D2 D5 D8

FLASH_ALE USB_DAT_VP/U5_RX GPO_4

D3 D6 D9

GPO_14

USB_OE_TP

GPIO_2/KEY_ROW6/E NET_MDC GPO_3/LCDVD[1] PWM_OUT2/INTSTAT/

D10 D13

D11 D14

GPO_18/MCOA0/LCDLP PWM_OUT1/LCDVD[16

D12 D15

广州周立功单片机发展有限公司

Tel: (020)38730976

38730977

Fax: 38730925

续上表

引脚 符号

MCABORT

引脚

符号 ]

引脚

符号 LCDVD[19]

D16 Row E E1 E4 E7 E10

KEY_ROW3/ENET_TX_ EN

B5 B8

B10

B11

B12

B13

B14

B15

B17

n.c.

C2 C5 C8

GPO_19 USB_SE0_ VM/U5_TX MS_DIO3/MAT0[3] GPIO_3/KEY_ROW7/ ENET_MDIO GPI_2/CAP2[0]/ ENET_RXD3 KEY_ROW4/ENET_TX D0

N3 N6 N9 N12 N15 N18

EMC_A[7/P1[7] VSS_EMC VDD_EMC VDD_AD V EMC_DQM[1] VSS_EMC VSS_EMC VSS_AD

P2 P5 P8 P11 P14

EMC_A[10]/P1[10] EMC_DQM[3] VSS_EMC VSS_EMC VSS_OSC

P3 P6 P9 P12 P15

lpc3250

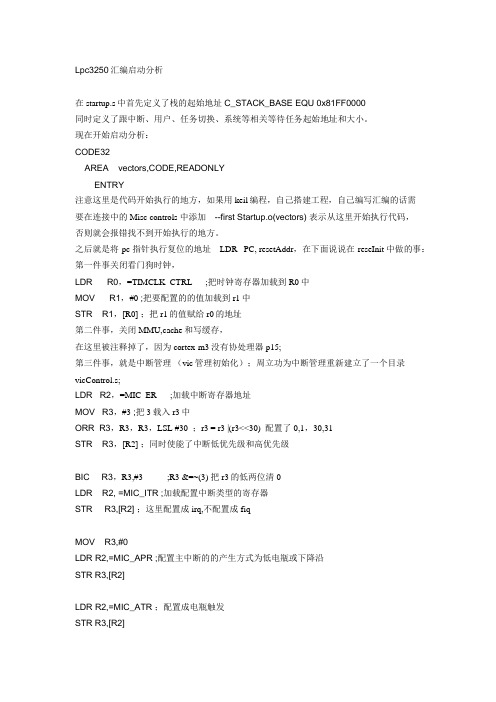

Lpc3250汇编启动分析在startup.s中首先定义了栈的起始地址C_STACK_BASE EQU 0x81FF0000同时定义了跟中断、用户、任务切换、系统等相关等待任务起始地址和大小。

现在开始启动分析:CODE32AREA vectors,CODE,READONLYENTRY注意这里是代码开始执行的地方,如果用keil编程,自己搭建工程,自己编写汇编的话需要在连接中的Misc controls 中添加--first Startup.o(vectors) 表示从这里开始执行代码,否则就会报错找不到开始执行的地方。

之后就是将pc指针执行复位的地址LDR PC, resetAddr,在下面说说在reseInit中做的事:第一件事关闭看门狗时钟,LDR R0,=TIMCLK_CTRL ;把时钟寄存器加载到R0中MOV R1,#0 ;把要配置的的值加载到r1中STR R1,[R0];把r1的值赋给r0的地址第二件事,关闭MMU,cache和写缓存,在这里被注释掉了,因为cortex-m3没有协处理器p15;第三件事,就是中断管理(vic管理初始化);周立功为中断管理重新建立了一个目录vicControl.s;LDR R2,=MIC_ER ;加载中断寄存器地址MOV R3,#3 ;把3载入r3中ORR R3,R3,R3,LSL #30 ;r3 = r3 |(r3<<30) 配置了0,1,30,31STR R3,[R2];同时使能了中断低优先级和高优先级BIC R3,R3,#3 ;R3 &=~(3) 把r3的低两位清0LDR R2, =MIC_ITR ;加载配置中断类型的寄存器STR R3,[R2] ;这里配置成irq,不配置成fiqMOV R3,#0LDR R2,=MIC_APR ;配置主中断的的产生方式为低电瓶或下降沿STR R3,[R2]LDR R2,=MIC_ATR ;配置成电瓶触发STR R3,[R2]MVN R1,R3 ; R1 = ~R3; r1 = 0xffffffffLDR R2,=MIC_RSRSTR R1,[R2]/*下面是配置sub interrupt*/........./*首先定义一个变量*/AREA vicAddr, DATA,ALIGN = 2 ;4字节对齐的数据段,有就是int型__GulVicEntry SPACE 32*3*4 + 4 ;申请388字节的空间,并初始化/*插入点资料*/AREA语法格式:AREA 段名属性1 ,属性2 ,……AREA 伪指令用于定义一个代码段或数据段。

LPC3250应用

LPC3250采用ARM926EJ-S内核,运行频率可高达208MHz;支持矢量浮点协处理器;32kB 指令高速缓存和32kB 数据高速缓存;高达256kB 的内部SRAM(IRAM);可选择从不同的外部设备中启动:NAND Flash、SPI 存储器、USB、UART 或静态存储器;多层 AHB 系统为每个AHB 主机单独提供总线,包括CPU 的指令总线和数据总线、DMA 控制器的两条数据总线和USB 控制器的另一条总线,两条数据总线一条用于LCD、另一条用于以太网MAC。

一般情况下没有仲裁延迟,除非出现2 个主机同时访问同一个从机的情况。

DDR 和SDR SDRAM 以及静态设备的外部存储器控制器;2 个NAND Flash 控制器。

一个支持单级NAND Flash 器件,另一个支持多级NANDFlash 器件;1 个主机中断控制器(MIC)和2 个从机中断控制器(SIC),支持74 个中断源;1 个8 路通用AHB DMA 控制器(GPDMA),可与SD 卡端口、高速UART、I2S端口和SPI 接口一同使用,来实现存储器到存储器之间的传输;串行接口:-带有特定 DMA 控制器的10/100 以太网MAC;-USB 接口支持设备、主机(遵循OHCI)或On-The-Go(OTG),带有相关的DMA 控制器,由特定的PLL 来提供所需的48MHz USB 时钟;-4 个标准UART,带有小数波特率发生器和64 字节FIFO,其中一个标准的UART支持IrDA;-3 个其它的高速UART,在13MHz 的主振荡器作用下可支持高达921,600bps的板内通信;所有高速UART 都提供64 字节FIFO;-2 个SPI 控制器;-2 个SSP 控制器;-2 个独立的主机I2C 接口,具有标准开漏管脚。

I2C 总线接口支持单主机、从机和多主机的I2C 配置;-2 个I2S 接口,每个具有独立的输入(RX)和输出(TX)通道。

!vivi中对Nand Flash的配置和操作

vivi中对Nand Flash的配置和操作Vivi中在head.S文件中有一段程序是对Nand Flash的配置,s3c2410支持从Nand Flash启动。

Nand Flash特点:(下面这篇文章介绍的很全面)/Blog/Detail_RD.Blog_yuwenxin_21349.htmlK9F1208U0M:此flash每页528Bytes(512byte的Main Area + 16byte的Spare Area),每32个page形成一个Block(32*528B)。

具体一片flash上有多少个Block视需要所定。

k9f1208U0M具有4096个block,故总容量为4096*(32*528B)=66MB,但是其中的2MB(Spaer Area)是用来保存ECC校验码等额外数据的,故实际中可使用的为64MB。

Nand flash以页(512Byte)为单位读写数据,而以块(16KB)为单位擦除数据。

按照这样的组织方式可以形成所谓的三类地址:● Column Address:列地址,地址的低8位● Page Address :页地址● Block Address :块地址一片Nand flash为一个设备(device),其数据存储分层为:1 (Device) = 4096 (Blocks)1 (Block) = 32 (Pages/Rows)页与行是相同的意思,叫法不一样1 (Page) = 528 (Bytes) =数据块大小(512Bytes) + OOB块大小(16Bytes)对于NAND Flash来讲,地址和命令只能在I/O[7:0]上传递,数据宽度也是8位,这导致在读写指定地址的数据时,地址是分4次传递的(3次右移),s3c2410这个处理器之所以可以直接从Nand flash启动,是因为CPU内置了4KB的片内SRAM,datasheet上称“Steppingstone”。

Linpo3250_linux使用手册

Linpo-LPC3250-Linux使用手册上海丰宝电子科技有限公司 NXP团队//版本0.22009.11第一章 Linux开发环境建立推荐操作系统:Fedora8/Fedora9/Fedora10网络:InternetLTIB(Linux Target Image Builder)是一个开发Linux系统的简洁开发工具。

LTIB会自动从网络上下载和安装所需要的安装包,使开发Linux更容易更快捷。

可以访问了解LTIB的相关内容。

安装LTIB前,Fedora系统需要安装一些软件包。

打开终端,如果是在user用户下打开的命令行终端,需要在终端下输入su 命令切换到root用户下,提示输入的password是root用户下的密码。

Linux终端下输入密码是不显示的,输入完成后按Eenter键即可。

在linux系统的终端下切换用户的命令是su ,要切换到root超级用户用户下,输入su 按回车,根据提示输入密码。

由root用户切换到usr用户下,输入su usr1,usr1是你普通用户的名字,根据具体情况而定。

如果你的普通用户名字是jim,切换到普通用户下的命令就是 su jim 。

以下引用的usr1都是您普通用户的名字,是根据具体情况而定的。

所有的命令按回车键后,才生效。

在root下分别执行如下命令:# yum install yum-fastestmirror -y# yum install tcl# yum install perl-libwww-perl1) 、在root用户下输入命令: /usr/sbin/visudo,修改用户权限找到如下的字段:# Allow root to run any commands anywhereroot ALL=(ALL) ALL(光标移动到此处,先按下键盘上“i“键,然后按Enter 键,在这后面添加如下内容)(usr1) ALL=(ALL) NOPASSWD: ALL(usr1)是实际用户的名字,比如:Jim ALL=(ALL) NOPASSWD: ALL添加完成后,先按一下Esc键,再按“Shift” 和“:”的组合键,然后输入”w””q”按回车键保存退出。

LPC3250 EMC 开发文档

文件标识:R&DNXPLPC3250_EK 平台当前版本:v1.00 作 者:林鸿飞 文件状态:[√] 草稿 [ ] 正式发布 [ ] 正在修改完成日期:2009-11-30EMC基本开发文档(BD)日 期:2009-11-30 作 者:林鸿飞版本/状态作者参与者起止日期修改内容v1.00 林鸿飞 2009-09-08/2009-11-30初始版本目录第1章 LPC32x0 外部存储器控制器 (EMC)1.1 介绍LPC32x0 外部存储器控制器是一个 ARM PrimeCell 多端口存储器控制器外设,用于异步静态存储器外设如:RAM、ROM 和 flash,以及动态粗存储器如单数据速率(SDR)和双数据速率(DDR)SDRAM。

EMC是一种遵循先进微控制器总线结构(AMBA)的外设。

1.2 EMC 的特性z动态存储器接口支持包括单一数据传输率和双数据传输率的 SDRAM;z支持 1.8 V I/O 接口的移动 SDRAM 设备;z异步静态存储器设备支持包括 RAM、ROM 和 Flash,可选用或者不选用异步页模式;z低传输等待时间(transaction latency);z带有读写缓冲区以减少延迟提高性能;z支持8位,16位和32位宽度的静态存储器;z支持 16位,32位宽度片选型 SDRAM 存储器;z静态存储器的特点包括:支持异步页模式读取;可编程的等待状态;总线循环延迟(turnaround delay);输出使能和写使能延迟;扩展的等待时间。

z多重省电模式,可动态控制到 SDRAM 的 CKE 和 CLKOUT 信号;z控制器可支持 2K、4K 和 8K 行地址同步存储器设备,也就是典型的 512 Mbit、256 Mbit 以及和 128 Mbit 设备,每个设备的数据可以为4、8、16 或 32 位;z如果需要,独立的复位域允许通过芯片复位进行自动刷新;z带有 4 个静态存储器设备选择信号;z带有 2 个同步存储器设备选择信号。

SmartARM3250

bus 接口、CF 卡接口、SD/MMC 卡接口、I2S 音频接口、以太网接口等,满足各种应用要求。

SmartARM3250全面深入地支持μC/OS -II 、WinCE 和Linux 操作系统,同时提供大量软件源代码及详细的开发文档,加快用户产品开发进度。

M3250-N64CPU 64MB SDRAM 2MB NOR Flash 256MB NAND Flash TFT SD/MMC USB Host 71112 1EMCTFT-4238-T TFT-4238-TZYAM1380 I2S 音频输入/输出模块(选配件)功能简介:ZYAM1380 I2S 音频输入/输出模块选用NXP 公司推出的UDA1380 芯片,该芯片是一个立体声音频编解码器,支持I2S 总线数据帧格式,数据字宽度多达24 位,集成了ADC 和DAC,支持全双工采样,采样精度支持16、18、20、24 位,且支持3 线控制标准(L3)。

它被广泛应用于MD/CD、笔记本电脑、mini 唱片播放器、数字视频摄像机等。

主要特性:可便利地连接至Smart ARM3250 开发平台;完整的数字音频输入/输出电路解决方案;输入/输出接口上具有ESD 器件,增强了电路的抗静电能力;UDA 1380 包含AGC 的模拟前端;UDA 1380 支持2V(RMS 值)输入信号;UDA 1380 可分别对ADC 或DAC 进行功率控制;UDA 1380 芯片的DAC 无须再接后端模拟滤波器;可通过I2C/L3 总线完成对UDA 1380 芯片的数字音频处理(如去重音、音量控制、低音增强、高音和软件静音等)和系统控制。

前后台和μC/OS-II嵌入式实时操作系统移植μC/OS-II到ARM9软件包源代码;NAND Flash控制器实验;EMC控制器实验GPDMA实验;I2S实验;GPIO相关实验;LCD控制器实验;看门狗实验;ADC相关实验;I2C相关实验;中断控制器相关实验;标准串口和高速串口试验;定时器相关试验;SD/MMC控制器实验;CF卡实验;触摸屏控制器相关实验;SSP控制器相关实验;以太网(TCP/UDP)相关实验(源码公开);CAN相关实验(源码公开);USB Device相关例程(源码公开);USB Host相关例程(源码公开);USB OTG相关例程(源码公开)。

LPC3250与S3C2440A性能及功能参数对比说明书

LPC3250与S3C2440A性能及功能参数对比1.性能/功能参数对比表续上表2.芯片的用户手册下载地址LPC3250用户手册下载地址:/support/documents/microcontrollers/pdf/user.manual.lpc3220.01.lpc3230.01.lpc3240.01.lpc3250.01.pdfS3C2440A用户手册下载地址:/global/business/semiconductor/productInfo.do?fmly_id=229&part num=S3C2440&xFmly_id=2293.结合WinCE系统分析LPC3250的优势优势(一)——AHB矩阵总线结构由于LPC3250内部采用了先进的矩阵总线结构,使得LPC3250即使主频比S3C2440A 低了近200MHZ,但是整体的性能差距却不大。

优势(二)——LCD分辨率LPC3250支持1024*768的分辨率,而对系统性能几乎不会产生影响;而S3C2440A数据手册中支持最高640*480的分辨率,实际应用最高也只能到800*480。

射 频 和 天 线 设 计 培 训 课 程 推 荐易迪拓培训()由数名来自于研发第一线的资深工程师发起成立,致力并专注于微波、射频、天线设计研发人才的培养;我们于2006年整合合并微波EDA网(),现已发展成为国内最大的微波射频和天线设计人才培养基地,成功推出多套微波射频以及天线设计经典培训课程和ADS、HFSS等专业软件使用培训课程,广受客户好评;并先后与人民邮电出版社、电子工业出版社合作出版了多本专业图书,帮助数万名工程师提升了专业技术能力。

客户遍布中兴通讯、研通高频、埃威航电、国人通信等多家国内知名公司,以及台湾工业技术研究院、永业科技、全一电子等多家台湾地区企业。

易迪拓培训推荐课程列表:/peixun/tuijian/射频工程师养成培训课程套装该套装精选了射频专业基础培训课程、射频仿真设计培训课程和射频电路测量培训课程三个类别共30门视频培训课程和3本图书教材;旨在引领学员全面学习一个射频工程师需要熟悉、理解和掌握的专业知识和研发设计能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

文件标识:R&DNXPLPC3250_EK 平台当前版本:v1.00 作 者:林鸿飞 文件状态:[√] 草稿 [ ] 正式发布 [ ] 正在修改完成日期:2009-12-06作 者:林鸿飞日 期:2009-12-06 基本开发文档(BD)NAND Flash版本/状态作者参与者起止日期修改内容初始版本v1.00 林鸿飞 2009-12-06目录第1章 LPC32x0 多级 NAND flash 控制器1.1 介绍注:LPC32x0 有两个 NAND Flash 控制器,一个多级 NAND Flash 控制器和一个单级 NAND Flash 控制器。

这两个 NAND Flash 控制器使用相同的引脚接口来外接 NAND Flash 芯片,因此在某一时间只有一个接口是可用的。

NAND Flash 控制器可在 FLASHCLK_CTRL 寄存器中设置位来禁止,为了省电在她们没有被用时。

多级单元MLC NAND Flash 控制器接口连接到多级 NAND Flash 设备。

外部 NAND Flash 设备(不论是多级还是单级类型)可用于允许自动引导程序加载到内部 RAM 用于执行应用程序,详情请见“引导程序开发文档”。

1.2 EMC 的特性1.3 管脚第2章 LPC32x0 单级 NAND flash 控制器2.1 介绍注:LPC32x0 有两个 NAND Flash 控制器,一个多级 NAND Flash 控制器和一个单级 NAND Flash 控制器。

这两个 NAND Flash 控制器使用相同的引脚接口来外接 NAND Flash 芯片,因此在某一时间只有一个接口是可用的。

NAND Flash 控制器可在 FLASHCLK_CTRL 寄存器中设置位来禁止,为了省电在她们没有被用时。

单级单元 MLC NAND Flash 控制器接口连接到单级 NAND Flash 设备。

外部 NAND Flash 设备(不论是多级还是单级类型)可用于允许自动引导程序加载到内部 RAM 用于执行应用程序,详情请见“引导程序开发文档”。

2.2 特性z 闪存设备大小高达 2Gbit 。

更小的设备将被隐藏。

z NAND 闪存宽度为 8位。

z DMA 页传输。

z 20 字节的 DMA 读和写 FIFO ,8 字节的命令 FIFO 。

z 在主数据区硬件支持 ECC (错误检查和校正)。

如果发现错误,软件必须修复。

支持双位错误检测和 1位错误更正。

备用区的错误检测则需由软件来实现。

2.3 管脚描述表 2.1 NAND flash 控制器管脚 管脚名称类型NAND 闪存 信号 功能FLASH_CE_N 输出 CEn 芯片选择,低电平有效。

FLASH_WR_N 输出 WEn 写使能,低电平有效。

FLASH_RD_N 输出 REn 读使能,低电平有效。

FLASH_ALE 输出 ALE 地址锁存使能。

FLASH_CLE 输出 CLE 命令锁存使能。

FLASH_RDY 输入 RDY 激活高就绪信号。

FLASH_IO[7:0]输入/输出D_IOI/O 管脚,命令,地址和数据。

2.3.1 2.3.2 NAND flash 控制器中断信号MLC NAND Flash 控制器中断被 NAND_INT_E 屏蔽且 ORed 在 SLC NAND Flash 控制器变为中断控制器之前带有中断信号。

MLC 和 SLC NAND Flash 控制器的中断连接入图 2.1 所示。

NAND flash 控制器 DMA 请求信号dma_breq(0)、dma_sreq(0)以及 dma_sreq(1) 都是 ORed 并连接到作为从 SLC Flash 控制器(DMA 控制器外围设备号 1)突发请求新信号的DMA 控制器。

为了能够使 SLC NAND Flash 控制器能够使用外设到外设的 DMA 传输,这种突发请求信号也被连接到 DMA 控制器外围设备号 12 在 SLC Flash 控制器被选择时。

当 MLC NAND Flash 控制器被选择,MLC Flash 控制器的突发请求信号被连接到 DMA 控制器外部设备号 12。

MLC 和SLC NAND Flash 控制器的 DMA 信号连接如图 2.1所示。

图 2.1 略。

2.4 SLC NAND flash 控制器描述SLC NAND flash 控制器的框图如图 2.2 所示。

2.5 DMA 接口下面的 DMA 信号用于SLC NAND flash 控制器。

在某一时间只有一个请求信号可被激活。

请求信号保持断言直到 DMA 控制器断言 DMACLR 信号。

2.5.1 DMA SREQ单字 DMA 请求。

2.5.1.1 DMABREQ突发 DMA 请求。

DMABREQ 信号用于数据传输阶段。

当读取时,如果数据 FIFO 有 4 字或更多需要传输就产生断言。

当写入时,如果在数据 FIFO 中少于 4 字则产生断言。

注:SLC 控制器产生的 dma_breq(0)、dma_sreq(0)以及dma_sreq(1)信号,它们连接在一起并连接到 DMA 控制器作为 SLC flash 控制器(作为外围设备号1)的突发请求信号。

为了能够使 SLC NAND Flash 控制器能够使用外设到外设的 DMA 传输,这种突发请求信号也被连接到 DMA 控制器外围设备号 12 在 SLC Flash 控制器被选择时。

2.5.1.2 DMACLRDMA 请求清除输入。

DMA 控制器在突发传输的最后字传输之间断言。

2.5.2 数据 FIFO这里只有一个数据 FIFO。

数据 FIFO 可配置成读或写模式。

1.当数据 FIFO 配置成读模式时,音序器从 NAND flash 读取数据并存储数据到数据 FIFO中。

然后,不论 ARM还是 DMA 在 AHB 总线上通过 32位读来清空 FIFO。

2.当数据 FIFO 配置成写模式时,ARM 或 DMA 写数据到带有 32位 AHB 总线写的 FIFO。

然后,音序器在某一个时间取出 FIFO 8位数据并把这些数据写入 NAND flash。

2.6 寄存器描述表 2.2 显示了单级 NAND 闪存控制器相关的寄存器以及它们的功能。

下面的表对每个寄存器都有做详细的说明。

表 2.2 单级 NAND 闪存控制寄存器地址寄存器名称描述复位值类型0x2002 0000 SLC_DATA SLC NAND flash 数据寄存器- R/W 0x2002 0004 SLC_ADDR SLC NAND flash 地址寄存器- W 0x2002 0008 SLC_CMD SLC NAND flash 命令寄存器- W 0x2002 000C SLC_STOP SLC NAND flash 停止寄存器- W 0x2002 0010 SLC_CTRL SLC NAND flash 控制寄存器0x00 R/W 0x2002 0014 SLC_CFG SLC NAND flash 配置寄存器0x00 R/W0x2002 0018 SLC_STAT SLC NAND flash 状态寄存器00X 二进制R0x2002 001C SLC_INT_STAT SLC NAND flash 中断状态寄存器0x00 R0x2002 0020 SLC_IEN SLC NAND flash 中断使能寄存器0x00 R/W 0x2002 0024 SLC_ISR SLC NAND flash 中断设置寄存器0x00 W 0x2002 0028 SLC_ICR SLC NAND flash 中断清除寄存器0x00 W 0x2002 002C SLC_TAC SLC NAND flash 读时序弧配置寄存器校验位0x00 R/W 0x2002 0030 SLC_TC SLC NAND flash 传输数据寄存器0x00 R/W 0x2002 0034 SLC_ECC SLC NAND flash 校验位0x00 R0x2002 0038 SLC_DMA_DATA SLC NAND flash DMA 数据- R/W 2.6.1 SLC NAND flash 数据寄存器(SLC_DATA - 0x2002 0000)SLC_DATA 是一个 16位宽寄存器,提供直接对 NAND flash存取功能。

SLC_DATA 的功能位如表 2.3 所示。

写入的数据进行缓冲,然后转移到 flash 内存。

SLC_DATA 必须是作为一个字寄存器来存取,尽管在都和写时只有8位数据。

任何 SLC_DATA 读被转移到 flash 存储器的读循环且总线处理可以延长直到请求数据可用。

表2.3 SLC NAND flash 数据寄存器(SLC_DATA - 0x2002 0000)位描述复位值15:8 保留,用户软件不要向这些位写1。

从保留位读出的值未定义。

-7:0 NAND flash 读或写数据-2.6.2 SLC NAND flash 地址寄存器(SLC_ADDR - 0x2002 0004)SLC_ADDR 是一个8位宽度寄存器,提供直接存取 NAND flash 地址寄存器功能。

SLC_ADDR 的功能位如表 2.4 所示。

CLE 输出在写 SLC_ADDR 后被驱动,且寄存器的内容被发送到 NAND flash 数据线D_OUT[7:0]。

多重写 SLC_ADDR 可以增加传输地址的总宽度。

写 SLC_ADDR 被存储在同样用于SLC_CMD 和 SLC_STOP 的内部 FIFO。

FIFO 允许内部继续操作尽管外部 NAND flash 操作已经完成。

表2.4 SLC NAND flash 地址寄存器(SLC_ADDR - 0x2002 0004)位描述复位值7:0 NAND flash 读和写地址。

-2.6.3 SLC NAND flash 命令寄存器(SLC_CMD - 0x2002 0008)SLC_CMD 是一个8位宽度寄存器,提供直接存取 NAND flash 命令寄存器功能。

CLE 输出在写SLC_CMD 后被驱动,且寄存器的内容被发送到 NAND flash 数据线。

写 SLC_CMD 被存储在同样用于SLC_ADDR 和 SLC_STOP 的内部 FIFO。

FIFO 允许内部继续操作尽管外部 NAND flash 操作已经完成。

表2.5 SLC NAND flash 命令寄存器(SLC_CMD - 0x2002 0008)位描述复位值7:0 NAND flash 命令。

-2.6.4 SLC NAND flash 停止寄存器(SLC_STOP - 0x2002 000C)写 SLC_STOP 寄存器引发闪存控制器挂起所有命令/地址序列。