Xilinx ISE软件简单教程1609514345.ppt22

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

ISE软件使用说明

说明这个说明主要介绍了使用开发板可能使用到的3个工具,主要以串口功能的实现作为例子,讲述了ISE, Plantform和EDK的使用方法以及操作的基本流程。

ISE的使用一.启动Xilinx ISE:开始Æ所有程序ÆXilinx ISE 7.1iÆProject Navigator二.新建/打开一个工程:如果已经有了工程,则在FileÆOpen Project弹出的对话框里面选择你的工程。

如果没有合适的工程就需要通过FileÆNew Project来新建一个工程。

具体操作步骤如下:分别在Project Name和Project Location里面填写您想要创建的工程的名称和路径。

在Top-Level Module Type的下拉菜单里面选择您的工程的顶层模块的类型。

本次串口通信的实验的顶层为原理图,所以选择Schematic。

然后点击下一步:在这个对话框的上半部分选择您使用的芯片的族(Spartan3),型号(xc3s400),封装(pq208)和速度(-4)。

下面选择您要使用编译和综合的软件,建议使用ISE自带的软件,一是使用简便,二是Xilinx公司对自己的FPGA了解程度比第三方要高很多,所以使用Xilinx公司自己的软件有的时候会获得意想不到的收获。

具体参数选择如图,然后单击下一步:在这个对话框里面新建工程里面的文件,这步也可以放到后面来实现,这里我们先选择下一步:这一步用来添加已经存在的文件,同样,我们在后面实现这步。

点击下一步:在最后这个对话框里面显示了我们即将建立的工程的详细信息,确认无误以后点击完成,ISE将为您创建一个名字为uart_test的工程:三.为刚创建的工程添加源文件:1.添加已经存在的源文件:选中屏幕右上的xc3s400-4pq208,单击ProjectÆAdd Source,在弹出的对话框里面选择您已经存在的程序文件(.v .vhd)。

关于Xilinx ISE简单使用方法介绍

output [7:0] y_out,

);

assign y_out = flag ? x_in : 8'b00000000;

endmodule

3.程序语法检查

如下图所示:

或者:

4.创建测试文件(功能仿真数据的建立)

ProjectNew Source。如输入文件名:Two2One_tf(*.v)。

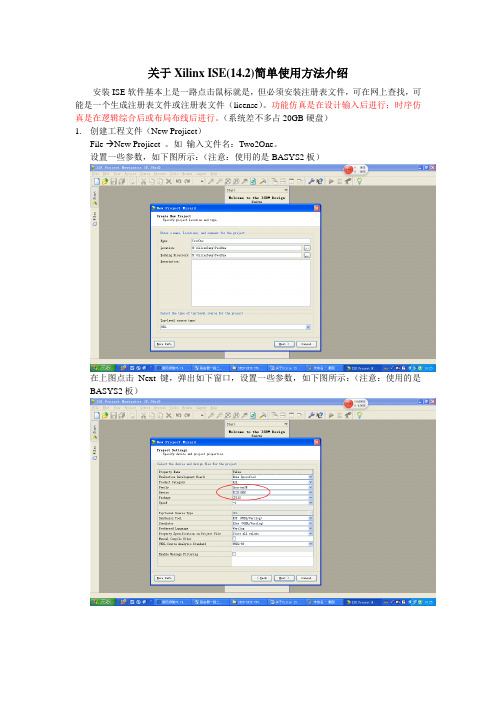

关于Xilinx ISE(14.2)简单使用方法介绍

安装ISE软件基本上是一路点击鼠标就是,但必须安装注册表文件,可在网上查找,可能是一个生成注册表文件或注册表文件(license)。功能仿真是在设计输入后进行;时序仿真是在逻辑综合后或布局布线后进行。(系统差不多占20GB硬盘)

1.创建工程文件(New Projiect)

将运行另外一个程序产生仿真波形图,如下图所示:

详细波形图:

6.管脚适配(为下载做准备)

先创建*.UCF文件

弹出窗口,点击Yes,创建.UCF文件

之后,系统会启动管脚配置程序,然后设计人员根据情况配置管脚,下图为BASYS2板管脚情况,所示:

适配后:

配置好管脚后保存好文件。

7.综合与实现

管脚分配完成之后,必须进行布局布线,如下图所示:

FileNew Projiect。如输入文件名:Two2One。

设置一些参数,如下图所示:(注意:使用的是BASYS2板)

在上图点击Next键,弹出如下窗口,设置一些参数,如下图所示:(注意:使用的是BASYS2板)

2.创建资源文件(New Source)

ProjectNew Source。如输入文件名:One2Two。

选择,如Verilog Test Fxiture,建立用于测试以上资源文件(电路)用的数据文件。建立不同时间段的输入数据,用于产生相应时段的输出波形。

xilinx ise 软件使用方法

双击【 Finish】

选择后缀为bit的文件,单击【 Open】

单击

单击【 Bypass 】

完成下载

1、光标移至该图 标,单击右键

2、单击 Program

单击【 Ok】

下载成功。在开发板上观察结果。

ISE软件使用

• 设计流程 • 新建项目 • 综合 • 仿真

• 设计实现

设计流程

文本编辑器、图形编辑器

VHDL仿真器 (行为仿真、 功能仿真、 时序仿真)

VHDL综合器

网表文件 (EDIF、XNL、 VHDL…) 门级仿真器

(逻辑综合、优化)

FPGA/CPLD布线/适配器 (自动优化、布局、布线、适配)

在测试文件的 tb 进程中对输入信号进行赋值

如下图,在Source for 中选择【Behavioral

Simulation】

如下图,在Processes 窗口中双击【Simulate Behavioral Model】

按下图选择【Add】【Wave】【Signal in Design】,添加 需要观察的信号。如不需观察中间信号,此步骤可省略。

在文本编辑器中输入源文件

综合

在Source窗口中选中需要处理的源文件,在Process窗口 中双击Synthesize-XST。

仿真

如下图,单击【 Create New Source】, 选择源文件类型【 VHDL Test Bench 】,填写源文件名称、路径 然后单击【Next】

如下图,选择与仿真测试文件所对应的源文件,然后单击 【Next】

按下图选择【Run All】, 【Zoom out】 【Zoom mode】、

并删除多余信号。如不需观察中间信号,此步骤可省略

Xilinx_ISE使用教程2

新建文件 的类型, 不同的类 型有着不 同的功能 和意义。

该文 件的 实体 名

Xilinx公司ISE10.1软件设计流程介绍

--添加实体端口

Next

端口名

端口的类型及位数

Xilinx公司ISE10.1软件设计流程介绍

--添加实体端口

给出了该文件 的概要

Finish

Xilinx公司ISE10.1软件设计流程介绍

Xilinx公司ISE10.1软件介绍

--处理(process)子窗口

在该窗口只有一个处理标签。该标签有下列功能: 添加已有文件; 创建新文件; 察看设计总结(访问符号产生工具,例化模板,察看 命令行历史和仿真库编辑); 用户约束文件(访问和编辑位置和时序约束); 综合(检查语法、综合、察看RTL和综合报告); 设计实现(访问实现工具,设计流程报告和其它一些 工具); 产生可编程文件(访问配置工具和产生比特流文件)。

Xilinx公司ISE10.1软件设计流程介绍

--打开ISE软件时的面板

当以前使用 过该软件时会默 认打开上一个工 程。

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

选择芯片 选择综合工具

选择仿真工具

选择代码语言

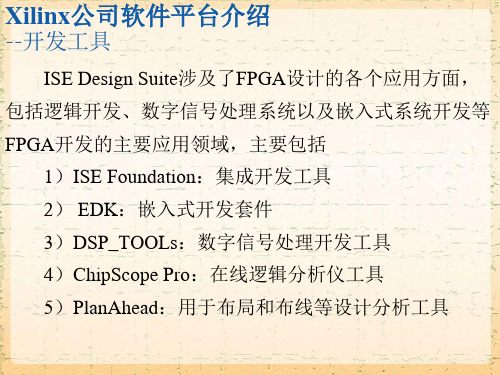

4)ChipScope Pro:在线逻辑分析仪工具

5)PlanAhead:用于布局和布线等设计分析工具

Xilinx公司软件平台介绍

--软件组成

集成开发环 境

在线逻辑分析 仪工具

片上系统开发

数字信号处 理开发工具

布局布线 工具

Xilinx公司软件平台介绍

ISE软件使用

entity count10 is port(clk: in std_logic; dout:out std_logic_vector(6 downto 0); dclk1:out std_logic); end count10; architecture Behavioral of count10 is signal clk1: std_logic := '1'; signal q: integer range 0 to 15:=0; signal w: integer range 0 to 10:=0; begin

6、新文件输入完善

建然后一直单击“下一步” 建然后一直单击“下一步”直到完成到下图

7、程序输入

在下图的右窗口输入设计源程序内容, 在下图的右窗口输入设计源程序内容,完成后点保存

设计输入例程

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_U启动软件

启动program/xilinx Navigator到下图界面 启动program/xilinx ise 9.1/project Navigator到下图界面

2、建立项目工程

project】 【file】--【new project】如下图所示 ,键入项目的名称和 file】--【 保存项目各文件的地址(可以先建好保存项目名的文件夹) 保存项目各文件的地址(可以先建好保存项目名的文件夹)

原文件的仿真运行

下图中选种Sources in Project窗下的仿真文件,双击处理窗中的 窗下的仿真文件, 下图中选种 窗下的仿真文件 ModelSim Simulator栏内的 栏内的Simulate Behavioral Model.开始仿真 栏内的 开始仿真

Xilinx_ISE操作示例

全文只有此3个告警信 息 , 更 无 “ errors” 信息。否则,需根 据信息内容回到前 面文件中纠正错误。

五.实现

在Processes小窗口中 下拉选项,找到并双 击“Implement Design”。等待程序 运行完毕。 运行结果正确后, Processes小窗口的 “Implement Design”项目中显 示如右图结果(绿 圈勾):

4.选择原理 图输入 5.点击

3.点击

选择器件型号和工具软件

1 . 选择器件型号与圈 内的3项完全一致

2.选择工具软件与圈内 的4项完全一致

3.点击

建立新的源文件

点击

敲入文件名,选择原理图

2. 选择原理 图选项

1. 键 入 新 的 原 理图文件名

3.点击

完成

点击

接下来两个弹出窗口连续单击“Next” ,第三个弹出窗口单击“Finish”

节点命名 k1 f2 注:5处红色的节 点都需命名

f1 k2 cp

节点命名后电路如下图。再选择“Add I/O Marker”图标,添加输入/输出盘:点击图标后 依次移动光标到节点名处,单击鼠标左键。

添加输入/输出盘

完成后电路如下图,保存电路图。

保存电路图

二.

功能仿真

按下图选项顺序操作:

2.单击 3.单击 4. 空 白 处 单 击 鼠标右键 1.单击

双击

运行结束后弹出功能仿真结果窗口如下图。

0 0

1 0

0 1

1 1

0 0

0bit

1bit

2bit

3bit

0bit

三.编写约束文件

在Sources小窗口的空白处单击鼠标右键,在弹出的 对话框中选择“New Source”后,再次弹出对话框 如下图,按图示顺序操作:

XilinxISE软件简单教程课件

Xilinx ISE软件的优缺点

概述Xilinx ISE软件的优点和 缺点,帮助用户全面评估软 件。

Xilinx ISE软件的应用场 景

介绍Xilinx ISE软件广泛应用 于哪些领域和项目,以及其 在每个领域中的优势。

XilinxISE软件简单教程课 件

Xilinx ISE软件简单教程课件为您提供了入门级的教程,让您了解Xilinx ISE软 件的作用、特点以及使用方法。

简介

Xilinx ISE软件是什么?

介绍Xilinx ISE软件是一款功能强大的FPGA开发工具,可以帮助您设计和验证数字电路。

Xilinx ISE软件的作用

解释下载和仿真之间的区别和各自的用途。

3 下载和仿真的流程

讲解下载和仿真的基本步骤,以便用户正确地验证并调试设计。

实例操作

具体实例操作演示

通过示范一个具体的实例,向用户展示Xilinx ISE软 件的使用方法。

实例的说明和分析

对实例进行逐步解析和分析,帮助用户理解设计过 程和结果。

总结

Xilinx ISE软件的功能

解释综合和实现在FPGA设计流 程中的作用和区别。

综合和实现的关系

讨论综合和实现之间的紧密关 联,以及它们在设计迭代中的 作用。

综合和实现的过程

详细描述综合和实现的步骤, 以及如何将设计转换为可下载 的位文件。

下载和仿真

1 下载和仿真的作用

介绍下载和仿真在FPGA设计验证和调试过程中的重要性。

2 下载和仿真的区别

参考资料

相关书籍和文献

提供与Xilinx ISE软件相关的书籍和文献,以便用户进一步学习和深入研究。