探索组合逻辑电路的竞争冒险现象及消除方法

组合逻辑电路竞争冒险现象和消除方法仿真研究_朱幼娟

ZHU You-juan WANG Lu

( School of Electronic and Electrical Engineering,Changzhou College of Information Technology,Changzhou 213164,China)

Abstract :Race and hazard phenomenon,in theory,is due to the delay in logic gate circuits and the transmission of input signals throughout different steps of components,which can be well demonstrated by the simulation software platform Multisim. Errors and bugs may come out and then effect cirrus' working,while this kind of phenomenon takes place. To judge if there will be these phenomenon,we have different methods,such as algebra analyze,computer simulating,practical measuring. The elimination methods are also various,adding excess subject,flip-flop deliver output signal,and output-port parallel connected with other circuits. The application of simulation in demonstration and reveal of race and hazard phenomenon work well,the practical result matches the theoretical one.

探索组合逻辑电路的竞争冒险现象及消除方法

探索组合逻辑电路的竞争冒险现象及消除方法随着电子技术的不断发展和应用,组合逻辑电路作为数字电路中最简单的一种电路,在电子设备中应用广泛。

然而,在实际应用中,我们常常会遇到一些竞争冒险的问题。

那么,究竟什么是竞争冒险呢?它又是如何产生的呢?如何消除这种现象呢?下面就来一一解答。

一、竞争冒险的定义竞争冒险(Race Hazard)是指输入信号有多条路径到达输出端,而输出信号的正确性与哪条输入路线先到达输出端有关的一种现象。

简而言之,竞争冒险就是同一信号在不同的路径上到达目的地的时间不同,导致信号的正确性无法得到保证。

二、竞争冒险的产生原因竞争冒险通常是在异步电路中产生的。

异步电路是一种没有时钟信号的电路。

因为没有时钟信号控制,异步电路的输入信号会在任何时间到达电路中。

如果异步电路的不同信号路径的延时不相等,就会产生竞争冒险。

三、竞争冒险的消除方法为了消除竞争冒险,我们有以下几种方法:1.插入缓冲器插入缓冲器是一种最基本的解决竞争冒险问题的方法。

在信号到达目的地之前,可以在较长的信号路径中插入缓冲器,使延时较短的信号路径延迟与较长的信号路径相同的时间,达到信号的同步。

2.加强约束条件加强约束条件也可以消除竞争冒险的问题。

在设计电路的时候,我们可以设置更为严格的约束条件,使得各个信号路径的延迟时间尽量相近,从而避免产生竞争冒险。

3.优化电路结构优化电路结构也可以解决竞争冒险的问题。

我们可以在电路设计过程中尽量避免存在长短不一的信号路径,或者在架构设计时就考虑到延迟问题,在电路结构设计时保持信号路径相对简单结构,减少信号传输延迟时间。

总之,竞争冒险是组合逻辑电路中不可避免的现象,我们应该在电路设计与实现中充分考虑其存在,采取相应的措施来消除竞争冒险带来的风险和影响。

探索组合逻辑电路的竞争冒险现象及消除方法

探索组合逻辑电路的竞争冒险现象及消除方法

组合逻辑电路是指一些由多个逻辑门组成的逻辑电路。

它们一般不具有记忆性,不涉及时钟信号,是根据输入信号直接输出结果的电路。

虽然组合逻辑电路看起来非常简单,但是在实际应用中存在着一些竞争冒险,这可能导致电路输出错误的结果。

本文将探讨组合逻辑电路的竞争冒险现象及消除方法。

竞争冒险是指当多个逻辑门的输入信号在不同的时间到达时,电路不能准确地确定输出信号。

这是由于电路中存在着多条不同的信号路径,当这些路径的信号到达的时间不同,就会发生竞争冒险。

这个现象如果不及时解决,就会导致电路输出错误的结果,甚至会使整个系统崩溃。

竞争冒险可以通过添加延迟元件来解决。

这些延迟元件包括反相器和缓冲器。

反相器可以改变输入信号的极性,并将输出信号延迟一定时间后输出。

缓冲器可以加强信号的强度,并将信号的延迟控制在很小的范围内。

通过添加这些延迟元件,可以精确地控制信号的延迟时间,从而避免竞争冒险。

另外,竞争冒险问题也可以通过优化电路结构来解决。

由于冒险问题是由信号路径的不同导致的,我们可以尽可能地减少信号路径的长度和数量。

在优化电路时,需要考虑到电路的性能和延迟时间之间的平衡。

如果性能过于复杂,就会增加信号延迟时间,从而导致冒险问题。

如果性能过于简单,就会降低电路的效率和稳定性。

总之,竞争冒险是组合逻辑电路中常见的问题之一。

通过添加

延迟元件和优化电路结构,可以有效地解决这个问题。

在实际应用中,我们必须注意电路的稳定性和效率,以便顺利地解决竞争冒险问题,保证电路的正确性。

组合逻辑电路中的竞争与冒险-Read

组合逻辑电路中的竞争与冒险(5)

消除竞争冒险的方法:

在电路输出端并联滤波电容C; 最简设计并

不一定是最优设

在电路输入端加选通信号; 计。

在电路设计中增加冗余项。

F AB BC AC

BC A 00 01 11 10

0

1

1

111

令 AC1

F AB BC AC B B 1 1

生瞬时错误的现 F

象。

组合逻辑电路中的竞争与冒险(2)

例2:

注意:竞争不一

A B

&

Y

定产生冒险!

考虑竞争时

不考虑竞争时

---由于信号变换过程的先后,有

A

A

A

VT

VT

B

B

VT B

VT

Y “0”

Y

Y

组合逻辑电路中的竞争与冒险(3)

竞争与冒险现象的判断

当竞争可能由于同一信号的不同传输延迟引起时, 可用以下方法判断:

代数法:将输出函数进行某种处理,若能化成 F XX

或 F X X 的形式,则可能产生冒险。

如:F AB BC

若令 A C 1 则 F B B

B

B

A B

ቤተ መጻሕፍቲ ባይዱ1 B

C

F1 AB &

F1

F1 B

F AB BC

&

F2

&

F2 B

F F1 F2 B B F

组合逻辑电路中的竞争与冒险(1)

竞争与冒险的概念

竞争:同一信号经不同途径传输后到达某一门电路时有先有后,

或同一门电路的不同输入信号由于过渡过程不同而引起

组合逻辑电路的竞争和冒险(精)

可能出现1型冒险。

Y A A

可能出现0型冒险。

例:试判别逻辑函数式 Y AC AB AC 是否可能出现冒险现象。 解:写出逻辑函数式 Y AC AB AC 由逻辑表达式可看出A、C具有竞争能力

BC 00, Y A BC 01, Y ABC 10, Y A

同一个门的一组输入信号,由于它们在此前通过 不同数目的门,经过不同长度导线的传输, 到达门输入端的时间会有先有后,这一现象称为竞争。

四、冒险

逻辑门因输入端的竞争而导致输出产生不应有的尖峰干扰脉冲 (又称过渡干扰脉冲)的现象。 如下图所示电路中,输出

G1 A 1 G2 >=1 Y Y A A 1 Y A 1tpd 1

Y AC AB AC BC 1 消除了冒险

BC 11, Y A A

Y A A 将产生偏“1”冒险。 由此可见,当BC=11时,

AB 00, Y C

AB 10, Y C

AB 01, Y 1

AB 11, Y C

虽然具有竞争,但不会产生冒险 说明 由于冒险出现的可能性很多,而且组合电路 的冒险现象只是可能产生,而不是一定产生, 更何况非临界冒险是允许存在的。

Y A A

A

理想情况下的工作波形如图12-6(b)所示。

如考虑到G1门的平均传输延迟时间tpd时,则工作波形 如图12-6(c)所示。

可见,G2门的两个输入信号A、

由于传输路径不同,到达G2门的输入端时,信号比A 延迟了tpd。因此,使G2门输出端出现了很窄的负脉冲。 按照设计要求,这个负尖脉冲是不应该出现的,他的 出现可能会导致负载电路的错误动作。 在下图12-7(a)所示电路中,输出 Y A A 如考虑G1门的平均传输延迟时间tpd时,则在G2输出端 出现了不应有的很窄的正尖峰脉冲,如图12-7(b)

组合逻辑电路中的竞争与冒险知识讲解

A

1tpd A

1 Y

理想情况下的工作波形如图12-6(b)所示。

如考虑到G1门的平均传输延迟时间tpd时,则工作波形 如图12-6(c)所示。

G1

A

1

G2

A

&

YA

1tpd

(a)

Y

(b)

五、产生竞争冒险的主要原因

在组合逻辑电路中,当一个门电路如G2输入两 个同时向相反方向变化的互补信号时,则在输 出端可能会产生不应有的尖峰原因

1

竞争 冒险

3 消除冒险 现象方法

2

冒险现象判别

一、理想情况

输入与输出为稳定状态或没有考虑信号通过导线和 逻辑门的传输延迟时间。

二、实际情况

信号通过导线和门电路时,都存在时间延迟tpd。 信号发生变化时也有一定的上升时间tr 或下降时间tf 。

在组合逻辑电路中,是否存在冒险现象,可由逻辑函数来判别 如根据组合逻辑电路写出的输出逻辑函数在一定条件下可简化成 下列两种形式时,则该组合逻辑电路可能存在冒险现象,即

YA•A 可能出现1型冒险。 YAA 可能出现0型冒险。 例:试判别逻辑函数式 YAC ABAC是否可能出现冒险现象。

解:写出逻辑函数式 YAC ABAC 由逻辑表达式可看出A、C具有竞争能力

一、加封锁脉冲

在输入信号产生竞争冒险的时间内,引入一个脉 冲将可能产生尖峰干扰脉冲的门封锁住。封锁脉 冲应在输入信号转换前到来,转换结束后消失。

二、加选通脉冲

对输出可能产生尖峰干扰脉冲的门电路增加一个接选通 信号的输入端,只有在输入信号转换完成并稳定后,才 引入选通脉冲将它打开,此时才允许有输出。在转换过 程中,没有加选通脉冲,输出不会出现尖峰干扰脉冲。

数字电子技术竞争与冒险

三、冒险现象的消除

1. 利用冗余项 如图所示卡诺图,只要在两圈相切处增加一个圈(冗余),就能 消除冒险。由此得函数表达式为

三、冒险现象的消除 1. 利用冗余项 2. 吸收法

在输出端加小电容C可以消除毛刺如图3-58所示。但是输出波 形的前后沿将变坏, 在对波形要求较严格时,应再加整形电路。

三、冒险现象的消除

本

章

(1)组合电路 任何时刻的输出仅决定于当时的输入,而与电路原来的状 态无关;它由基本门构成,不含存贮电路和记忆元件,且 无反馈线。 (2)组合电路的分析 根据已经给定的逻辑电路,描述其逻辑功能。 (3)组合电路的设计 根据设计要求构成功能正确、经济、可靠的电路

小

结

(4)常用的中规模组合逻辑模块

加法器、比较器、译码器、编码器、数据选择器等。

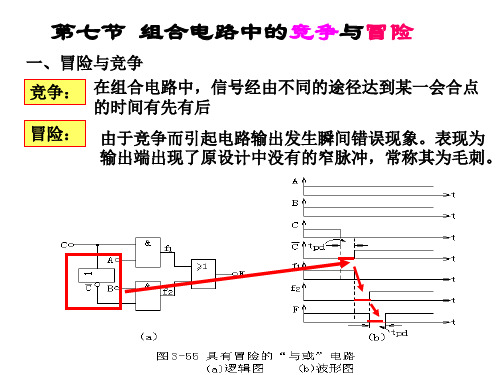

第七节 组合电路中的竞争与冒险

一、冒险与竞争 竞争: 在组合电路中,信号经由不同的途径达到某一会合点 的时间有先有后 冒险:

由于竞争而引起电路输出发生瞬间错误现象。表现为 输出端出现了原设计中没有的窄脉冲,常称其为毛刺。

ቤተ መጻሕፍቲ ባይዱ

二、竞争与冒险的判断

代数法:或的形式时,A变量的变化可能引起险象。 卡诺图法: 如函数卡诺图上为简化作的圈相切,且相切处又无 其他圈包含,则可能有险象。 如图所示电路的卡诺图两圈相切,故有险象。

1. 利用冗余项

2. 吸收法 3.取样法 电路稳定后加入取样脉冲,在取样脉冲作用期间输出的信号才有 效,可以避免毛刺影响输出波形。

加取样脉冲原则: “与”门及“与非”门加 正取样脉冲

“或”门及“或非”门 加负取样脉冲

三种方法比较:

利用冗余项:只能消除逻辑冒险,而不能消除功能冒险;适 用范围有限

竞争冒险现象分析与消除

整理课件

6

(a)竞争冒险现象的仿真电路例1

整理课件

7

(b)0(低电平)型冒险输出 图8.10.1 竞争冒险现象的仿真电路与输出波形

整理课件

8

2. 竞争冒险现象的仿真电路例

竞争冒险现象的仿真电路例2如图8.10.2 (a)所示,该电路的逻辑功能为,从逻辑表 达式来看,无论输入信号如何变化,输出应保 存不变,恒为0(低电平)。但实际情况并非 如此,从仿真的结果可以看到,由于74LS05D

整理课件

2

利用卡诺图可以判断组合逻辑电路是否可能 存在竞争冒险现象,具体做法如下:根据逻辑函 数的表达式,作出其卡诺图,若卡诺图中填1的格 所形成的卡诺图有两个相邻的圈相切,则该电路 就存在竞争冒险的可能性。

整理课件

3

组合逻辑电路存在竞争就有可能产生冒险, 造成输出的错误动作。因此,在设计组合逻辑电 路时必须分析竞争冒险现象的产生的原因,解决 电路设计中的问题,杜绝竞争冒险现象的产生。 常用的消除竞争冒险的方法有:加取样脉冲,消 除竞争冒险;修改逻辑设计,增加冗余项;在输 出端接滤波电容;加封锁脉冲等。

整理课件

14

(a)竞争冒险现象的仿真电路例3

整理课件

15

(b)0(低电平)型冒险输出 图8.10.2 竞争冒险现象的仿真电路与输出波形

整理课件

16

8.10.3 竞争冒险现象的消除

为了消除图8.10.3(a)所示电路的竞争冒险 现象,修改逻辑设计,增加冗余项BC,该电路的逻 辑功能为+BC,修改后的电路和仿真结果如图 8.10.4所示,输出保持不变,恒为1(高电平), 电路的竞争冒险现象被消除。

竞争冒险现象的仿真电路例3如图8.10.3 (a)所示,该电路的逻辑功能为,已知B=C=1, 所以。从逻辑表达式来看,无论输入信号如何变 化,输出应保存不变,恒为1(高电平)。但实 际情况并非如此,从仿真的结果可以看到,

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

探索组合逻辑电路的竞争冒险现象及消除方法

探索组合逻辑电路的竞争冒险现象

在组合逻辑电路中,当两个或多个数字信号在一个逻辑门的输入端同时到达时,它们可能会在输出端引发竞争冒险现象。

竞争冒险是一种反复变化的情况,它会导致逻辑门的输出错误,导致系统出现故障和数据的不稳定性。

竞争冒险通常发生在门的输入信号不同步的情况。

例如,当一个逻辑门的输入信号有较长的传输延迟时,就会发生竞争冒险现象。

竞争冒险现象包括两种类型:正竞争冒险和负竞争冒险。

正竞争冒险现象是指当两个或多个输入信号在一个逻辑门的输入端发生相等的变化时,输出信号经历一段时间后发生突变,随后又恢复到原始状态。

反之,负竞争冒险现象在输入信号发生变化时,输出信号开始反转,但在一段时间后突然又回到了原来的状态。

消除竞争冒险的方法

1.增加延迟器:一个适当的延迟器可以将输入信号的时间稍微延迟,使得输入信号的“斜率”上升和下降不那么陡峭。

门可增加输入延迟管分量,来保持一致到达。

另外,在输出延迟管分量中引入等同或近似的延迟。

2.使用锁存器或触发器:锁存器或触发器可以消除竞争冒险。

它们允许信号在一段时间内维持稳定状态,从而消除竞争。

锁存器或触发器的初始状态是通过设定输入信号来实现的。

锁存

器或触发器的一个典型应用是用于设置微处理器中的同步逻辑。

3.使用带有输入同步的片:带有输入同步的片可用于消除竞争

冒险。

输入同步保持各种输入信号在一个稳定的电平上,直到其同步时钟到达。

同步片的输入同步机制允许输入信号在时钟边沿处被读取,比较突出。

4.使用逻辑修正电路:逻辑修正电路用于处理竞争冒险,使逻

辑门产生正确的输出。

修正电路可解决所有类型的竞争问题。

它的作用是将输入信号延迟一个适当的时间,使得它们在逻辑门中被处理。

此外,逻辑修正电路还允许信号在特定间隔内保持稳定状态,以避免出现竞争。

总的来说,消除竞争冒险的方法包括增加延迟器、使用锁存器或触发器、使用带有输入同步的片和使用逻辑修正电路。

这些方法在不同的情况下都可以显著地降低竞争冒险现象的风险,从而提高组合逻辑电路的可靠性和稳定性。